sopc开发流程

sopc

∙SoPC即片上可编程系统(SoPC-System on a Programmable Chip),是一种灵活、高效的SoC解决方案。

它将处理器、存储器、I/O口、LVDS等系统需要的作用模块集成到一个PLD器件上,构成一个可编程的片上系统。

它是PLD和SOC技术融合的结果。

目录∙构成sopc的三种方案∙sopc三种方案的比较∙sopc的特点∙sopc的开发流程∙sopc的解决方案构成sopc的三种方案∙ 1 基于FPGA嵌入IP硬核的SOPC系统:该方案是指在FPGA中预先植入处理器.最常用的是含有ARM32位知识产权处理器核的器件。

为了到达通用性,必须为常规的嵌入式处理器集成诸多通用和专用的接口,但增加了成本和功耗.如果将ARM或其它处理器核以硬核方式植入FPGA中,利用FPGA中的可编程逻辑资源,按照系统作用需求来添加接口作用模块,既能实现目标系统作用,又能降低系统的成本和功耗. 这样就能使得FPGA灵活的硬件设计和处理器的强大软件作用有机地结合在一起,高效地实现SOPC系统。

IP硬核直接植入FPGA存在以下不足: IP硬核多来自第三方公司,FPGA厂商无法控制费用,从而导致FPGA器件价格相对偏高. IP硬核预先植入,使用者无法根据实际需要改变处理器结构.更不能嵌入硬件加速模块(DSP). 无法根据实际设计需要在同一FPGA中集成多个处理器. 无法根据实际设计需要裁减处理器硬件资源以降低FPGA成本. 只能在特定的FPGA中使用硬核嵌入式处理器2 基于FPGA嵌入IP软核的SOPC系统:IP软核处理器能有效克服上述不足: 目前最有代表性的软核处理器分别是Altera公司的Nios II核,以及Xilinx公司的MicroBlaze核.特别是Nios II核,能很好的解决上述五方面的问题. Altera的Nios II核是用户可随意配置核构建的32位嵌入式处理器IP核,采用Avalon总线结构通信接口;包含由FS2开发的基于JTAG的片内设备内核. 在费用方面,由于Nios II是由Alter公司直接提供而非第三方厂商产品,故用户通常无需支付知识产权费用,Nios II的使用费用仅仅是其瞻仰的FPGA逻辑资源的费用3 基于HardCopy技术的SOPC系统:HardCopy就是利用原有的FPGA开发工具, 将成功实现于FPGA器件上的SOPC系统通过特定的技术直接向ASIC转化,从而克服传统ASIC设计中普遍存在的问题. ASIC (SOC)开发中难于克服的问题包括:开发周期长,产品上市慢,一次性成功率低,有最少投片量要求,设计软件工具繁多且昂贵, 开发流程复杂等.利用HardCopy技术设计ASIC,开发软件费用少,SOC级规模的设计周期不超过20周,转化的ASIC和用户设计习惯的掩模层只有两层,且一次性投片的成功率近乎100%,即所谓的FPGA 向ASIC的无缝转化用ASIC实现后的系统性能将必原来在HardCopy FPGA上验证的模型提高近50%,而功耗则降低40%.HardCopy技术是一种全新的SOC级ASIC设计解决方案,即将专用的硅片设计和F PGA至HardCopy自动迁移过程结合在一起的技术,首先利用Quartus II将系统模型成功实现于HardCopy FPGA上,然后帮助设计者把可编程解决方案无缝地迁移到低成本的ASIC上.这样, HardCopy器件就把大容量FPGA的灵活性和ASIC 的市场优势结合起来,实现对于有较大批量要求并对成本敏感的电子产品上,从而避开了直接设计ASIC的困难.sopc三种方案的比较∙sopc的特点∙SOPC结合了SOC和PLD、FPGA各自的优点,一般具备以下基本特征:至少包含一个嵌入式处理器内核;具有小容量片内高速RAM资源;丰富的IP Core资源可供选择;足够的片上可编程逻辑资源;处理器调试接口和FPGA编程接口;可能包含部分可编程模拟电路;单芯片、低功耗、微封装。

EDA技术——SOPC设计“hello world”

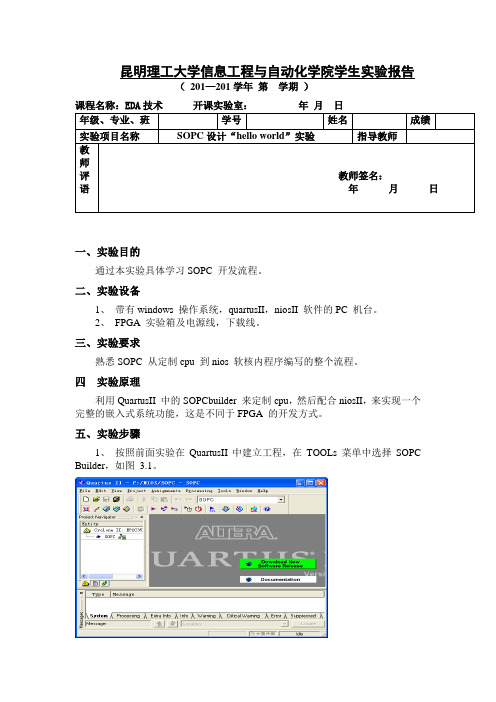

昆明理工大学信息工程与自动化学院学生实验报告( 201—201学年 第 学期 )课程名称:EDA 技术 开课实验室: 年 月 日 年级、专业、班 学号 姓名 成绩 实验项目名称 SOPC 设计“hello world ”实验 指导教师教师评语教师签名:年 月 日一、实验目的通过本实验具体学习SOPC 开发流程。

二、实验设备1、 带有windows 操作系统,quartusII ,niosII 软件的PC 机台。

2、 FPGA 实验箱及电源线,下载线。

三、实验要求熟悉SOPC 从定制cpu 到nios 软核内程序编写的整个流程。

四 实验原理利用QuartusII 中的SOPCbuilder 来定制cpu ,然后配合niosII ,来实现一个完整的嵌入式系统功能,这是不同于FPGA 的开发方式。

五、实验步骤1、 按照前面实验在QuartusII 中建立工程,在TOOLs 菜单中选择SOPC Builder ,如图 3.1。

图3.1 建立工程✧新工程名命名为SOPC。

✧建完这个工程后,首先建一个原理图文件。

✧File->new->Block Diagram/Schematic File,通过此操作建好一个原理图文件,如图3.2所示。

图3.2 建立原理图文件2、定制CPU,参照上图,有一个图标,点击它打开SOPC builder,打开后,在弹出的界面system name后填写名字,这里写的是cpu,自己可以起其他名字,然后点ok,如图 3.3。

图 3.3 SOPC builder 界面1) 构建处理器模块:处理器就是用来做解释程序,运算等操作,图中左栏可以看到,Nios II Processer选项,双击后弹出处理器的属性选项框,我们自己设置参数,来定制所需的处理器,如图 3.4。

图 3.4 处理器属性框✧这里为我们提供了三种类型的CPU,Nios II/e 占用资源最少600-800LEs,功能也最简单,速度最慢。

sopc开发环境的使用

• 设置好软件运行 的硬件环境属性后, 便可进行编译、链 接和调试、运行程 •对用户程序进行 序。 编译,生成可执 行文件*.elf。 • 接 下 来 在 IDE 的 指令集仿真器(ISS) 上仿真软件和运行/ 调试软件。 • 在目标板上反 复调试软件。

下载配置文件到 FPGA器件

在目标板上 下载可执行 软件到 Nios II系统

SOPC开发流程和开发工具

软件开发

软件开发使用Nios II IDE,它是一个基于Eclipse IDE架构的集成 开发环境,它包括: GNU开发工具(标准GCC编译器,连接器,汇编器和 makefile工具等); 基于GDB的调试器,包括软件仿真和硬件调试; 提供用户一个硬件抽象层HAL; 提供嵌入式操作系统MicroC/OS-II和LwTCP/IP协议栈的支持; 提供帮助用户快速入门的软件模板; 提供Flash下载支持(Flash Progrmmer 和QuartusII Programmer)

软 件 开 发 也 可 以 在 SOPC Builder 生成系统模块后立 即进行!与传统软件开发类 似,唯一不同在于系统是自 己定制的,所受局限小!

NiosII内核 &标准外设

打开SOPC Builder 定义和生成系统

定制指令&定 制外设逻辑

自定义的 功能模块

集成SOPC生 成的系统到 Quartus II工程

打开SOPC Builder 定义和生成系统

定制指令&定 制外设逻辑

自定义的 功能模块

集成SOPC生 成的系统到 Quartus II工程

Altera的 LPM模块

硬件抽象层 (HAL)&外设 驱动程序

使用Nios II IDE开发软件

SOPC综合课程设计指导书

第一章EDA技术综合应用设计基础1.1 EDA技术综合应用的形式随着EDA技术的深入发展和EDA技术软硬件性能价格比的不断提高,EDA技术的应用将向广度和深度两个方面发展。

根据利用EDA技术所开发的产品的最终主要硬件构成来分,作者认为,EDA技术的应用发展将表现为如下几种形式:(1) CPLD/FPGA系统:使用EDA技术开发CPLD/FPGA,使自行开发的CPLD/FPGA作为电子系统、控制系统、信息处理系统的主体。

(2) ―CPLD/FPGA+MCU‖系统:综合应用EDA技术与单片机技术,将自行开发的―CPLD/FPGA+MCU‖作为电子系统、控制系统、信息处理系统的主体。

(3) ―CPLD/FPGA+专用DSP处理器‖系统:将EDA技术与DSP专用处理器配合使用,用―CPLD/FPGA+专用DSP处理器‖构成一个数字信号处理系统的整体。

(4) 基于FPGA实现的现代DSP系统:基于SOPC(a System on a Programmable Chip)技术、EDA技术与FPGA技术实现方式的现代DSP系统。

(5) 基于FPGA实现的SOC片上系统:使用超大规模的FPGA实现的,内含1个或数个嵌入式CPU或DSP,能够实现复杂系统功能的单一芯片系统。

(6) 基于FPGA实现的嵌入式系统:使用CPLD/FPGA实现的,内含嵌入式处理器,能满足对象系统要求的特定功能的,能够嵌入到宿主系统的专用计算机应用系统。

1.2 EDA技术综合应用的设计方法与建模1.2.1 分析方法传统的电路设计方法都是自底向上进行设计的,也就是首先确定可用的元器件,然后根据这些器件进行逻辑设计,完成各模块后进行连接,最后形成系统。

在基于EDA技术的系统设计的最重要环节——在系统的基本功能或行为级上对设计的产品进行描述和定义时,我们采用自顶向下分析,自底向上设计的方法。

所谓―自顶向下分析‖,就是指将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大,则还需将子系统进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子系统关系合理,并便于逻辑电路级的设计和实现为止。

sopc课程设计

SoPC课程设计(报告)题目:液晶控制显示器学院:电子工程学院系部:微电子学系专业:集成电路设计与集成系统班级: 1002 学生姓名:曹松松指导教师:曾泽沧起止时间: 2013年6月17日——2013年6月28日目录1 课程设计要求 (2)基本要求 (2)2 实验使用平台 (2)3 题目:选题2 (2)4 课程设计总结 (5)5 附件 (5)1课程设计要求基本要求课程设计要求所有题目采用Quartus II 工具提供的图形输入或者VerilogHDL语言输入方式作为电路设计工具,在NiosII上采用C语言实现编程,自定向下正向设计方法,先设计硬件系统,再进行软件编程,能够生成正确的FPGA下载代码和NiosII执行的软件代码。

硬件功能仿真和时序仿真采用第三方工具(建议为:modelsim),综合与布局布线工具为:Quartus II,SOPC Builder建立软件运行环境,具体要求为:1)根据课设题目,进行总体设计方案(10分);2)硬件电路顶层设计、模块划分、引脚定义(10分);3)电路设计及NiosII设计,提交电路设计源代码或电路图(10分);4)综合与布局布线,提交综合与布局布线报告(10分);5)FPGA下载代码和引脚分布(10分);6)软件总体设计及画出流程图(10分);7)程序设计,提交程序代码(10分);8)程序编译下载及仿真调试(10分)。

2实验使用平台实验平台使用Altera的DE2开发板,开发工具使用Altera的Quartus II和Nios II IDE。

3 题目:选题2在字符型液晶显示器上移动显示“XIAN UNIVERSITY POST AND TELECOMMUNICATIONS YOUR NAME 2013-6”,要求FPGA 设计硬件,内嵌NiosII,液晶显示采用软件实现。

1)根据课设题目,进行总体设计方案;(10分)此次sopc课程设计选题2,题目相对比较简单。

ARM与FPGA的接口实现

4.2 基于Altera公司的Excalibur 系列芯片实现的图像采集处理系统

4.2 基于FPGA+ARM实现的星敏感器

4.2.1 星敏感器的原理框图

星空

光学 系统

图像 传感器

信号 处理

星点 提取

星图 识别

姿态 计算

姿态

导航星库

星表/导航星

观测星图/观测星

4.2.2 星敏感器的相关技术

镜头设计 图像传感器选择 图像驱动 图像处理(星图识别)

3 SOPC开发工具及开发流程

QUARTUS II + SOPC Builder + Nios II IDE

EDK(XPS+SDK) + ISE

-参考书 《基于EDK的FPGA嵌入 式系统开发》

4 嵌入式系统应用实例

4.1 基于Altera公司的Excalibur 系列芯片的EPXA10开发板

2 FPGA的嵌入式处理器

选择软核处理器还是硬核处理器?

对处理器的性能要求不高(仅要求几个到一两百个DMIPS,采用不多的 FPGA资源就可以,则采用嵌入软核处理器是合适的选择。

需要数据、协议处理能力超过300DMIPS,且难以由多个处理器分担,则

采用1,100MIPS的高性能PowerPC嵌入硬核处理器较合适。 FPGA中嵌入的处理器应当与FPGA及其所面向的市场、应用需求相匹配。

是否需要在FPGA中嵌入处理器?

FPGA适合用于逻辑控制、接口控制、规则数据处理,设计具有复杂算 法和逻辑控制系统时,需要结合使用嵌入式处理器 对系统集成度要求较高,将处理器嵌入FPGA能最大限度地提高系统集 成度,降低系统设计复杂度,加快上市时间。 对需求变化提供较大的灵活性,在FPGA中嵌入处理器较为合适。FPGA 与芯片处理器的结合的优点是无

sopc系统的开发流程

sopc系统的开发流程英文回答:The development process of a SOPC (System on Programmable Chip) system typically involves several key steps.1. System Requirements and Design: The first step in developing a SOPC system is to clearly define the system requirements and design the system architecture. This involves understanding the functionality and performance requirements of the system and determining the key components that will be included in the design.2. Hardware Design: Once the system architecture is defined, the next step is to design the hardware components of the SOPC system. This may involve designing custom logic using hardware description languages (HDL) such as Verilog or VHDL, as well as selecting and integrating off-the-shelf IP cores for standard functions.3. Software Development: In parallel with hardware design, software development for the SOPC system also takes place. This may involve writing device drivers, firmware, and application software that will run on the system.4. Integration and Testing: After the hardware and software components are developed, they need to beintegrated and tested together as a complete system. This involves verifying that the hardware and software work together as intended and meet the system requirements.5. Verification and Validation: Once the SOPC system is integrated, it needs to undergo thorough verification and validation to ensure that it meets the functional and performance requirements. This may involve simulation, emulation, and prototype testing.6. Deployment and Maintenance: After the SOPC systemhas been verified and validated, it can be deployed for use. However, the development process doesn't end here. The system will require ongoing maintenance and support toaddress any issues that arise and to incorporate new features or updates.中文回答:SOPC系统的开发流程通常包括以下几个关键步骤。

SOPC开发流程及开发平台简介PPT课件

分配外设地址和中断

生成系统

SOPC Builder GUI

自定义命令

IP

模块

处理器库

外设模块库

硬件开发

Nios II IDE

软件开发

Quartus II

GNU Tools

HDL 源文件 测试台

用户逻辑设计 其它的IP模块 SOPC Builder的 顶层.bdf文件

2.1 SOPC开发流程

软件开发

配置Nios II处理器

选择并配置外设.IP

连接各外设模块

分配外设地址和中断

生成系统

SOPC Builder GUI

自定义命令

IP

模块

处理器库

外设模块库

硬件开发

Nios II IDE

软件开发

Quartus II

GNU Tools

使用SOPC Builder生成系统后,可以直接使用Nios II IDE开始设计C/C++应用程序代码。Altera提供外设驱动程序和硬件抽象层(HAL),使用户能够快速编写与低级硬件细节无关的Nios II程序;

2.1 SOPC开发流程

QuartusII: 用于完成Nios II系统的分析综合、硬件优化、适配、配置文件编程下载以及硬件系统测试等;

SOPC Builder: 它是Nios II软核处理器的开发包,用于实现Nios II系统配置、生成以及与Nios II系统相关的监控和软件调试平台的生成;

Nios II IDE: 用于完成基于Nios II系统的软件开发和调试,并可借助其自带的Flash编程器完成对Flash以及EPCS的编程操作。

2.1 SOPC开发流程

SOPC系统架构与系统生成

FPGA 硬件设计流程

tclk

DA Lab

Timing Analysis(时序分析)

- Verify Performance Specifications Were Met - Static Timing Analysis

Gate Level Simulation(门级仿真)

- Timing Simulation - Verify Design Will Work in Target Technology

FPGA开发环境

Quartus II

以Altera公司的SOPC解决方案为例

DA Lab

系统构建软件

SOPC Builder

NiosII软件开发环境

Nios II IDE GNU GCC工具链

IP

MegaCore

Nios II是什么?

DA Lab

Altera’s 第二代软核32位RISC微处理器

DA Lab

SOPC设计技术

SOPC设计技术

SOPC系统架构与系统生成

杭州电子科技大学电子信息学院 系统集成技术研究所

问题提出: 降低成本、系统复杂度和功耗

I/O CPU I/O

I/O I/O I/O

DA Lab

Flash

SDRAM

I/O

FPGA

CPU DSP

DSP

解决方案:用可编程逻辑替代外扩器件

Write

Data In (32)

Data Out (32)

ROM

(with Monitor)

General Purpose Timer

UART Periodic Timer

Reconfig PIO

杭州康芯SOPC实验开发系统说明

杭州康芯SOPC实验开发系统说明(型号:GW48-PK2S)1、关于ASIC、CPLD、sopc、FPGAASIC(Application Specific Intergrated Circuits)即专用集成电路,是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

目前用CPLD(复杂可编程逻辑器件)和FPGA(现场可编程逻辑阵列)来进行ASIC设计是最为流行的方式之一,它们的共性是都具有用户现场可编程特性,都支持边界扫描技术,但两者在集成度、速度以及编程方式上具有各自的特点。

ASIC的特点是面向特定用户的需求,品种多、批量少,要求设计和生产周期短,它作为集成电路技术与特定用户的整机或系统技术紧密结合的产物,与通用集成电路相比具有体积更小、重量更轻、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

在二○世纪九十年度末,可编程逻辑器件(PLD)的复杂度已经能够在单个可编程器件内实现整个系统。

完整的单芯片系统(SOC)概念是指在一个芯片中实现用户定义的系统,它通常暗指包括片内存储器和外设的微处理器。

最初宣称真正的SOC――或可编程单芯片系统(SOPC)――能够提供基于PLD的处理器。

在2000年,Altera发布了Nios处理器,这是Altera Excalibur嵌入处理器计划中第一个产品,它成为业界第一款为可编程逻辑优化的可配置处理器。

本文阐述开发Nios处理器设计环境的过程和涉及的决策,以及它如何演化为一种SOPC工具。

Altera很清楚地意识到,如果我们把可编程逻辑的固有的优势集成到嵌入处理器的开发流程中,我们就会拥有非常成功的产品。

基于PLD的处理器恰恰具有应用所需的特性。

一旦定义了处理器之后,设计者就“具备”了体系结构,可放心使用。

因为PLD和嵌入处理器随即就生效了,可以马上开始设计软件原型。

CPU周边的专用硬件逻辑可以慢慢地集成进去,在每个阶段软件都能够进行测试,解决遇到的问题。

sopc开发流程

SOPC开发流程

一、硬件设计阶段

1.确定系统需求

(1)定义系统功能和性能要求

(2)确定硬件接口和功能模块

2.进行系统架构设计

(1)划分系统模块

(2)设计模块之间的通信接口

二、软件编程阶段

1.确定软件需求

(1)定义软件功能和算法

(2)确定软件与硬件的接口规范

2.进行软件编程

(1)编写软件程序

(2)测试软件功能和稳定性

三、系统集成阶段

1.硬件与软件集成

(1)将硬件和软件进行集成

(2)确保硬件与软件协同工作正常2.进行系统调试

(1)调试系统功能和性能

(2)优化系统性能和稳定性

四、验证和测试阶段

1.确认系统功能

(1)验证系统功能是否符合需求(2)进行功能性测试

2.进行性能测试

(1)测试系统响应速度和资源利用率(2)确保系统性能达标

五、部署和发布阶段

1.准备部署环境

(1)确定部署硬件平台和软件环境(2)进行部署准备工作

2.系统部署

(1)将系统部署到目标平台

(2)部署后的系统功能测试

六、运行和维护阶段

1.系统运行

(1)系统投入运行

(2)监控系统运行状态

2.系统维护

(1)定期维护系统

(2)处理系统运行中的问题

以上是SOPC开发流程的详细步骤,确保系统开发按照规范进行,达到预期效果。

第5章SOPC技术

图5-7Nios II 存储器和I/O结构

1.指令与数据总线 NiosⅡ结构支持分离的指令和数据总线,属于哈佛 结构。指令和数据总线都作为Avalon主端口实现,遵从 Avalon接口规范。主数据端口连接存储器和外设,指令 主端口仅连接存储器构件。 (1)小端对齐的存储器组织方式 NiosⅡ的存储器问采用小端对齐的方式,在存储器 中,字和半字最高有效位字节存储在较高地址单元中。 (2)存储器与外设访问 NiosⅡ结构提供映射为存储器的I/O访问。数据存储器 和外设都被映射到数据主端口的地址空间。存储器系统 中处理器数据总线低8位分别连接存储器数据线7-0。

(3)指令主端口 NiosⅡ指令总线作为32位Avalon主端口来实现,通 过Avalon交换架构连接到指令存储器的Avalon主端口。 指令主端口只执行一个功能:对处理器将要执行的指令 进行取指。指令主端口是具有流水线属性的Avalon主端 口。它依赖Avalon交换结构中的动态总线对齐逻辑始终 能接收32位数据。NiosⅡ结构支持片内高速缓存还支持 紧耦合存储器,对紧耦合存储器的访问能实现低延迟。 注意:指令主端口不执行任何写操作。动态总线对齐逻 辑不管目标存储器的宽度如何,每次取指都会返回一个 完整的指令字,因而程序员不需要知道NiosⅡ处理器系 统中的存储器宽度。片内高速缓存,用于改善访问较慢 存储器时的平均指令取指性能

Nios II提供3种核不同的内,以满足系统对不同性能 和成本的需求,包括快速内核Nios II/f(性能最优,在 StratixⅡ中,性能超过200DMIPS,仅占用1800个LE)、 标准内核Nios II/s(平衡性能和尺寸)和经济内核Nios II/e(占用逻辑单元最少)。 3种内核的二进制代码完全兼容,具有灵活的性能,当 CPU内核改变时,无须改变软件。

第5讲SOPCBuilder使用简介

System on Chip

片上系统

与基于ASIC的SOC相比,SOPC具有更多的特点与吸

引力:

开发软件成本低 硬件实现风险低

产品上市效率高

产品设计成本低

系统结构可重构及硬件可升级

5.1.2 SOPC Builder 简介 SOPC Builder 是Altera公司推出的一种可加快在 PLD内实现嵌入式处理器相关设计的工具。它是一个 革命性的系统级开发工具,旨在提高设计者的效率。

利用图形用户界面,用户可以快速方便地定义和连

接复杂的系统。如图5.1所示,用户可从左边的库中添加 所需的部件,然后在右边的表中配置它们。

图5.1 SOPC Builder的图形用户界面

2. 自动生成和集成软件与硬件 SOPC Builder会生成每个硬件部件以及连接部件的片 内总线结构,仲裁和中断逻辑。它也会产生系统可仿真的 RTL描述以及为特定硬件配置设计的测试平台,能够把硬 件系统综合到单个网表中。 另外,SOPC Builder还能够生 成C和汇编头文件,这些头文件定义了存储器映射、中断 优先级和每个外设寄存器空间的数据结构。这样的自动生 成过程可以帮助软件设计者处理硬件潜在的变化性。如果 硬件改变了,SOPC Builder会自动更新这些头文件。SOPC Builder也会为系统中现有的每个外设生成定制的C和汇编 函数库。例如,如果系统包括一个UART,SOPC Builder 就会访问UART的寄存器并定义一个C结构,生成通过 UART发送和接收数据的C和汇编例程。

SOPC Builder GUI引导用户完成两部分的配置:部件 配置和系统配置。部件配置需要汇总参数,Class PTF文件 标准包括了为这一要求定义GUI的格式。当需要时, SOPC Builder读取该格式,产生相应的部件向导 (Component Wizard),收集所需的用户数据。然后SOPC Builder把收集的参数值存放在System PTF文件中。系统配 置是指把用户提供的有关处理器的配置、外设连接等数据 写入System PTF中。 当这两部分配置都完成后,SOPC Builder进入到生成 阶段,生成设计的输出文件。SOPC Builder查阅每个Class PTF文件,允许相关的部件生成程序,它们会正确地输出 特定系统配置的硬件和/或软件文件。

第四讲 SOPC系统开发技术

PCB

Co Processor

CPU

Flash Ram

UART

FPGA Co SOPC Processor IP集成

Codec DMA Con. LCD Con.

Flash Ram

UART

Codec DMA Con.

CPU

LCD Con.

FPGA

此方案适合于系统的预研初期,投资小、风险小,可以快 速构建原型系统,加速产品上市,提高市场获益。

4.3 SOPC系统设计示例

4.3.2 Nios II软件设计流程

4.3 SOPC系统设计示例

4.3.2 Nios II软件设计流程

4.3 SOPC系统设计示例

4.3.2 Nios II软件设计流程

4.3 SOPC系统设计示例

4.3.2 Nios II软件设计流程

4.3 SOPC系统设计示例

3.降低系统成本

三、 SOPC系统设计示例

4.3.1 Nios II硬件系统设计流程

4.3 SOPC系统设计示例

4.3.1 Nios II硬件系统设计流程

4.3 SOPC系统设计示例

4.3.1 Nios II硬件系统设计流程

4.3 SOPC系统设计示例

4.3.1 Nios II硬件系统设计流程

4.4 SOPC系统接口设计

4.4.2 用户自定义指令设计

4.4 SOPC系统接口设计

4.4.3 IDE Flash编程下载

4.4 SOPC系统接口设计

4.4.3 IDE Flash编程下载

4.4 SOPC系统接口设计

4.4.3 IDE Flash编程下载

4.4 SOPC系统接口设计

4.4.3 IDE Flash编程下载

SOPC开发流程及开发平台简介

案例二:智能门禁系统的SOPC开发

要点一

总结词

要点二

详细描述

智能门禁系统是SOPC开发的另一个应用领域,通过集成微 处理器、读卡器、显示屏等模块,实现门禁的智能化管理 。

智能门禁系统SOPC开发同样涉及硬件设计、逻辑设计、 系统集成等多个环节。在硬件设计方面,需要选择合适的 读卡器、显示屏等器件,并设计合理的电路板布局和布线 。在逻辑设计方面,需要编写门禁控制程序和算法,实现 门禁的智能化管理。在系统集成方面,需要将各个模块进 行整合,并进行测试和调试,确保系统的稳定性和可靠性 。

IP核

可重用的硬件模块,用于加速SOPC系统的开发,如处理器核、存储器控制器等。

硬件描述语言

用于描述硬件逻辑的编程语言,如VHDL和Verilog。

软件开发平台

嵌入式操作系统

提供多任务管理和系统资源 管理功能,如Linux、 VxWorks等。

1

开发工具

用于编写、编译和调试应用 程序的软件工具,如Eclipse

IP核

用于设计可复用的硬件模块,如CPU、DSP、GPU等。IP核可以由第三方提供,也可以 自己开发。

软件开发工具

编译器

01

调试器

பைடு நூலகம்02

03

集成开发环境(IDE)

用于将高级语言编写的程序编译 成机器码,常见的编译器有GCC、 Clang等。

用于调试程序,常见的调试器有 GDB、JTAG等。

用于编写、编译、调试程序,常 见的IDE有Eclipse、Visual Studio等。

通信领域

信号处理

SOPC技术在通信领域广泛应用于信号处理,如调制解调、信道编解码等。

高速串行接口

SOPC技术可以实现高速串行接口,如PCI Express、Serial RapidIO等,用于高速数据传输。

sopc的开发流程

sopc的开发流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!SOPC(System-on-a-Programmable-Chip)的开发流程一般包括以下步骤:1. 系统需求分析:确定系统的功能和性能要求,包括处理器类型、外设需求、接口标准等。

SOPC历程文档

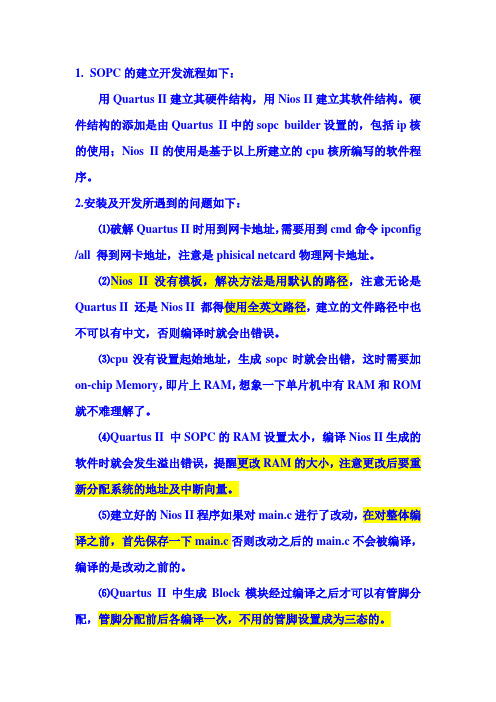

1.SOPC的建立开发流程如下:用Quartus II建立其硬件结构,用Nios II建立其软件结构。

硬件结构的添加是由Quartus II中的sopc builder设置的,包括ip核的使用;Nios II的使用是基于以上所建立的cpu核所编写的软件程序。

2.安装及开发所遇到的问题如下:⑴破解Quartus II时用到网卡地址,需要用到cmd命令ipconfig /all 得到网卡地址,注意是phisical netcard物理网卡地址。

⑵Nios II 没有模板,解决方法是用默认的路径,注意无论是Quartus II 还是Nios II 都得使用全英文路径,建立的文件路径中也不可以有中文,否则编译时就会出错误。

⑶cpu没有设置起始地址,生成sopc时就会出错,这时需要加on-chip Memory,即片上RAM,想象一下单片机中有RAM和ROM 就不难理解了。

⑷Quartus II 中SOPC的RAM设置太小,编译Nios II生成的软件时就会发生溢出错误,提醒更改RAM的大小,注意更改后要重新分配系统的地址及中断向量。

⑸建立好的Nios II程序如果对main.c进行了改动,在对整体编译之前,首先保存一下main.c否则改动之后的main.c不会被编译,编译的是改动之前的。

⑹Quartus II中生成Block模块经过编译之后才可以有管脚分配,管脚分配前后各编译一次,不用的管脚设置成为三态的。

⑺如果SPOC中生成的并行总线名称是LED,则NIOSII中对总线的操作为:IOWR_AL TERA_A V ALON_PIO_DA TA(LED_BASE,led);后面的小写的led是定义的变量,这句话的意思是将所定义变量led 发送到并行端口LED那去。

如果SPOC中生成的并行总线名称是pio_0,则NIOSII中对总线的操作为:IOWR_AL TERA_A V ALON_PIO_DA TA(PIO_0_BASE,led);这可能是由NIOSII的语法所决定的,大写了SOPC中的PIO,而BASE表示基址,可以到SOPC中看一下,末地址是用END表示的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一

一、实验目的

1.掌握用 Quartus II 开发 SOPC 的基本流程。

2.掌握用 SOPC Builder 进行 Nios II CPU 开发的基本流程。

3.掌握整个 Nios II 集成开发环境。

二、实验环境

1.SOPC-NIOSII SOPC 开发平台一套。

2.USB下载电缆一条。

三、实验原理

本实验的目的主要是对 SOPC 有一个基本的认识,了解整个实验过程,并掌握整个 Nios II 集成开发环境的应用。

(1) 在 Quartus II中新建一个工程。

(2) 在 SOPC Builder中根据自己的需要加入各种参数值。

(3) 利用 SOPC Builder 产生 Quartus II 能够识别的文件。

(4) 在(1)中新建的工程中加入(3)中生成的文件。

(5) 加入输入、输出以及双向端口,并根据需要对其命名。

(6) 对(5)中命名的输入、输出核双向端口根据选定的 FPGA 进行引脚分配。

(7) 编译工程。

(8) 下载编辑代码到 FPGA。

(9) 利用 Nios II 新建另一个工程。

(10) 根据(2)中的资源,编写项目需要的代码。

(11) 编译、下载并调试,查看运行结果,直到正确。

(12) 如果需要,将(11)中生成的代码下载到代码 Flash 中。

四、实验内容

为了熟悉 SOPC 的基本开发流程,本实验要完成的任务就是设计一个最简单的系统,系统中包括 Nios II CPU、作为标准输入/输出的 JTAG UART 以及存储执行代码SRAM。

通过 SOPC Builder 对系统进行编译,然后通过 Quartus II 对

系统进行二次编译,并把产生的 FPGA 配置文件通过 USB 下载电缆下载到实验箱上,这时便完成了本实验中的硬件开发。

接下来的工作是软件协同开发——在Nios II IDE 中编写一个最简单的 C 代码,对其编译后,通过 USB 下载电缆下载到 FPGA 中执行,执行的结果就是在 Nios II 的 Console 窗口打印一条信息——“Hello Nios II!”。

五、实验步骤

1.在【开始】菜单中,打开 Quartus II 。

2.点击 File 菜单中的 New Project Wizard,新建一个工程。

以D:\EXP2文件夹 (文件夹不能含有空格)为例,工程名称为EXP2,如图 1-1 所示。

图 1-1

3.点击【Next】按钮,进入到添加工程文件步骤。

由于工程全部为空,所以也没有文件加入,因此直接点击【Next】进入到选择芯片步骤(在 Family 下拉菜单中选择 Cyclone III;在 Filters 中的 Pin Count 下拉菜单中选择324;在Speed grade下拉菜单中选择8,然后在Available devices 中选择EP3C25F324C8),如图 1-2所示。

图 1-2

4.FPGA 选好后,点击【Next】,进入到选择其它 EDA 工具窗口。

本实验中需要

任何 EDA 工具,所以直接点击【Next】按钮,然后再点击【Finish】按钮,完成新工程的创建,如图 1-3 所示。

图 1-3

5.点击 File 菜单中的 New,新建一个工程文件。

本实验中需要创建的是一个原理图工程文件。

如图 1-4 所示。

图 1-4 新建的原理图工程文件界面

6.点击 Tools 菜单中的 SOPC Builder(也可点击工具栏图标),启动 SOPC Builder 软件,创建一个名为 EXP2的系统,如图 1-5 所示。

图 1-5

7.点击【OK】按钮,开始创建系统。

图1-6

8.点击左侧的Nios II Processor,出现一界面,选择Nios II/e,接下来每步

点击【Next】按钮直到Finish,如下图。

图1-7

图1-8

图1-9

9.添加作为标准输入/输出的设备,本实验中用 JTAG UART 来作为输入输出终端。

在左侧System Contents栏搜索下输入Jtag,单击选中 System Contents 列表中的 Communication 类中的 JTAG UART,则会出现如下图所示界面,点击Next 按钮直【Finish】,即可把 JTAG UART 添加到新建系统中。

10.在左侧System Contents栏搜索下输入ON -CHIP,单击选中 System Contents 列表中的 Communication 类中的 ON -CHIP Memory ,则会出现如下图所示界面,

设置参数如图,点击【Finish】按钮,即可把ON- CHIP 添加到新建系统中。

11.双击下图中的CPU,跳出界面如下图,选择参数如图,单击Next按钮直Finish。

12. SOPC Builder 底部窗口会出现一些红色错误信息,单击System 选择Auto-Assign Base Addresses,当软件提示基地址冲突的提示时,可点击System 菜单下的 Auto-Assign Base Address ,重新分配基地址。

13.双击clk-0,将其改为clk- 50。

14.右键单击加入的 Nios II CPU,选择 Rename,将其命名为 cpu。

15.步骤同上

16.单击窗口下方的【Generate】单击save Changes。

17.系统编译结束后,会出现下图所示的提示界面。

17.点击【Exit】按钮退出 SOPC Builder 窗口。

重新返回到 Quartus II 窗口,在新建的原理图文件空白区域双击鼠标左键,在弹出的 Symbol 对话框中,选择

Libraries 窗口下面 Project 文件夹中的 EXP2。

18.点击【OK 】按钮,添加 SOPC Builder 产生的 EXP2系统到之前创建的工程文件中。

19.加入输入端口。

在工程文件的空白处双击鼠标左键,并在弹出的 Symbol 对话框右下侧 Name 栏中键入“input”,点击【OK 】按钮后,在工程文件空白处单击 2 次鼠标左键,即可加入 2 个input 端口,然后再单击鼠标右键,选择 Cancel ,取消加入符号的操作。

20.点击 File 菜单下的 Save (也可直接点击工具栏上的存盘按钮 ),此时 会弹出如图所示的对话框,直接点击【保存】即可。

21.编译工程。

点击 Processing 菜单下面的 Start Compilation (也可直接 点击工具栏上的编译按钮 ),开始编译当前工程。

22.步骤 21编译工程的目的是为了检查工程有无错误,如果编译无误的话, 边可以进行端口引脚分配了。

根据要求硬件连接,分配端口到对应的 FPGA 引

脚。

点击 Assignments 菜单下面的 Pin Planner (也可直接点击工具栏上的引脚分 配按钮 ),进入到引脚分配窗口,如图所示。

23.将clk 和rst 输入端分别分配为A10和U9,如图所示。

所示。

25.到此为止硬件开发工作就全部结束,剩下的工作就是软件了。

在【开始】 菜单中,启动 Nios II ,如图所示。

26.创建新的软件工程。

关闭 Nios II 欢迎界面后,点击 file 菜单下的New 子菜单中的 Project ,会出现图所示工程类型选择窗口。

27.直接选择 C/C++ Application 后,点击【Next】按钮,进入到创建工程对话框。

选中以下各模块:

✧ Name:Hello_Nios_II

✧ Use Default Lacation:选中

✧ SOPC Builder System: E:\Exp1-Hello_Nios_II\myCPU.ptf

✧ Select Project Template:Blank Project

如下图所示。

28.此时的工程是一个空的工程, 没有用户文件, 所以必须创建一个新的文件, 来编写属于自己的程序代码。

右键点击 C/C++ Projects 窗口中 Hello_Nios_II 工 程, 点击快捷菜单中 New/File , 如图。

弹出图所示对话框后, 在 File name 中键入文件名 main.c ,然后点击【Finish 】按钮,此时工程中会出现该文件。

29.存盘后, 点击 Project 菜单下的 Build All ,编译文件,如图所示。

缆插入到实验箱系统板上的 JTAG 接口,开启实验箱电源。

31.在 Quartus II 中通过 USB 下载电缆将 Hello_Nios_II.sof 文件通过 JTAG 接口下载到 FPGA 中。

32.待数据配置结束后,在返回到 Nios II IDE 窗口,点击 Nios II IDE 中 Run 菜单下的 Run ,会出现图所示的设置 Nios II 硬件窗口。

图所示。

验箱电源,拔出 USB 下载电缆。