sopc实验指导书(1)

SOPC实验指导书

SOPC实验指导书电信学院实验中心目录第一章EL-SOPC4000实验系统的资源介绍 (1)一、系统功能概述 (1)二、系统硬件资源 (2)三、特别说明 (11)第二章数字可编程设计实验 (12)实验一组合逻辑3-8译码器的设计 (12)第三章基于NIOS的软核设计实验 (23)实验一 Nios软核的设计 (23)实验二外设模块的设计 (27)实验三 SOPC应用系统的生成 (40)实验四 Nios II软核验证以及Nios II IDE软件的介绍 (46)实验五 SOPC系统的PIO验证 (52)实验六基于NIOS的交通灯实验 (55)实验七 7段数码管显示实验 (59)实验八按键及拨码开关实验 (61)实验九 16×16 LED点阵实验 (62)实验十 UART与PC机通信实验 (64)第一章EL-SOPC4000实验系统的资源介绍一、系统功能概述EL-SOPC4000实验箱是集EDA 和SOPC 开发为一体的综合性实验箱,它不仅可以独立完成各种EDA 设计,也可以完成多种SOPC开发。

主CPU适配器E-PLAY-SOPC配合EL-SOPC4000底板,可完成各种基本的EDA实验。

在实验板上有丰富的外围扩展资源,有常用的按键,拨码开关,LED灯,蜂鸣器,交通灯,16x16点阵,数码管,4x4矩阵键盘,AD/DA,CAN功能单元,RS232,RS485,可调时钟输出。

实验板上还集成了一个8寸的VGA接口的液晶屏,可完成视频图像的显示。

由于CPU 适配器E-PLAY-SOPC本身具有E_PLAY接口,只需提供电源即可独立完成功能测试,也可控制用户开发的E_PLAY接口模块。

由于EL-SOPC4000底板加入了两路E_LAB外扩接口,可以配合公司现有的多种E_LAB模块,来完成大学生毕业设计、电子设计竞赛、及创新设计,同时该系统也是从事教学及科研的广大教师和工程师们的理想开发工具,具有极高的灵活性,开放性和可开发性。

SOPC试验指导

1.实验目的 (1)2.实验内容 (1)3.预备知识 (1)4.实验设备 (1)5.基础知识 (1)(1)SOPC的基本概念 (1)(2)NIOS II简介 (1)(3)Avalon总线简介 (1)(4)开发工具简介 (2)6.实验过程 (3)(1)Quartus II的应用—跑马灯工程开发流程 (3)设计输入_控制模块 (4)编译工程 (15)工程仿真 (17)设计输入_分频模块 (20)锁定引脚 (22)下载配置文件 (24)(2)创建基于NIOS II的SOPC硬件系统 (26)创建系统模块 (26)编译工程 (34)锁定引脚 (34)(3)开发基于NIOS II的软件工程 (34)创建工程 (34)编译工程 (39)工程仿真 (39)SOPC实验指导1.实验目的(1)了解SOPC设计技术(2)了解基于软核的嵌入式系统设计的原理和技术(3)学习并掌握一种系统定制的方法2.实验内容(1) 创建并完成一个基本的跑马灯工程,熟悉Altera综合开发平台Quartus II 的应用(2) 利用SOPC Builder创建基于NIOS II的SOPC硬件系统(3) 利用NIOS II IDE开发应用程序,利用软件实现控制一个LED灯闪烁3.预备知识(1)C语言基础、VHDL或Verilog语言基础(2)程序调试的基础和方法4.实验设备(1)硬件:NIOS II Evaluation Kit(基于Cyclone EP1C12)、PC机;(2)软件:操作系统(Windows98/2000/XP)、Quartus II、NIOS II IDE。

5.基础知识(1)SOPC的基本概念z SOPC即片上可编程系统,这种技术基于FPGA芯片,将处理器、存储器、I/O口等系统设计需要的模块集成到一起,完成整个系统的主要逻辑功能,具有设计灵活,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

(2)NIOS II简介z在很多对速度的要求不是很高的低端应用,Altera将一个软核放入PLD,这 个软核就是NIOS,它只占芯片内部很少的一部分逻辑单元,成本很低。

SOPC实验指导书(EP2C20Q240C8)

目录目录 (1)第一章系统的硬件单元及使用说明 (2)一、本实验箱的结构特点: (2)二、各模块电路说明: (3)1、数码管显示模块 (3)2、AD 转换模块 (3)3、DA 转换模块 (4)4、以太网模块 (4)6、VGA接口模块 (5)7、PS/2接口模块 (6)8、串行接口模块 (6)9、开关量输入输出模块 (7)10、按键模块 (7)11、LED 灯指示模块 (8)12、音频接口模块 (8)13、TFT液晶接口模块 (9)14、USB接口电路 (9)第二章QUARTUS II和NIOS II 软件的使用方法 (10)一、Q UARTUS II软件的使用方法 (10)二、SOPC B UILDER /N IOS II IDE软件使用方法 (19)第三章VHDL基本程序设计实验 (27)实验一组合逻辑半加器的设计 (27)实验二使用VHDL设计组合逻辑全加器 (34)实验三带进位输入的8位加法器 (40)实验四全减器 (43)实验五四位向量加法/减法器 (46)实验六组合逻辑3-8译码器的设计 (48)实验七数据比较器 (51)实验八多路数据选择器 (53)实验九编码器 (56)实验十计数器 (59)实验十一7段数码管控制接口 (62)实验十二16*16点阵设计 (64)实验十三MOORE机 (68)实验十四MEALY机 (71)实验十五D/A接口 (74)实验十六A/D接口 (76)第一章系统的硬件单元及使用说明一、本实验箱的结构特点:1、系统构成SOPC综合实验系统开发实验平台采用ALTERA Cyclone II EP2C20处理器,集众多功能于一体,采用全新的"主控制板+……+核心板+平台主板"自由组合式结构。

根据实验研发需求,可实现基于ALTERA、XILINX、ACTEL、Lattice等厂家的软核/硬核处理器相结合的嵌入式系统设计。

本实验系统实验平台功能强大,硬件接口丰富,平台嵌入式软件除支持C、C++语言开发之外,还支持uC/OS II、uClinux嵌入式操作系统。

SOPC实验指导书 Ver 2[1].5

![SOPC实验指导书 Ver 2[1].5](https://img.taocdn.com/s3/m/183a71ec4afe04a1b071de72.png)

目录目录目录 (I)第一章绪论与引导性知识 (1)1.1 SOC技术的发展 (1)1.2 SOPC及其技术 (1)1.2.1 基于FPGA的嵌入IP软核的SOPC系统 (2)1.2.2 基于HardCopy技术的SOPC系统 (2)1.3 认识SOPC开发环境:Altium Designer Summer 08 (6)第二章设计案例 (9)2.1 一个简单的FPGA设计案例 (9)2.1.1 实验目的 (9)2.1.2 实验步骤 (9)2.2 VHDL设计时钟分频器 (13)2.2.1 实验目的 (13)2.2.2 实验原理 (13)2.2.3 实验步骤 (13)2.3 基于SOPC的51内核最小系统设计 (17)2.3.1 实验目的 (17)2.3.2 实验原理 (17)2.3.3 实验步骤 (18)2.4 基于SOPC的音频混响系统 (24)2.4.1 实验目的 (24)2.4.2 实验原理 (24)2.4.3 实验步骤 (25)第三章设计性实验 (48)3.1 基于SOPC技术的32位处理器最小系统实验 (48)3.1.1 实验目的 (48)3.1.2 预习要求 (48)3.1.3 实验器材 (48)3.1.4 实验内容以及步骤 (48)3.1.5 报告要求 (49)3.2 基于SOPC技术的视频采集回显实验 (50)3.2.1 实验目的 (50)3.2.2 预习要求 (50)3.2.3 实验器材 (50)3.2.4 实验内容以及步骤 (50)3.2.5 报告要求 (52)第一章绪论与引导性知识1.1 SOC技术的发展20世纪90年代后期,嵌入式系统设计从以嵌入式微处理器/DSP为核心的“集成电路”设计不断的向“集成系统”级设计发展,提出了SOC(System on a Chip,片上系统)的基本概念。

目前嵌入式系统进入了单片系统SOC的设计阶段,并逐步进入实用化、规范化阶段,集成电路已进入SOC的设计流程。

SOPC技术LED流水灯设计

Sopc_LED实验指导一.实验目的:1.掌握NIOS II软核的定制流程。

2.掌握NIOS II的开发流程。

3.熟识NIOS II IDE 开发环境的使用。

4.掌握基本的软件的调试方法。

5.掌握通过寄存器形式对硬件进行控制,可以更透彻地看清NIOS II 开发过程。

二.实验内容:1.PIO 模块的构建。

2.软件编程,通过寄存器形式对硬件进行控制。

3.下载程序并硬件调试。

4. 扩展实验:程序功能通过SOPC建立的软核来运行程序功能:LED 显示控制。

通过PIO 直接控制8 个LED 产生流水灯效果三.实验简介:这一节,我将给大家了解第一个与硬件有关的程序,虽然内容简单,却极具代表性。

我将采用一种寄存器的操作方案,让大家感受到开发NIOS跟单片机一样的简单,看透NIOS II开发的本质,尽量避免使用NIOS II IDE提供的API,这样做有很多好处。

首先,有单片机开发经验的人应熟悉这种操作方案,其次,它是硬件试验部分的第一课,通过这个简单的实验,可以让你对单片机的操作有一个感官上的了解,可以说意义不同寻常。

这一节,我也通过LED 实验来带大家进入NIOS II 的开发世界,感受NIOS 的魅力所在,下面我们开始吧。

四.实验内容:1.硬件开发第一步,我们要在软核中加入PIO 模块。

打开我们上一次建的Quartus 工程,如下图红圈所示(如果你没保留上次的工程,需要按照上次指导书重新再做一个下面的。

)双击上图的hello_word后进入了SOPC BUILDER界面,如下图所示点击下图所示红圈处PIO(Parallel I/O)点击后,如下图所示,红圈1处是你需要的PIO口的宽度,即你需要几个IO口,这里面我设置为8,即我要控制8个LED,红圈2是选择输出方式,我选择为输出(Output)。

接下来,点击Finish,完成PIO模块的构建,然后将其改名为LED,如下图所示接下来,需要自动分配一下基地址,上一次已经讲过,如下图所示接下来,双击cpu,看下图红圈的地址为下图的。

SOPC综合课程设计指导书

第一章EDA技术综合应用设计基础1.1 EDA技术综合应用的形式随着EDA技术的深入发展和EDA技术软硬件性能价格比的不断提高,EDA技术的应用将向广度和深度两个方面发展。

根据利用EDA技术所开发的产品的最终主要硬件构成来分,作者认为,EDA技术的应用发展将表现为如下几种形式:(1) CPLD/FPGA系统:使用EDA技术开发CPLD/FPGA,使自行开发的CPLD/FPGA作为电子系统、控制系统、信息处理系统的主体。

(2) ―CPLD/FPGA+MCU‖系统:综合应用EDA技术与单片机技术,将自行开发的―CPLD/FPGA+MCU‖作为电子系统、控制系统、信息处理系统的主体。

(3) ―CPLD/FPGA+专用DSP处理器‖系统:将EDA技术与DSP专用处理器配合使用,用―CPLD/FPGA+专用DSP处理器‖构成一个数字信号处理系统的整体。

(4) 基于FPGA实现的现代DSP系统:基于SOPC(a System on a Programmable Chip)技术、EDA技术与FPGA技术实现方式的现代DSP系统。

(5) 基于FPGA实现的SOC片上系统:使用超大规模的FPGA实现的,内含1个或数个嵌入式CPU或DSP,能够实现复杂系统功能的单一芯片系统。

(6) 基于FPGA实现的嵌入式系统:使用CPLD/FPGA实现的,内含嵌入式处理器,能满足对象系统要求的特定功能的,能够嵌入到宿主系统的专用计算机应用系统。

1.2 EDA技术综合应用的设计方法与建模1.2.1 分析方法传统的电路设计方法都是自底向上进行设计的,也就是首先确定可用的元器件,然后根据这些器件进行逻辑设计,完成各模块后进行连接,最后形成系统。

在基于EDA技术的系统设计的最重要环节——在系统的基本功能或行为级上对设计的产品进行描述和定义时,我们采用自顶向下分析,自底向上设计的方法。

所谓―自顶向下分析‖,就是指将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大,则还需将子系统进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子系统关系合理,并便于逻辑电路级的设计和实现为止。

SOPC实验讲稿

2、实验内容

本实验通过使用 NiosII SDK Shell 、 QuartusII 和 SOPC Builder 共同建立

本开发板的目“ UP_AR2000_board ”。 然后新建工程“ USB_test ”,使用

SOPC Builder 定制一个标准的 NiosII 系统,该系统是“ UP_AR2000_board ” 为目标板建立的。从而完成硬件开发。用QuartusII 分配管脚,编译、生成 sof 文件。然后,使用 NiosII IDE 移植 uClinux 操作系统、 编译、 烧写。 建立根 文件系统编译、 烧写。 建立应用程序工程, 编译生成 .exe 文件。把 exe 文 件拷贝到根文件系统中的 bin 文件夹下。 再重新编译根文件系统, 烧写。 最 后 sof 文件。 运行通过超级终端我们就可以运行位于 bin 文件夹下的应用程 序命令了。

2在sopcbuilder上完成niosii硬件系统配置然后完成硬件系统生成3在quartusii上完成硬件引脚的添加与硬件锁定综合3在quartusii上完成硬件引脚的添加与硬件锁定综合4在niosiiide上完成中建立的linux内核工程和linux根文件系统工程然后新建应用工程5添加应用程序到应用工程

仿真波形图

4、实验要求 (1)记录调试与验证的结果 (2 )记录实验过程中出现的问题及解决办法

(3) 实验结束,保持实验室整洁

实验二

1、实验目的

LED实验

(1)学习使用 SOPC Builder 定制 一个最小NiosII 硬件系统的设计。

(2)学习使用 NiosII IDE 软件完成应用程序开发。

(6)将实验箱的JTAG与主机连接好,在Quartus II完成 .sof文件编程, 在NiosII上运行硬件调试,观察实验箱上LED的显示 (7)对 makefile 进行修改, 保存。指定 Rules.mak 的路径。改为: TOPDIR=E:\example\cheng\example\USB_test\software\Linux_app1

《SOPC设计与应用技术》研究性实践教学指导书-学生

东华理工大学自编教材2011年6月《SOPC设计与应用技术》研究性实践教学指导书编写黄乡生东华理工大学机械与电子工程学院二○一一年六月随着电子技术的发展,特别是集成电路技术的发展,使电子电路逐步告别分立元件时代,向小型化、集成化方向发展,要开发拥有自主知识产权的硬件电路,就必须进行ASIC(Application Special Integrated Circuit 专用集成电路)、SOPC(System on Programmable Chip单片可编程系统)的设计,就必须使用和掌握现代EDA(Electronic Design Automation 电子设计自动化)技术,这是科学技术的发展对教学内容提出的新要求。

目前,“数字电子技术基础”知识仍然是数字电路和数字系统的基本设计方法。

为了适应新世纪人才培养的需要,紧跟新技术的发展,要求学生掌握数字系统设计的新方法,用现代EDA 技术解决传统的数字系统设计问题。

EDA技术对于高等学校工科电子类学生能力培养的重要性已经非常明确,但是如何合理安排教学内容,如何实施实践教学,使学生在有限的时间内尽快掌握EDA的基本方法,对于《EDA技术与应用》这门实践性非常强的课程来说是应该首先加以研究的重要问题。

基于上述考虑,我们提出“研究性实践”教学方法的理念,作为实践教学改革的一种尝试,这正是编写这本教材的出发点。

本教材完全摒弃了一般EDA教材先给出实验原理、方法、步骤,学生照搬教材内容、按部就班就可完成实验的编写套路。

《EDA技术与应用研究性实践教学指导书》分为基本研究方法实验、实验的综合设计与研究、课题研究与设计实现等三个部分。

三个部分既互相关联又相对独立是一个内容由浅入深、由易到难、逐层递进的有机整体。

前两个部分实验都有原理介绍或实例,然后给出实验或综合设计题目、要求但是不给出程序,最后均有思考题。

每个实践内容都要求学生预习,填写预习报告,由指导老师评分。

SOPC实验指导书

篇一:sopc实验指导书sopc实验3.1使用niosⅱ ide建立用户程序1.创建一个新的c/c++应用工程执行下面的步骤来创建一个新的c/c++应用工程:1. 启动niosⅱ ide。

选择【开始】??【程序】??【altera】??【quartusⅱ 5.0】??【nios ⅱ development kits 5.0】??【niosⅱ ide】启动niosⅱ ide。

也可以通过图1.1直接点击ⅱ ide。

按钮来启动nios图1 启动niosⅱ ide2.如果出现workspace launcher对话框,单击设置工作空间为quartusⅱ工程的文件夹,如图2所示,这样便于管理。

如果是第一次进入工作区,niosⅱ ide会先弹出一个欢迎界面,此时点击右上角的workbench图标,就可以进入niosⅱ ide编辑界面。

图2设置ide工作空间3.如图3所示,选择【file】??【new】??【c/c++ application】来打开新建c/c++工程向导,如图4所示。

图3打开新建c/c++工程向导1图4新建c/c++工程向导4.单击select target hardware右侧的按钮打开select target hardware窗口,选择led_nios2_system.ptf文件,即指向当前硬件设计系统,如图5所示。

图5选择硬件目标文件5.选择select project template列表中的hello_led。

name栏中自动更新为hello_led_0,确认选中use default location栏,如图6所示,单击完成工程创建。

2图6完成设置后的工程向导向导中的select project templates一栏中是已经设计好的软件工程,用户可以选择其中的一个,把它当作模板来创建自己的工程。

当然也可以选择blank project(空白工程),完全由用户写所有的代码。

本实验选取了hello_led工程,然后在此基础上进行适当的修改,一般情况下这比空白工程更加容易,也更方便。

SOPC实验指导书1

SOPC实验指导书钮文良韩玺编著北京联合大学信息学院2007年12月6日目录第1章SOPC实验系统介绍 (3)1.1 系统硬件平台设计 (3)1.2 系统软件实验开发 (7)1.3 SOPC系统实验介绍 (8)第2章SOPC基本概念与基本原理 (10)2.1 SOPC技术 (10)2.2 基于FPGA嵌入IP软核的SOPC系统 (11)2.3 SOPC设计 (13)第3章SOPC设计开发案例 (14)3.1 Nios控制LED实验 (14)3.2 构建比较复杂的Nios II系统实验 .................................. 错误!未定义书签。

3.3 SOPC下μC/OS II操作系统移植实验............................ 错误!未定义书签。

3.4 Nios II控制下的UART串行接口通信实验 .................. 错误!未定义书签。

3.5 底板8×8点阵LED图形实验 ......................................... 错误!未定义书签。

3.6 VGA&SVGA接口显示器彩条信号发生器实验............ 错误!未定义书签。

3.7 按键控制数码管计数器实验 ........................................... 错误!未定义书签。

3.8 信号发生器设计实验 ....................................................... 错误!未定义书签。

3.9 底板键盘控制SOPC实验板数码管实验 ....................... 错误!未定义书签。

3.10 4位按键控制下的LED、数码管SOPC计数实验...... 错误!未定义书签。

3.11 基于SOPC的128*64 LCD显示实验 .......................... 错误!未定义书签。

SOPCEDA实验指导书

EDA/SOPC实验指导书(含GW48-PK2 SOPC/DSP实验开发系统详细使用说明)广东工业大学目录第一章 Quartus II使用指南第一节基于Quartus II的设计过程第二节Quartus II设计输入2.1、建立一个新项目2.2、图形输入方式2.3、文本输入方式2.4、第三方EDA工具输入方式第三节Quartus II编译3.1指定器件3.2 引脚锁定3.3 开始编译3.4 编译报告3.5 延时分析第四节Quartus II仿真第五节Quartus II编程下载第二章 GW48 SOPC系统(GW48-PK2)使用说明第一节GW48教学实验系统原理与使用介绍一、GW48系统使用注意事项二、GW48系统主板结构与使用方法第二节实验电路结构图一、实验电路信号资源符号图说明二、各实验电路结构图特点与适用范围简述第三章用Verilog HDL设计数字电路【实验1】4选1多路选择器设计【实验2】8位硬件加法器设计【实验3】八位移位寄存器设计【实验4】移位相加8位硬件乘法器电路设计【实验5】任意模加法/减法计数器【实验6】六分频器的设计【实验7】交通灯控制系统【实验8】A/D采样控制电路设计第一章 Quartus II使用指南第一节基于Quartus II的设计过程使用Quartus II软件进行设计和开发的流程如图1.1所示,主要包括以下几个步骤:图1.1 Quartus II开发流程第二节Quartus II设计输入Quartus II软件的设计输入方法有很多种,具体如下:--Quartus II·原理图式图形设计输入·文本编辑--AHDL,VHDL,Verilog·内存编辑--Hex,Mif--第三方工具·EDIF·HDL·VQM--或采用一些别的方法去优化和提高输入的灵活性·混合设计格式·利用LPM和宏功能模块来加速设计输入Quartus II的编译器能够接受多种输入文件格式,也能输出多种文件格式。

济南大学 SOPC 综合实验系统 实验指导书

SOPC综合实验系统实验指导书济南大学控制学院责任编辑:济南大学信息学院电子信息中心目录目录 (1)第一章系统的硬件单元及使用说明 (4)一、本实验箱的结构特点 (4)1、系统构成 (4)2、创新设计应用领域 (4)3、适用专业范围 (5)二、各模块电路说明 (5)1、数码管显示模块 (5)2、AD 转换模块 (6)3、DA 转换模块 (6)4、以太网模块 (7)5、VGA接口模块 (7)6、PS/2接口模块 (8)7、串行接口模块 (8)8、开关量输入输出模块 (8)9、按键模块 (9)10、LED 灯指示模块 (10)11、音频接口模块 (10)12、TFT液晶接口模块 (11)13、USB接口电路 (11)第二章 QUARTUS II和NIOS II 软件的使用方法 (12)一、Q UARTUS II软件的使用方法 (12)二、SOPC B UILDER /N IOS II IDE软件使用方法 (21)第三章 VHDL基本程序设计实验 (29)实验一组合逻辑半加器的设计 (29)实验二使用VHDL设计组合逻辑全加器 (36)实验三带进位输入的8位加法器 (41)实验四全减器 (46)实验五四位向量加法/减法器 (50)实验六组合逻辑3-8译码器的设计 (53)实验七数据比较器 (57)实验八多路数据选择器 (60)实验九编码器 (64)实验十计数器 (69)实验十一7段数码管控制接口 (72)实验十二 16*16点阵设计 (76)实验十三 MOORE机 (83)实验十四 MEALY机 (87)实验十五 D/A接口 (91)实验十六 A/D接口 (94)实验十七动态数码管显示实验 (98)实验十八频率信号源实验 (102)第四章 SOPC系统基本实验 (109)实验一 Hello-Led流水灯实验 (109)实验二数码管显示实验 (117)实验三按键输入中断实验 (121)实验四定时计数器实验 (125)实验五串行口通信实验 (129)实验六存储器配置实验 (132)实验七4乘4键盘实验 (138)第五章 SOPC系统综合实验 (141)实验一高速DAC实验 (141)实验二DDS实验 (149)实验三高速ADC实验 (155)实验四静态数码管显示实验 (158)实验五VGA彩条显示实验 (160)实验六PS2键盘实验 (166)实验七USB数据读写实验 (171)实验八TFT真彩屏实验 (173)实验九SD卡实验 (176)实验十UC\OS-II操作系统移植实验 (181)实验十一 PS2鼠标控制实验 (188)实验十二音频接口实验 (191)实验十三百兆以太网实验 (199)实验十四四相步进电机实验 (208)实验十五 CAN总线实验 (211)第一章系统的硬件单元及使用说明一、本实验箱的结构特点1、系统构成SOPC综合实验系统开发实验平台采用ALTERA Cyclone III EP3C16处理器,集众多功能于一体,采用全新的“主控制板+……+核心板+平台主板”自由组合式结构。

SOPC实验手册

《SOPC技术与应用》实验指导书哈尔滨理工大学自动化学院电子信息科学与技术系2008年10月7日实验一 SOPC快速入门一、实验目的1、学习Quartus II、SOPC Builder、Nios II IDE的基本操作;2、初步了解SOPC的开发流程,基本掌握Nios II软核的定制流程;3、掌握Nios II软件的开发流程;掌握软件的基本调试方法。

二、实验设备硬件:PC机,GW48系列SOPC/EDA实验开发平台;软件:Quartus II 8.0,SOPC Builder 8.0,Nios II IDE 8.0。

三、实验内容建立可用于控制LED闪烁的简单Nios II处理器系统,具体包括:1、在Quartus II中建立一个工程;2、使用SOPC Builder建立并生成一个简单的基于Nios II的硬件系统;3、在Quartus II工程中编译基于Nios II的硬件系统并生成配置文件.sof;4、在Nios II IDE中建立对应硬件系统的用户C/C++工程,编写一简单用户程序,在Nios II IDE中编译程序生成可执行文件.elf;5、将配置文件.sof和可执行文件.elf都下载到FPGA进行调试运行。

四、实验原理控制LED灯闪烁的用户程序代码很小,可将其固化在片内ROM来执行。

变量、堆栈等空间使用片内RAM,不使用任何片外存储器。

整个系统的框图如图1所示。

从图1控制LED闪烁的系统框图可知,其它逻辑与Nios II系统一样可存在于FPGA中。

Nios II 系统可与其它片内逻辑相互作用,取决于整个系统的需要。

为了简单起见,本实验在FPGA内不包括其它逻辑。

图1 控制LED闪烁的系统框图五、实验步骤1、使用Quartus II建立工程2、使用SOPC Builder创建NiosII系统SOPC Builder设计过程不需要按固定顺序进行,本实验采用常用设计步骤。

读者可采用不同的顺序进行SOPC Builder设计。

EL-EMCU-I(SOPC)实验指导书

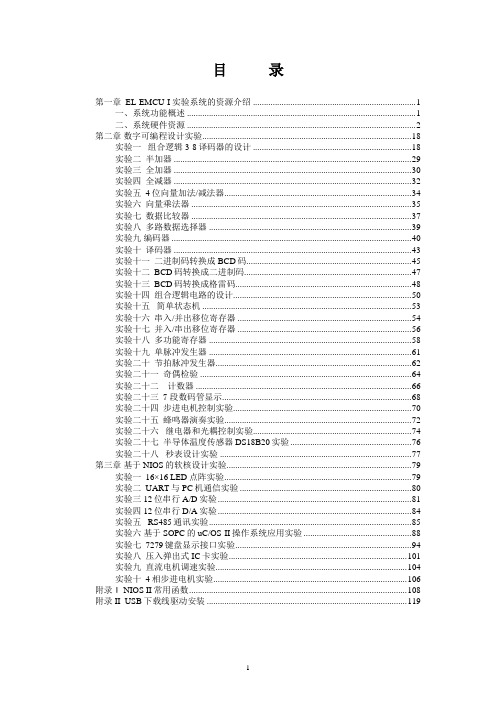

目录第一章 EL-EMCU-I实验系统的资源介绍 (1)一、系统功能概述 (1)二、系统硬件资源 (2)第二章数字可编程设计实验 (18)实验一组合逻辑3-8译码器的设计 (18)实验二半加器 (29)实验三全加器 (30)实验四全减器 (32)实验五 4位向量加法/减法器 (34)实验六向量乘法器 (35)实验七数据比较器 (37)实验八多路数据选择器 (39)实验九编码器 (40)实验十译码器 (43)实验十一二进制码转换成BCD码 (45)实验十二 BCD码转换成二进制码 (47)实验十三 BCD码转换成格雷码 (48)实验十四组合逻辑电路的设计 (50)实验十五简单状态机 (53)实验十六串入/并出移位寄存器 (54)实验十七并入/串出移位寄存器 (56)实验十八多功能寄存器 (58)实验十九单脉冲发生器 (61)实验二十节拍脉冲发生器 (62)实验二十一奇偶检验 (64)实验二十二计数器 (66)实验二十三 7段数码管显示 (68)实验二十四步进电机控制实验 (70)实验二十五蜂鸣器演奏实验 (72)实验二十六继电器和光耦控制实验 (74)实验二十七半导体温度传感器DS18B20实验 (76)实验二十八秒表设计实验 (77)第三章基于NIOS的软核设计实验 (79)实验一 16×16 LED点阵实验 (79)实验二 UART与PC机通信实验 (80)实验三 12位串行A/D实验 (81)实验四 12位串行D/A实验 (84)实验五 RS485通讯实验 (85)实验六基于SOPC的uC/OS-II操作系统应用实验 (88)实验七 7279键盘显示接口实验 (94)实验八压入弹出式IC卡实验 (101)实验九直流电机调速实验 (104)实验十 4相步进电机实验 (106)附录I NIOS II常用函数 (108)附录II USB下载线驱动安装 (119)第一章 EL-EMCU-I实验系统的资源介绍一、系统功能概述EL-EMCU-I型教学实验系统是属于一种综合的教学实验系统,该系统支持8位的8051 / C8051F021等型号、16位的MSP430系列 / AVR系列以及基于Cortex-M3内核的32位群星系列ARM处理器,实现了多模块的应用实验。

SOPC技术及应用实验指导

《SOPC技术原理及应用》实验指导书适用专业:电气、测控等编写单位:电气信息学院编写人:曹林审核人:审批人:批准时间:年月日目录前言MagicSOPC 创新教学实验开发平台 (3)实验1 PIO 输出—流水灯控制 (4)实验2 PIO输出—步进电机控制 (7)实验3 PIO 输入—读取开关信号 (12)实验4 PIO 外部中断实验 (15)前言MagicSOPC 创新教学实验开发平台MagicSOPC 是基于Altera Nios II SOPC 系列的专业级创新教学实验开发平台;采用Altera 公司Cyclone II 系列150 万门的FPGA,先进的系统化、模块化设计;丰富的人机交互方式,众多的高性能外设使得MagicSOPC 实验开发平台具有卓越的性能和无与伦比的灵活性;是SOPC、EDA、DSP 教学实验、电子设计创新实验室、现代嵌入式系统实验室、科研开发的上佳选择。

实验开发平台采用核心板加主板的结构,提供多种人机交互方式,多种模块外设,如:矩阵键盘、按键、拔档开关、触摸屏输入;数码管显示、大屏幕TFT 彩色液晶显示屏;AC97 音频模块;VGA、TV、PS/2、USB、IrDA、CAN、I2C、SPI、RS232、RS485、Modem、Ethernet、CF 卡、SD/MMC 卡、IDE 接口及高速AD/DA 模块等。

开发工程师可在该实验平台上实现EDA、SOPC、DSP 等各种设计并进行验证。

核心板可灵活地用于二次开发。

与一般的实验箱不同,MagicSOPC 主板的所有外设都不需要进行跳线设置,做实验时方便简单;此外每个外设的信号都设置了测试点,方便用户使用逻辑分析仪进行信号测量。

一切为设计为用户考虑是本开发平台的出发点。

考虑到核心板对用户的实用性,核心板除设计最小系统外,还设计有按键、LED 以及电源插座等,用户直接/或量身定制底板使用,这样核心板可用于用户自己的设计中,亦可用于电子设计大赛。

SOPC实验指导书解析

SOPC实验3.1使用NiosⅡ IDE建立用户程序1.创建一个新的C/C++应用工程执行下面的步骤来创建一个新的C/C++应用工程:1. 启动NiosⅡ IDE。

选择【开始】››【程序】››【Altera】››【QuartusⅡ 5.0】››【NiosⅡ Development Kits 5.0】››【NiosⅡ IDE】启动NiosⅡ IDE。

也可以通过图1.1直接点击按钮来启动Nios Ⅱ IDE。

图1 启动NiosⅡ IDE2.如果出现Workspace Launcher对话框,单击设置工作空间为QuartusⅡ工程的文件夹,如图2所示,这样便于管理。

如果是第一次进入工作区,NiosⅡ IDE会先弹出一个欢迎界面,此时点击右上角的Workbench图标,就可以进入NiosⅡ IDE编辑界面。

图2设置IDE工作空间3.如图3所示,选择【File】››【New】››【C/C++ Application】来打开新建C/C++工程向导,如图4所示。

图3打开新建C/C++工程向导图4新建C/C++工程向导4.单击Select Target Hardware右侧的按钮打开Select Target Hardware窗口,选择led_nios2_system.ptf文件,即指向当前硬件设计系统,如图5所示。

图5选择硬件目标文件5.选择Select Project Template列表中的hello_led。

Name栏中自动更新为hello_led_0,确认选中Use Default Location栏,如图6所示,单击完成工程创建。

图6完成设置后的工程向导向导中的Select Project Templates一栏中是已经设计好的软件工程,用户可以选择其中的一个,把它当作模板来创建自己的工程。

当然也可以选择Blank Project(空白工程),完全由用户写所有的代码。

本实验选取了hello_led工程,然后在此基础上进行适当的修改,一般情况下这比空白工程更加容易,也更方便。

实验指导书SoPC

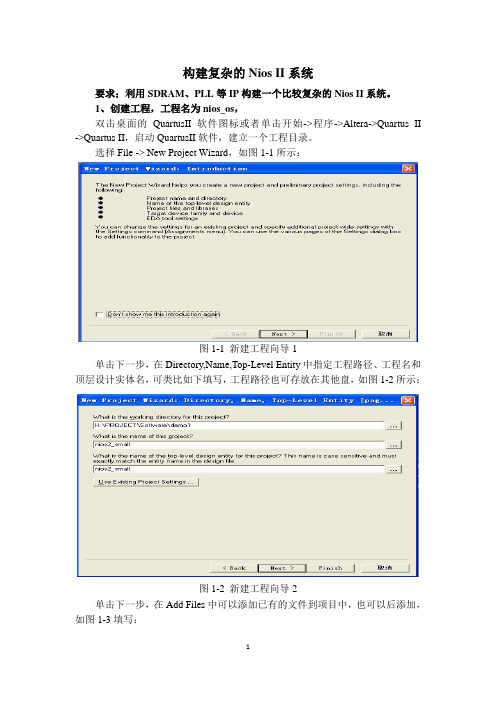

构建复杂的Nios II系统要求;利用SDRAM、PLL等IP构建一个比较复杂的Nios II系统。

1、创建工程,工程名为nios_os,双击桌面的QuartusII软件图标或者单击开始->程序->Altera->Quartus II ->Quartus II,启动QuartusII软件,建立一个工程目录。

选择File -> New Project Wizard,如图1-1所示:图1-1 新建工程向导1单击下一步,在Directory,Name,Top-Level Entity中指定工程路径、工程名和顶层设计实体名,可类比如下填写,工程路径也可存放在其他盘,如图1-2所示:图1-2 新建工程向导2单击下一步,在Add Files中可以添加已有的文件到项目中,也可以后添加,如图1-3填写:图1-3 新建工程向导3单击下一步,在Family & Device Settings中选择器件类型,如图1-4填写:图1-4 新建工程向导4单击下一步,在EDA Tools Setting中也可类比如图1-5填写:图1-5 新建工程向导5单击下一步,选择Finish。

图1-6 新建工程向导6注意:工程名为nios2_small改为nios_os。

2、构建一个复杂的Nios系统打开SOPC Builder,生成的Nios起名为nios_os,在Clock时钟设置中,填入所需要的时钟,48M;在对Nios II核选择时,选为标准型(Nios II/s),如图2-1所示:图2-1 Nios II处理器选型窗口在Caches & Tightly Coupled Memories的设置中,将Instruction Cache的设置改为2 Kbytes。

图2-2 指令缓存设置其它的按默认设置即可,更改cpu_0名称为cpu。

添加SDRAM控制器软核,双击Memory下的SDRAM Controller,数据位设置为16位,片选1位,4块banks,地址线12行,8列,其他参数设置及时序设置见图2-4:其中,Memory Profile的设置如图2-3所示:Timing的设置如图2-4所示:将sdram_0重命名为sdram,注意sdram的参数设置必须正确,否则将不能使用,时序参数的设置可以参考芯片的数据手册根据需要适当调整。

《SOPC实验指导》

东华理工大学自编教材2011年6月《SOPC设计与应用技术》研究性实践教学指导书东华理工大学机械与电子工程学院二○一一年六月目录一、DE2开发板介绍 (1)1.1 DE2开发板的配置 (1)1.2 DE2硬件原理 (3)1.3 准备使用DE2开发板 (16)二、课程实验....................................................................................................... 错误!未定义书签。

实验一8位二进制加法器设计——DE2板的使用 (18)实验二流水灯实验 (19)实验三按键控制指示灯实验 (31)实验四按键中断实验 (34)实验五定时器实验 (39)一、DE2开发板介绍1.1 DE2开发板的配置DE2是Altera公司针对大学教学及研究机构推出的FPGA多媒体开发平台。

DE2为用户提供了丰富的外设及多媒体特性,并具有灵活而可靠的外围接口设计。

DE2能帮助使用者迅速理解和掌握实时多媒体工业产品设计的技巧,并提供系统设计验证。

DE2平台的设计和制造完全按照工业产品标准进行,可靠性很高。

DE2开发板的硬件外观如图1.1所示,DE2开发板的硬件布局如图1.2所示。

DE2平台上提供的资源如下:1. Altera CycloneⅡ系列EP2C35F672C6 FPGA U11,内含35,000个逻辑单元(LE)。

2. 主动串行配置器件EPCS16 U30。

3. 板上内置用于编程调试和用户API设计的USB Blaster,支持JTAG和AS(主动串行)模式;U25是实现USB Blaster的USB接口芯片FT245B;U26是控制和实现JTAG模式和AS模式配置的CPLD EPM3128,可以用SW19选择配置模式;USB接口为J9。

4. 512 K字节SRAM(U18)。

5. 8 M字节(1M×4×16)SDRAM(U17)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CON目录第一章实验箱简介 (2)第二章EDA实验单元 (5)实验一七人表决器 (5)实验二格雷码变换 (13)实验三BCD码加法器 (15)实验四四位全加器 (17)实验五四人抢答器 (19)实验六四位并行乘法器 (20)实验七设计基本触发器 (21)实验八设计74LS169计数器功能模块 (25)实验九步长可变的加减计数器 (27)实验十可控脉冲发生器 (28)实验十一正负脉宽数控调制信号发生器 (30)实验十二序列检测器 (32)实验十三四位并行流水乘法器 (34)实验十四出租车计费器 (37)实验十五多功能数字钟 (39)实验十六数字秒表 (41)实验十七频率计 (43)实验十八交通灯控制器 (45)实验十九数码锁 (47)实验二十VGA彩条发生器 (49)附录 (51)第一章实验箱简介EDA/SOPC实验箱是集EDA和SOPC开发为一体的综合性实验箱,它不仅可以独立完成几乎所有的EDA设计,也可以完成大多数的SOPC开发。

采用Altera公司的Cyclone系列的12万门FPGA为核心,整个系统采用模块化设计,各个模块之间可以自由组合,使得该实验箱的灵活性大大提高。

同时实验箱还提供了丰富的接口模块,供人机交互,从而大大增加了实验开发者开发的乐趣,满足了普通高等院校、科研人员等的需求。

开发工程师可以使用VHDL语言、Verilog HDL语言、原理图输入等多种方式,利用Altera公司提供的Quartus II及Nios软件进行编译,下载,并通过EDA/SOPC实验箱进行结果验证。

实验箱提供多种人机交互方式,如键盘阵列、按键、拨挡开关输入;七段码管、大屏幕图形点阵LCD显示;串口通信;VGA接口、PS2接口、USB接口、Ethernet接口等,利用Altera 公司提供的一些IP资源和Nios 32位处理器,用户可以在该实验箱上完成不同的SOPC设计。

EDA/SOPC实验箱提供的资源有:●Altera公司的EP1C6Q240C8,12万门级FPGA,另外可选配更高资源的FPGA●FPGA配置芯片采用可在线变成的EPC2,通过JTAG口和简单的跳线即可完成设计的固化●1个数字时钟源,提供48MHz、12MHz、1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、2Hz和1Hz等多个时钟●1个模拟信号源,提供频率和幅度可调的正弦波、三角波和方波●两个串行接口,一个用于SOPC开发时的调试,另一个可以完成其它的通信●1个VGA接口●1个PS2接口,可以接键盘或鼠标●1个USB接口,利用PDIUSBD12芯片实现USB协议转换●1个Ethernet接口,利用RTL8019芯片实现TCP/IP协议转换●基于SPI接口的音频CODEC模块●1个输入、输出探测模块,供数字信号的观察●16个LED显示●8个拨挡开关输入●8个按键输入●1个4X4键盘阵列●8个七段码管显示●1个扬声器模块●1个交通灯模块●1个直流电机模块●1个高速AD和1个高速DA●240×128大屏幕图形点阵LCD显示●存储器模块提供256K×32Bit的SRAM和2M×8Bit的FLASHROM实验箱基本布局如下图1-1所示:图1-1 EDA/SOPC 试验箱系统布局下面就部分模块做简要介绍。

FPGA模块FPGA采用Altera公司提供的Cyclone系列的EP1C6Q240C8,该芯片采用240脚的PQFP封装,提供185个IO接口。

该芯片拥有5980个LEs;20个M4K RAM Block;总共可以提供92160Bit的RAM;另外芯片内部还自带有2个锁相环,可以在高速运行的时候保证系统时钟信号的稳定性。

FPGA与实验箱上提供的各个模块都已经连接好(详情请查看附录1),这样就避免了实验过程中繁琐的连线以及由于连线造成的不稳定的后果。

配置模块本实验箱的配置芯片采用可在线多次编程的EPC2,该芯片通过JTAG (与FPGA共用,通过跳线选择)下载,即可完成FPGA设计的固化。

这样就避免了用户需要多条电缆或者需要编程器才能完成固化的任务,同时也方便了用户只需一条下载电缆即可完成FPGA的配置和EPC2的编程。

时钟模块时钟的产生由有源晶振产生48MHz的时钟信号,再由CPLD分频完成多种时钟信号的产生。

时钟信号已经在系统板上连接到FPGA的全局时钟引脚(PIN_28),只需要通过时钟模块的简单跳线,即可完成FPGA时钟频率的选择。

USB模块USB模块采用Philips公司的PDIUSBD12芯片,它通常用作微控制器系统中实现与微控制器进行通信的高速通用并行接口。

它还支持本地的DMA传输。

PDIUSBD12完全符合USB1.1版的规范、它还符合大多数器件的分类规格:成像类、海量存储器件、通信器件、打印设备以及人机接口设备。

另外该芯片还集成了许多特性,包括SoftConnect TM、GoodLink TM、可编程时钟输出、低频晶振和终止寄存器集合,所有这些特性都为系统显著的节约了成本,同时使USB功能在外设上的应用变得容易。

存储器模块实验箱上提供了256K×32Bit的SRAM和2M×8Bit的FLASH ROM,其中SRAM主要是为了在开发SOPC是存放可执行代码和程序中用到的变量,而FLASH则是用来固化调试好的SOPC代码等。

SRAM选用两片ISSI 公司的IS61LV25616(256K×16Bit)进行数据线并联从而扩展为256K×32Bit的存储区;FLASH ROM采用的是AMD公司的AM29LV017D,其容量为2Mbyte。

Ethernet模块Ethernet模块采用的TCP/IP转换芯片为RTL8019AS芯片,该芯片是一款高集成度、全双工以太网控制器,内部集成了三级省电模式,由于其便捷的接口方式,所以成了多数系统设计者的首选。

RTL8019AS支持即插即用标准,可以自动检测设备的接入,完全兼容Ethernet II以及IEEE802.3 10BASE5、10BASE2、10BASET等标准,同时针对10BASET还支持自动极性修正的功能,另外该芯片还有很多其他功能,此处不再赘述。

高速AD&高速DA本实验箱中采用的高速AD为TLC5510,TLC5510是一个8位高速AD,其最高转换速率可到20MSPS,单5V供电,被广泛的应用在数字电视、医疗图象、视频会议等高速数据转换的领域。

本实验箱中采用的高速DA位TLC5602,该芯片也是一个单5V供电的8位高速DA,其最高转换输率可到33M,足以满足一般数据处理的场合。

240×128图形点阵LCD本实验箱所用的图形点阵LCD为240×128点,可以用来显示图形、曲线、文本、字符等等。

显示模块内嵌有T6963C控制器,在该液晶显示模块上已经实现了行列驱动器及显示缓冲区RAM的接口,同时也硬件设置了液晶的结构:单屏显示、80系列的8位微处理器接口、显示屏长度为30个字符、宽度为16个字符等。

第二章EDA实验单元实验一七人表决器一实验目的1.熟悉Quartus II软件的使用。

2.熟悉EDA/SOPC实验箱。

3.熟悉EDA开发的基本流程。

二硬件需求1.EDA/SOPC实验箱一台。

三实验原理所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

四实验内容本实验就是利用EDA/SOPC实验箱中的拨挡开关模块和LED模块来实现一个简单的七人表决器的功能。

拨挡开关模块中的K1~K7表示七个人,当拨挡开关输入为‘1’时,表示对应的人投同意票,否则当拨挡开关输入为‘0’时,表示对应的人投反对票;LED模块中LED1_1表示七人表决的结果,当LED1_1点亮时,表示一致同意,否则当LED1_1熄灭时,表示一致反对。

拨挡开关K1~K7以及LED1_1与FPGA的引脚连接请查看附录一。

五实验步骤完成七人表决器的实验步骤如下:1.选择开始>程序>Altera>Quartus II 4.0,运行Quartus II软件。

2.选择File>New Project Wizard,新建一个工程。

3.在introduction中点击next。

4.指定工作目录,如E:/SOPC。

5.指定工程核顶层设计实体名称,如exp1。

见图2-1。

6.点击3次next。

7.选择FPGA器件:选择Cyclone,并在Do you want to assign a specific device?选项中选择Yes,并点击next。

见图2-2。

图2-1 指定工程名称及目录图2-2 选择器件8.首先在Speed选项中选择8,然后再选择EP1C6Q240C8器件。

见图2-3。

图2-3 选择具体的FPGA9.点击Finish,工程文件建立结束。

10.点击File>New,新建一个VHDL文件。

见图2-4。

图2-4 新建VHDL文件11.点击OK,并点击File>Save,无需做任何更改,点击OK即可。

见图2-5。

图2-5 存储新建的VHDL文件12.按照自己的想法,在新建的VHDL文件中编写VHDL程序(可参考光盘中【实验内容/EDA实验/example1/exp1.vhd】)。

13.代码书写结束后,选择Processing>Start Compilation对编写的代码进行编译,直到编译通过。

14.编译通过后,选择File>New,在弹出的对话框中点击Other Files,选择Vector Waveform File,并点击OK,建立一个波形文件。

见图2-6。

图2-6 新建波形文件15.点击File>Save,在弹出的对话框中点击OK即可。

见图2-7。

图2-7 存储新建的波形文件16.在波形文件中点击鼠标右键,选择Insert Node or Bus,在弹出的对话框中点击Node Finder,在新弹出的对话框中的Filter中选择Pins:all,然后点击List,这样在Nodes Founder区域就会出现先前VHDL文件中定义的输入、输出端口,然后再点击>>,选择OK即可,然后在Insert Node or Bus 对话框中也选择OK。