巴克码检测VHDL设计

《EDA技术》习题(解答)5

《EDA技术》习题5 习题5-1 归纳利用Quartus II进行VHDL文本输入设计的流程:从文件输入一直到SignalTap II 测试。

P95~P115答:1 建立工作库文件夹和编辑设计文件;2 创建工程;3 编译前设置;4 全程编译;5 时序仿真;6 引脚锁定;7 配置文件下载;8 打开SignalTap II编辑窗口;9 调入SignalTap II的待测信号;10 SignalTap II参数设置;11 SignalTap II参数设置文件存盘;12 带有SignalTap II测试信息的编译下载;13 启动SignalTap II进行采样与分析;14 SignalTap II的其他设置和控制方法。

5-2 由图5-40和图5-41,详细说明工程设计CNT10的硬件工作情况。

P114~P115答:图5-40给出工程设计CNT10的十进制计数工作情况;当计数CQ或CQI到9时,计数进位COUT输出正脉冲。

图5-41给出工程设计CNT10的十进制计数和内部计数节点CQI计数线性递增的信号波形的工作情况。

5-3 如何为设计中的SignalTap II加入独立采样时钟?试给出完整的程序和对它的实测结果。

P115答:为SignalTap II提供独立时钟的方法是在顶层文件的实体中增加一个时钟输入端口,如语句:LOGC_CLK:IN STD_LOGIC;在此实体中不必对其功能和连接具体定义,而在SignalTap II的参数设置中则可以选择LOGC_CLK为采样时钟。

5-4 参考QuartusII的Help,详细说明Assignments菜单中Settings对话框的功能。

(1)说明其中的Timing Requirements&Qptions的功能、他用方法和检测途经。

Specifying Timing Requirements and Options (Classic Timing Analyzer)You can specify timing requirements for Classic timing analysis that help you achieve the desired speed performance and other timing characteristics for the entire project, for specific design entities, or for individual clocks, nodes, and pins.When you specify either project-wide or individual timing requirements, the Fitter optimizes the placement of logic in the device in order to meet your timing goals.You can use the Timing wizard or the Timing Analysis Settings command to easily specify all project-wide timing requirements, or you can use the Assignment Editor to assign individual clock or I/O timing requirements to specific entities, nodes, and pins, or to all valid nodes included in a wildcard or assignment group assignment.To specify project-wide timing requirements:1.On the Assignments menu, click Settings.2.In the Category list, select Timing Analysis Settings.3.To specify project-wide t SU, t H, t CO, and/or t PD timing requirements, specify valuesunder Delay requirements.4.To specify project-wide minimum delay requirements, specify options underMinimum delay requirements.5.Under Clock Settings, select Default required fmax.6.In the Default required fmax box, type the value of the required f MAX and select atime unit from the list.7.If you want to specify options for cutting or reporting certain types of timing pathsglobally, enabling recovery/removal analysis, enabling clock latency, and reporting unconstrained timing paths, follow these steps:8.Click OK.To specify clock settings:1.On the Assignments menu, click Settings.2.In the Category list, select Timing Analysis Settings.3.Under Clock Settings, click Individual Clocks.4.Click New.5.In the New Clock Settings dialog box, type a name for the new clock settings in theClock settings name box.6.To assign the clock settings to a clock signal in the design, type a clock node name inthe Applies to node box, or click Browse... to select a node name using the Node Finder.7.If you want to specify timing requirements for an absolute clock, follow these steps:8.If you have already specified timing requirements for an absolute clock, and you wantto specify timing requirements for a derived clock, follow these steps:9.In the New Clock Settings dialog box, click OK.10.In the Individual Clocks dialog box, click OK.11.In the Settings dialog box, click OK.To specify individual timing requirements:1.On the Assignments menu, click Assignment Editor.2.In the Category bar, select Timing to indicate the category of assignment you wishto make.3.In the spreadsheet, select the To cell and perform one of the following steps:•Type a node name and/or wildcard that identifies the destination node(s) you want to assign.•Double-click the To cell and click Node Finder to use the Node Finder to enter a node name.•Double-click the To cell, click the arrow that appears on the right side of the cell, and click Select Assignment Group to enter an existing assignmentgroup name.4.To specify an assignment source, repeat step 3 to specify the source name in theFrom cell.5.In the spreadsheet, double-click the Assignment Name cell and select the timingassignment you wish to make.6.For assignments that require a value, double-click the Value cell and type or selectthe appropriate assignment value.To specify timing analysis reporting restrictions:1.On the Assignments menu, click Settings.2.In the Category list, double-click Timing Analysis Settings.3.Click Timing Analyzer Reporting.4.To specify the range of timing analysis information reported, specify one or moreoptions in the Timing Analyzer Reporting page.5.Click OK.(2)说明其中的Compilation Process的功能和使用方法。

EDA课程ROM扩展巴克码检测器

控制系统

用于检测控制系统的异 常情况,提高控制系统

的可靠性和稳定性。

医疗设备

用于检测医疗设备中的 异常情况,提高医疗设 备的安全性和可靠性。

优势与局限性

优势

ROM扩展巴克码检测器具有高可靠 性、高稳定性、高抗干扰能力等优点 ,能够有效地检测和纠正信号中的错 误,提高系统的性能和可靠性。

局限性

由于ROM扩展巴克码检测器的实现较 为复杂,且需要预先定义检测码,因 此在某些情况下可能无法适应快速变 化的环境和信号。

软件实现

软件算法设计

根据巴克码检测器的算法 需求,设计合理的软件算 法,包括编码、解码和检 测等算法。

编程语言选择

选择适合的编程语言,如 C/C或Verilog等,进行软 件算法的实现。

代码优化与调试

对实现的算法进行优化和 调试,确保软件的正确性 和性能。

测试与验证

测试环境搭建

搭建适合的测试环境,包括硬件测试平台和软件测试 平台。

ROM扩展巴克码检测器可根据不同的 应用场景和需求进行灵活配置,具有 广泛的应用前景。

该检测器具有较高的检测效率和准确 性,能够在较短时间内完成信号的解 码和纠错。

对未来研究的展望

01

深入研究其他类型的巴克码

除了ROM扩展巴克码检测器,还有其他类型的巴克码,如Reed-

Solomon码等。未来可以进一步研究这些巴克码的性能和应用。

高速化

随着信号传输速率的不断提高,ROM扩展巴克码检测器 的高速化将成为未来的发展方向,能够适应高速信号的检 测和纠正需求。

05

结论

总结课程收获

掌握ROM扩展巴克码检测器的原理

01

通过学习,我深入理解了ROM扩展巴克码检测器的工作原理,

巴克码

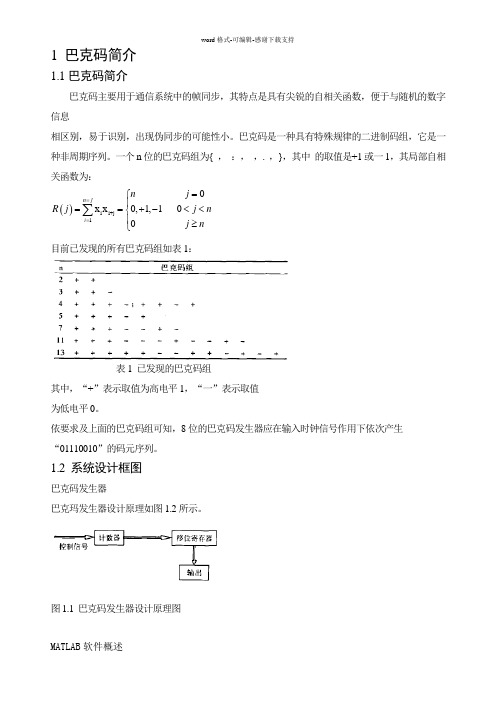

1 巴克码简介1.1巴克码简介巴克码主要用于通信系统中的帧同步,其特点是具有尖锐的自相关函数,便于与随机的数字信息相区别,易于识别,出现伪同步的可能性小。

巴克码是一种具有特殊规律的二进制码组,它是一种非周期序列。

一个n 位的巴克码组为{ , :, ,. ,},其中 的取值是+1或一1,其局部自相关函数为:()i i+j 10x x 0,1,100n j i n j R j j n j n ===⎧⎪==+-<<⎨⎪≥⎩∑目前已发现的所有巴克码组如表1:表1 已发现的巴克码组其中,“+”表示取值为高电平1,“一”表示取值为低电平0。

依要求及上面的巴克码组可知,8位的巴克码发生器应在输入时钟信号作用下依次产生“01110010”的码元序列。

1.2 系统设计框图巴克码发生器巴克玛发生器设计原理如图1.2所示。

图1.1 巴克码发生器设计原理图MATLAB 软件概述MATLAB是矩阵实验室(Matrix Laboratory)的简称,是美国MathWorks公司出品的商业数学软件,用于算法开发、数据可视化、数据分析以及数值计算的高级技术计算语言和交互式环境,主要包括MATLAB和Simulink两大部分。

MATLAB是由美国mathworks公司发布的主要面对科学计算、可视化以及交互式程序设计的高科技计算环境。

它将数值分析、矩阵计算、科学数据可视化以及非线性动态系统的建模和仿真等诸多强大功能集成在一个易于使用的视窗环境中,为科学研究、工程设计以及必须进行有效数值计算的众多科学领域提供了一种全面的解决方案,并在很大程度上摆脱了传统非交互式程序设计语言(如C、Fortran)的编辑模式,代表了当今国际科学计算软件的先进水平。

MATLAB和Mathematica、Maple并称为三大数学软件。

它在数学类科技应用软件中在数值计算方面首屈一指。

MATLAB可以进行矩阵运算、绘制函数和数据、实现算法、创建用户界面、接其他编程语言的程序等,主要应用于工程计算、控制设计、信号处理与通讯、图像处理、信号检测、金融建模设计与分析等领域。

巴克码发生器设计

摘要本课程设计主要是利用QUARTERSⅡ设计一个8位巴克码代码发生器,当识别到一组代码时,输出一个高电平脉冲。

巴克码主要用于通信系统中的帧同步,其特点是具有尖锐的自相关函数,便于与随机的数字信息相区别,易于识别,出现伪同步的可能性小。

巴克码是一种具有特殊规律的二进制码组,它是一种非周期序列。

关键词:QUARTERSⅡ,巴克码,信号发生器,序列1绪论在通信系统中,同步技术起着相当重要的作用。

通信系统能否有效地、可靠地工作,很大程度上依赖于有无良好的同步系统。

通信系统中的同步可分为载波同步、位同步、帧同步等几大类。

当采用同步解调或相干检测时,接收端需要提供一个与发射端调制载波同频同相的相干载波,获得此相干载波的过程称为载波提取,或称为载波同步。

而在数字通信中,消息是一串连续的信号码元序列,解调时常须知道每个码元的起止时刻。

因此,就要求接收端必须能产生一个用作定时的脉冲序列,以便与接收的每一个码元的起止时刻一一对齐。

在接收端产生与接收码元的重复频率和相位一致的定时脉冲序列的过程称为码元同步或位同步。

数字通信中的消息数字流总是用若干码元组成一个“字”,又用若干“字”组成一“句”。

因此,在接收这些数字流时,同样也必须知道这些“字”、“句”的起止时刻,在接收端产生与“字”、“句”起止时刻相一致的定时脉冲序列,统称为群同步或帧同步。

当通信是在两点之间进行时,完成了载波同步、位同步和帧同步之后,接收端不仅获得了相干载波,而且通信双方的时标关系也解决了,这时,接收端就能以较低的错误概率恢复出数字信息。

在数字通信系统中,实现帧同步的方法通常有两种:起止式同步法和集中式插入同步法。

起止式同步比较简单,一般是在数据码元的开始和结束位置加入特定的起始和停止脉冲来表示数据帧的开始和结束。

另外在计算机RS232串口通信中通常也使用类似方法。

而在集中式插入同步法中,要求插入的同步码在接收端进行同步识别时出现伪同步的概率尽可能小,并且要求该码组具有尖锐的自相关函数以便于识别。

VHDL实验报告(1)

VHDL 实验报告******班级:电子0701学号:************实验一组合逻辑电路设计一实验目的:1. 熟悉mux+pluxII软件,可以进行新文件的编辑和文件的修改。

2. 掌握门电路VHDL语言程序设计方法。

3. 掌握选择器VHDL语言程序设计方法。

4. 掌握加法器VHDL语言程序设计方法。

5. 熟悉VHDL编程的基本方法。

二实验设备:1.计算机2.Max+PlusII软件三实验原理及内容:1 二输入与门(1)实验原理二输入与门是我们数字电路中的一个基础逻辑门电路,是最基本的逻辑门电路之一,也是最简单的逻辑门之一。

它能实现两个输入端的相与,一般有三个端口。

二输入与门的表达式是:Y=ab二输入与门的逻辑符号如图(1)所示,真值表如表(1)所示。

图(1)与门逻辑符号表(1)与门真值表(2)实验内容a.在mux+pluxII文本编辑环境下,打开新文本,编写两输入与门VHDL语言源程序,程序设计如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY and2 ISPORT(a,b: IN STD_LOGIC;Y: OUT STD_LOGIC);END and2;ARCHITECTURE behave OF and2 ISBEGINY <= a and b;END behave;b.对源程序进行编译,按照提示进行修改,直至编译通过。

c.对编译程序进行仿真,分析并记录仿真波形,其仿真波形图如图(2)所示。

图(2)二输入与门仿真图d.在自己的目录下保存相应的源文件、波形文件。

2 四选一选择器(1)实验原理四选一选择器如图(3)所示,真值表如表(2)所示。

图(3)mux4管脚图表(2)mux4真值表(2)实验内容a.在mux+plusII文本编辑环境下,打开新文件,编辑四选一VHDL源程序文件,其程序设计如下:LIBRARY IEEEUSE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT(A: IN STD_LOGIC_VECTOR (1 DOWNTO 0);D0,D1,D2,D3:IN STD_LOGIC;G:IN STD_LOGIC;Y: OUT STD_LOGIC);END mux4;ARCHITECTURE dataflow OF mux4 ISBEGINPROCESS (A,D0,D1,D2,D3,G)BEGINIF (G ='0') THENIF (A="00")THEN Y <= D0;ELSIF(A="01")THEN Y <= D1;ELSIF(A="10")THEN Y <= D2;ELSE Y <= D3;END IF;ELSE Y <='0';END IF;END PROCESS;END dataflow;b.对源程序进行编译,按照提示进行修改,直到编译通过。

VHDL编程规范

华为VHDL编程规范(2010-10-18 13:30:09)转载分类:FPGA标签:vhdl编程规范杂谈1.标识符 (Identifiers)命名习惯标识符用于定义实体名结构体名信号和变量名等选择有意义的命名对设计是十分重要的命名包含信号或变量诸如出处有效状态等基本含义下面给出一些命名的规则包括VHDL语言的保留字2.标识符定义命名规定标识符第一个字符必须是字母最后一个字符不能是下划线不许出现连续两个下划线基本标识符只能由字母数字和下划线组成标识符两词之间须用下划线连接标识符不得与保留字同名3. 标识符大小写规定对常量数据类型实体名和结构体名采用全部大写对变量采用小写对信号采用第一个词首字符大写保留字一律小写建议用有意义而有效的名字能简单包含该信号的全部或部分信息如输入输出信息Data_in 总线数据输入Din 单根数据线输入FIFO_out FIFO数据总线输出如宽度信息Cnt8_q 8位计数器输出信号的命名变量主要用在高层次的模拟模型建模及用于运算的用途但变量的综合较难定义对于编写可综合的VHDL模块在没有把握综合结果情况下建议不使用在VHDL中信号(signal)代表硬件连线因此可以是逻辑门的输入输出同时信号也可表达存贮元件的状态端口也是信号在进程process 中信号是在进程结束时被赋值因此在一个进程中当一个信号被多个信号所赋值时只有最后一个赋值语句起作用1. 实体结构体使用规定library IEEE use IEEE.std_logic_1164.all 除IEEE大写外其余小写实体名和结构体名必须用大写标识实体名必须与文件名同名自定义的其他标识符如信号名变量名标号等不得与实体名结构体名同名实体端口数据模式不准使用buffer 模式需要反馈的信号可定义内部信号来解决如计数器端口Count 可内部定义信号signal Cnt8_q STD_LOGIC_VECTOR(7 downto 0)实体端口数据类型规定实体端口的数据类型采用IEEE std_logic_1164 标准支持的和提供的最适合于综合的数据类型STD_ULOGIC STD_LOGIC和这些类型的数组不采用IEEE 1076 /93 标准支持和提供的BIT BIT数组INTEGER及其派生类型这是为保证模拟模型和综合模型的一致性及减少转换时间和错误代码书写要有层次即层层缩进格式清晰美观要有必要的注释25%实体开始处应注明文件名功能描述引用模块设计者设计时间及版权信息等如-- Filename ﹕-- Author ﹕-- Description ﹕library IEEE;use IEEE.std_logic_1164.all;entity ENTITY_NAMEport(Port1 : in STD_LOGIC;Port2 : in STD_LOGIC;Port3 : out STD_LOGIC;..Portn : out STD_LOGIC);end ENTITY_NAME ;architecture BEHAVIOR of ENTITY_NAME isbeginStatements;end BEHAVIOR ;实体名的命名建议能大致反映该实体的功能如COUNTER8 8位宽的计数器模块DECODER38 3-8线译码器模块一个实体可以有多个结构体对单个结构体的实体文件要包含结构体和实体说明便于查阅对多个结构体的实体建议把常用的结构体放在文件中其余结构体用单独文件表示使用时用configuration 语句进行配置2. VHDL各语句使用规定with-select-when 语句书写规范规定with- select - when 语句提供选择信号赋值是根据选定信号的值对信号赋值代码的书写规范为with S selectX <= A when 00,B when 01,C when 10,D when others;when_else 语句书写规范规定when_else 语句提供为条件信号赋值即一个信号根据条件被赋一值代码书写规范为Signal_name <= value_a when condition1 elsevalue_b when condition2 elsevalue_c when condition3 elsevalue_x当条件是表达式时表达式须用()括起来使代码更为清晰如when (a = b and C= ‘1 ’)elseif 必须有一个else 对应除在如下面例子的情况下可不写else语句例process( Clk,Rst)beginif ( Rst = '1') thenQ <= '0';elsif ( Clk ‘event and Clk = ‘1’) thenQ <= D;end if;end process;case- when 语句书写规范规定该语句用于规定一组根据给定选择信号的值而执行的语句可用with-select-when 语句等效代码的书写规范为case- selection_signal iswhen value1_of _selection signal =>Statements1;when value2_of _selection signal =>Statements2;....when last_value_of _selection signal =>Statements x ;when others =>Statements x;end case;process 显示敏感列表必须完整对有Clk 的process 不同综合工具有不同的要求有些只要写Clk和Rst就可建议根据具体情况简化设计书写有clk的process 的敏感列表中为方便修改敏感列表书写规范如下Lab: process (Clk, Rst,list1,list2)begin每个process 前须加个lable为便于阅读port map 采用名字对应(=> )映射方法port map 中总线到总线映射时(X downto Y )要写全VHDL保留字VHDL语言的保留字如下absaccess after alias all and architecture array assert attributebegin block buffer bus case component configuration constantdisconnect downto else elsif end entity exit file for functiongenerate generic group guarded if impure in inertial inoutis label library linkage literal loop map mod nand new next nornot null of on open or others out package portpostponed procedure process pure range record register reject rem report return rol ror select severity signal shared sla sll sra srl subtype then to transport type unaffected units until use variablewait when while with xnor xorVHDL 编写范例。

10 VHDL综合设计实验(大作业)

综合设计:基于VHDL的线路编解码实现数字光纤通信系统对线路码型的要求主要是保证传输的透明性,如下图,在电调制光源之前,通常需要对解码或扰码后的二进制码进行线路编码,减小功率谱中的高低频分量,为光接收机提供足够的定时信息,保证定时信息丰富,或能提供一定的冗余码,用于平衡码流、误码监测和公务通信。

而接收端进行光电转换后,提取位时钟信号进行判决得到线路编码信号,还需要进行解码还原出原始数字信号。

图1-1 光发送机的线路编码电路FPGA在通信领域应用非常广泛,即将成为硬件设计的主流技术,编解码系统是其最基本的应用之一。

希望同学们能珍惜这次历练的机会,独立自主完成该作业,提升自己FPGA分析问题、解决问题的能力,为就业和将来的深造打好基础!一、线路编解码的相关知识mBnB、mB1C、mB1P、mB1H等都是常用的光线路编码,下面分别对其原理和实现方法进行介绍:1)、mBnB线路编解码及其实现方法mBnB码是把输入的二进制原始码流进行分组,每组有m个二进制码,记为mB,称为一个码字,然后把一个码字变换为n个二进制码,记为nB,并在同一个时隙内输出。

这种码型是把mB变换为nB,所以称为mBnB码。

其中,m和n都是正整数,n>m,一般选取n=m+1。

mBnB码有1B2B、3B4B、5B6B、 8B9B等等。

最简单的mBnB码是1B2B码,即曼彻斯特码,这就是把原码的“0”变换为“01”,把“1”变换为“10”。

因此最大的连“0”和连“1”的数目不会超过两个,例如1001和0110。

但是在相同时隙内,传输1比特变为传输2比特,码速提高了1倍(以太网中应用)。

设计者应根据最佳线路码特性的原则来选择码表。

作为普遍规则,引入“码字数字和”(WDS)来描述码字的均匀性,并以WDS 的最佳选择来保证线路码的传输特性。

所谓“码字数字和”,是在nB码的码字中,用“-1”代表“0”码,用“+1”代表“1”码,整个码字的代数和即为WDS。

巴克码简介

j=0 0< j<n j≥n

对于 7-bit 巴克码,相关函数如下图所示:

Hale Waihona Puke 13-17 6 5 4 3 2 1 0 -1 -2 -10 -5 0 5 10

图 2 巴克码的(0 扩展)相关函数 除了 7-bit 巴克码之外,还有一下长度的巴克码: 长度 2 3 4 5 7 11 13 编码 ++ ++ + + + ;+ + + +++++ ++++ +++++ +++++++++

-1 -2 -10 -5 0 5 10

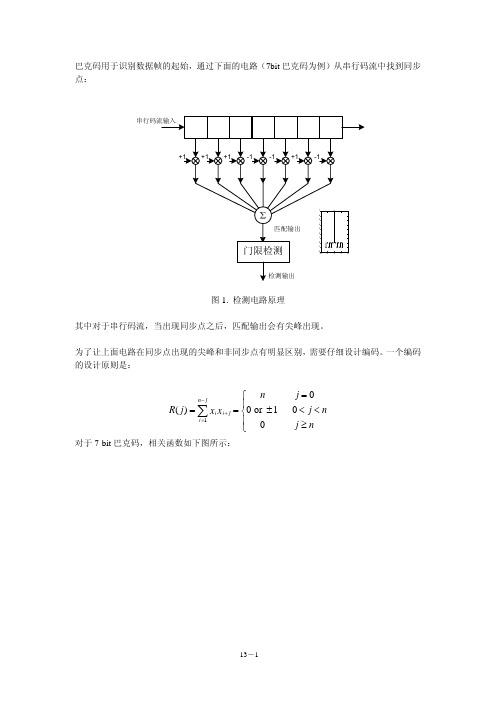

图 1. 检测电路原理 其中对于串行码流,当出现同步点之后,匹配输出会有尖峰出现. 为了让上面电路在同步点出现的尖峰和非同步点有明显区别, 需要仔细设计编码. 一个编码 的设计原则是:

n R ( j ) = ∑ x i x i + j = 0 or ± 1 i =1 0

131巴克码用于识别数据帧的起始通过下面的电路7bit巴克码为例从串行码流中找到同步点

uingrd@

巴克码用于识别数据帧的起始,通过下面的电路(7bit 巴克码为例)从串行码流中找到同步 点:

串行码流输入

+1

+1

+1

-1

-1

+1

-1

7 6 5 4

匹配输出

3 2 1 0

门限检测

检测输出

13-2

�

帧同步电路的 VerilogHDL 设计

帧同步电路的VerilogHDL 设计Design of A Frame Synchronization Circuit with VerilogHDL(解放军镇江船艇学院)张 伟 李霞明ZHANG Wei LI Xiaming摘要:帧同步技术是通信系统中的关键技术。

文中采用自顶向下的方法,以Verilog 语言描述了可辨别2PSK 相位模糊的巴克码识别器,给出了时序仿真波形,并探讨了完整帧同步电路的实现方法。

关键词:帧同步、巴克码、verilogHDL 、软核 中图分类号:TN927 文献标识码:AAbstract : Frame synchronization technique plays an important part in the communication system. We propose a verilog discription of a frame synchronization circuit which can identify the phase blur of the 2PSK receiver. The simulation wave is given and the implementation metheod of a complete frame synchroniazation circuit is discussed.Key word : frame synchronization, baker code, verilogHDL, soft core0 引言数字通信系统中的信息码流总是把码元组成一个个码组来传送,因此接收信息时必须知道这些码组的起止时刻。

帧同步的任务就是在接收端产生与这些码组起止时刻相一致的定时脉冲序列【1】。

巴克码是连贯式插入法【1】实现帧同步时常用的码组。

VerilogHDL 与VHDL 都是IEEE 标准的硬件描述语言,两者各有千秋,都能实现自顶向下的设计方法,单就语法的简洁和灵活程度来说,Verilog 更胜一筹。

EDA课设巴克码

课程设计任务书学生姓名:专业班级:指导教师:工作单位:题目:巴克码发生器初始条件:QuartusⅡ,CPLD要求完成的主要任务:1、设计并实现一个巴克码(01110010代码)发生器。

波形图见图1。

图1 巴克码(01110010代码)发生器仿真波形图2、将所设计的整个系统写入CPLD 器件中,加上需要的外围电路在实验箱上实现整个系统的硬件搭建,并调试出结果。

时间安排:收集资料第1天学习VHDL语言的基本知识第2-3天学习巴克码的基本知识第4-5天编写程序并调试出结果完成设计要求第6-9天答辩第10天指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)ABSTRACT (II)绪论 (1)1巴克码简介 (3)1.1巴克码简介 (3)1.2巴克码的产生与检测 (3)1.2.1巴克码的产生 (3)1.2.2巴克码的识别 (4)2 QUARTERS Ⅱ设计软件介绍 (6)3 巴克码发生器的设计 (7)3.1设计原理框图 (7)3.2单元模块设计 (7)3.2.1分频模块设计 (7)3.2.2八位计数控制模块设计 (8)3.2.3巴克码产生模块设计 (8)3.2.4显示模块设计 (9)3.3顶层电路设计 (9)4仿真与调试 (10)4.1软件仿真 (10)4.2硬件调试 (10)4.2.1硬件配置与初始化 (10)4.2.2演示结果及分析 (11)5小结即心得体会 (12)附录 (14)摘要本文介绍了一种采用单片CPLD芯片进行巴克码发生器的设计方法,主要阐述如何使用新兴的EDA 器件取代传统的电子设计方法,利用CPLD 的可编程性,简洁而又多变的设计方法,缩短了研发周期。

本设计实现了巴克码发生器的一些基本功能,主要包括八位巴克码序列产生,以及数码显示功能。

本次设计主要包括采用了CPLD 芯片,使用VHDL 语言进行编程,使其具有了更强的移植性,更加利于产品升级。

巴克码主要用于通信系统中的帧同步,其特点是具有尖锐的自相关函数,便于与随机的数字信息相区别,易于识别,出现伪同步的可能性小。

VHDL的编码器和译码器的设计

VHDL的编码器和译码器的设计摘要: VHDL是Very High Speed Integrated Circuit Hardware Description Language的缩写,意思是超高速集成电路硬件描述语言。

以MAX+plusII软件工具为开发环境,以可编程逻辑器件为实验载体,实现源代码编程和仿真功能。

本设计提出了一种基于VHDL语言的编码器和译码器的实现方法。

编码器与译码器是计算机电路中基本的器件,本课程设计采用VHDL设计编码和译码器。

编码器由8线-3线优先编码器作为实例代表,译码器则包含3线-8线译码器和2线-4线译码器两个实例模块组成。

课程设计采用硬件描述语言VHDL把电路按模块化方式进行设计,然后进行编程、时序仿真和分析等。

设计的系统结构简单,使用方便,具有一定的应用价值。

关键词: VHDL;MAX+plusII;编码器;译码器Encoder and decoder design based on VHDLAbstract: VHDL is the Very High Speed Integrated Circuit Hardware Description Language acronym, meaning high speed integrated circuit hardware description language.MAX+plusII software as tools for the development of the environment,programmable logic devices in experimental carrier,the realiztionof the source code programming and simulation. The paper proposes a method for encoder and decoder based on the VHDL language.Encoder and decoder is a basic computer circuit devices.This Curriculum design by VHDL design encoder and decoder.Encoders from 8 - 3 priority encoder for example,and decoder includes3 - 8 decoder and the 2 -4 examples of the two decoder modules.And then to program, the timing simulation and analysis.Curriculum design, simple system structure, easy to use and has a value.Keyword: VHDL; MAX+plusII; Encoder; Decoder基于VHDL的编码器和译码器的设计目录1 引言 (1)1.1 设计的目的 (1)1.2 设计的内容 ........................................................ 1 2 MAX+plusII及VHDL简介 .. (3)2.1 MAX+plusII 基本介绍 (3)2.1.1 MAX+plusII的概念 (3)2.1.2 使用MAX+plusII设计的特点 ................................... 3 2.2 硬件描述语言――VHDL . (3)2.2.1 VHDL的简介 (3)2.2.2 VHDL语言的特点 .............................................. 4 2.2.3 VHDL的设计流程 . (4)3 设计实现 (6)3.1编码器 (6)3.1.1 8线-3线优先编码器的工作原理 (6)3.1.2 8线-3线优先编码器的设计 ................................... 7 3.2译码器 (8)3.2.1 译码器的工作原理 (8)3.2.2 3线-8线译码器的设计 ...................................... 10 3.2.3 2线-4线译码器的设计 .. (11)4 系统仿真与时序分析 (12)4.1 8线-3线优先编码器仿真及时序分析 (12)4.2 3线-8线译码器仿真及时序分析 ................................ 13 4.3 2线-4线译码器仿真及时序分析 .. (14)5 结束语 ................................................................15 致谢 ....................................................................16 参考文献 ................................................................17 附录 ...................................................................17基于VHDL的编码器和译码器的设计第1页共20页1 引言随着社会的发展,科学技术也在不断的进步。

EDA课程ROM扩展巴克码检测器

巴克码检测器状态转换图

第19页/共27页

VHDL程序

第20页/共27页

第21页/共27页

第22页/共27页

仿真波形

第23页/共27页

巴克码信号发生器

实验要求 (1)可循环产生产生巴克码信号 (2)可控制信号发生器的启动和停止

设计思路 由实验要求可以得,将巴克码01110010逐个赋给一

个信号,并通过二进制信号s来控制循环产生巴克码,当 s=000时,产生巴克码的第一个数,s+1,当s为111时, 将s清零成000,开始产生新一轮的巴克码。

第24页/共27页

VHDL源程序

第25页/共27页

仿真波形Байду номын сангаас

第26页/共27页

感谢您的欣赏!

第27页/共27页

单脉冲发生器 原理图

M

单脉冲发

Q

生器

PUL

第1页/共27页

单脉冲发生器VHDL源 程序

第2页/共27页

波形仿真图

第3页/共27页

节拍脉冲发生器用来产生计算机工作所需的节拍脉冲 ,当给START一个高电平脉冲时,节拍脉冲发生器启 动,从P0~P3输出节拍脉冲:当给STOP一个高电平脉 冲时,节拍脉冲发生停止输出节拍脉冲,当给RESET 一个高电平时,节拍脉冲发生一组节拍脉冲

第10页/共27页

➢ 设计分析

首先确定 256X8 ROM 用到了8位 二进制端口即可访问256个存储单 元(也就是说有256个地址),然 后用低四位作并联在16个例化的 ROM 的四位地址端口,并将高四 位接在一个4—16译码器上,作为 位选端口, 译码器的输出端分别接 在16个ROM的en使能位。最后用 一个16选一的数据选择器将译码器 使能的那块ROM的输出端(8位) 作为 256X8 ROM 的输出端口或者

VHDL语言介绍与设计

“X ”—不定 “1”—1 “W”—弱信号不定 “H”—弱信号 1 “_”—不可能情况 注意在使用该类型数据时, 在程序中必须写出库说明语句和使用包集合的说 明语句。 3. 用户定义的数据类型 1.1.3 VHDL 语言的运算操作符 在 VHDL 语言中共用 4 类操作符,可以分别进行逻辑运算(Logic) 、关系 运算(Relational) 、算术运算( Arithmetic)和并置运算(Concatenation) 。被操 作符所操作的对象是操作数,且操作数的类型应该和操作符所要求的类型相一 致。需要注意的是,各家 EDA 综合软件对运算操作符支持程序各不相同,使用 时应参考综合工具说明。 1) 逻辑运算符 运算符在 VHDL 语言中逻辑运算符有 6 种,他们分别为: NOT(非) AND(与) NAND(与非) OR(或) NOR(或非) XOR(异或) 2) 关系运算符 关系运算符它们分别是: =(等于) /=(不等于) <(小于) <=(小于等于) >(大于) >=(大于等于) 3) 算术运算符 +(加) -(减) *(乘) /(除) MOD(求模) REM(取余) SLL(逻辑左移) SRL(逻辑右移) SLA(算术左移) ROR(逻辑循环右移) ABS(取绝对值) 4) 其他运算符 <=(信号赋值) :=(信号赋值) -(负) + (正) & (并置运算符,用于位的连接) =>(并联运算符,在元件例化时可用于形参到实参的映射) 1.2 VHDL 语言的结构 VHDL 语言主要组成构件有设计实体( Entity) 、构造体(Architecture) 、 子 程序( Function Procedure ) 、集合包(Package )和库(Library ) ,前四种称为 可编译的设计单元。一个 VHDL 设计就是有这四种构件的组成,编译之后将它 们放在制定的库中共享。其中,实体用于描述设计的接口界面信号,它规定端口 数目,端口方向和端口类型。它与硬件电路设计中 的符号相对应。而结构体指定设计的真实行为,性能和结构,与硬件电路设计中 的原理图相对应。 子程序是可被调用的执行某一特定功能算法的集合。集合包则 是为了使常用的数据类型、 常数和子程序对于其他设计块可用而集中存放的一批 设计单元和约定。

巴克码序列检测

物理与电子工程学院 廖磊

设计要求

某通信接收机的同步信号为巴克码 1110010。 设计一个检测器,其输入位串行码x,输 出位检测结果y,当检测到巴克码时,输 出1。

巴克码序列检测器状态转换图

设计范例

library ieee; use ieee.std_logic_ll64.all; entity jcq is port (clk, Xiபைடு நூலகம் in std_logic; Z: out stdJogic ); end jcq; architecture archjcq of jcq is type StateType is (S0, Sl, S2, S3, S4, S5, S6, S7); signal present_state, next_stat: StateTyPe; begin

双进程状态机模型

输出信号 外界输入信号

下一状态

当前状态信号

状态 译码 PROCESS1

下一状态

状态 当前状态信号 寄存器

时钟信号

PROCESS2

END

state_clk: process (clk) begin if (clk'event and clk =' l ' ) ) then present_state <= next_state; end if; end process state_clk; end archjcq;

波形仿真

序列检测器仿真波形

设计范例(续)

when S5 => Z <= ' 0 '; if Xi =' l ' then next_state <= S6; else next_state <= S0; end if; when S6 => Z <= ' 0'; if Xi = ' l ' then next_state <= S2; else next_state <= S7; end if; when S7=> Z <=' l '; if Xi = ' 1 ' then next_state <= Sl ; else next_state <= S0; end if; end case; end process state_comb;

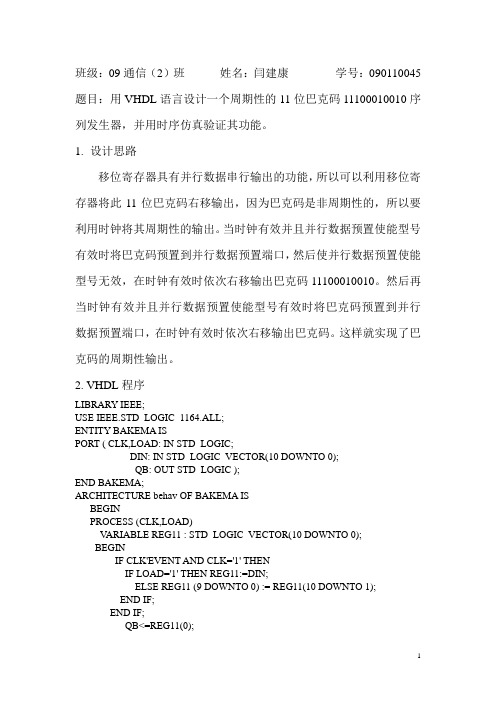

用VHDL语言设计一个周期性的11位巴克码11100010010序列发生器

班级:09通信(2)班姓名:闫建康学号:090110045 题目:用VHDL语言设计一个周期性的11位巴克码11100010010序列发生器,并用时序仿真验证其功能。

1.设计思路移位寄存器具有并行数据串行输出的功能,所以可以利用移位寄存器将此11位巴克码右移输出,因为巴克码是非周期性的,所以要利用时钟将其周期性的输出。

当时钟有效并且并行数据预置使能型号有效时将巴克码预置到并行数据预置端口,然后使并行数据预置使能型号无效,在时钟有效时依次右移输出巴克码11100010010。

然后再当时钟有效并且并行数据预置使能型号有效时将巴克码预置到并行数据预置端口,在时钟有效时依次右移输出巴克码。

这样就实现了巴克码的周期性输出。

2. VHDL程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BAKEMA ISPORT ( CLK,LOAD: IN STD_LOGIC;DIN: IN STD_LOGIC_VECTOR(10 DOWNTO 0);QB: OUT STD_LOGIC );END BAKEMA;ARCHITECTURE behav OF BAKEMA ISBEGINPROCESS (CLK,LOAD)V ARIABLE REG11 : STD_LOGIC_VECTOR(10 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF LOAD='1' THEN REG11:=DIN;ELSE REG11 (9 DOWNTO 0) := REG11(10 DOWNTO 1);END IF;END IF;QB<=REG11(0);END PROCESS;END behav;3.仿真波形4. 程序分析该程序描述的是一个带有同步并行预置功能的11位右移移位寄存器。

CLK是移位时钟信号,DIN是8位并行预置数据端口,LOAD 是并行数据预置使能信号,QB是串行输出端口。

用VerilogHDL设计可辨别相位模糊的巴克码识别器

用VerilogHDL设计可辨别相位模糊的巴克码识别器

张伟

【期刊名称】《现代电子技术》

【年(卷),期】2004(27)7

【摘要】使用Verilog语言描述了可辨别2PSK相位模糊的巴克码识别器,给出了时序仿真波形,并探讨了完整帧同步电路的实现方法.

【总页数】2页(P45-46)

【作者】张伟

【作者单位】解放军理工大学,通信工程学院,江苏,南京,210007

【正文语种】中文

【中图分类】TP311

【相关文献】

1.巴克码识别器的设计与FPGA的实现 [J], 龙光利

2.基于数字量设计的环网柜用通用型相位识别器的研究与设计 [J], 苏秋丽

3.一种模糊识别器的设计方案 [J], 符海东;袁细国

4.三元阵相位干涉仪无模糊基线设计 [J], 肖香彬;杜冶;任峰

5.基于模糊函数的MIMO雷达跳频相位编码波形设计 [J], 刘锦;杨德贵;梁步阁;朱政亮;赵锐

因版权原因,仅展示原文概要,查看原文内容请购买。

VHDL代码设计规范

签名签名编制审核部门部门签名审核签名审核加盖受控章部门部门签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门签名签名审核审核部门部门审批批准生效日期:签名签名文件编号文件标题现行版本VHDL 代码设计规范V1.0版次编制日期更改内容(条款)文件编号:编制:审核:文件编号:编制:审核:可靠性审核:标准化:批准:........................................................................................................................................................................................................................................................................................................................................................................................................5.1. 书写规范 (3)5.1.1. 命名规范...................................................................... 3..5.1.2. 注释规范...................................................................... 5..5.1.3. 其他书写规范..................................................................6..5.2. 设计规范 (6)5.2.1. 复位..........................................................................6..5.2.2. 时钟.......................................................................... 7..5.2.3. 状态机........................................................................ 7..5.2.4. 异步信号...................................................................... 7..5.2.5. 其他设计规范.................................................................. 8..5.3. 设计常识 (9)................................................................................6.1. 例子说明(规范详细解释) (9)6.2. 代码模板 (18)规范 VHDL 的设计风格,保证代码的可读性、重用性及与现有 EDA 工具的一致性,从而形成对设计代码的标准化管理。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

巴克码检测器设计

一.目的

(1)了解通信领域中经常使用的巴克码检测器的设计方法

(2)掌握使用状态机设计时序电路的方法

三.说明

巴克码检测可通过多种方法实现,实验中检测的串行码组可用脉冲按键输入,输入的检测结果由发光二极管火数码管指示。

三.源程序

ST0表示0;

ST1表示1;

ST2表示11;

ST3表示111;

ST4表示1110;

ST5表示11100;

ST6表示111001;

ST7表示1110010;

状态转移图:

巴克码检测的VHDL程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY JCBKM IS

PORT(CLK:IN STD_LOGIC;

D:IN STD_LOGIC;

Y:OUT STD_LOGIC);

END JCBKM;

ARCHITECTURE BHV OF JCBKM IS

TYPE STATE_TYPE IS (ST0,ST1,ST2,ST3,ST4,ST5,ST6,ST7);

SIGNAL P_STATE,N_STA TE:STATE_TYPE;

BEGIN

REG:PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1') THEN P_STATE<=N_STATE;

END IF;

END PROCESS;

COM:PROCESS(P_STATE,D)

BEGIN

CASE P_STA TE IS

WHEN ST0=>Y<='0';

IF(D='1') THEN N_STATE<=ST1;

ELSE N_STATE<=ST0;

END IF;

WHEN ST1=>Y<='0';

IF(D='1') THEN N_STATE<=ST2;

ELSE N_STATE<=ST0;

END IF;

WHEN ST2=>Y<='0';

IF(D='1') THEN N_STATE<=ST3;

ELSE N_STATE<=ST0;

END IF;

WHEN ST3=>Y<='0';

IF(D='1') THEN N_STATE<=ST3;

ELSE N_STATE<=ST4;

END IF;

WHEN ST4=>Y<='0';

IF(D='1') THEN N_STATE<=ST1;

ELSE N_STATE<=ST5;

END IF;

WHEN ST5=>Y<='0';

IF(D='1') THEN N_STATE<=ST6;

ELSE N_STATE<=ST0;

END IF;

WHEN ST6=>Y<='0';

IF(D='1') THEN N_STATE<=ST2;

ELSE N_STATE<=ST7;

END IF;

WHEN ST7=>Y<='1';

IF(D='1') THEN N_STATE<=ST1;

ELSE N_STATE<=ST0;

END IF;

END CASE;

END PROCESS;

END BHV;

四、仿真结果

其中D,CLK为输入端,Y为输出端,在监测到有连续的1110010来时,Y 输出一个高电平。

仿真波形图为:。