Power-aware RAM mapping for FPGA embedded memory blocks

Conformal_Verification_Guide_8.1

I N VE N TI V ECONFIDENTIALFormal Verification GuidePrototype | Implement | VerifyAgenda• Equivalence Checking Refresh • Verification Guide– RTL Design – Verifiable Synthesis Flow – Abort Resolution• ECO Automation • Best Practice Recommendation2August 6, 2009Cadence ConfidentialEncounter Conformal Product FamilyVerifies 100% of design functionality without requiring test vectors Provides independent verification for lowest risk silicon Validates CPF LP Equivalence Checking Verifies Low Power design implementation Performs structural and functional checksEquivalence CheckingRTL or Gate RTL or GateDigital Custom Verification including Memories, Data Paths, and IO Orders of magnitude faster than simulationLow Power VerificationFunctional Checksv1v2ISOABFinds bugs earlier in the design cycle Verifies proper CDC synchronization to avoid clock related re-spins Creates safer EC environmentValidation, generation and analysis of constraints Uses industry proven formal engines Shorter design cycle with improved timing constraintsConstraint DesignECO Implementationo1 o2Provides automated RTL2GDS ECO solution Identifies and generates fix to implement ECO Interfaces with physical implementation tool flow3August 6, 2009Cadence ConfidentialEncounter Conformal & FED Product FamilyEquivalence CheckingRTL or Gate RTL or GateConstraint DesignLow Power VerificationFunctional ChecksAValidation, generation & analysis of constraints Shorter design cycles with improved timing constraintsv 1v2ISOB100% Independent vector-less verification of implementation RTL Gate Transistor CDC & Ext ChecksStructural and functional LP checks LP design implementation Verification LP Equivalence CheckingNew Products ECO Implementation RC-Physical Synthesis Chip Planning Systemso 1 o 2Automated RTL2GDS ECO solution Identifies and generates ECO fix Physical Correlation & Predictability with final backend Congestion Analysis & Opto (Congestion Relief) Architectural & Economic Forecasting Lower IC Cost & Expedite TTM4August 6, 2009Cadence ConfidentialI N VE N TI V ECONFIDENTIALCrash Course on Equivalency CheckingPrototype | Implement | VerifyEquivalence Checking FlowGolden Design Standard Library Revised DesignSpecify Constraints and Design ModelingSetup Mode LEC ModeSpecify Compare ParametersCompare DesignsMiscompare?yesDiagnosenoEquivalence Checking Complete6August 6, 2009Cadence ConfidentialMapping! What is that?Pairing corresponding golden and revised key points:G RPI PO DFF DLAT BBOX CUT Z EPI PO DFF DLAT BBOX CUT Z E Key points Combinatorial logicGolden RevisedE UExtra Points Unreachable Points Unmapped Points7August 6, 2009Cadence ConfidentialComparison– Only mapped points can be compared. – Comparison is an iterative process.• Conformal remembers points already compared. • Comparison can be interrupted with Control-c. • Enter compare to continue comparing.set log file logfile.$LEC_VERSION -replace add notranslate module *sram* -library -both read design cpu_rtl.v -verilog -golden read design -file verilog.vc -verilog -revised // Command:pin constraint 0 scan_en -revised add compare ================================================================================ set flatten model -latch_fold Compared points PO DFF DLAT BBOX Total add renaming rule rule0 "abc" "xyz" -map -revised -------------------------------------------------------------------------------Equivalent renaming rule rule1 "xyz" "C" -map -golden 2 146 2 1 151 add -------------------------------------------------------------------------------set system mode lec Non-equivalent 0 2 0 0 2 add compare points -all ================================================================================ compare ...8August 6, 2009Cadence ConfidentialUsing the Mapping Manager to Debug NEQsMain windowUnmapped pointsMapped pointsCompared points9August 6, 2009Cadence ConfidentialCategories of Comparison ResultsEquivalent: Key points proven to be equivalent (green-filledcircle)Inverted-Equivalent: Key points proven to be complementary (divided green-filled circle) Nonequivalent: Key points proven to be different (red-filled circle) Abort: Key points not yet proven equivalent or nonequivalent due to timeout or other system parameters (yellow-filled circle) Not-Compared: Key points not yet compared?10LEC> report compare data -class [...]August 6, 2009Cadence ConfidentialI NVENTIVE CONFIDENTIAL RTL DesignFor Ease of VerificationRTL Design For Ease of Verification•To highlight the impact of RTL design on verification –Useful for RTL designers to understand their impact of coding styles on verification–Useful guidelines for machine/script generated RTL codes •Factors in RTL designs that can affect the ease of verifications are–Don’t care conditions in RTL description–Structuring of logics–Partitioning of designsRTL Design For Ease of VerificationDon’t-Cares Conditions in RTL•Don’t-care conditions are created in RTL by–X assignments–Incomplete case–Out-of-range indexing–Range constraint (VHDL)• A don’t-care condition can be synthesized to– a constant (zero or one)–or any Boolean function•Designs with extensive don’t-care conditions can be difficult to verify •Use LEC “report design data”to report don’t cares•Use LEC “report rule checks”to report out-of-range indexingRTL Rule Checkers•LEC’s RTL rule checker provides an fast and easy way to detect RTL coding styles that can impact verification •For example, index out of range is reported as –// Warning: (RTL7.3) Array index in RHS might be out of range (occurrence:1)•Running LEC RTL rule checker early in the RTL design process can reduce many potential synthesis andverification issues later onRTL Rule CheckersSETUP> read design –golden rtl.vSETUP> read design –revised rtl.vSETUP> set system mode lecSETUP> report rule check –golden –design –verbose > lint.rptSETUP> report message –golden –model –verbose > model.rpt•Consider Synthesis and EC ramifications of design –Multiply-driven and floating nets–Combinational cycles–Assignment size mismatch–Ambiguities leading to simulation mismatches–EtcRTL Design For Ease of VerificationDon’t-Cares Due to Index Out of Range•Don’t care is created when index is out of range –When the index can address more locations thanwhat an array can hold•For examplereg[4:0] q; // q has 5 locationsReg[2:0] A; // A can index 8 locationsBAD -q[A];// (1) out-of-range conditionGOOD -q[(A> 4) ? 0: A)];// (2) No out-of-rangeLogic Structuring•Structural Similarity–How closely does RTL structure match the netlist •Designs with higher structural similarity between RTL and netlist are easier to verify•Synthesis can restructure code. For examples:–Resource sharing–Map unsigned operators to signed operators•Minimize structural differences between RTL and netlist by:–Using Verilog 2K to code signed arithmetics–Using explicit grouping (such as in additions) with parenthesis –Manually code resource sharingDesign Partitioning•Partitioning a complex block breaks it into smaller pieces for ease of verification•Guidelines–Keep high complexity design modules small in size–Avoid excessive logic cone depth–Separate datapath block (especially those requiring retiming) from control block–Partitioning may impact QOR so the tradeoffs should be explored early in the design cycle•Smaller blocks are easier to verify. Well partitioned designs can also make use of more techniques to ease verificationsI NVENTIVE CONFIDENTIAL Verifiable Synthesis FlowModule Data PathArchitecture & Advanced Synthesis Optimizations Create Verification Challenges DatapathArchitectureBoundary OptimizationPhase Inversion Resource Sharing• A synthesis flow with verification considerations can significantly reduce verification challenges–Enable the identification of synthesis bugs more easily–Allow use of more LEC features (e.g., module-based datapath analysis, hierarchical comparisons) to streamline the verification processL E CSynthesis Optimization on Datapath Modules•Synthesis tools like RC and DC can group several datapath operators into asingle datapath unit which called datapath module. These modules can be synthetic or they can be instantiated components such as DW modules•For Design Compiler, these modules are reported in the resource report with string DP_OP as naming convention•These modules boundary are not preserved if ungrouping and boundary optimization are applied, making them difficult to prove Synthesis Flow Needs To Be Verification-Friendly R T L D a t a p a t h D e si g n ungroup/boundary optimizationMulti-Stage Synthesis•The basic principle of ensuring ease of verification is to break difficult to verify synthesis optimizations intostages in the synthesis flow•Recommend synthesis stages–RTL to first mapped netlist•Enable: datapath synthesis•Disable: ungrouping, boundary optimizations, phase inversions –Mapped netlist to optimized mapped•Enable: Ungrouping, Incremental optimizations, boundaryoptimizationsEmbed Verification Requirements in Synthesis •To deploy an easy to verify synthesis flow, embed the verificationsinto the synthesis scripts–Instead of resynthesizing after running into verification challenges •Control synthesis options that impact verification, e.g.,–Range constraint–Datapath synthesis, resource sharing–Ungrouping, boundary optimizations•Allow for a range of verification requirements to allow for trade-offs in verifiability•This is default behavior for Encounter RTL Compiler (RC)LEC Feature Module Based Datapath (MDP) Analysis (DC Synthesis)•Datapath synthesis may cause aborts because of operator optimization.•This is handled in RTL Compiler with Netlist Verification (more later). DC netlists require MDP.•Module-Based Datapath (MDP) Analysis performs datapath abstraction at a module level•This analysis is performed in addition to and prior to the regular operator level analysis•The result goal is to improve the quality of the operator-level analysis•Requires the preservation of synthetic datapath modules during synthesisRTLRTLFinal GateDC Script LE C DC Script Original Flow New Flow RTL FinalGate DC + MDP Script Intermediate Gate L E C LE C •Include MDP Script •Output Intermediate &Final Netlist•Perform RTL2Gate•Perform Gate2Gate Improve Synthesis Script to Ensure Verification Success (MDP) Analysis (DC Synthesis)DC Synthesis Script to Enable MDP Analysis•To enable the successful verification of datapath design using Design Compiler synthesis, LEC provides a script to ensure that LEC’s Module-Based Datapath (MDP) Analysis can be effectively applied•The script can be embedded into the overall synthesis script as followssource <lec_release_path>/share/cfm/lec/scripts/mdp.tcl…compile_ultra_mdp<level> <design_module>compile_ultra……<continue original DC synthesis script commands>…•compile_ultra_mdp command is placed before the first compile_ultra command in the DC script•Design module is the name of the top module that is synthesizedDC Synthesis Script for Datapath Verification •MDP level can be 1, 2, 3, or 4, and affects the synthesis as followsMDP Level Preserve Hierarchy ofBoundaryOptimizationSequentialOutputInversion DP/DW Design1YES NO ALLOW ALLOW 2YES NO DISABLE ALLOW 3YES NO DISABLE DISABLE 4YES YES DISABLE DISABLECollecting DC Synthesis Data•During the synthesis process, the following information should be collected for verification–Datapath Resource File: This is required to ensure that datapath intensive design can be easily verified–Change Name File: This is required to ensure name-based mapping for ease of verification–VSDC File: This file contains information that can help to guide the setup of the verification–Synthesis log file: This can contain information to help guide the setup of the verificationLEC Feature Qualifying Your DC Synthesis Environments •New versions of synthesis tools may introduce new verificationrequirements–New optimization techniques (e.g., sequential constant groups)–New datapath structures (e.g., new multiplier architectures)–New technology mapping techniques (e.g., using multi-bit library cells)–Changes in naming conventions (e.g., in generate statements)–Changes in default synthesis option settings (e.g., having sequential merge optimizations ON by default)•LEC ships with IP-free designs that can be used as testcases in a new synthesis environment or tool–Enable users to provide early feedbacks to the Conformal team to ensure success of verifications in the latest synthesis environment –At $conformal_dir/share/cfm/lec/demo/*How to Determine QoR ImpactRTL RTLFinalGate DC ScriptL E CDCScriptOriginal FlowNew FlowRTLRTLFinalGateDC ScriptDC + MDPScriptIntermediateGate L ECL E CQoR ImpactRC Netlist Verification Flow• RC verification flow– Only one intermediate netlist between RTL code and the final netlist – Two LEC comparisons: RTL-to-Intermediate & Intermediate-toFinal – Better support of advanced (datapath) optimizations – LEC-friendly netlist by 'write_hdl –lec’• additional datapath info (as comments) about architecture changes31August 6, 2009Cadence ConfidentialRC Netlist Verification Flow•Synthesize with no ungrouping •Output Intermediate & Final Netlist •Perform RTL2Gate •Perform Gate2GateNew Flowwrite_hdl -lecRTLFinal GateEC LIntermediate GateEC LIntermediate netlist to Ensure Verification Success32August 6, 2009Cadence ConfidentialRC Netlist Verification Flow for Datapathread_hdl elaborate read_sdcFirst netlist generated with “-lec” optionsynthesize -to_mapped write_hdl -lec > intermediate.v write_do_lec -revised intermediate.v > rtl2map.do [ungroup in any way] <no more datapath architecture change> Do not ungroup before first netlistsynthesize -incr as many times as wished without “-lec” option; write_hdl > final.v write_do_lec -golden intermediate.v -revised final.v > map2final.do exit Every “write_hdl” followed by “write_do_lec”33August 6, 2009Cadence ConfidentialRC Netlist Verification Flow for Datapath• First LEC run (RTL-gate):read design <RTL_code> -golden read design intermediate.v -revised compare – write_do_lec generates a hierarchical dofile script (rtl2map.do) – Conformal dofile script will contain the following commands: analyze datapath –module –verbose analyze datapath -verbose• Second LEC run (gate-gate):read design intermediate.v -golden read design final.v -revised compare – write_do_lec generates a flat dofile script (map2final.do)34August 6, 2009Cadence ConfidentialSummary• When a design is complex and contains many datapath operators, with today’s advance synthesis optimizations, the datapath become structurally different between RTL and netlist, creating challenge to all verification tools • To effectively help Conformal datapath analysis quality and improve verification result, an integrated synthesis & verification flow is needed • DC MDP Analysis and the recommended synthesis script will help close the gap between datapath synthesis and verification • RC Netlist Verification flow reduces the chance of aborts for a more complete verification35August 6, 2009Cadence ConfidentialI N VE N TI V ECONFIDENTIALAbort ResolutionResolving Aborts• Abort is reported when formal (exhaustive) analysis cannot provide a complete proof of equivalence within a resource limit– The design has been partially verified since no input vector resulting in non-equivalence has been found either• Resource limit is adjusted by compare effort– SET COMPARE EFFORT <LOW|MED|HIGH|COMPLETE>• This section describes– Techniques to resolve aborts – Methods to isolate abort to better understand the aborted region and options for further verifications37August 6, 2009Cadence ConfidentialResolving AbortsReview Synthesis Flow• Abort can be avoided by following the guidelines given earlier • For datapath intensive design– Check that MDP level 4 has been used for DC synthesis – Use Netlist Verification Flow for RC synthesis• RTL design for ease of verification– Check for excessive don’t care conditions with LEC’s rule checker and design report• Partition the design well and use LEC’s hierarchical comparison– Check that all complex modules can be hierarchically compared38August 6, 2009Cadence ConfidentialResolving AbortsReview LEC Dofiles• Hierarchical Comparison– Check that hierarchical comparison is used – For module containing abort, check that it has no submodules that can be further hierarchically compared• For datapath intensive design– Check that MDP has been used (Analyze datapath –module) – Check that datapath analysis are successful• Abort Analysis– Check that LEC’s abort analysis has been used (analyze abort)• Multithreading– Check that multithreading is used for abort analysis39August 6, 2009Cadence ConfidentialResolving AbortsAdvanced LEC Techniques• Several advanced techniques are available to resolve aborts • Advanced options for ‘analyze datapath’– – – – -wordlevel -share -effort high -addertree• Advanced commands and techniques– run partition_compare (help run partition_compare –verbose) – add partition points – read design –norangeconstraint –vhdl40August 6, 2009Cadence ConfidentialRe-synthesis and RTL Recoding•Re-synthesis of problem blocks–Adjust effort level–Disable range constraints–Preserve key signals and boundaries •Pros–Makes verification easy for all future runs •Cons–Requires additional efforts, may impact qualityAbort Isolation•When aborts cannot be completely resolved, it is useful to identify the region where aborts occurred–Allow for a more targeted re-synthesis–Allow for a better understanding on the netlist that leads to abort –Allow for additional verification to these smaller regions •Techniques to isolate abort–Ensure that the modules are hierarchically compared•Easier if RTL is partitioned well–In MDP analysis flow, abstracted datapath cluster can be automatically isolatedAbort Isolation for Datapath Module •When using MDP analysis, LEC can isolate the datapathmodule that causes the abort so that the remaining non-aborting netlist can be verified–That is, if the remaining netlist is equivalent and the datapath module is also equivalent, then the entire netlist is equivalent •Provides more visibility into the region of abort –Instead of reporting all fanout keypoints from the datapath module as abort, only the datapath module is reported as abort(See next slide)•The is invoked as–ANALYZE DATAPATH –isolate_abort_module…Abort Isolation for Datapath Module •Results with abort:==============================================================Compared points PO Total--------------------------------------------------------------Abort 67 67==============================================================•Results with abort isolation:==============================================================Compared points PO Total--------------------------------------------------------------Equivalent 67 67==============================================================Compared results of isolated instances in Revised design (top)==============================================================Status Instance (Module)--------------------------------------------------------------Abort i5/add_123_S1_DP_OP_123_456(NV_GR_PE_STRI_core_add_123_S1_DP_OP_123_456) ==============================================================Multi-Threading•For machines with multi-core CPUs–No need to set up the parallel processing environment–Takes advantage of multi-core, multi-CPU machines •Parallel ComparisonLEC> compare –threads #•Best for large gate-to-gate comparisons, where the comparison canbe distributed to multiple comparison threadsLEC> analyze abort –compare –threads #•Best for RTL-to-gate comparison aborts, where a few keypoints canconsume a large portion of the runtime*Obsoletes the previous method of parallel comparisons using the command Run Parallel Compare•Support two new multiplier architectures •Improve divider architecture analysis•Support higher effort analysis for better datapath learning quality.Results from sample testcasesRadix-8Unsigned DividerHigh Effort AnalysisDatapath AnalysisI NVENTIVE CONFIDENTIAL ECO AutomationPrototype | Implement | VerifyECO ChallengesNomenclature•Engineering Change Order (ECO) is the process of making local changes to the design netlist without re-running the entire synthesis and P&R flow•ECO Types–Functional ECO•Changes the functionality of the design–Non-functional ECO•Fix timing, cross talk, DRV, routing violations with minimal effort•ECO Stages–Pre-Mask ( Pre tape-out) ECO•Uses normal logic gates to implement change–Post-Mask (Metal-only ECO)•Uses spare gates only to implement changeECO ChallengesManual Task•Current ECO flows are manual–Process is very time and resource consuming–Error Prone–Limited by ECO size•Very difficult to identify location of needed fix–Easy to modify RTL, yet difficult to transfer fix to gate netlist•Manual ECO changes do not easily incorporate use of –Spare gates, location, timing, routing access–Freed cells (used originally but not used in ECO patch)•Hard to manually optimize the eco patchECO ChallengesManual Flow Targeting Post Mask ECOSynthesisNew RTL (R2)Old RTL (R1)Old Netlist (G1)Final Netlist (New DEF)ECO Route/DRV/SIOld DEFP&RManual EditingTest InsertionNew Netlist(G2)ECECDelete/add connections Map to spare gatesDifficult to identify where to fix!Which logic cones are affected?P&RWhat type/many spare cells are available and how can I optimally map new gates to them?Use limited Metal Layers!How can I get the smallest possible change?Create ECO CmdWill this ECO meet timing, is it DRC clean?ORB a c k -e n d EC Or o n t -e n d E C ORepeat process for each ECO。

PM5461-KIT PSX PFX PFX-I PFX-L 96 80 64×G3 PCIe Sw

PM5461-KITPSX/PFX/PFX-I/PFX-L 96/80/64×G3PCIe® Switch HD Evaluation KitHighlightsPCIe Interface• 1 ×16 edge connector for connection to a host• 1 ×16 slot connector for add-in cardsMini-SAS HD• 8 SFF-8644 external mini-SAS HD connectors• 8 SFF-8643 internal mini-SAS HD connectorsPCIe Clock Interface• Common reference clock with or without spread spectrumclocking (SSC)• Separate reference clock no SSC (SRNS)• Separate reference clock with independent SSC (SRIS)Serial Peripheral Interfaces (SPI)• 2 quad SPI buses• 128 Mb on-board SPI Flash for bootup and initializationThe Microchip name and logo and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies. © 2020, Microchip Technology Incorporated. All Rights Reserved. 12/20 DS00002850BPeripheral I/O Interfaces• 11 two-wire (TWI)/SMBus interfaces• 128 Kbps SEEPROM for storage and PCIe switch configuration • TWI bus access and connectivity to the temperature sen-sor, fan controller, voltage monitor, GPIO and TWI expand-ers, PCIe connectors, iPass Sideband and FPGA• 109 GPIOs with 3 dedicated as GPIOs and 106 GPIOs are multiplexed to provide TWI, SPI, SGPIO, Ethernet and UART interfaces• UART access using USB Type B and 3-pin connector header • 14-pin EJTAG connector header for Green Hills Software probe connectivity•10/100 Mbps Ethernet supporting MII and RMIIFPGA and CPLD Functionality • Drive board status LEDs• Monitor interrupts from I/O expanders and PCIe SFF cables• Provide Adaptive Voltage Scaling (AVS) control signal to device and regulators• Control and monitor power regulator output •Manage board and switch resetLocal Bus Interface (LBI)—PSX Only• 4 chip selects mapping to a unique 16 MB memory interface• 128 Mb of on-board NOR flash memory for storage of firmware image•16 Mb of on-board SRAM for extended command/data RAMPower Supply• 0.925 V and 1.8 V power rails supplied by on-board regulators • PCIe switch sense points for monitoring and measuring power rail voltages•12V power provided through 8-pin CPU power connector or 6-pin PCIe connector or PCIe edge connector (add-in card)PSX Software Development Kit• The PSX software development kit allows development and test of custom PCIe switch functionality• The PSX SDK relies on the Green Hills MULTI ® develop-ment environment available directly from Green Hills Software•The EJTAG debugger supports test and debug of custom PSX firmwareChipLink Diagnostic ToolsThe ChipLink diagnostic tools software provides the following:• Access to registers in the PCIe switch• Configuration of high-speed analog settings for signal integrity evaluation• Monitoring of status and mode indicatorsNote: For PFX-I, only functional evaluation is possible because commercial temperature parts are populated on the evalua-tion board.Kit ContentsThe following contents are included with the PM5461-KIT:• PSX/PFX/PFX-I/PFX-L Gen3 PCIe Switch HD Eval Board • SFF-8644 (×4) external to SFF-8639 multi-link 1 m cable • SFF-8643 (×4) internal to SFF-8639 multi-link 1 m cable • SFF-8644 (×4) external to SFF-8644 (×4) external 1 m cable • SFF-8643 (×4) internal to SFF-8644 (×4) external 1 m cable • iPass internal-to-internal 1 m cable and SATA-to-SATA cable • 3-wire to serial 1 m UART cable• Evaluation kit software installation files and user's guide • Power supply and USB-RS232 cableKit Requirements (Supplied Separately)Required for operation of the kit and must be supplied separately:• Personal computer running Windows, Linux, or Mac OS • ATX 750 W power supply, 1 × 6-pin PCIe connect and one 8-pin CPU power connector (Microchip recommends a Corsair CX750M ATX power supply)Optional (Supplied Separately)The following optional items must be supplied separately:• NVMe/PCIe SSD• High-speed oscilloscope for performing eye-diagram measurements• Jitter analyzer for analyzing jitter components• For PSX only: Green Hills MULTI development environ-ment and EJTAG debugger for firmware developmentOptional Evaluation Kit Adapter CardsNot included with the kit but available as separate purchases:• ADP_1×16SLOT_4×4HD: PCIe Gen3 1×16 slot to 4×4 HD • ADP_EDGEG4: PCIe Gen3/Gen4 1x16 Edge to 4x4 OcuLink Adapter Board Converts a x16 Edge PCIe Interface to an OCuLink PCIe interface or vice-versa• ADP_SLOTG4: PCIe Gen3/Gen4 1x16 Slot to 4x4 OcuLink Adapter Board Converts a x16 Slot PCIe Interface to an OCuLink PCIe Interface or vice-versa。

Himax HM01B0 UPduino 芯片说明书

HM01B0-UPD-EVNHimax HM01B0 UPduino Shield User GuideFPGA-UG-02081 Version 1.0November 2018Himax HM01B0 UPduino ShieldUser GuideContentsAcronyms in This Document (3)1.Introduction (4)1.1.Further Information (4)2.Power Supply (5)3.Board Overview (5)4.iCE40 UltraPlus Pin Summary (7)5.Software Requirements (9)6.Board Configuration and Programming (9)6.1.Board Configuration (9)6.2.Programming the SPI Flash (10)6.3.Programming the CRAM Directly (11)7.Storage and Handling (13)8.Ordering Information (13)References (14)Technical Support Assistance (14)Appendix A. Himax HM01B0 UPduino Shield Board Schematics (15)Revision History (19)FiguresFigure 1.1. Himax HM01B0 UPduino Shield (4)Figure 3.1. UPduino v2.0 – Front View (5)Figure 3.2. UPduino v2.0 – Back View (5)Figure 3.3. Himax HM01B0 Adapter Board – Front View (6)Figure 3.4. Himax HM01B0 Adapter Board – Back View (6)Figure 6.1. Programming Settings (9)Figure 6.2. Device Family and Device Setting (10)Figure 6.3. Onboard SPI Flash Device Properties Settings (11)Figure 6.4. Device Family and Device Settings (12)Figure 6.5. Device Properties for iCE40 Device Configuration Memory (12)Figure A.1. UPduino 2.0 FPGA Schematic (15)Figure A.2. UPduino 2.0 SPI Flash/I/O Pins/Regulator Connections (16)Figure A.3. UPduino 2.0 FTDI Chip Connection (17)Figure A.4. Himax HM01B0 Adapter Board Schematic (18)TablesTable 4.1. Upstream Connector Mapping (7)Table 8.1. Reference Part Number (13)© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.2 FPGA-UG-02081-1.0Himax HM01B0 UPduino ShieldUser Guide Acronyms in This DocumentA list of acronyms used in this document.Acronym DefinitionFPGA Field-Programmable Gate ArrayFTDI Future Technology Devices InternationalI²S Inter-IC SoundLED Light-Emitting DiodeSOIC Small Outline Integrated CircuitSPI Serial Peripheral InterfaceUSB Universal Serial Bus© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-UG-02081-1.0 3Himax HM01B0 UPduino ShieldUser Guide© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal .All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.4 FPGA-UG-02081-1.01. IntroductionThe Himax HM01B0 UPduino Shield is an evaluation and development platform based on the iCE40™ UltraPlus FPGA (Field-Programmable Gate Array). It consists of two boards – the UPduino v2.0 and the Himax HM01B0 Aapter Board. The UPduino v2.0 is an efficient, low-cost base platform designed by Gnarly Grey, including the iCE40UP5K FPGA, and basic power and programming control. The Himax HM01B0 Adapter Board adds a camera with a low-power Himax image sensor, two microphones, and multiple LEDs for quick visual feedback.This flexible and powerful platform enables designers to investigate and experiment with key features of the iCE40 UltraPlus FPGA and assists with rapid prototyping and testing of specific designs.Key features of the Himax HM01B0 UPduino Shield include: ∙ UPduino v2.0∙ iCE40 FPGA - iCE40UP5K-SG48I (5K LUTs, 39 I/Os, 120 Kbits Embedded Block RAM, 1 PLL and more in a 7 mm x7 mm 48-pin QFN package.)∙ USB connection for UART and device programming ∙ On-board Boot Flash ∙ RGB LED∙ Himax HM01B0 Adapter Board∙ Camera module with Himax HM01B0 image sensor ∙ Two I 2S microphones ∙ Six green LEDs∙ Also included with the kit∙ 3 ft Micro USB cable for programming and power ∙ QuickStart GuideFigure 1.1. Himax HM01B0 UPduino Shield1.1. Further InformationThis board features an iCE40UP5K-SG48I FPGA. More information about this FPGA can be found on the Lattice web site at: /iCE40UltraPlus . A complete description of this device can be found in iCE40 UltraPlus Family Data Sheet (FPGA-DS-02008).Himax HM01B0 UPduino ShieldUser Guide© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal .All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.FPGA-UG-02081-1.0 52. Power SupplyExternal 5 V Power from the USB Connector (J7) provides power to the entire two board set. Alternately, power can be applied to headers on the UPduino v2.0 board: ∙ J6 - 5.0 V ∙ J9 – Ground3. Board OverviewThe following diagrams show key features of the Himax HM01B0 Adapter and UPduino v2.0 boards.RGB LED iCE40 UltraPlus FPGAMicro USB ConnectorFigure 3.1. UPduino v2.0 –Front ViewUSB uCFigure 3.2. UPduino v2.0 – Back ViewHimax HM01B0 UPduino ShieldUser Guide© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal .All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.6FPGA-UG-02081-1.0Camera Module with Himax HM01B0 Sensor Holes for MicrophoneAudio InputLEDsFigure 3.3. Himax HM01B0 Adapter Board –Front ViewDual I2S MicrophonesFigure 3.4. Himax HM01B0 Adapter Board – Back ViewHimax HM01B0 UPduino ShieldUser Guide© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal .All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.FPGA-UG-02081-1.0 74. iCE40 UltraPlus Pin SummaryThe following is a reference to indicate the connection of the iCE40 UltraPlus FPGA I/O pins on each board. SG48 Function Pin Type Bank Differential Pair UPduino v2.0 Himax HM01B0Adapter 1 VCCIO_2 VCCIO 2 – – – 2 IO B_6a PIO 2 –JP6-16 I2S data 3 IO B_9b DPIO 2 COMP_of_IOB_8a JP6-11 Molex1 – 8: SDA 4 IO B_8a DPIO 2 TRUE_of_IOB_9bJP6-10 Molex1 – 7: SCL5 VCC VCC VCC –– –6 IO B_13b DPIO 1 COMP_of_IOB_12aJP6-8 Molex1 – 5: FVLD7 CDONE CONFIG 1 – LED – D2– 8 creset_b CONFIG 1 – – –9 IO B_16a PIO 1 – JP6-7 Molex1 – 4: TRIG 10 IO B_18a PIO 1 – TP3 – 11 IO B_20a PIO 1 –JP6-6 MCLK12 IO B_22a DPIO 1 TRUE_of_IOB_23b JP6-1 Molex1 – 18: D1 13 IO B_24a DPIO1 TRUE_of_IOB_25bJP6-3RESET_CAM (NC)14 IO B_32a_SPI_SO DPIO/CONFIG_SPI 1 – SPI Flash – SDO – 15 IO B_34a_SPI_SCK DPIO/CONFIG_SPI 1 – SPI Flash – SCK – 16 IO B_35b_SPI_SS DPIO/CONFIG_SPI 1 – SPI Flash – CS – 17 IO B_33b_SPI_SI DPIO/CONFIG_SPI1 – SPI Flash – SDI–18 IO B_31b PIO 1 – JP6- 5 PWDN (NC) 19 IO B_29b PIO 1 – JP6- 4 Molex1 – 16: PCLK 20 IO B_25b_G3 DPIO/GBIN 1 COMP_of_IOB_24a TP4 –21 IO B_23b DPIO 1 COMP_of_IOB_22aJP6- 2 Molex1 – 17: D022 SPI_V CCIO1 VCCIO 1 –– – 23 IOT_37a DPIO/I3C 0 TRUE_of_IOT_36bJP5- 3 D9 24 VPP_2V5 VPP VPP –– – 25 IOT_36b DPIO/I3C 0 COMP_of_IOT_37a JP5- 4 D826 IOT_39a DPIO 0 TRUE_of_IOT_38b JP5- 5 Molex1 – 24: D7 27 IOT_38b DPIO 0 COMP_of_IOT_39aJP5- 6 Molex1 – 23: D628 IOT_41a PIO 0 – JP5- 16 LED5 29 VCCPLL VCCPLL – – – 30 VCC VCC VCC –– –31 IOT_42b DPIO 0 COMP_of_IOT_43a JP5- 9 Molex1 – 20: D3 32 IOT_43a DPIO 0 TRUE_of_IOT_42bJP5- 7 Molex1 – 22: D533 VCCIO_0 VCCIO 0 –– – 34 IOT_44b DPIO 0 COMP_of_IOT_45aJP5- 11 LEDO35 IOT_46b_G0 DPIO/GBIN 0 –JP5- 8 Mole x1 – 21: D436 IOT_48b DPIO 0 COMP_of_IOT_49a JP5- 13 LED237 IOT_45a_G1 DPIO/GBIN 0 TRUE_of_IOT_44b JP5- 10 Molex1 – 19: D238 IOT_50b DPIO 0 COMP_of_IOT_51aJP5- 15 LED4 39 RGB0 LED 0 – RGB LED – Red –40 RGB1 LED 0 – RGB LED – Green – 41 RGB2 LED 0 –RGB LED – Blue– 42 IOT_51a DPIO 0 TRUE_of_IOT_50b JP5- 14 LED3 43IOT_49aDPIOTRUE_of_IOT_48bJP5- 12LED1Himax HM01B0 UPduino ShieldUser Guide© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal .All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.8 FPGA-UG-02081-1.0SG48 Function Pin Type Bank Differential Pair UPduino v2.0 Himax HM01B0Adapter 44 IO B_3b_G6 DPIO/GBIN 2 COMP_of_IOB_2a JP6- 9 Molex1 – 6: LVLD 45 IO B_5b DPIO 2 COMP_of_IOB_4a JP6- 13 U2 – 2: STBY 46 IO B_0a PIO 2 –JP6- 15 I25 Clk 47 IO B_2a DPIO 2 TRUE_of_IOB_3b JP6- 14 I25 WS 48 IO B_4a DPIO 2 TRUE_of_IOB_5bJP6- 12 –Paddle GNDGNDGND––Molex1 – 9: INTHimax HM01B0 UPduino ShieldUser Guide 5.Software RequirementsInstall the following software before you begin developing designs for the board:∙Lattice Radiant 1.0 (or higher)∙Used for developing your own custom designs for the iCE40 UltraPlus FPGA∙Download at: /radiant∙Radiant Programmer 1.0 (or higher)∙Used to program the iCE40 UltraPlus FPGA∙This is included with Radiant software installation, or as a stand-alone tool.∙Download at: /radiant6.Board Configuration and Programming6.1.Board ConfigurationThe iCE40 UltraPlus on Himax HM01B0 UPduino Shield can be programmed via the included micro-USB cable using a PC running Lattice Radiant Programmer software. After the software is installed and launched, and the USB cable is connected to the board, see below for programming procedures.There are two modes to program the iCE40 UltraPlus FPGA on the UPduino v2.0 board.∙SPI Flash Programming (default): In this mode, the on-board SPI Flash is programmed, which in-turn programs the iCE40 UltraPlus FPGA at power-up or reset. This allows the user program to be stored in non-volatile memory when the board is powered-off or reset. This is the default programming mode.∙Direct CRAM Programming: In this mode, the iCE40 UltraPlus FPGA CRAM memory is programmed directly. This may allow for more rapid reconfiguration (if you need to regularly re-program the iCE40 UltraPlus whiledebugging), but the program is not be retained when the board is powered-off. To use this mode, a modification to the board is required.The default programming mode is SPI Flash programming. To change the programming mode, resistor R4 and R3 must be removed and replaced in the orientation shown in Figure 6.1.Figure 6.1. Programming Settings© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-UG-02081-1.0 9Himax HM01B0 UPduino ShieldUser Guide6.2.Programming the SPI FlashTo program the SPI Flash:1.Set board resistors to horizontal for SPI Flash programming.Note: This is the default mode.2.Connect the Himax HM01B0 UPduino Shield via USB cable to PC with Radiant Programmer installed.3.Start Radiant Programmer.4.Set Device Family to iCE40 UltraPlu s and Device to iCE40UP5K as shown in Figure 6.2.Figure 6.2. Device Family and Device Setting5.Click the iCE40 UltraPlus row, and select Edit > Device Properties.6.In the Device Properties dialog box, apply the settings below that are common to the three files to program (seeFigure 6.3).a.Under Device Operation, select the options below:∙Target Memory —External SPI Flash Memory (SPI FLASH)∙Port Interface—SPI∙Access Mode— Direct Programming∙Operation—Erase, Program, Verifyb.Under Programming Options, select the option below:∙Programming File —<Select desired file to program>c.Under SPI Flash Options, select the options below:∙Family —SPI Serial Flash∙Vendor —Winbond∙Device —W25P32∙Package —16-pin SOIC© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.10 FPGA-UG-02081-1.0Himax HM01B0 UPduino ShieldUser GuideFigure 6.3. Onboard SPI Flash Device Properties Settings7.Click OK to close the Device Properties window.8.Click the Program button in Radiant Programmer to program the Onboard SPI Flash.6.3.Programming the CRAM DirectlyTo program the CRAM directly:1.Set board resistors to vertical for CRAM Programming.2.Connect the Himax HM01B0 UPduino Shield via USB cable to PC with Radiant Programmer installed.3.Start Radiant Programmer.4.Set Device Family to iCE40 UltraPlus and Device to iCE40UP5K as shown in Figure 6.4.5.Click the iCE40 UltraPlus row, and select Edit > Device Properties.© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice. FPGA-UG-02081-1.0 11Himax HM01B0 UPduino ShieldUser GuideFigure 6.4. Device Family and Device Settings6.In the Device Properties dialog box, apply the as shown in Figure 6.5.∙Target Memory —Compressed Random Access Memory (CRAM)∙Port Interface —Slave SPI∙Access Mode — Direct Programming∙Operation —Fast Configuration7.Click OK to close the Device Properties window.8.Click the Program button in Radiant Programmer to begin programming.Figure 6.5. Device Properties for iCE40 Device Configuration Memory© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.12 FPGA-UG-02081-1.0Himax HM01B0 UPduino ShieldUser Guide© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal .All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.FPGA-UG-02081-1.0 137. Storage and HandlingStatic electricity can shorten the life span of electronic components. Observe these tips to prevent damage that can occur from electrostatic discharge:∙ Use antistatic precautions such as operating on an antistatic mat and wearing an antistatic wristband. ∙ Store the development board in the provided packaging.∙ Touch a metal USB housing to equalize voltage potential between you and the board.8. Ordering InformationDescriptionOrdering Part Number China RoHS Environment-Friendly Use Period (EFUP)Himax HM01B0 UPduino ShieldHM01B0-UPD-EVNHimax HM01B0 UPduino ShieldUser GuideReferencesFor more information, refer to∙iCE40 Ultra Plus Family Data Sheet (FPGA-DS-02008)∙/iCE40UltraPlusTechnical Support AssistanceSubmit a technical support case through /techsupport.© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.14 FPGA-UG-02081-1.0Himax HM01B0 UPduino ShieldUser Guide Revision HistoryRevision 1.0, November 2018Section Change SummaryAll Initial release.© 2018 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at /legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.FPGA-UG-02081-1.0 197th Floor, 111 SW 5th Avenue Portland, OR 97204, USAT 503.268.8000 HM01B0-UPD-EVN。

DLP Design DDLLPP-FFPPG USB-FPGA Module User Manua

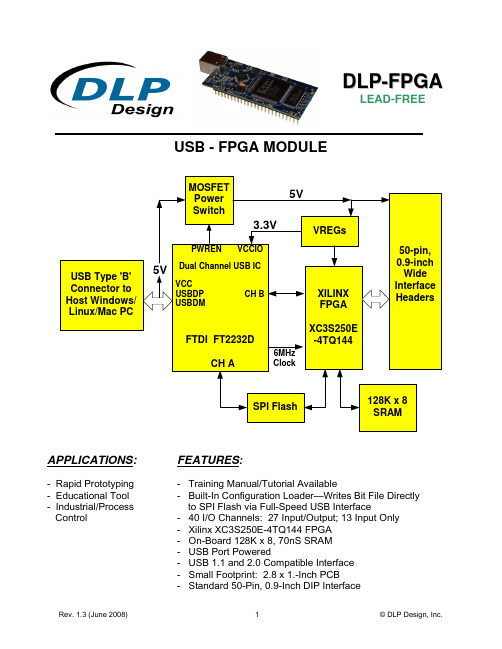

D L P-F P G ALEAD-FREEUSB - FPGA MODULEAPPLICATIONS:- Rapid Prototyping- Educational Tool- Industrial/ProcessControlFEATURES:- Training Manual/Tutorial Available- Built-In Configuration Loader—Writes Bit File Directlyto SPI Flash via Full-Speed USB Interface- 40 I/O Channels: 27 Input/Output; 13 Input Only- Xilinx XC3S250E-4TQ144 FPGA- On-Board 128K x 8, 70nS SRAM- USB Port Powered- USB 1.1 and 2.0 Compatible Interface- Small Footprint: 2.8 x 1.-Inch PCB- Standard 50-Pin, 0.9-Inch DIP Interface1.0 INTRODUCTIONThe DLP-FPGA Module is a low-cost, compact prototyping module that can be used for rapid proof of concept or for educational environments. The module is based on the Xilinx Spartan 3E and Future Technology Devices International’s FT2232D Dual-Channel USB IC. Used by itself or with the optional 200-page training manual, the DLP-FPGA provides both the beginner as well as the experienced engineer with a rapid path to developing FPGA-based designs. When combined with the free WebPACK™ Tools from Xilinx, this module is more than sufficient for creating anything from basic logical functions to a highly complex system controller.As a bonus feature, one channel of the dual-channel USB interface is used to load user bit files directly to the SPI Flash—no external programmer is required. This represents a savings of as much as $200 in that no additional programming cable is required for configuring the FPGA. All that is needed to load bit files to the DLP-FPGA is a Windows software utility (free with purchase), a Windows PC and a USB cable. The module can also be programmed from within the Xilinx ISE tool environment using a Xilinx programming cable (purchased separately).The DLP-FPGA is fully compatible with the free ISE™ WebPACK™ tools from Xilinx. ISE WebPACK offers the ideal development environment for FPGA designs with HDL synthesis and simulation, implementation, device fitting and JTAG programming.The DLP-FPGA has on-board voltage regulators that generate all required power supply voltages from a single 5-volt source. Power for the module can be taken from either the host USB port or from a user-supplied, external 5-volt power supply.Connection to user electronics is made via a 50-pin, 0.9-inch wide, industry-standard 0.025 square inch post DIP header. Other on-board features include a 128K x 8 static RAM IC for user projects, and both JTAG and SPI Flash interface ports for connection to Xilinx programming tools.2.0 TRAINING MANUALA 200+ page training manual for the DLP-FPGA is also available. While this manual is designed to provide entry-level instruction for those new to designing with FPGAs, it is recommended for developers who have some experience with FPGA products and associated development tools. An ISE™ WebPACK™Software installation DVD is included with the manual.The manual is comprised of 5 Chapters and 4 Labs as outlined below:Chapter 1: Installing the Xilinx ISE WebPACK tools and Understanding the Design FlowChapter 2: Lab 1: Implementing a Simple AND Gate: Create a New Project, Implement the Design, View the Synthesized Design, View the Placed and Routed DesignChapter 3: Lab 2: Heartbeat: Understanding the Digital Clock Manager (DCM), Methods of Starting ISE Project Navigator, VHDL Module Structure, Utilizing Hierarchy, Adding the DCM Component, Adding the Heartbeat Component, Connecting the Components, Synthesizing the Design Using XST, Simulating the Design Using the ISE Simulator, Adding the User Constraint File, Implementing the Design, Download the Design to the FPGAChapter 4: Lab 3: Memory Test: Block Diagram, DCM Design, SRAM State Machine, Bi-Directional Buffers, Test Failed Indicator, User Constraint File, Synthesize the Memory Test Design, Simulate the Memory Test Design, Implementing the Design, Download the Design to the FPGAChapter 5: Lab 4: USB Loopback: Initial Design, USB State Machine Module, Language Template, Bi-Directional Buffers, Synthesize, Simulate, Pin Constraints, Implement, Download the Design to the FPGA(The completed design files for each lab are available for download from the DLP Design website upon purchase of the DLP-FPGA and Lab Manual.)3.0 FPGA SPECIFICATIONSThe FPGA device used on the DLP-FPGA is the Xilinx Spartan 3E: XC3S250E-4VQ100.•Part Number: XC3S250E•System Gates: 250K•Equivalent Logic Cells: 5,508• CLB Arrayo Rows: 34o Columns: 26o Total CLB’s: 612o Total Slices: 2,448•Distributed RAM Bits: 38K•Block RAM Bits: 216K•Dedicated Multipliers: 12•DCM’s: 44.0 BITLOADAPP SOFTWAREWindows software is provided for use with the DLP-FPGA that will load an FPGA configuration (.bit) file directly to the SPI Flash device via the USB interface. This app (shown below) will allow the user to erase the flash, verify the erasure and then program and verify the flash:5.0 JTAG INTERFACEThe easiest way to load an FPGA configuration (bit file) to the FPGA is to run the BitLoadApp software, then select and program a file from the local hard drive directly to the SPI flash. Once written to the SPI flash, the configuration will load to the FPGA and execute. Alternatively, a traditional JTAG header location is provided on the DLP-FPGA giving the user access to the pins on the FPGA required by the development tools. (Refer to the schematic at the end of this datasheet for details.)6.0 EEPROM SETUP / MPROGThe DLP-FPGA has a dual-channel USB interface to the host PC. Channel A is used exclusively to load an FPGA configuration (bit file) to the SPI flash. This configuration data is automatically transferred to the FPGA when power is applied to the module. Channel B is used for communication between the FPGA and host PC at run time. A 93C56B EEPROM connected to the USB interface IC is used to store the setup for the two channels. The parameters stored in the EEPROM include the Vendor ID (VID), Product ID (PID), Serial Number, Description String, driver selection (VCP or D2XX) and port type (UART serial or FIFO parallel).As mentioned above, Channel A is used exclusively for loading the FPGA’s configuration to the SPI flash, and Channel B is used for communication between the host PC and the DLP-FPGA. As such, the D2XX drivers and FIFO mode must be selected in the EEPROM for Channel A. Channel B must use the FIFO mode, but can use either the VCP or D2XX drivers. The VCP drivers make the DLP-FPGA appear as an RS232 port to the host app. The D2XX drivers provide faster throughput, but require working with a .lib or .dll library in the host app.The operational modes and other EEPROM selections are written to the EEPROM using the MPROG utility. This utility and its manual are available for download from the bottom of the page at.7.0 TEST BIT FILEA test file is provided as a download from the DLP Design website that provides rudimentary access to the I/O features of the DLP-FPGA.The following features are provided:• Ping•Read the High/Low State of the Input-Only Pins•Drive I/O Pins High/Low or Read their High/Low State•Simple Loopback on Channel B•Simple Read/Write of Each Address in the SRAMThis bit file is available from the DLP-FPGA’s download page.8.0 USB DRIVERSUSB drivers for the following operating systems are available for download from the DLP Design website at :W i n d o w s X P x 64 M a c O S X W i n d o w s S e r v e r 2003M a c O S 9 W i n d o w s 2000 M a c O S 8 W i n d o ws 98, M EL i n u xNotes:1. The bit file load utility only runs on the Windows platforms.2. The bit file load utility requires the use of USB channel A, and channel A is dedicated to this function.3. If you are using the dual-mode drivers from FTDI (CDM2.02.04) and wish to use the VirtualCOM Port (VCP) drivers for Channel B communications, then it may be necessary to disable the D2XX drivers first via Device Manager. To do so, right click on the Channel B entry under USB Controllers that appears when the DLP-FPGA is connected, select Properties, select the Advanced tab, check the option for “Load VCP” and click OK. Once you unplug and then replug the DLP-FPGA, a COM port should appear in Device Manager under Ports (COM & LPT).9.0 USING THE DLP-FPGASelect a power source via Header Pins 23 and 24, and connect the DLP-FPGA to the PC to initiate the loading of USB drivers. The easiest way to do this is to connect Pins 23 and 24 to each other. This will result in operational power being taken from the host PC. Once the drivers are loaded, the DLP-FPGA is ready for use.Pin 25Top View (Interface Headers on bottom of PCB)Pin 50T A B L E1NN (dec)* NN (hex)* Name FPGA Pin JP2 Pin0 0 user_io(0) U5 Pin 58 JP2 Pin 21 1 user_io(1) U5 Pin 59 JP2 Pin 42 2 user_io(2) U5 Pin 93 JP2 Pin 53 3 user_io(3) U5 Pin 94 JP2 Pin 64 4 user_io(4) U5 Pin 96 JP2 Pin 75 5 user_io(5) U5 Pin 97 JP2 Pin 86 6 user_io(6) U5 Pin 103 JP2 Pin 97 7 user_io(7) U5 Pin 104 JP2 Pin 108 8 user_io(8) U5 Pin 105 JP2 Pin 129 9 user_io(9) U5 Pin 106 JP2 Pin 1310 A user_io(10) U5 Pin 112 JP2 Pin 1411 B user_io(11) U5 Pin 113 JP2 Pin 1512 C user_io(12) U5 Pin 116 JP2 Pin 1613 D user_io(13) U5 Pin 117 JP2 Pin 1714 E user_in(14) [INPUT ONLY!] U5 Pin 119 JP2 Pin 1815 F user_in(15) [INPUT ONLY!] U5 Pin 120 JP2 Pin 1916 10 user_io(16) U5 Pin 122 JP2 Pin 2017 11 user_io(17) U5 Pin 123 JP2 Pin 2118 12 user_io(18) U5 Pin 124 JP2 Pin 2219 13 user_io(19) U5 Pin 125 JP2 Pin 2720 14 user_io(20) U5 Pin 126 JP2 Pin 2921 15 user_io(21) U5 Pin 130 JP2 Pin 3022 16 user_io(22) U5 Pin 131 JP2 Pin 3123 17 user_io(23) U5 Pin 132 JP2 Pin 3224 18 user_io(24) U5 Pin 134 JP2 Pin 3325 19 user_io(25) U5 Pin 135 JP2 Pin 3426 1A user_io(26) U5 Pin 139 JP2 Pin 3527 1B user_io(27) U5 Pin 140 JP2 Pin 3628 1C user_io(28) U5 Pin 142 JP2 Pin 3730 1E user_in(0) U5 Pin 10 JP2 Pin 4931 1F user_in(1) U5 Pin 12 JP2 Pin 4832 20 user_in(2) U5 Pin 29 JP2 Pin 4733 21 user_in(3) U5 Pin 31 JP2 Pin 4634 22 user_in(4) U5 Pin 36 JP2 Pin 4535 23 user_in(5) U5 Pin 38 JP2 Pin 4436 24 user_in(6) U5 Pin 41 JP2 Pin 4337 25 user_in(7) U5 Pin 47 JP2 Pin 4238 26 user_in(8) U5 Pin 48 JP2 Pin 4139 27 user_in(9) U5 Pin 66 JP2 Pin 3940 28 user_in(10) U5 Pin 69 JP2 Pin 38Read: 29,>40 Read:1D,>29Returns Read Pin Error E4 n/a n/aWrite: 14, 15, >30 Write: E, F,>1EReturns Write Pin Error E2 for PinClear (low), or E3 for Pin Set(high)n/a n/aGround 1,11,25,26,40,50FPGA_RESET 1283 5VIN – Module power source 23PORTVCC – Power from Host PC 24VCCSW – 5V power after hostenumerates the USB port28*N o t e:This is the I/O number for use with the Test Bit File described in Section 7.10.0 MECHANICAL DIMENSIONS IN INCHES (MM) (PRELIMINARY)11.0 DISCLAIMER© DLP Design, Inc., 2007Neither the whole nor any part of the information contained herein nor the product described in this manual may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder.This product and its documentation are supplied on an as-is basis, and no warranty as to their suitability for any particular purpose is either made or implied. DLP Design, Inc. will not accept any claim for damages whatsoever arising as a result of the use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device, or system in which the failure of the product might reasonably be expected to result in personal injury.This document provides preliminary information that may be subject to change without notice.12.0 CONTACT INFORMATIONDLP Design, Inc.1605 Roma LaneAllen, TX 75013Phone: 469-964-8027Fax: 415-901-4859Email Sales: *******************EmailSupport:*********************Website URL: 。

FPGA可编程逻辑器件芯片XCZU9EG-2FFVB1156I中文规格书

General DescriptionThe Zynq® UltraScale+™ MPSoC family is based on the Xilinx® UltraScale™ MPSoC architecture. This family of products integrates a feature-rich 64-bit quad-core or dual-core Arm® Cortex™-A53 and dual-core Arm Cortex-R5 based processing system (PS) and Xilinx programmable logic (PL) UltraScale architecture in a single device. Also included are on-chip memory, multiport external memory interfaces, and a rich set of peripheral connectivity interfaces.Processing System (PS)Arm Cortex-A53 Based Application Processing Unit (APU)•Quad-core or dual-core•CPU frequency: Up to 1.5GHz•Extendable cache coherency•Armv8-A Architectureo64-bit or 32-bit operating modeso TrustZone securityo A64 instruction set in 64-bit mode,A32/T32 instruction set in 32-bit mode •NEON Advanced SIMD media-processing engine •Single/double precision Floating Point Unit (FPU)•CoreSight™and Embedded Trace Macrocell(ETM)•Accelerator Coherency Port (ACP)•AXI Coherency Extension (ACE)•Power island gating for each processor core •Timer and Interruptso Arm Generic timers supporto Two system level triple-timer counterso One watchdog timero One global system timer•Cacheso32KB Level1, 2-way set-associativeinstruction cache with parity (independent foreach CPU)o32KB Level1, 4-way set-associative data cache with ECC (independent for each CPU) o1MB 16-way set-associative Level2 cache with ECC (shared between the CPUs)Dual-core Arm Cortex-R5 Based Real-Time Processing Unit (RPU)•CPU frequency: Up to 600MHz•Armv7-R Architectureo A32/T32 instruction set•Single/double precision Floating Point Unit (FPU)•CoreSight™ and Embedded Trace Macrocell (ETM)•Lock-step or independent operation•Timer and Interrupts:o One watchdog timero Two triple-timer counters•Caches and Tightly Coupled Memories (TCMs) o32KB Level1, 4-way set-associativeinstruction and data cache with ECC(independent for each CPU)o128KB TCM with ECC (independent for each CPU) that can be combined to become 256KBin lockstep modeOn-Chip Memory•256KB on-chip RAM (OCM) in PS with ECC •Up to 36Mb on-chip RAM (UltraRAM) with ECC in PL•Up to 35Mb on-chip RAM (block RAM) with ECC in PL•Up to 11Mb on-chip RAM (distributed RAM) in PL 找FPGA和CPLD可编程逻辑器件,上深圳宇航军工半导体有限公司Programmable Logic (PL)Configurable Logic Blocks (CLB)•Look-up tables (LUT)•Flip-flops•Cascadable adders36Kb Block RAM•True dual-port•Up to 72 bits wide•Configurable as dual 18Kb UltraRAM•288Kb dual-port•72 bits wide•Error checking and correctionDSP Blocks•27x18 signed multiply•48-bit adder/accumulator•27-bit pre-adder Programmable I/O Blocks •Supports LVCMOS, LVDS, and SSTL• 1.0V to 3.3V I/O•Programmable I/O delay and SerDes JTAG Boundary-Scan•IEEE Std 1149.1 Compatible Test Interface PCI Express•Supports Root complex and End Pointconfigurations•Supports up to Gen3 speeds•Up to five integrated blocks in select devices 100G Ethernet MAC/PCS•IEEE Std 802.3 compliant•CAUI-10 (10x 10.3125Gb/s) orCAUI-4 (4x 25.78125Gb/s)•RSFEC (IEEE Std 802.3bj) in CAUI-4 configuration •Up to four integrated blocks in select devices Interlaken•Interlaken spec 1.2 compliant•64/67 encoding•12 x 12.5Gb/s or 6 x 25Gb/s•Up to four integrated blocks in select devices Video Encoder/Decoder (VCU)•Available in EV devices•Accessible from either PS or PL •Simultaneous encode and decode•H.264 and H.265 supportSystem Monitor in PL•On-chip voltage and temperature sensing•10-bit 200KSPS ADC with up to 17 external inputsZynq UltraScale+ MPSoCsA comprehensive device family, Zynq UltraScale+ MPSoCs offer single-chip, all programmable,heterogeneous multiprocessors that provide designers with software, hardware, interconnect, power, security, and I/O programmability. The range of devices in the Zynq UltraScale+MPSoC family allows designers to target cost-sensitive as well as high-performance applications from a single platform using industry-standard tools. While each Zynq UltraScale+MPSoC contains the same PS, the PL, Video hard blocks, and I/O resources vary between the devices.The Zynq UltraScale+ MPSoCs are able to serve a wide range of applications including:•Automotive: Driver assistance, driver information, and infotainment•Wireless Communications: Support for multiple spectral bands and smart antennas•Wired Communications: Multiple wired communications standards and context-aware network services •Data Centers: Software Defined Networks (SDN), data pre-processing, and analytics •Smarter Vision: Evolving video-processing algorithms, object detection, and analytics•Connected Control/M2M: Flexible/adaptable manufacturing, factory throughput, quality, and safetyThe UltraScale MPSoC architecture provides processor scalability from 32 to 64 bits with support for virtualization, the combination of soft and hard engines for real-time control, graphics/video processing, waveform and packet processing, next-generation interconnect and memory, advanced powermanagement, and technology enhancements that deliver multi-level security, safety, and reliability. Xilinx offers a large number of soft IP for the Zynq UltraScale+MPSoC family. Stand-alone and Linux device drivers are available for the peripherals in the PS and the PL. Xilinx’s Vivado® Design Suite, SDK™, and PetaLinux development environments enable rapid product development for software, hardware, and systems engineers. The Arm-based PS also brings a broad range of third-party tools and IP providers in combination with Xilinx's existing PL ecosystem.The Zynq UltraScale+MPSoC family delivers unprecedented processing, I/O, and memory bandwidth in the form of an optimized mix of heterogeneous processing engines embedded in a next-generation, high-performance, on-chip interconnect with appropriate on-chip memory subsystems. Theheterogeneous processing and programmable engines, which are optimized for different application tasks, enable the Zynq UltraScale+ MPSoCs to deliver the extensive performance and efficiency required to address next-generation smarter systems while retaining backwards compatibility with the original Zynq-7000 All Programmable SoC family. The UltraScale MPSoC architecture also incorporates multiple levels of security, increased safety, and advanced power management, which are critical requirements of next-generation smarter systems. Xilinx’s embedded UltraFast™ design methodology fully exploits theTable 7:Zynq UltraScale+ MPSoC Device FeaturesCG DevicesEG DevicesEV DevicesAPU Dual-core Arm Cortex-A53Quad-core Arm Cortex-A53Quad-core Arm Cortex-A53RPU Dual-core Arm Cortex-R5Dual-core Arm Cortex-R5Dual-core Arm Cortex-R5GPU –Mali-400MP2Mali-400MP2VCU––H.264/H.265ASIC-class capabilities afforded by the UltraScale MPSoC architecture while supporting rapid system development.The inclusion of an application processor enables high-level operating system support, e.g., Linux. Other standard operating systems used with the Cortex-A53 processor are also available for theZynq UltraScale+MPSoC family. The PS and the PL are on separate power domains, enabling users to power down the PL for power management if required. The processors in the PS always boot first, allowing a software centric approach for PL configuration. PL configuration is managed by software running on the CPU, so it boots similar to an ASSP.。

FPGA可编程逻辑器件芯片XCZU5EV-2SFVC784I中文规格书

Programmable Logic DesignMay 8, 2008Military and AerospaceTable 2-9:Virtex-5 FamilyMilitary and AerospaceXilinx is the leading supplier of high-reliability PLDs to the aerospace and defensemarkets. These devices are used in a wide range of applications such as electronic warfare, missile guidance and targeting, RADAR, SONAR communications, signal processing, avionics, and satellites. The Xilinx QPro family of ceramic and plastic QML products provides you with advanced programmable logic solutions for next-generation designs. The QPro family also includes select products that are radiation hardened for use insatellite and other space applications. Our quality management system is fully compliant with all ISO9001 requirements. In 1997, Xilinx became fully qualified as a QML supplier by meeting all of the requirements for MIL Standard 38535.Automotive and IndustrialXilinx XA Solutions – Architecting Automotive IntelligenceIn-car electronic content is increasing at a phenomenal rate. It includes such applications as navigation systems, entertainment systems, instrument clusters, advanced driverinformation systems, and communications devices. To address the needs of automotive electronics designers, Xilinx has created a new family of devices with an extended industrial temperature range option. This new “XA” family consists of existing Xilinx industrial grade (I) FPGAs and CPLDs, with the addition of a new extended temperature grade (Q) for selected devices. The new Q product grade (-40°C to +125°C ambient for CPLDs and junction for FPGAs) is ideal for automotive and industrial applications. The wide range of device density and package combinations enables you to deliver high- performance, cost-effective, flexible solutions that meet your application needs.Design-In FlexibilityWith Xilinx XA devices, you can design-in flexibility and get your product to market faster than ever before. Because many new standards continue to evolve (such as the LIN, MOST, Logic Logic/Serial DSP/Serial Emb./SerialOct ‘06Feb ‘07NowMay ‘06LX LXT SXT FXTProgrammable Logic Design May 8, 2008HDL Design Process architecture BEHAVE of MULT isbeginY <= A * B;end BEHAVE;After (32 x 32 multiplier):entity MULT isport(A,B:in std_logic_vector (31 downto 0);Y:out std_logic_vector (63 downto 0));end MULT;architecture BEHAVE of MULT isbeginY <= A * B;end BEHAVE;HDL is also ideal for design re-use. You can share your “library” of parts with otherdesigners at your company, therefore saving and avoiding duplication of effort.HDL SynthesisOnce we have specified the design in a behavioral description we can convert it into gatesusing the process of synthesis. The synthesis tool does the intensive work of figuring outwhat gates to use, based on the high-level description file you provide (using schematiccapture, you would have to do this manually.) Because the resulting netlist is vendor anddevice family-specific, you must use the appropriate vendor library. Most synthesis toolssupport a large range of gate array, FPGA, and CPLD device vendors.In addition, you can specify optimization criteria that the synthesis tool will take intoaccount when making the gate-level selections, also called mapping. Some of these optionsinclude: optimizing the complete design for the least number of gates, optimizing a certainsection of the design for fastest speed, using the best gate configuration to minimize power,and using the FPGA-friendly, register-rich configuration for state machines.You can easily experiment with different vendors, device families, and optimizationconstraints, thus exploring many different solutions instead of just one with the schematicapproach.To recap, the advantages of high level design and synthesis are many. It is much simplerand faster to specify your design using HDL, and much easier to make changes to thedesign because of the self-documenting nature of the language. You are relieved from thetedium of selecting and interconnecting at the gate level. You merely select the library andoptimization criteria (e.g., speed, area) and the synthesis tool will determine the results.You can also try different design alternatives and select the best one for your application. Infact, there is no real practical alternative for designs exceeding 10,000 gates.ISE SoftwareISE advanced HDL synthesis engines produce optimized results for PLD synthesis, one ofthe most essential steps in your design methodology. It takes your conceptual HDL designdefinition and generates a logical or physical representation for the targeted silicon device.A state-of-the-art synthesis engine is required to produce highly optimized results with afast compile and turnaround time. To meet this requirement, the synthesis engine must betightly integrated with the physical implementation tool and proactively meet design。

FPGA可编程逻辑器件芯片XC7K325T-2FFG900I中文规格书

Chapter1 Packaging OverviewAbout this GuideXilinx® 7series FPGAs include four FPGA families that are all designed for lowest power to enable a common design to scale across families for optimal power, performance, and cost.The Spartan®-7 family is the lowest density with the lowest cost entry point into the7series portfolio. The Artix®-7 family is optimized for highest performance-per-watt and bandwidth-per-watt for cost-sensitive, high-volume applications. The Kintex®-7 family is an innovative class of FPGAs optimized for the best price-performance. The Virtex®-7family is optimized for highest system performance and capacity.This 7series packaging and pinout product specification, part of an overall set ofdocumentation on the 7series FPGAs, is available on the Xilinx website .IntroductionThis section describes the pinouts for the 7series FPGAs in various fine pitch and flip-chip1.0mm pitch BGA packages, 0.8mm and 0.5mm pitch chip-scale packages, and 0.5mmpitch wire-bond lead frame packages.Spartan-7, Artix-7, and Kintex-7 devices are offered in low-cost, space-saving packages that are optimally designed for the maximum number of user I/Os.Virtex-7T and Virtex-7XT devices are offered exclusively in high performance flip-chip BGA packages that are optimally designed for improved signal integrity and jitter.For pinout and packaging information on the Virtex-7HT devices.Package inductance is minimized as a result of optimal placement and even distributionas well as an increased number of Power and GND pins.The FFG, FLG, FHG, FBG, SBG, and RFG flip-chip packages marked with the Pb-free Character on the upper right of the device are RoHS 6 of 6 compliant. The FFG, FLG, FHG, FBG, SBG, and RFG flip-chip packages not marked with the Pb-free character are RoHS 6 of 6 compliant,Pin DefinitionsTable1-12 lists the pin definitions used in 7series FPGAs packages.Note:There are dedicated general purpose user I/O pins listed separately in Table1-12. There are also multi-function pins where the pin names start with either IO_LXXY_ZZZ_# or IO_XX_ZZZ_#, where ZZZ represents one or more functions in addition to being general purpose user I/O. If not used for their special function, these pins can be user I/O.user I/O after stage 2 configuration is complete.Power/Ground PinsGND Dedicated N/A GroundRSVDGND Dedicated N/A Reserved pins, tie to GNDVCCAUX Dedicated N/A 1.8V power-supply pins for auxiliary circuits VCCAUX_IO_G#(2)Dedicated N/A 1.8V/2.0V power-supply pins for auxiliary I/O circuits VCCINT Dedicated N/A0.9V/1.0V power-supply pins for the internal core logic VCCO_#(3)Dedicated N/A Power-supply pins for the output drivers (per bank) VCCBRAM Dedicated N/A 1.0V power-supply pins for the FPGA logic block RAMVCCBATT_0Dedicated N/A Decryptor key memory backup supply; this pin should be tied to the appropriate V CC or GND when not used(4). Specific Spartan-7 devices (XC7S6 and XC7S15) do not support AES encryption. In these devices, connect VCCBATT_0 to VCCAUX or GND.VREF Multi-function N/A These are input threshold voltage pins. They become user I/Os when an external threshold voltage is not needed (per bank).Analog to Digital Converter (XADC) PinsFor more information, see the XADC Package Pins table in UG480, 7Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User GuideVCCADC_0(5)(6)Dedicated N/A XADC analog positive supply voltageThe XC7S6 and XC7S15 Spartan-7 devices do not support the XADC. In these devices, connect the VCCADC_0 pin to VCCAUX.GNDADC_0(5)(6)Dedicated N/A XADC analog ground referenceThe XC7S6 and XC7S15 Spartan-7 devices do not support the XADC. In these devices, connect the GNDADC_0 pin to GND.VP_0(5)Dedicated Input XADC dedicated differential analog input (positive side) VN_0(5)Dedicated Input XADC dedicated differential analog input (negative side) VREFP_0(5)Dedicated N/A 1.25V reference inputVREFN_ 0(5)Dedicated N/A 1.25V reference GND referenceAD0P through AD15PAD0N through AD15N Multi-function Input XADC (analog-to-digital converter) differential auxiliary analog inputs 0–15.Auxiliary channels 6, 7, 13, 14, and 15 are not supported on Kintex-7 devices.Table 1-12:7Series FPGAs Pin Definitions (Cont’d)Pin Name Type Direction DescriptionChapter 2:7Series FPGAs Package Files。

FPGA现状及发展趋势

FPGA核心单元-CLB LUT作为函数发生器:

FPGA核心单元-CLB

LUT作为移位寄存器:

FPGA核心单元-DCM

3、数字时钟管理模块(DCM)

大多数FPGA均提供数字时钟管理。通过该模 块提供数字时钟管理和相位环路锁定。相位环路 锁定能够提供精确的时钟综合,且能够降低抖动 ,并实现过滤功能。

Device,CPLD)

现场可编程门阵列(Field Programmable Gate Array,

FPGA)

可编程逻辑器件简介

• PROM、EPROM和EEPROM, 第一阶段 • 由于结构的限制,只能完成简单的数字逻辑功能。

• PAL和GAL,正式被称为PLD,能够完成各种逻辑运算功能。 第二阶段 • 由“与”、“非”阵列组成,以乘积和形式完成大量的逻辑组合。

PLD的发展史

FPGA的发展史(1)

1985年 Xilinx 1991年 Xilinx 1995年 Altera 1998年 Xilinx

• 推出全球第一款FPGA产品——XC2064,采用2μm工艺, 包含64个逻辑模块和85,000个晶体管,门数量不超过1,000 门。

• 推出XC4000系列FPGA,这是第一款被广泛使用的FPGA, 包含44万个晶体管。采用0.7μm工艺。

• 7系列FPGA统计架构 • 利用高-K金属栅、高性能、低功耗28nm工艺技术,为您实现低

功耗、最高性能和生产力最大化。

Xilinx公司简介

Xilinx公司成立于1984年,首创了现场可编

程逻辑阵列(FPGA)这一创新性的技术,并 于1985年首次推出商业化产品。目前Xilinx 占有全世界FPGA产品一半以上的市场份额 。Xilinx公司的FPGA器件基于SRAM架构, 可“无限次”编程;LUT可配置为分布式 RAM;块RAM可配置为多种模式;全数字 式的时钟管理系统,可提供灵活精确的时 钟信号;VersaRing提供了IOB与CLB的连接 ,可以更便利的实现PIN锁定。

FPGA可编程逻辑器件芯片XC7A100T-2CSG324I中文规格书

Chapter1 Packaging OverviewAbout this GuideXilinx® 7series FPGAs include four FPGA families that are all designed for lowest power to enable a common design to scale across families for optimal power, performance, and cost.The Spartan®-7 family is the lowest density with the lowest cost entry point into the7series portfolio. The Artix®-7 family is optimized for highest performance-per-watt and bandwidth-per-watt for cost-sensitive, high-volume applications. The Kintex®-7 family is an innovative class of FPGAs optimized for the best price-performance. The Virtex®-7family is optimized for highest system performance and capacity.This 7series packaging and pinout product specification, part of an overall set ofdocumentation on the 7series FPGAs, is available on the Xilinx.IntroductionThis section describes the pinouts for the 7series FPGAs in various fine pitch and flip-chip1.0mm pitch BGA packages, 0.8mm and 0.5mm pitch chip-scale packages, and 0.5mmpitch wire-bond lead frame packages.Spartan-7, Artix-7, and Kintex-7 devices are offered in low-cost, space-saving packages that are optimally designed for the maximum number of user I/Os.Virtex-7T and Virtex-7XT devices are offered exclusively in high performance flip-chip BGA packages that are optimally designed for improved signal integrity and jitter.For pinout and packaging information on the Virtex-7HT devices.Package inductance is minimized as a result of optimal placement and even distributionas well as an increased number of Power and GND pins.The FFG, FLG, FHG, FBG, SBG, and RFG flip-chip packages marked with the Pb-free Character on the upper right of the device are RoHS 6 of 6 compliant. The FFG, FLG, FHG, FBG, SBG, and RFG flip-chip packages not marked with the Pb-free character are RoHS 6 of 6 compliant,Table 1-6 lists the quantity of GTX and GTH serial transceiver channels for the Virtex-7XT FPGAs. In all devices, a serial transceiver channel is one set of MGTRXP, MGTRXN, MGTTXP, and MGTTXN pins.Table 1-6:Serial Transceiver Channels (GTX/GTH) by Device/Package (Virtex-7XT FPGAs)DeviceFFG1157FFV1157RF1157FFG1158FFV1158RF1158FFG1761FFV1761RF1761FFG1926FFG1927FFV1927FFG1928FFG1930RF1930FLG1926FLG1928FLG1930GTX GTH GTX GTH GTX GTH GTX GTH GTX GTH GTX GTH GTX GTH GTX GTH GTX GTH GTX GTHXC7VX330T 020–028–––––––XC7VX415T 020048––048–––––XC7VX485T 200480280–560–240–––XC7VX550T –048––080–––––XC7VX690T 0204836064080–024–––XC7VX980T –––064–07224–––XC7VX1140T –––––––06496024XQ7VX330T 020–028–––––––XQ7VX485T ––280–––240–––XQ7VX690T 0204836–––024–––XQ7VX980T––––––24–––Spartan-7 Devices User I/OPinsSpartan-7 FPGA Packages: HR I/O Banks OnlyCPGA196CSGA225CSGA324FTGB196FGGA484FGGA676XC7S6 XA7S6User I/O100100–100––Differential9696–96––XC7S15 XA7S15User I/O100100–100––Differential9696–96––XC7S25 XA7S25User I/O–150150100––Differential–14414496––XC7S50 XA7S50User I/O––210100250–Differential––20296240–XC7S75 XA7S75User I/O––––338400 Differential––––324384XC7S100 XA7S100User I/O––––338400 Differential––––324384Power/Ground PinsGND Dedicated N/A GroundRSVDGND Dedicated N/A Reserved pins, tie to GNDVCCAUX Dedicated N/A 1.8V power-supply pins for auxiliary circuits VCCAUX_IO_G#(2)Dedicated N/A 1.8V/2.0V power-supply pins for auxiliary I/O circuits VCCINT Dedicated N/A0.9V/1.0V power-supply pins for the internal core logic VCCO_#(3)Dedicated N/A Power-supply pins for the output drivers (per bank) VCCBRAM Dedicated N/A 1.0V power-supply pins for the FPGA logic block RAMVCCBATT_0Dedicated N/A Decryptor key memory backup supply; this pin should be tied to the appropriate V CC or GND when not used(4). Specific Spartan-7 devices (XC7S6 and XC7S15) do not support AES encryption. In these devices, connect VCCBATT_0 to VCCAUX or GND.VREF Multi-function N/A These are input threshold voltage pins. They become user I/Os when an external threshold voltage is not needed (per bank).Analog to Digital Converter (XADC) PinsFor more information, see the XADC Package Pins table in UG480, 7Series FPGAs and Zynq-7000 All Programmable SoC XADC Dual 12-Bit 1 MSPS Analog-to-Digital Converter User GuideVCCADC_0(5)(6)Dedicated N/A XADC analog positive supply voltageThe XC7S6 and XC7S15 Spartan-7 devices do not support the XADC. In these devices, connect the VCCADC_0 pin to VCCAUX.GNDADC_0(5)(6)Dedicated N/A XADC analog ground referenceThe XC7S6 and XC7S15 Spartan-7 devices do not support the XADC. In these devices, connect the GNDADC_0 pin to GND.VP_0(5)Dedicated Input XADC dedicated differential analog input (positive side) VN_0(5)Dedicated Input XADC dedicated differential analog input (negative side) VREFP_0(5)Dedicated N/A 1.25V reference inputVREFN_ 0(5)Dedicated N/A 1.25V reference GND referenceAD0P through AD15PAD0N through AD15N Multi-function Input XADC (analog-to-digital converter) differential auxiliary analog inputs 0–15.Auxiliary channels 6, 7, 13, 14, and 15 are not supported on Kintex-7 devices.Table 1-12:7Series FPGAs Pin Definitions (Cont’d)Pin Name Type Direction Description。

基于存储器映射的Flash高速低功耗驱动实现

基于FPGA双RAM乒乓操作的数据存储系统的研究-图文(精)

科技信息。

机械与电子o2021年第2l期基于FPGA双RAM乒乓操作的数据存储系统的研究钱黄生1夏忠珍z11。

中国电子科技集团公司第四十一研究所山东青岛266555;2.南京立汉化学有限公.-3江苏南京211102l【搐要】本文阐速了在对实时性要求较高,而对数据存储深度要求不高的数据采集系统中,用FPGA构建双RAM来乒乓存储数据的方法,重点介绍了乒乓操作的控制方法。

本方法在XILINX9.1软件中通过时序仿真。

并且通过XC2VP20验证了本方法完全能够满足设计的要求。

【关键词】FPGA;KAM;乒乓操作0引言经过70年的不断开展,FPGA已由当初的1200门开展成为今天的百万门级。

通过不断更新优化产品架构和生产工艺,实现了更多的逻辑单元、更高的性能、更低的单位本钱和功耗【11。

本文用到的FPGA是xilinx公司Virtex-Il Pro家族的xc2vp20芯片,它包含2个POWER PC处理器.20880个cell.多达290KB的分布式RAM以及88个18KB的Block RAM嘲。

由于本系统的存储深度不大,所以采用FPGA片内资源来构建RAM。

这样效率更高.且使用方便,而且还可以防止板级信号干扰。

既节省了印制板空间又节约了成本。

1乒乓操作原理乒乓操作口棚是种经常应用于数据流控制的处理方法。

图l是它的典型操作示意图。

乒乓操作的处理流程为:输人数据流通过“输入数据选择单元〞将数据流等时分配到两个数据缓冲区.数据缓冲模块选择双口RAM (DPRAM或单r】RAM,FIFO等。

在第一个周期,将输入的数据流缓存到。

数据暂存单元1〞:在第2个周期,通过“输人数据选择单元〞的切换,将输入的数据流缓存到“数据暂存单元2〞,同时将“数据暂存单元1〞缓存的第1个周期数据通过“输出数据选择单元〞的选择。

输送到“数据处理单元〞即上位机凄走进行处理;在第3个缓冲周期通过“输人数据选择单元〞的再次切换,将输入的数据流缓存到“数据暂存单元1〞,同时将“数据暂存单元2〞缓存的第2个周期的数据通过“输出数据选择单元〞切换,输送到“数据处理单元〞进行运算处理。

XilinxFPGA 的power-up配置和 start-up过程

Xilinx FPGA的power-up配置和 start-up过程FPGA的配置分为3步,1.清除配置SRAM2.下载配置数据3. Start-up过程激活逻辑Power-up配置从上图可见,配置在FPGA上电时自动进行。

上电后,FPGA自动开始清楚RAM的内容(此时,外围电路应使/program=1),清除RAM后,FPGA使/INIT变为无效,开始装载配置bit(如果保持/INIT信号有效,则可以延迟装载bit,INIT是双向端口)。

装载bit的过程中,FPGA会做CRC检查,发现错误则把/INIT信号拉低。

配置完成后done变高。

配置时序如下图所示。

也可以通过把/program置低开始(在不重新上电的情况下开始配置FPGA)对Xilinx FPGA的配置有四个主要步骤(不重新上电的情况下开始配置FPGA):(1)配置存储器清空(Clearing Configuration Memory)将PROGRAM管脚拉低300ns以上。

当PROGRAM拉低后,开始配置存储器,将存储器清空。

此时INIT将被拉低,当PROGRAM置高后,FPGA将继续将INIT置低直到完全清除完所有的配置存储器。

当INIT变高时,配置便可以开始了。

(2)加载配置数据(Loading Configuration Data)当INIT变高时,便可以配置FPGA了。

配置时,先将CCLK置低,再将数据发送到DIN上,延时45ns以上,再将CCLK置高,该位数据便写入到了FPGA中(数据是低位在前),然后再准备下一次的输入。

如此反复,将所有数据输入完毕为止。

(3)CRC错误校验(CRC Error Checking)在加载数据过程中,嵌入到配置文件中的CRC值同FPGA计算出来的值比较,若有CRC 校验错误产生,则INIT置低,且FPGA停止加载。

Start-up过程默认的start-up过程在DONE信号变高并延迟一个CCLK后进行,此时global tri-state signal(GTS)信号释放,这样允许器件output打开。

PolarFire SoC FPGA:工程样本(ES)设备 55900219 版本1.0 7 20