四象限乘法器

四象限乘法器设计

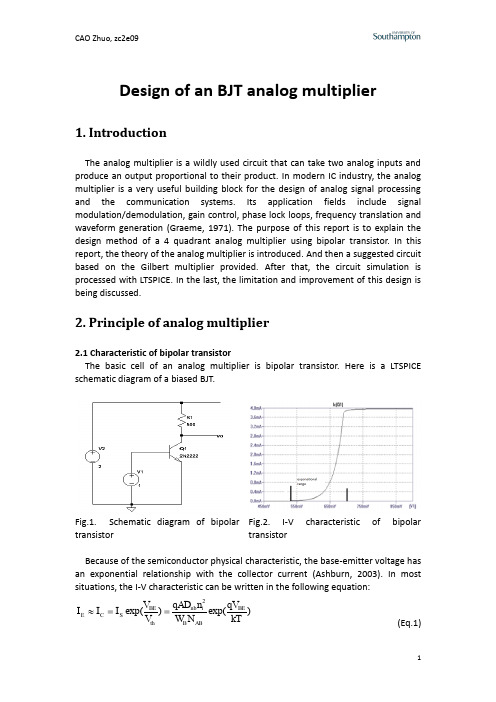

Design of an BJT analog multiplier1. IntroductionThe analog multiplier is a wildly used circuit that can take two analog inputs and produce an output proportional to their product. In modern IC industry, the analog multiplier is a very useful building block for the design of analog signal processing and the communication systems. Its application fields include signal modulation/demodulation, gain control, phase lock loops, frequency translation and waveform generation (Graeme, 1971). The purpose of this report is to explain the design method of a 4 quadrant analog multiplier using bipolar transistor. In this report, the theory of the analog multiplier is introduced. And then a suggested circuit based on the Gilbert multiplier provided. After that, the circuit simulation is processed with LTSPICE. In the last, the limitation and improvement of this design is being discussed.2. Principle of analog multiplier2.1 Characteristic of bipolar transistorThe basic cell of an analog multiplier is bipolar transistor. Here is a LTSPICE schematic diagram of a biased BJT.Fig.1. Schematic diagram of bipolar transistor Fig.2. I-V characteristic of bipolartransistorBecause of the semiconductor physical characteristic, the base-emitter voltage has an exponential relationship with the collector current (Ashburn, 2003). In most situations, the I-V characteristic can be written in the following equation:2exp()exp()nb i BE BE E C S th B AB qAD n V qV I I I V W N kT(Eq.1)Here, 2nb i S B AB qAD n I W N is saturation current of the base. th kT V q is thermal voltage, which can be considered equal to 26mV in room temperature. I C is the collector current. I E is the emitter current. V BE is the base-emitter voltage. I S is a constant which is determined by the geometric size of base and its doping density. V th is a constant which is only determined by the temperature. It can be seen from the equation that the collector current will exponential increase with the base-emitter voltage. Using LTSPICE DC simulation, the figure 2 can show this relationship directly. From the graph it can be seen that the I C equals nearly to 0 when V BE is less than 520mV. Also I C has a maximum value when V BE arrival 700mV. So the threshold voltage V T is in this range. And the exponential relationship only works in this range.2.2 Simple multiplierBased on the characteristic of bipolar transistor discussed above, a simple multiplier circuit can be developed. The structure of this circuit is shown in figure 3 and 4.Fig.3. the differential amplifier circuit Fig.4. 2 quadrant analog multiplier circuit In figure 3, Vx is the differential input. Io is the current source. Q1, Q2 are two NPN transistors. It can be seen that:And:According to these 2 equations, . From the Eq.1., we canobtain . In mathematics, when(about 2*26mV), . Thus we get:(Eq.2) The different current and can be used as the output, so we can get an output voltage which is proportional to the input voltage (Gray, 2001). This is:(Eq.3) The circuit of figure 4 is established on the circuit of figure 3. In this circuit, there isSubstitute this formula into the Eq.3, we have:(Eq.4) If, Eq.4 is approximately equal to:(Eq.5) In this equation, can be either positive or negative. But in order to ensure the Q3 is turned on, must be larger than , which means must be positive. Thus this analog multiplier can only work in 2 quadrants, the first quadrant and the second quadrant.2.3 The Gilbert CellThe basic Gilbert analog multiplier cell is presented in the figure 5.Fig.5 the circuit of Gilbert cellIn this circuit, the input voltage Vx and Vy can generate pairs of differential currents, which results in the collector currents of the transistors. According to Eq.2, there areThus, the combination of these 3 equations above gives the difference of two output currentsBecause the derivation of this derivation is based on the Eq.2, it must satisfy the same requirement, which is and . At this time, the output voltage isFrom this equation it can be seen that the output voltage is proportional to the product of Vx and Vy. However, different from the 2 quadrant multiplier, here the input signal Vy can be either positive or negative. So, an analog multiplier can be realised.3. Circuit design3.1 basic analog multiplier circuitThe circuit of the practical basic 4 quadrant multiplier build on the previous analysis is presented in the following figure.Fig.6 the 4 quadrant multiplier based on the Gilbert cellThe compositions of this circuit are resisters and transistors. For the rough design, current source is used directly. And the structure of two current sources is more sensitive than that of one current source, so the circuit will get a better balance characteristic. According to the analysis in 2.1, the exponential relationship between base-emitter voltage and collector current only remain in the range of 520mV-700mV. So the static base-emitter current can be chosen at 610mV, the middle point of thisrange. From figure 4, the corresponding collector current is about 0.2mA. In addition, the emitter current is approximately equal to the collector current. So 0.2mA can be set as the value of the current resources.In this circuit, the npn transistors are all 2N2222. It can be seen from the circuit that the function of the transistor pair Q7 and Q8 is transforming the voltage input signal into current input signal, so is the transistor pair Q5 and Q6. Thus, the multiplier operation is based on the variation of the currents. In addition, the four transistors Q7, Q8, Q9, Q10 and the resistor R2 consist of a block which can generate a signal of function. This current can compensate the function generated by the next transistors Q1, Q2, Q3 and Q4. Thus, the output current signal has no relationship with function, that means there is no limitation of (Gray, 2001). This feature significantly expands the input signal magnitude. The transistors Q5, Q6 and resistor R1 have the same feature and the limitation is also cancelled. The output of the nonlinear compensation block in the front of Gilbert cell isFor Ic7 and Ic8, there areSubstitute Ic7 and Ic8 into Eq.9, the output of the nonlinear compensation block is given byIn the Gilbert cell block, the emitter resistors of Q5 and Q6 are much smaller than R1, so we have . So Ic5 and Ic6 is given byUse Eq.11, Eq.12 and Eq.10 to calculate the output voltage based on the Eq.6, Eq.7 and Eq.8. Finally we can obtainFrom this equation and the above derivation, it can be seen that:When R1 and R2 is big enough, the output voltage Vo is proportional to theproduct of Vx and Vy. And the circuit will get the nearly ideal multiplierfunction.Both Vx and Vy can be positive and negative, so it is a 4 quadrant multiplier.The gain coefficient , which is determined by the paramount Rc,R1, R2 andK has no relationship with Vth, so this circuit has a nice thermal stability.In this circuit, because the current sources are all 0.2mA, a several independentcurrent sources based on the current mirror can be used.From Gray and Hurst, there are mainly 3 types of current mirrors: the simple current mirror, simple current mirror with beta () helper, and the Wilson current mirror (Gray, 2001). For the first one, the output current . For the third one, the outputcurrent is . It can easily be seen that the Wilson current mirror can geta much more precise output current. Thus, in this report, the Wilson current mirror isused as the current source. The whole structure is shown in figure 7.Fig.7 the circuit structure with mirror current sourceIn order to get a precise value of the current , a resistor is added between the Vdd and the current mirror transistor. The aimed current is 0.2mV, so the value of this resistor .Use LTSPICE to simulate the circuit. Here is the DC sweep for the circuit.Fig.8. The DC sweep simulation resultThe settings of this simulation are as the follows: sweep Vx from -13V to 13V, and the increment is 1V; sweep Vy from 13V to -13V, and the increment is 1V. During the design, it can be noticed that the magnitude of input signals have a proportional relationship with the product of and R1 (or R2). Besides, to get high amplitude of Vo, Eq.13 must be considered. In this report, the circuit has a nice linear range of output signal when the input signal varies from -13V to +13V. And the output signal has the same range with the input signals.In order to obtain this amplitude of output signal, the V dd and V EE are set up at +32V and -15V respectively.Transient simulation:Fig.8 simulation result for AC inputs Fig.10 simulation results for squareoperationThe settings of the simulation of figure 8 are as the follows:Vx: amplitude=13V; frequency=10 kHz; phase=0. Vy: amplitude=13V; frequency=10 kHz; phase=90o. The Vx input is a sin(t) signal, the Vy input is a cos(t) signal. In this simulation, the Vx and Vy contain all 4 quadrant inputs combinations in one period, which are (Vx>0, Vy>0), (Vx>0, Vy<0), (Vx<0, Vy<0), (Vx>0, Vy>0). So the results proved the circuit can work in 4 quadrants. Furthermore, the frequency of the output signal is twice as the input signals and the amplitude is about half of the input ones. These features satisfy the functionof. So the result proved the circuit can work as an analog multiplier.One useful application of analog multiplier is square operation. As the figure 10 shows, make the two pulse input signal same, then we can obtain a parabola output signal. So the results of can be calculated.Frequency response simulation:Fig.11 Simulation result of frequency responseThis figure shows the frequency response of the circuit. When theAmplitude-frequency characteristic decrease from -22dB to -25dB (increased by -3dB), the relative operation frequency is 500.4 kHz. Below this frequency, the circuit can work nicely.Another useful application of analog multiplier is modulator. In the modulator, the low frequency signal is used to modulate, and the high frequency signal acts as a carrier.Fig.12. modulator simulation: Vx has no DC offset Fig.13 modulator simulation: Vx has a 1.5V DC offsetIt can be seen from the above 2 figures, the frequency of the output signal can be changed by change the magnitude of the input signal.3.2 improvement of output signal amplifyThe output signal of the 3.1 circuit has double ends, which is not so convenient to the following circuits. Besides, for some applications, people need large output signals and a wide band width. This can be realised by adding a Double-ended input single-ended output circuit (shown in figure 14). This additional circuitconsist of a differential amplifier and a basic common collector circuit (shown infigure 15 and 16).Fig.14 2 ended inputs 1 ended output circuit Fig.15 LTP with activeloadFig.16 basic commoncollector circuitThe practical circuit with this addition output circuit is shown below.Fig.17 the circuit followed with 2 input ended 1 output ended circuit The DC sweep simulation is as follow (same setting as 3.1):Fig.18 the relative DC simulationCompared with figure 8, the output voltage increased, but the amplitude of output signal decreased. Furthermore, the common mode signal was amplified by the differential amplifier circuit, so the average value of output voltagebecomes to 22V. When Vx=0 or Vy=0, the output voltage equals to 22V. Thiscircuit can not operate as a multiplier. In a word, this additional circuit did not get the expected result.4. DiscussionAs the analysis showed in 3.1, the circuit of figure 6 can cancel the influence caused by temperature. This is because the differential and balance structure of the nonlinear composition block can remove the common mode signal. The temperature is physical paramount, which change by the same value in a small electric circuit. So noise caused by the temperature can be considered as the common mode signal. The circuit design in this report has a nice thermal stability.Use LTSPICE simulation, the power consumption of each and total elements can be detected easily. In order to reduce the power of the circuit, the current source should relatively be at a small value. But at the same time, the current should ensure the operation of the transistors.The limitation of this design is the same of the bipolar transistor. As the figure 2 shows, bipolar transistor has a limited exponential operation range. This feature asks for a highly accurate collector current control. To solve this problem, one way is to change the physical paramount of the transistor. For example, reduce the cross-section area. Another way is to use MOS transistors. Because the CMOS operation is based on the movement of majority carriers, there is no exponential relationship between drain current and drain-source voltage.5. ConclusionIn this report, an analog multiplier is proposed. Firstly, the principle of the design is introduced. Then a practical circuit is proposed. At the same time, the methods of how to change the paramount to achieve a suitable output signal are described. During the design, theory analyses and explains are also presented. The simulation is processed with LTSPICE. For this report, the results of simulation can satisfy the principle derivation. The designed circuit achieves its porpours.ReferenceGraeme.J.G., Tobey.G.E. and Huelsman. L.P. 1971. Operational Amplifiers: Design and Application. New York: McGRAW-HILL Book Company. (p.397-398)Peter Ashburn. 2003. SiGe Heterojunction Bipolar Transistors. West Sussex: John Wiley & Sons Ltd.GRAY Paul R. Analysis and design of analog integrated circuits. New York: John Wiley & Sons Ltd.。

乘法器与混频器

乘法器与混频器前言之前有人问过我这样的问题:乘法器和混频器到底有什么关系,混频器能不能用作乘法器?这里介绍一下它们的原理和异同点,相信各位都能有所理解。

乘法器乘法器正如其名,是做乘法的电子器件。

主要用途有调幅、调频、数学运算等。

真正数学意义上的乘法器全称四象限模拟乘法器。

所谓“四象限”指乘法器的两个输入信号的符号可能为正也可能为负均为双极性信号,此时乘法器能实现真正的数学意义上的乘法运算。

如果其中一个信号为单极性信号而另一个为双极性,那么称其为二象限。

如果全为单极性信号则为一象限。

但是通常我们在设计电路时并不会太多地设计四象限电路,所以一、二象限的应用更多一些。

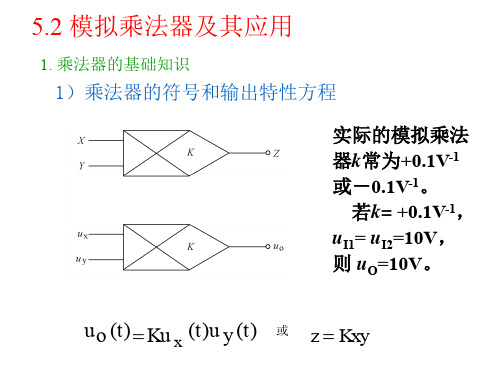

首先一个理想的乘法器的输出和两输入的乘积成比例,具有以下端口特性:Vout=K×VX×VYV_{out}=K \times V_{X} \times V_{Y} Vout =K×VX×VY当然并不局限于本例中的电压信号,电流信号也是可以的。

一开始的乘法器是基于对数放大器设计的,对数放大器和加法器就能构成乘法器。

Vout=log(VX)+log(VY)V_{out}=log(V_{X})+log(V_{Y})Vout=log(VX)+log(VY)但是这种结构的劣势也很明显。

对数放大器是基于PN结的,结果受温度影响较为明显。

同时这种结构较难设计高速电路,带宽比较受限。

而且这个结构只能实现一个象限内的运算。

后来一位叫巴里·吉尔伯特(Barrie Gilbert)的高人设计了名为吉尔伯特单元(Gilbert cell)的电路,这个电路直接改变了整个电子通信行业。

巴里·吉尔伯特(Barrie Gilbert,1937年6月5日至2020年1月30日)),IEEE终身院士、美国国家工程院院士、同时也是ADI的首位院士(ADI Fellow)。

他于1937年出生于英国伯恩茅斯,1972年担任ADI公司的IC设计师,成为第一代研究员,1979年创建ADI首个远程设计中心,此后一直专注于高性能模拟IC的开发。

模拟乘法器调幅(AM、DSB、SSB)实验报告

实验十二模拟乘法器调幅(AM、DSB、SSB)一、实验目的1.掌握用集成模拟乘法器实现全载波调幅。

抑止载波双边带调幅和单边带调幅的方法。

2.研究已调波与调制信号以及载波信号的关系。

3.掌握调幅系数的测量与计算方法。

4.通过实验对比全载波调幅、抑止载波双边带调幅和单边带调幅的波形。

5.了解模拟乘法器(MC1496)的工作原理,掌握调整与测量其特性参数的方法。

二、实验内容1.调测模拟乘法器MC1496正常工作时的静态值。

2.实现全载波调幅,改变调幅度,观察波形变化并计算调幅度。

3.实现抑止载波的双边带调幅波。

4.实现单边带调幅。

三、实验原理幅度调制就是载波的振幅(包络)随调制信号的参数变化而变化。

本实验中载波是由晶体振荡产生的465KHz高频信号,1KHz的低频信号为调制信号。

振幅调制器即为产生调幅信号的装置。

1.集成模拟乘法器的内部结构集成模拟乘法器是完成两个模拟量(电压或电流)相乘的电子器件。

在高频电子线路中,振幅调制、同步检波、混频、倍频、鉴频、鉴相等调制与解调的过程,均可视为两个信号相乘或包含相乘的过程。

采用集成模拟乘法器实现上述功能比采用分离器件如二极管和三极管要简单得多,而且性能优越。

所以目前无线通信、广播电视等方面应用较多。

集成模拟乘法器常见产品有BG314、F1596、MC1495、MC1496、LM1595、LM1596等。

(1)MC1496的内部结构在本实验中采用集成模拟乘法器MC1496来完成调幅作用。

MC1496是四象限模拟乘法器。

其内部电路图和引脚图如图12-1所示。

其中V1、V2与V3、V4组成双差分放大器,以反极性方式相连接,而且两组差分对的恒流源V5与V6又组成一对差分电路,因此恒流源的控制电压可图12-1 MC1496的内部电路及引脚图正可负,以此实现了四象限工作。

V7、V8为差分放大器V5与V6的恒流源。

(2)静态工作点的设定1)静态偏置电压的设置静态偏置电压的设置应保证各个晶体管工作在放大状态,即晶体管的集-基极间的电压应大于或等于2V ,小于或等于最大允许工作电压。

AD734模拟乘法器的原理与应用

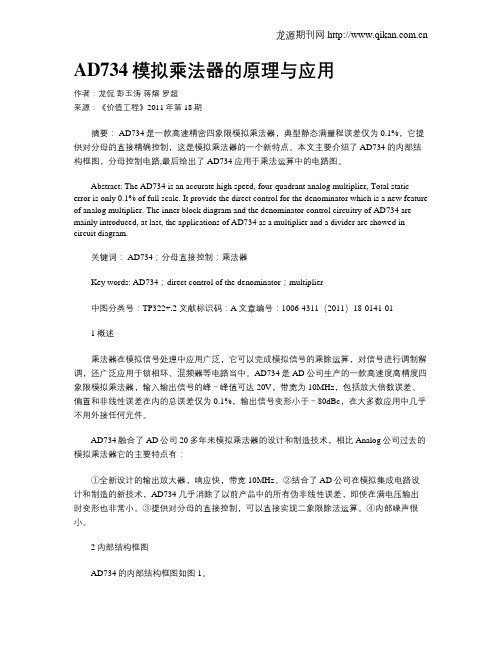

AD734模拟乘法器的原理与应用作者:龙侃彭玉涛蒋熔罗超来源:《价值工程》2011年第18期摘要: AD734是一款高速精密四象限模拟乘法器,典型静态满量程误差仅为0.1%,它提供对分母的直接精确控制,这是模拟乘法器的一个新特点。

本文主要介绍了AD734的内部结构框图,分母控制电路,最后给出了AD734应用于乘法运算中的电路图。

Abstract: The AD734 is an accurate high speed, four-quadrant analog multiplier, Total static error is only 0.1% of full scale. It provide the direct control for the denominator which is a new feature of analog multiplier. The inner block diagram and the denominator control circuitry of AD734 are mainly introduced, at last, the applications of AD734 as a multiplier and a divider are showed in circuit diagram.关键词: AD734;分母直接控制;乘法器Key words: AD734;direct control of the denominator;multiplier中图分类号:TP322+.2 文献标识码:A文章编号:1006-4311(2011)18-0141-011概述乘法器在模拟信号处理中应用广泛,它可以完成模拟信号的乘除运算,对信号进行调制解调,还广泛应用于锁相环、混频器等电路当中。

AD734是AD公司生产的一款高速度高精度四象限模拟乘法器,输入输出信号的峰-峰值可达20V,带宽为10MHz,包括放大倍数误差、偏置和非线性误差在内的总误差仅为0.1%,输出信号变形小于-80dBc,在大多数应用中几乎不用外接任何元件。

笔记

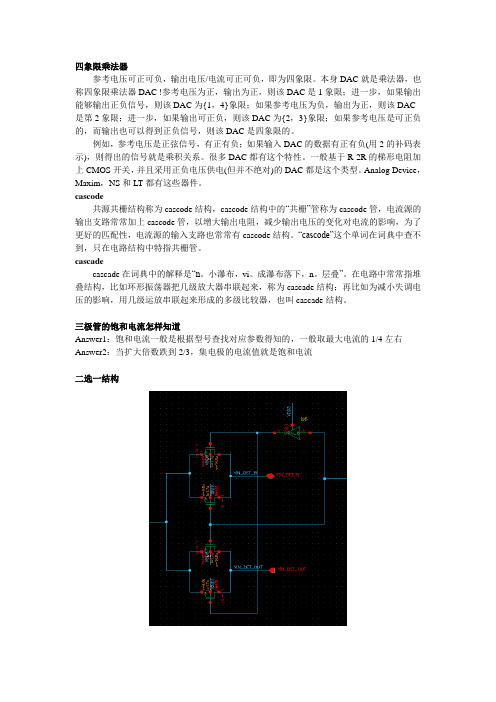

四象限乘法器参考电压可正可负,输出电压/电流可正可负,即为四象限。

本身DAC就是乘法器,也称四象限乘法器DAC !参考电压为正,输出为正,则该DAC是1象限;进一步,如果输出能够输出正负信号,则该DAC为{1,4}象限;如果参考电压为负,输出为正,则该DAC 是第2象限;进一步,如果输出可正负,则该DAC为{2,3}象限;如果参考电压是可正负的,而输出也可以得到正负信号,则该DAC是四象限的。

例如,参考电压是正弦信号,有正有负;如果输入DAC的数据有正有负(用2的补码表示),则得出的信号就是乘积关系。

很多DAC都有这个特性。

一般基于R-2R的梯形电阻加上CMOS开关,并且采用正负电压供电(但并不绝对)的DAC都是这个类型。

Analog Device,Maxim,NS和LT都有这些器件。

cascode共源共栅结构称为cascode结构,cascode结构中的“共栅”管称为cascode管,电流源的输出支路常常加上cascode管,以增大输出电阻,减少输出电压的变化对电流的影响,为了更好的匹配性,电流源的输入支路也常常有cascode结构。

“cascode”这个单词在词典中查不到,只在电路结构中特指共栅管。

cascadecascade在词典中的解释是“n。

小瀑布,vi。

成瀑布落下,n。

层叠”。

在电路中常常指堆叠结构,比如环形振荡器把几级放大器串联起来,称为cascade结构;再比如为减小失调电压的影响,用几级运放串联起来形成的多级比较器,也叫cascade结构。

三极管的饱和电流怎样知道Answer1:饱和电流一般是根据型号查找对应参数得知的,一般取最大电流的1/4左右Answer2:当扩大倍数跌到2/3,集电极的电流值就是饱和电流二选一结构。

四象限乘法

四象限乘法器是一种可以在四个象限内进行精确模拟乘法的电子元件,两个输入可能为正也可能为负,输出同样也可以是正或负。

从电路角度来看,四象限乘法器可以被理解为两个输入信号均为双极性的模拟乘法器。

在实际应用中,DAC(数模转换器)本来就具备乘法器的功能,因此也被称为四象限乘法器DAC。

参考电压和输出的关系决定了DAC所处的象限:当参考电压为正,输出也为正时,该DAC属于第1象限;若参考电压为负,而输出为正,则该DAC属于第2象限;如果参考电压和输出的符号都可能发生反转,那么该DAC就属于 {1,4}象限;最后,如果参考电压和输出的符号都可能变为正负,那么该DAC就是四象限DAC。

在所有四个象限对信号做精确模拟乘法绝非易事,因为需要处理的信号可正可负,并且乘法结果的符号也需要正确。

然而,由于并非所有应用都需要全四象限乘法器,所以常常使用的是仅支持一象限或二象限的精密器件。

例如,AD539就是一款宽带双通道二象限乘法器,而AD734则是一款高精度、高速的10MHz四象限乘法器/除法器。

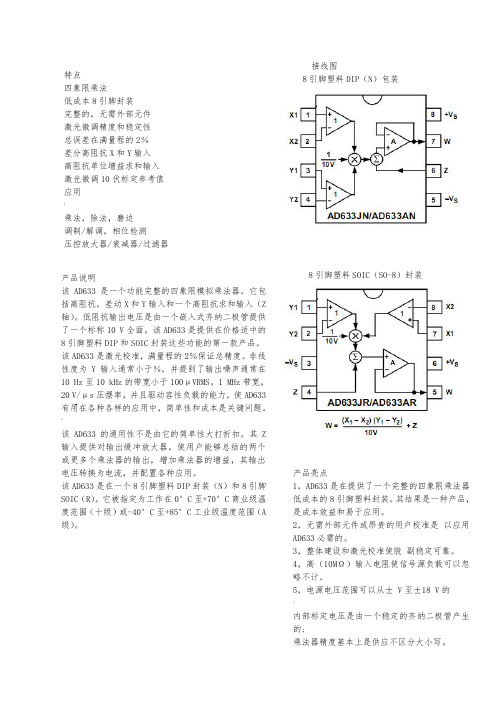

AD633四象限乘法器中文资料

接线图8引脚塑料DIP (N )包装"~.特点 四象限乘法 低成本8引脚封装 完整的,无需外部元件 激光微调精度和稳定性 总误差在满量程的2% 差分高阻抗X 和Y 输入 高阻抗单位增益求和输入 激光微调10伏标定参考值 应用 ! 乘法,除法,磨边调制/解调,相位检测 压控放大器/衰减器/过滤器 产品说明 该AD633是一个功能完整的四象限模拟乘法器。

它包括高阻抗,差动X 和Y 输入和一个高阻抗求和输入(Z 轴)。

低阻抗输出电压是由一个嵌入式齐纳二极管提供了一个标称10 V 全面。

该AD633是提供在价格适中的8引脚塑料DIP 和SOIC 封装这些功能的第一款产品。

该AD633是激光校准,满量程的2%保证总精度。

非线性度为Y 输入通常小于%,并提到了输出噪声通常在10 Hz至10 kHz 的带宽小于100μVRMS 。

1 MHz 带宽,20 V/μs 压摆率,并且驱动容性负载的能力,使AD633有用在各种各样的应用中,简单性和成本是关键问题。

"该AD633的通用性不是由它的简单性大打折扣。

其Z 输入提供对输出缓冲放大器,使用户能够总结的两个或更多个乘法器的输出,增加乘法器的增益,其输出电压转换为电流,并配置各种应用。

该AD633是在一个8引脚塑料DIP 封装(N )和8引脚SOIC (R )。

它被指定为工作在0°C 至+70°C 商业级温度范围(十级)或-40°C 至+85°C 工业级温度范围(A 级)。

8引脚塑料SOIC (SO-8)封装 产品亮点1,AD633是在提供了一个完整的四象限乘法器 低成本的8引脚塑料封装。

其结果是一种产品,是成本效益和易于应用。

2,无需外部元件或昂贵的用户校准是 以应用AD633必需的。

3,整体建设和激光校准使脱 副稳定可靠。

4,高(10M Ω)输入电阻使信号源负载可以忽略不计。

5,电源电压范围可以从± V 至±18 V 的 /内部标定电压是由一个稳定的齐纳二极管产生的;乘法器精度基本上是供应不区分大小写。

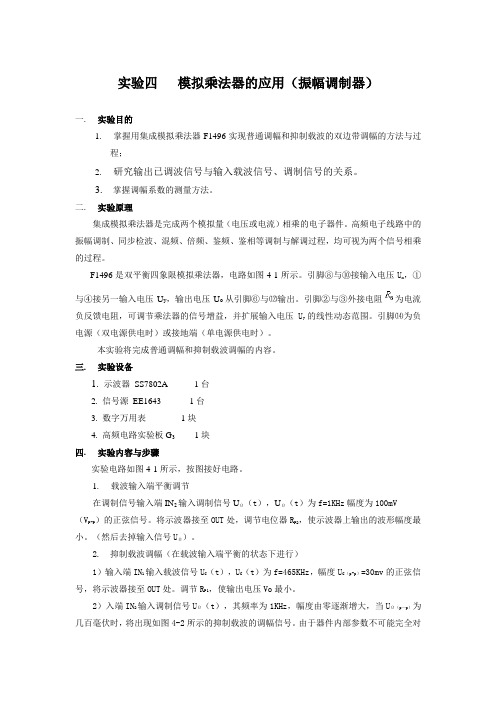

实验四 模拟乘法器的应用(振幅调制器)

实验四模拟乘法器的应用(振幅调制器)一.实验目的1.掌握用集成模拟乘法器F1496实现普通调幅和抑制载波的双边带调幅的方法与过程;2.研究输出已调波信号与输入载波信号、调制信号的关系。

3.掌握调幅系数的测量方法。

二.实验原理集成模拟乘法器是完成两个模拟量(电压或电流)相乘的电子器件。

高频电子线路中的振幅调制、同步检波、混频、倍频、鉴频、鉴相等调制与解调过程,均可视为两个信号相乘的过程。

F1496是双平衡四象限模拟乘法器,电路如图4-1所示。

引脚⑧与⑩接输入电压U x,①与④接另一输入电压U y,输出电压U o从引脚⑥与⑿输出。

引脚②与③外接电阻为电流负反馈电阻,可调节乘法器的信号增益,并扩展输入电压U y的线性动态范围。

引脚⒁为负电源(双电源供电时)或接地端(单电源供电时)。

本实验将完成普通调幅和抑制载波调幅的内容。

三.实验设备1. 示波器SS7802A 1台2. 信号源EE1643 1台3. 数字万用表1块4. 高频电路实验板G31块四.实验内容与步骤实验电路如图4-1所示,按图接好电路。

1.载波输入端平衡调节在调制信号输入端IN2输入调制信号UΩ(t),UΩ(t)为f=1KHz幅度为100mV(V P-P)的正弦信号。

将示波器接至OUT处,调节电位器R P2,使示波器上输出的波形幅度最小。

(然后去掉输入信号UΩ)。

2.抑制载波调幅(在载波输入端平衡的状态下进行)1)输入端IN1输入载波信号U C(t),U C(t)为f=465KHz,幅度U C(p-p)=30mv的正弦信号,将示波器接至OUT处。

调节R P1,使输出电压Vo最小。

2)入端IN2输入调制信号UΩ(t),其频率为1KHz,幅度由零逐渐增大,当UΩ(p—p)为几百毫伏时,将出现如图4-2所示的抑制载波的调幅信号。

由于器件内部参数不可能完全对称,致使输出波形出现漏载信号。

可通过调节电位器R P2来改善波形的对称性。

记录波形并测出V O(p-p)值。

双平衡四象限模拟乘法器工作原理

双平衡四象限模拟乘法器是一种常用于电子电路中的模拟乘法器,它可以对两个输入信号进行乘法运算,并输出它们的乘积。

这种乘法器可以在各种电子设备中使用,比如模拟信号处理系统、通信系统和控制系统等。

其工作原理主要基于双平衡调制技术和四象限运算技术,通过精确的电路设计和运算放大器的作用,实现了高精度和高线性度的模拟乘法运算。

1. 双平衡四象限模拟乘法器的基本原理双平衡四象限模拟乘法器主要由一个双平衡调制器和四象限运算放大器组成。

双平衡调制器是一种特殊的调制器,它可以对输入信号进行平衡混频处理,得到两路相位正交的信号。

四象限运算放大器是一种能够在所有四个象限内进行线性运算的运算放大器,通过它可以对两路输入信号进行乘法运算。

2. 工作原理分析两个输入信号分别经过双平衡调制器的处理,得到它们的正交相位信号。

这两路正交信号分别输入到四象限运算放大器中,进行乘法运算。

在四象限运算放大器内部,通过合适的反馈网络和控制电路,实现了对两路信号的乘法运算,并将乘积信号输出。

输出的乘积信号经过滤波、放大等后续处理,得到最终的模拟乘法器输出信号。

3. 特点和优势双平衡四象限模拟乘法器具有高精度、高线性度、宽带宽、低失真等特点和优势。

通过合理的电路设计和精确的参数选择,可以实现对输入信号的高精度乘法运算,输出信号的失真度极低,并且适用于宽频带的信号处理。

4. 应用领域双平衡四象限模拟乘法器广泛应用于各种模拟信号处理系统中,比如射频调制解调、通信系统中的信号处理、微波信号处理、医学成像系统中的信号处理等。

它在这些领域中可以实现高精度和高质量的信号处理,对系统的整体性能起到至关重要的作用。

总结:双平衡四象限模拟乘法器是一种非常重要和实用的模拟电路元件,它通过双平衡调制和四象限运算技术,实现了对两路输入信号的乘法运算,并具有高精度、高线性度、宽带宽、低失真等特点和优势。

它在电子电路中有着非常广泛的应用,对于各种模拟信号处理系统的设计和性能提升具有重要意义。

模拟乘法器AD834的原理与应用

模拟乘法器AD834的原理与应用1.AD834的主要特性AD834是美国ADI公司推出的宽频带、四象限、高性能乘法器,其主要特性如下:●带符号差分输入方式,输出按四象限乘法结果表示;输出端为集电极开路差分电流结构,可以保证宽频率响应特性;当两输入X=Y=±1V时,输出电流为±4mA;●频率响应范围为DC~500MHz;●乘方计算误差小于0.5%;●工作稳定,受温度、电源电压波动的影响小;●低失真,在输入为0dB时,失真小于0.05%;●低功耗,在±5V供电条件下,功耗为280mW;●对直通信号的衰减大于65dB;●采用8脚DIP和SOIC封装形式。

2.AD834的工作原理AD834的引脚排列如图1所示。

它有三个差分信号端口:电压输入端口X=X1-X2和Y=Y1-Y2,电流输出端口W=W1-W2;W1、W2的静态电流均为8.5mA。

在芯片内部,输入电压先转换为差分电流(V-I转换电阻约为280Ω),目的是降低噪声和漂移;然而,输入电压较低时将导致V-I转换线性度变差,为此芯片内含失真校正电路,以改善小信号V-I转换时的线性特性。

电流放大器用于对乘法运算电路输出的电流进行放大,然后以差分电流形式输出。

AD834的传递函数为:W=4XY (X、Y的单位为伏特,W的单位为mA)3.应用考虑3.1 输入端连接尽管AD834的输入电阻较高(20kΩ),但输入端仍有45μA的偏置电流。

当输入采用单端方式时,假如信号源的内阻为50Ω,就会在输入端产生1.125mV的失调电压。

为消除该失调电压,可在另一输入端到地之间接一个与信号源内阻等值的电阻,或加一个大小、极性可调的直流电压,以使差分输入端的静态电压相等;此外,在单端输入方式下,最好使用远离输出端的X2、Y1作为输入端,以减小输入直接耦合到输出的直通分量。

应当注意的是,当输入差分电压超过AD834的限幅电平(±1.3V)时,系统将会出现较大的失真。

四象限乘法器/除法器在伽玛相机中的应用

四象限乘法器/除法器在伽玛相机中的应用AD734是Analog Devices(AD公司)的产品,与同类产品相比,具有挺直除法模式,可以利用外部输入挺直控制除法模式中的分母电压,用法起来相当灵便便利。

而其他同类产品除法模式的分母电压只能由内部提供,外部无法控制。

AD734还可以作为调制器、解调器、宽带增益控制器、直流均方根转换器、压控、和用法,用途十分广泛。

?1 AD734的基本结构及功能AD734是一个高精度、高速四象限模拟乘法器/除法器,他与符合工业标准的模拟乘法器/除法器AD534引脚相互兼容,其传递函数为W=XY/U。

他具有以下特点:(1) 高精度:0.1%的典型误差。

(2) 高速:10 MHz满功率带宽;450 V/μs的回转率;升高到满功率的0.1%需200 ns。

(3)低失真:随意输入信号的失真均为-80 dB。

(4)低噪声:10 Hz~20k Hz时,信噪比为94 dB;10 Hz~10M Hz时,信噪比为70 dB。

(5)挺直除法模式。

(6)增益为100时,带宽为2 MHz。

图1所示为AD734的管脚暗示图。

其详细管脚定义如下:X1和X2:差动输入端;Y1和Y2:差动输入端;Z1和Z2:差动输入端;U0,U1,U2:分母电压控制端;W:输出端;VP:正电源供电;DD:电压控制使能;ER:参考电压;VN:负电源供电。

AD734与AD534相比,其先进的功能有:(1)AD734是一个新型的输出放大器。

在满功率带宽10 MHz时,AD734的回转率(450V/μs)要比AD534(20 V/μs)高出20多倍。

(2)AD734的失真十分低,即使在满功率的状况下也一样。

在AD734的设计中采纳了新的电路设计技术及激光微调技术,消退了全部的寄生非线性误差,而这些误差在早期的设计中是无法消退的。

(3)AD734可以实现分母电压的挺直控制。

外部输入在10 mV~10 V之间的随意值均可代替分母电压。

四象限乘法器

由式(4.3.1)可知, I0(t)与g(t)均是与u2无关的参数, 故iC与 u2可看成一种线性关系, 但是I0(t)与g(t)又是随时间变化的, 所以将这种工作状态称为线性时变工作状态。

若u1=Um1cosω1t, u2=Um2cos ω2t, 由图4.3.1可以看出, 在 周期性电压UQ+Um1cos·ω1t 作用下, g(t)也是周期性变化的,

对于变容二极管, 它的库伏特性不仅是一条曲线, 而且 它的法伏特性在C-u平面上也是一条曲线, 其表达式如第4章 (4.4.1)式所示。

由图例4.2可见, 当u=-UQ+Uscosωst时, 结电容Cj是一个 周期性的略为失真的余弦函数, 故可展开为傅里叶级数 Cj=C0+ cos nωst。将此式和u的表达式一起代入式(4.2.4), 可以求得i=-ωs

如果u2u1, 则可以认为晶体管的工作状态主要由UQ与u1

决定,

(UQ+u1)处将输出电流iC展开为幂

级数, 可以得到:

iC=f(uBE)=f(UQ+u1+u2)

=f(UQ+u1)+f′(UQ+u1)u2+ (UQ+u1)un2+…

f″(UQ+u1)u22+…+ f(n)

因为u2很小, 故可以忽略u2的二次及以上各次谐波分量, 由此简化为:

虽然在线性放大电路里也使用了晶体管这一非线性器 件, 但是必须采取一些措施来尽量避免或消除它的非线性效 应或频率变换效应, 而主要利用它的电流放大作用。 例如, 使小信号放大电路工作在晶体管非线性特性中的线性范围 内, 在丙类谐振功放中利用选频网络取出输入信号中才有的 有用频率分量而滤除其它无用的频率分量, 等等。

MC1594L四象限模拟乘法器

MC1594L四象限模拟乘法器模拟相乘器是一种时变参量电路。

在高频电路中,相乘器是实现频率变换的基本组件,与一般非线性器件相比,相乘器可进一步克服某些无用的组合频率分量,使输出信号频谱得以净化。

在通信系统及高频电子技术中应用最广的乘法器有两种,一种是二极管平衡相乘器,另一种是由双极型或 MOS 器件构成的四象限模拟相乘器。

随着集成电路的发展,这些相乘器还具有工作频带宽、温度稳定性好等优点,广泛用于调制、解调及混频电路中。

四象限模拟乘法器又大致分为两种。

一种是在集成高频电路中经常用到的乘法器,它们大多属于非理想乘法电路,是为了完成某种功能而制成的一种专用集成电路,如电视接收机中的视频信号同步检波电路、相位检波电路以及调频立体声接收机中的立体声解码电路等。

这种乘法电路均采用差动电路结构。

另一种是较为理想的模拟乘法器,属于通用的乘法电路,用户可用这种乘法器按需要设计,完成其功能。

常用的集成化模拟乘法器的产品有 BG314 、MC1494L/MC1594L 、MC1495L/MC1595L 、XR-2208/XR2208M 、AD530 、AD532 、AD533 、A D534 、AD632 、BB4213 、BB421等。

相乘器的基本特性及实现方法:若输入信号分别用v 1 ( t ) 和v 2 ( t ) 表示,输出信号用v o ( t ) 表示,则理想模拟乘法器的传输特性方程可表示为v o ( t )= K v 1 ( t ) v 2 ( t ) (4-18)式中,K 是乘法器的比例系数或增益系数。

该式表明,对一个理想的相乘器,其输出电压的瞬时值v o ( t ) 仅与两个输入电压在同一时刻的瞬时值v 1 ( t ) 和v 2 ( t ) 的乘积成正比,而不包含任何其它分量。

输入电压v 1 ( t ) 和v 2 ( t ) 可以是任意的,即其波形、幅度、极性和频率 ( 包括直流 ) 均不受限制。

1.MC1594L四象限乘法器原理图:用MC1594L模拟乘法器做交流电压乘法器(其原理图):2.各部分电路进行分析:该电路主要分为三个部分:(1)电压调整器:电压调整器就是使输出电压在一定条件下保持稳定当输入电压改变,负载条件变时,输出电压要尽可能保持不变。

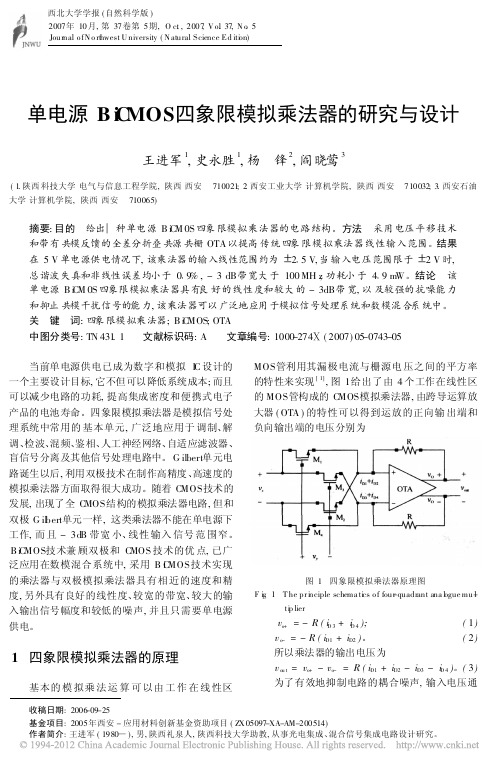

单电源BiCMOS四象限模拟乘法器的研究与设计

所以乘法器的输出电压为

v ou t = vo+ - vo- = R ( iD1 + iD2 - iD3 - iD 4 )。( 3) 为了有效地抑制电路的耦合噪声, 输入电压通

收稿日期: 2006-09-25 基金项目: 2005年西安 - 应用材料创新基金资助项目 ( ZX 05097-XA-AM-200514) 作者简介: 王进军 ( 1980) ), 男, 陕西礼泉人, 陕西科技大学助教, 从事光电集成、混合信号集成电路设计研究。

1 四象限模拟乘法器的原理

基本的 模 拟乘 法 运 算 可 以由 工 作 在 线 性区

MOS管利用其漏极电流与栅源电 压之间的平方率 的特性来实现 [ 1] , 图 1给出了由 4 个工作在线性区 的 MOS管构成的 CMOS模拟乘法器, 由跨导运算放 大器 ( OTA ) 的特性可以得到运放的正向输 出端和 负向输出端的电压分别为

vout = R Bvx vy。

( 6)

2 B iCMOS 四象限模拟乘法器的原 理、设计与实现

211 模拟乘法器的 BiCM OS实现 由前面 的分 析 可 知, 要 完 成 模 拟 乘法 运 算,

CMOS 模拟 乘法 器 中的 MOS 管 必须 工作 在 线性 区 [ 2] , 这就要求图 2( a) 中 V a - V b - VTH > 0, 从而使 得输入范围受到了很大的限制。一种改进的方法是 采用图 2( b) 所示的 B iCMO S线性区跨导结构 [ 3] , 它 由一个被偏置在线性区的 NMO S 管 M i 和一个双极 晶体管 Q i 组成, 这种结构具有非常好的线性度和高 的输入阻抗。图 2 ( b) 中晶体管 Q i把 M i的漏极电位 钳位在 Vb - VBE, 如果满足 NMO S管工作在线性区的 条件: Vb - VBE < VDsat = V a - VTH, 即 Vb - VBE < V a - VTH, 在忽略衬偏效应的情况下可以得到

模拟电子技术5.2乘法器及其应用

若集成运放的同相输入端与反相输入端互换,则k和uI2的极 性应如何?

4) 开平方运算电路

uo1

uo1

R2 R1

ui

ui

i2

R1

R2

uo1 Kuo2

i1

-∞

+A +

uo

1R

u

2 (u )

R

O

KR

i

1

为实现上式,电路中uI、 uO、k的极性是什么?为什么? 若要uO<0,则有何变化? 若要求uI、 uO均大于0,则有何变化? 若集成运放的负反馈通路中为某种运算电路,则整个电 路实现其逆运算!

T1

T2

T3

i c3

Re

- VE E

3. 乘法器的应用

1) 乘法运算

uX uY

uo uo=KuXuY

实现了对正弦波

若uI 2Ui sin t

电压的二倍频变换

则uO 2kUi2 sin2 t 2kUi2 (1 cos2 t)

2) 平方和立方运算

ui

uo

ui

uo

平方运算电路

uo=K(ui)2

如何实现开三次方运算电路?

利用运算电路,求解方程。已知模拟乘法器的相乘因子为0.1V-1。

设x=uI,按运算顺序搭建电路。

调整uI,使 uO 为 0 的 uI 就是方程 的解;解 为1、4。 电路不唯 一!

已知R1=R2,求解uO= f (uI) = ? 二极管什么时候导通?什么时候截止?

uO uI

在集成运放应用电路中开关管的工作状态往往决定于输入 信号或输出信号的极性!

5.2 模拟乘法器及其应用

1. 乘法器的基础知识

四象限乘法应用电路

四象限乘法应用电路导言:四象限乘法应用电路是一种常见的电子电路,可用于将两个输入信号相乘并输出乘积信号。

这种电路通常在模拟电路和信号处理系统中使用,具有广泛的应用。

一、四象限乘法应用电路的原理四象限乘法应用电路的原理基于模拟电路中的乘法运算,通过将两个输入信号相乘,得到其乘积的结果。

这种电路的特点是可以处理正负信号,并且输出结果可以同时具有正负值。

二、四象限乘法应用电路的组成四象限乘法应用电路通常由四个关键部分组成:乘法器、输入信号调节电路、偏置电路和输出滤波电路。

1. 乘法器:乘法器是四象限乘法应用电路的核心部分,负责将两个输入信号相乘。

乘法器常用的实现方式有模拟乘法器和数字乘法器,其原理是基于集成电路中的乘法运算。

2. 输入信号调节电路:输入信号调节电路用于调节输入信号的幅值和偏置,以使其适应乘法器的工作范围。

这部分电路常用放大器、运算放大器等器件实现。

3. 偏置电路:偏置电路用于提供乘法器所需的偏置电压,以确保乘法器正常工作。

偏置电路通常由电阻、电容等元件组成,可以根据具体需求进行设计。

4. 输出滤波电路:输出滤波电路用于滤除乘法器输出信号中的杂散频率成分,得到干净的乘积信号。

常用的输出滤波电路有低通滤波器、带通滤波器等。

三、四象限乘法应用电路的应用四象限乘法应用电路在模拟电路和信号处理系统中有广泛的应用。

以下是几个常见的应用场景:1. 模拟调制解调器:四象限乘法应用电路可以用于模拟调制解调器中的信号调制和解调过程。

通过将调制信号和载波信号进行乘法运算,可以实现信号的调制和解调。

2. 音频处理器:四象限乘法应用电路可以用于音频处理器中的音频混合、音效处理等功能。

通过将不同音频信号进行乘法运算,可以实现音频信号的混合和处理。

3. 信号调幅:四象限乘法应用电路可以用于信号调幅过程中的幅度调制。

通过将调制信号和载波信号进行乘法运算,可以实现信号的幅度调制。

4. 功率放大器:四象限乘法应用电路可以用于功率放大器中的功率控制。

第六章第6个知识点 乘法和除法运算电路

uX

iC4 2UT

uX

)Rc

RcuX 2UT

( iC3

iC4

)

RcuX uY UT RY

乘法器符号如图所示。

uX

X

uO

uY

Y

(a)不带运放的乘法器符号

uX

X

uY

Y

uO

(b)带运放的乘法器符号

乘法器的表示符号

数控技术

uO KuX uY

乘法器的应用

利用集成模拟乘法器和集成运算放大器可组成平方、除法及开方等 运算电路。 在通信设备中可作平衡调制器,同步检波器、鉴频器、混频器等; 在测量技术中可以进行单相功率测量、三相功率测量、功率因数的 测量等; 此外还可以作为倍频器、压控滤波器等。

uX

R1

_

+ Rb

1

uY

R1

_

+ Rb

1

T R2

uo

1

T R2

uo

2

uO2

U T

ln

uY R1IS2

uO3 (uO1 uO2 )

R2

_

+

uo

Rb

3

2

R3

_

uI

T +

uo

Rb

3

uO

R3

I euO3 S3

/UT

uO1

U T

ln

uX R1IS1

uO2

U T

ln

uY R1IS2

uO3

(uO1

uO2 )

乘除运算电路

广泛应用于信号处理、信号检测、通信工程、自动控制等科学领域。

1.乘法运算电路 对数式乘法器

Z =X *Y =eln( X *Y ) eln X +lnY

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

四通道四象限模拟乘法器MLT04

四通道四象限模拟乘法器MLT04

1MLT04的结构功能和主要特点

在高频电子线路中,振幅调制、同步检波、混频、倍频、鉴频等调制与解调的过程均可视为两个信号相乘的过程,而集成模拟乘法器正是实现两个模拟量电压或电流相乘的电子器件。

采用集成模拟乘法器实现上述功能比用分立器件要简单得多,而且性能优越,因此集成模拟乘法器在无线通信、广播电视等方面应用较为广泛。

在目前的乘法器中,单通道器件(如MOTOROLA的MC1496)无法实现多通道的复杂运算;二象限器件(如ADI公司的AD539)又会使负信号的应用受到限制。

而ADI公司的MLT04则是一款完全四通道四象限电压输出模拟乘法器,这种完全乘法器克服了以上器件的诸多不足之处,适用于电压控制放大器、可变滤波器、多通道功率计算以及低频解调器等电路。

非常适合于产生复杂的要求高的波形,尤其适用于高精度CRT显示系统的几何修正。

其内部结构及引脚排列如图1所示。

MLT04是由互补双极性工艺制作而成,它包含有四个高精度四象限乘法单元。

温度漂移小于0.005%/℃。

0.3μV/Hz的点噪声电压使低失真的Y通道只有0.02%的总谐波失真噪声,四个8MHz通道的总静止功耗也仅为150mW。

MLT04的工作温度范围为-40℃~+85℃。

MLT04的其它主要特性如下:

●四个独立输入通道;

●四象限乘法信号;

●电压输入电压输出;

●乘法运算无需外部元件;

●电压输出:W=(X×Y)/2.5V,其中X或Y上的线性度误差仅为0.2%;

●具有优良的温度稳定性:0.005%;

●模拟输入范围为±2.5V,采用±5V电压供电;

●低功耗一般为150mW。

2误差源和非线性

模拟乘法器的静态误差主要由输入失调电压、输出偏置电压、比例系数以及非线性度引起。

在这四种误差源中,只有X和Y的输入失调电压可以由外部调整。

而MLT04的输出偏置电压在出厂时已由厂家调整至50mV,比例系数在整个量程之内被内部调整为2.5%。

MLT04的输入失调电压的误差可以采用图2所示的可变失调电压调整电路来消除。

这种电路还可以减小乘法器内核中的输出偏置电压、增益误差以及非线性器件引起的固有误差。

乘法器的内部非线性是器件的固有误差。

它指的是所有成对输入值的实际输出与理想的线性理论输出值之间的差值。

其定义是在完全没有电流误差时,误差量与满刻度的百分比。

在最坏的情况下,MLT04的X输入端的最大非线性也小于0.2%,Y输入端的最大非线性仅为0.06%。

因此,在应用于调制解调器或是混频器时,最好将载波信号由X输入端输入,而实际信号由Y输入端输入。

3应用电路

3.1乘法器

图3所示为乘法器的基本连接方法。

四个独立通道中的每一个通道都是由两个单端电压输入(X和Y)和一个低阻抗电压输出(W)组成,而且每个通道都有自己专有的接地,这些接地都被接至模拟地。

为了达到最好的性能,电路布局一定要紧凑并且连线要短,电源电压的馈电电流要旁路。

不用的通道引脚要接地。

3.2平方和倍频器

如需对输入信号进行平方运算,可将输入信号VIN并行的同时接到X和Y输入端以产生输出信号VIN/2.5V。

这里的输入信号可以是任意极性,但得到的输出信号一定是正值。

图4为平方运算电路。

如果输入是正弦波VINsinωt,由以下的三角公式可知,平方电路也可以作为倍频器:此外通过反乘法器配置还可利用MLT04来设计除法器和平方根函数发生器等电路。

图6中,当VX从25mV变化到2.5V时,滤波电路的截至频率也将从1kHz变化到100kHz。

因此,利用这种方法可以构造出中心频率、通带增益以及Q值等参数由直流电压控制的滤波器。

(VINsinωt)2/2.5V=V2IN(1-cosωt)/(2×2.5V)

由上式还可看出,输出中含有直流部分,直流随着输入VIN的变化会发生很大变化。

通过高通滤波器可以除去MLT04输出中的直流偏置。

为了得到理想的频率特性,高通滤波器的截止频率应该接近输入信号的基频。

这种配置中的一个基本误差源是X和Y输入端的失调电压。

输入的失调电压和输入信号混在一起将导致输出波形失真。

为了解决这一问题,图5电路中,利用双运放OP285提供的反相放大器可以调整X和Y输入端的失调。

3.3压控低通滤波器

图6所示是用模拟乘法器MLT04构成的一个压控低通滤波器。

比传统的滤波器配置相比这种技术的好处在于滤波器的截至频率ω0直接正比于乘法器的输入电压。

这使得滤波器中的电容可以由电压控制,从而可以直接或间接调整。

这样滤波器的频率特性就可以在不影响其它参数的情况下由一个单独的电压进行控制。