Compiler-Directed Scratch Pad Memory Hierarchy Design and Management

Memory Compiler

SEC ASIC

5-1

STDL80

MEMORY COMPILERS SELECTION GUIDE

MEMORY COMPILERS

In 0.5µm CMOS standard cell memory compilers, the y-mux type selecting option was added to give the customers freedom selecting aspect ratio of the memory layout. Many of the characteristics of a memory cell are depend on its y-mux type. So, when you change the y-mux type from one to the other to change the aspect ratio, you have to know that it will change many major characteristics, such as access time, area and power consumption, of the memory. < Figure 1. Example of Y-mux Types and Aspect Ratio >

y-mux ቤተ መጻሕፍቲ ባይዱ 4

y-mux = 8

y-mux = 16

Dual Banks

In some of 0.5µm CMOS standard cell memory compilers is a generator option which defines the number of bit array banks. This dual bank scheme doubles the maximum capacity of the memory compilers.

计算机编程英语

page replacement algorithm 页替换算法

paged segments 段页式管理

PCB(process control block) 进程控制块

peer entities 对等实体

period 时期 周期

phase 阶段 局面 状态

multiple - term formula 多项式

multiplexing 多路复用技术

multiplication 乘法

mutual exclusion 互相 排斥

non - key attributes 非码属性

Nyquist 奈奎斯特

object oriented 对象 趋向的 使适应的

process 过程 加工 处理

program debugging 程序排错

projection selection join 投影 选择 连接

protocol 协议

prototype 原型 样板

prototyping method(model) 原型化周期(模型)

pseudo - code 伪码(程序设计语言PDL)

IPC 工业过程控制

ISAM VSAM 索引顺序存取方法 虚拟存储存取方法

join/natural join/semi join 连接/自然连接/半连接

kernel executive supervisor user 核心 执行 管理 用户

kernels 核心程序

key comparison 键(码)值比较

Manchester 曼彻斯特

map 地图 映射图

matrix 矩阵 点阵

XDAIS标准

现代软件开发,已从上世纪的面向过程编程发展到当前的面向框架编程。

软件开发经验已证明:框架话、模块化的开发方式可以极大的提高软件开发效率,提高代码质量及代码重用率。

然而,在嵌入式编程中,由于长期缺乏完善的开发框架和可用的API,开发人员依旧利用C或汇编语言和底层硬件打交道,凡是亲力亲为,这必然会增加嵌入式开发的入门门槛,降低代码的重用性,甚至增加代码易集时的复制度(不过这些缺点,对于程序员来说确是好事,入门门槛高、开发复制意味着高付出高回报,不像现在桌面电脑端的开发,已经被人研究烂了,如果你不是超超超超级大牛,根本找不到一份满意的薪水)。

基于这点,TI公司发布了一套DSP算法标准——TMS320 DSP Algorithm Standard,规范了DSP算法软件的开发,并提供了类似C++语言类的封装方式的算法接口,使得算法集成变得简单统一。

XDAIS标准如果你对TMS320 DSP Algorithm Standard还陌生的话,那么如果提起另一个名字:xdais,那么就顺眼地多了。

没错,我们在Codec Engine文档中经常看到的xdais,实际上就是TMS320 DSP Algorithm Standard的另一个名字。

根据TI官方白皮书,xdais标准一共提供了39条规则,15条指南。

这些规则和指南一共分为4个部分:只要你的算法满足xdais标准,你也可以像笔记本上打上的“Vista Capable”那样,在算法上面打上TI的认证图标:IALG接口前面说了,xdais标准里含有39条标准,15个指南。

这些标准、指南几乎涵盖了整个DSP开发的生命周期,例如使用TI的C语言啊,所有C6x算法必须支持低位优先啊。

具体的规则可以参考《TMS320 DSP Algorithm Standard Rules and Guidelines User’s Guide》,本文不再讨论。

xdais作为一个DSP的开发框架,定义了一些接口:•IALG –为算法实例对象的创建定义了独立于框架的算法接口。

Memory-Compiler使用入门介绍

Memory Compiler使用介绍在使用Memory Compiler时,请务必确保你的RAM从头到尾的规格与设定都相同,否则会造成一些不可避免的错误。

首先在RTL代码阶段,要用到RAM就要用Artisan公司提供的Memory Compile产生的verilog代码,此时不需要着急产生其他后阶段的必要数据,因为RTL代码阶段,只需要行为级模型即可。

当进入门级代码后,RAM compiler就要产生其他的相关数据了,同时要考虑RAM版图的位置与方向。

由于一个大的设计不会设计一次就会完成,所以有两个重点,第一个是每次使用RAM compiler时都一定要让它产生特性设置文档,避免忘记自己做过的设定。

第二件事是对应的文件名要定义好,否则RAM的方向不同但是又用到了相同的文件名,就会把原始数据覆盖掉。

下图为SRAM在流程中需要产生的文档RTL阶段在RTL阶段主要只是产生verilog行为级和设置文件。

因为在RTL阶段不需要考虑RAM 的位置信息。

Memory Compiler提供4种选择,分别为ra1sh,ra2sh,rf1sh,rf2sh。

前面的ra与rf分别指的是SRAM与register file,其中rf在同样的情况下比ra占的面积小,但是rf的大小有限制,其限制大小位4096bits。

而后面1sh与2sh表示位单端口还是双端口,如果SRAM 的容量比较大的话,相同设置下,1sh比2sh面积要小,速度也要快,功耗要低。

Memory Compiler运行界面如下图所示instance name:该设置是对RAM的命名,由于ram的特性有地址和位数,所以在命名的时候尽量包含这些信息。

number of words:该设置用来确定RAM的深度,即寻址空间大小。

number of bits:该设置用来确定RAM的宽度。

frequency:该设置用来确定RAM的工作频率,该设置确定后就可以基本确定RAM的功耗,估计的结果位平均电流,通过该数据来设定电源环的宽度。

计算机专业常用英语

2.RISCReducedInstructionsetComputing 精简指令集计算技术

比较CISCcomplexInstructionsetComputing复杂指 令集计算技术

3.assignmentstatement赋值语句

4.optimizev.优化

optimizer优化器[程序]

4. package 软件包;( 封装 )外壳

packaged software 套装软件

比较 packet n. ( 信息 )包;( 报文 )分组 pack v. 压缩

5. descending sort 降序排序

比较 ascending sort 升序排序

7

2021/10/10

6. superscalar 超标量结构

8

2021/10/10

7. complex number 复数

比较 real number 实数

8. Multimedia Extensions 多媒体扩展(技术)

multimedia 多媒体 extension 扩展名

9. benckmark n. 基准(测试)程序

v. 测量性能

A test used to measure hardware or software performance. 一种用于测量硬件或软件性能的测试程序。

To change a program in order to be able to run it on a different computer.改变一个程序,使之能在不同的计算 机上运行。

24

2021/10/10

3.1 Boolean Algebra

1. Boolean algebra 布尔代数

编译原理术语中英文对照表

General left recursion

通常左递归

General LR(1) parsing algorithm 通用 LR(1)语法分析算法

Global data

全局数据

Global declaration Global optimization

全局声明 全局优化

Global variable GNU Bison parser generator

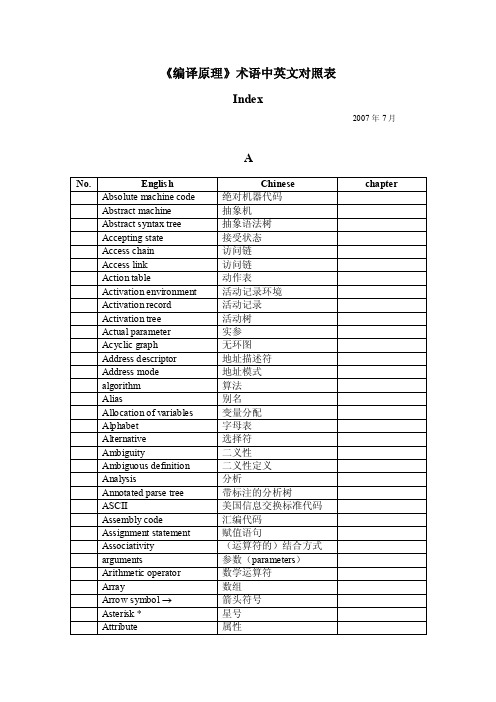

《编译原理》术语中英文对照表

Index

2007 年 7 月

No.

Englis h

Absolute machine code

Abstract machine

Abstract syntax tree

Accepting state

Access chain

Access link

Action table

Activation environment

F

Chinese 阶乘函数 有限自动机 First 集 一个词法分析器的自动 生成器 浮点除法 浮点数 浮点值类型 流图 Follow 集 形式定义 For 语句 编译器的前端 函数声明 函数定义

chapter

G

No.

Englis h

Chinese

Garbage collection

垃圾收集

General immediate left recursion 通常直接左递归

chapter

Attribute grammar Automata Automatic code generator Auxiliary routine Available expression

属性文法 自动机 代码自动生成 附属函数 有效表达式

sdcc 语法-概述说明以及解释

sdcc 语法-概述说明以及解释1.引言1.1 概述SDCC(Small Device C Compiler)是一款开源的C语言编译器,主要针对嵌入式系统和小型设备进行编译优化。

它具有高度的可移植性和灵活性,可在各种硬件平台上进行交叉编译,包括8位和16位微控制器和其他嵌入式设备。

与传统的C语言编译器相比,SDCC在资源受限的环境下表现出色。

它使用了许多优化技术,如占用内存的最小化、代码紧凑化、速度优化等,以最大程度地减小生成的机器码的大小和执行时间。

这将有助于提高嵌入式系统的性能和效率,适用于各种小型项目和嵌入式应用。

此外,SDCC还支持多种目标平台的编译,包括各种常用的嵌入式处理器和微控制器。

它提供了广泛的功能和库支持,可以方便地与其他外部设备和传感器进行交互。

这使得开发人员能够灵活地构建各种嵌入式应用,从简单的小型项目到复杂的嵌入式系统。

尽管SDCC是一款开源的编译器,但它的功能和性能丝毫不逊色于商业化的C编译器。

它经过多年的发展和改进,已经成为嵌入式系统开发中的重要工具之一。

在开发嵌入式软件时,选择SDCC作为编译器可以帮助开发人员提高代码质量、加快开发速度,并且兼顾项目的可维护性和可移植性。

总之,SDCC是一款优秀的C语言编译器,特别适用于嵌入式系统和小型设备。

它的高度可移植性、灵活性和优化技术使得开发人员能够高效地构建各种嵌入式应用。

无论是初学者还是有经验的开发人员,都可以通过学习和使用SDCC来掌握嵌入式系统开发的核心技能,为各种小型项目和嵌入式应用提供高效、可靠的解决方案。

1.2文章结构文章结构是指文章的整体组织框架,它有助于读者更好地理解文章的内容和思路。

本文的结构由引言、正文和结论三个部分组成。

引言部分介绍了整篇文章的背景和内容概要。

在引言的基础上,文章的结构被进一步展示出来。

因此,引言可被看作是整个文章结构的一个入口。

正文部分是论述文章的重点内容。

它由多个要点组成,每个要点以二级标题的形式呈现。

introduction Compiler

LLi

15

G di Policies Grading P li i

LLi 4

Course Objectives

Programming Language Design

– Strengthens the understanding of the key concepts of f programming i languages l – Provides the theoretical foundation and implementation skills for designing and implementing programming languages.

#include <stdio.h> int main ( ) { int i, j; i = 1; i 1; j = i++ + ++i; printf("%d\n", j); }

LLi 8

•

“ The world of compiler design has changed significantly. Programming languages have evolved to present new compilation problems. Computer architectures offer a variety of resources of which hi h th the compiler il d designer i must tt take k advantage. d t P Perhaps h most t interestingly, the venerable technology of code optimization has found use outside compilers. It is now used in tools that find bugs in software and most importantly software, importantly, find security holes in existing code code. And much of the "front-end" technology - grammars, regular expressions, parsers, and syntax-directed translators – are still in wide use.” use. “ We recognize g that few readers will build, or even maintain, a compiler for a major programming language. Yet the models, theory, and algorithms associated with a compiler can be applied to a wide range of problems in software design and software development . W therefore We th f emphasize h i problems bl th that t are most t commonly l encountered in designing a language processor, regardless of the source language or target machine. ”

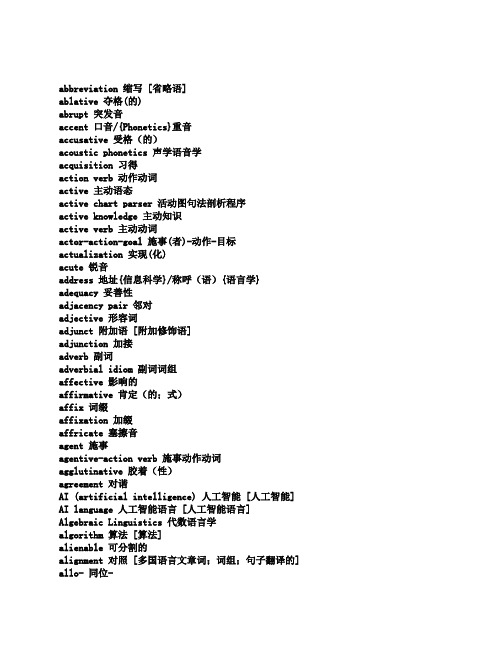

自然语言处理中英文术语对照

abbreviation 缩写 [省略语]ablative 夺格(的)abrupt 突发音accent 口音/{Phonetics}重音accusative 受格(的)acoustic phonetics 声学语音学acquisition 习得action verb 动作动词active 主动语态active chart parser 活动图句法剖析程序active knowledge 主动知识active verb 主动动词actor-action-goal 施事(者)-动作-目标actualization 实现(化)acute 锐音address 地址{信息科学}/称呼(语){语言学} adequacy 妥善性adjacency pair 邻对adjective 形容词adjunct 附加语 [附加修饰语]adjunction 加接adverb 副词adverbial idiom 副词词组affective 影响的affirmative 肯定(的;式)affix 词缀affixation 加缀affricate 塞擦音agent 施事agentive-action verb 施事动作动词agglutinative 胶着(性)agreement 对谐AI (artificial intelligence) 人工智能 [人工智能] AI language 人工智能语言 [人工智能语言]Algebraic Linguistics 代数语言学algorithm 算法 [算法]alienable 可分割的alignment 对照 [多国语言文章词;词组;句子翻译的] allo- 同位-allomorph 同位语素allophone 同位音位alpha notation alpha 标记alphabetic writing 拼音文字alternation 交替alveolar 齿龈音ambiguity 歧义ambiguity resolution 歧义消解ambiguous 歧义American structuralism 美国结构主义analogy 类推analyzable 可分析的anaphor 照应语 [前方照应词]animate 有生的A-not-A question 正反问句antecedent 先行词anterior 舌前音anticipation 预期 (音变)antonym 反义词antonymy 反义A-over-A A-上-A 原则apposition 同位语appositive construction 同位结构appropriate 恰当的approximant 无擦通音approximate match 近似匹配arbitrariness 任意性archiphoneme 大音位argument 论元 [变元]argument structure 论元结构 [变元结构] arrangement 配列array 数组articulatory configuration 发音结构articulatory phonetics 发音语音学artificial intelligence (AI) 人工智能 [人工智能] artificial language 人工语言ASCII 美国标准信息交换码aspect 态 [体]aspirant 气音aspiration 送气assign 指派assimilation 同化association 关联associative phrase 联想词组asterisk 标星号ATN (augmented transition network) 扩充转移网络attested 经证实的attribute 属性attributive 属性auditory phonetics 听觉语音学augmented transition network 扩充转移网络automatic document classification 自动文件分类automatic indexing 自动索引automatic segmentation 自动切分automatic training 自动训练automatic word segmentation 自动分词automaton 自动机autonomous 自主的auxiliary 助动词axiom 公理baby-talk 儿语back-formation 逆生构词(法)backtrack 回溯Backus-Naur Form 巴科斯诺尔形式 [巴科斯诺尔范式] backward deletion 逆向删略ba-construction 把─字句balanced corpus 平衡语料库base 词基Bayesian learning 贝式学习Bayesian statistics 贝式统计behaviorism 行为主义belief system 信念系统benefactive 受益(格;的)best first parser 最佳优先句法剖析器bidirectional linked list 双向串行bigram 双连词bilabial 双唇音bilateral 双边的bilingual concordancer 双语关键词前后文排序程序binary feature 双向特征[二分征性]binding 约束bit 位 [二进制制;比特]biuniqueness 双向唯一性blade 舌叶blend 省并词block 封阻[封杀]Bloomfieldian 布隆菲尔德(学派)的body language 肢体语言Boolean lattice 布尔网格 [布尔网格]borrow 借移Bottom-up 由下而上bottom-up parsing 由下而上剖析bound 附着(的)bound morpheme 附着语素 [黏着语素]boundary marker 界线标记boundary symbol 界线符号bracketing 方括号法branching 分枝法breadth-first search 广度优先搜寻 [宽度优先搜索]breath group 换气单位breathy 气息音的buffer 缓冲区byte 字节CAI (Computer Assisted Instruction) 计算机辅助教学CALL (computer assisted language learning) 计算机辅助语言学习canonical 典范的capacity 能力cardinal 基数的cardinal vowels 基本元音case 格位case frame 格位框架Case Grammar 格位语法case marking 格位标志CAT (computer assisted translation) 计算机辅助翻译cataphora 下指Categorial Grammar 范畴语法Categorial Unification Grammar 范畴连并语法 [范畴合一语法] causative 使动causative verb 使役动词causativity 使役性centralization 央元音化chain 炼chart parsing 表式剖析 [图表句法分析]checked 受阻的checking 验证Chinese character code 中文编码 [汉字代码]Chinese character code for information interchange 中文信息交换码[汉字交换码]Chinese character coding input method 中文输入法 [汉字编码输入] choice 选择Chomsky hierarchy 杭士基阶层 [Chomsky 层次结构]citation form 基本形式CKY algorithm (Cocke-Kasami-Younger) CKY 算法classifier 类别词cleft sentence 分裂句click 啧音clitic 附着词closed world assumption 封闭世界假说cluster 音群Cocke-Kasami-Younger algorithm CKY 算法coda 音节尾code conversion 代码变换cognate 同源(的;词)Cognitive Linguistics 认知语言学coherence 一致性cohesion 凝结性 [黏着性;结合力]collapse 合并collective 集合的collocation 连用语 [同现;搭配]combinatorial construction 合并结构combinatorial insertion 合并中插combinatorial word 合并词Combinatory Categorial Grammar 组合范畴语法comment 评论commissive 许诺[语行]common sense semantics 常识语意学Communication Theory 通讯理论 [通讯论;信息论]Comparative Linguistics 比较语言学comparison 比较competence 语言知能compiler 编译器complement 补语complementary 互补complementary distribution 互补分布complementizer 补语标记complex predicate 复杂谓语complex stative construction 复杂状态结构complex symbol 复杂符号complexity 复杂度component 成分compositionality 语意合成性 [合成性]compound word 复合词Computational Lexical Semantics 计算词汇语意学Computational Lexicography 计算词典编纂学Computational Linguistics 计算语言学Computational Phonetics 计算语音学Computational Phonology 计算声韵学Computational Pragmatics 计算语用学Computational Semantics 计算语意学Computational Syntax 计算句法学computer language 计算器语言computer-aided translation 计算机辅助翻译 [计算器辅助翻译]computer-assisted instruction (CAI) 计算机辅助教学computer-assisted language learning 计算机辅助语言学习[计算器辅助语言学习] concatenation 串联concept classification 概念分类concept dependency 概念依存conceptual hierarchy 概念阶层concord 谐和concordance 关键词 (前后文) 排序concordancer 关键词 (前后文) 排序的程序concurrent parsing 并行句法剖析conditional decision 条件决定 [条件决策]conjoin 连接conjunction 连接词 (合取;逻辑积;"与";连词)conjunctive 连接的connected speech 连续语言Connectionist model 类神经网络模型Connectionist model for natural language 自然语言类神经网络模型[自然语言连接模型]connotation 隐涵意义consonant 子音 [辅音]constituent 成分constituent structure tree 词组结构树constraint 限制constraint propagation 限制条件的传递 [限定因素增殖]constraint-based grammar formalism 限制为本的语法形式Construct Grammar 句构语法content word 实词context 语境context-free language 语境自由语言 [上下文无关语言]context-sensitive language 语境限定语言 [上下文有关语言;上下文敏感语言] continuant 连续音continuous speech recognition 连续语音识别contraction 缩约control agreement principle 控制一致原理control structure 控制结构control theory 控制论convention 约定俗成[规约]convergence 收敛[趋同现象]conversational implicature 会话含义converse 相反(词;的)cooccurrence relation 共现关系 [同现关系]co-operative principle 合作原则coordination 对称连接词 [同等;并列连接]copula 系词co-reference 同指涉 [互指]co-referential 同指涉coronal 前舌音corpora 语料库corpus 语料库Corpus Linguistics 语料库语言学corpus-based learning 语料库为本的学习correlation 相关性counter-intuitive 违反语感的courseware 课程软件 [课件]coverb 动介词C-structure 成分结构data compression 数据压缩 [数据压缩]data driven analysis 资料驱动型分析 [数据驱动型分析]data structure 数据结构 [数据结构]database 数据库 [数据库]database knowledge representation 数据库知识表示 [数据库知识表示]data-driven 资料驱动 [数据驱动]dative 与格declarative knowledge 陈述性知识decomposition 分解deductive database 演译数据库 [演译数据库]default 默认值 [默认;缺省]definite 定指Definite Clause Grammar 确定子句语法definite state automaton 有限状态自动机Definite State Grammar 有限状态语法definiteness 定指degree adverb 程度副词degree of freedom 自由度deixis 指示delimiter 定界符号 [定界符]denotation 外延denotic logic 符号逻辑dependency 依存关系Dependency Grammar 依存关系语法dependency relation 依存关系depth-first search 深度优先搜寻derivation 派生derivational bound morpheme 派生性附着语素Descriptive Grammar 描述型语法 [描写语法]Descriptive Linguistics 描述语言学 [描写语言学] desiderative 意愿的determiner 限定词deterministic algorithm 决定型算法 [确定性算法] deterministic finite state automaton 决定型有限状态机deterministic parser 决定型语法剖析器 [确定性句法剖析程序] developmental psychology 发展心理学Diachronic Linguistics 历时语言学diacritic 附加符号dialectology 方言学dictionary database 辞典数据库 [词点数据库]dictionary entry 辞典条目digital processing 数字处理 [数值处理]diglossia 双言digraph 二合字母diminutive 指小词diphone 双连音directed acyclic graph 有向非循环图disambiguation 消除歧义 [歧义消除]discourse 篇章discourse analysis 篇章分析 [言谈分析]discourse planning 篇章规划Discourse Representation Theory 篇章表征理论 [言谈表示理论] discourse strategy 言谈策略discourse structure 言谈结构discrete 离散的disjunction 选言dissimilation 异化distributed 分布式的distributed cooperative reasoning 分布协调型推理distributed text parsing 分布式文本剖析disyllabic 双音节的ditransitive verb 双宾动词 [双宾语动词;双及物动词] divergence 扩散[分化]D-M (Determiner-Measure) construction 定量结构D-N (determiner-noun) construction 定名结构document retrieval system 文件检索系统 [文献检索系统] domain dependency 领域依存性 [领域依存关系]double insertion 交互中插double-base 双基downgrading 降级dummy 虚位duration 音长{语音学}/时段{语法学/语意学}dynamic programming 动态规划Earley algorithm Earley 算法echo 回声句egressive 呼气音ejective 紧喉音electronic dictionary 电子词典elementary string 基本字符串 [基本单词串]ellipsis 省略EM algorithm EM算法embedding 崁入emic 功能关系的empiricism 经验论Empty Category Principle 虚范畴原则 [空范畴原理]empty word 虚词enclitics 后接成份end user 终端用户 [最终用户]endocentric 同心的endophora 语境照应entailment 蕴涵entity 实体entropy 熵entry 条目episodic memory 情节性记忆epistemological network 认识论网络ergative verb 作格动词ergativity 作格性Esperando 世界语etic 无功能关系etymology 词源学event 事件event driven control 事件驱动型控制example-based machine translation 以例句为本的机器翻译exclamation 感叹exclusive disjunction 排它性逻辑 “或”experiencer case 经验者格expert system 专家系统extension 外延external argument 域外论元extraposition 移外变形 [外置转换]facility value 易度值feature 特征feature bundle 特征束feature co-occurrence restriction 特征同现限制 [特性同现限制] feature instantiation 特征体现feature structure 特征结构 [特性结构]feature unification 特征连并 [特性合一]feedback 回馈felicity condition 妥适条件file structure 档案结构finite automaton 有限状态机 [有限自动机]finite state 有限状态Finite State Morphology 有限状态构词法 [有限状态词法]finite-state automata 有限状态自动机finite-state language 有限状态语言finite-state machine 有限状态机finite-state transducer 有限状态置换器flap 闪音flat 降音foreground information 前景讯息 [前景信息]Formal Language Theory 形式语言理论Formal Linguistics 形式语言学Formal Semantics 形式语意学forward inference 前向推理 [向前推理]forward-backward algorithm 前前后后算法frame 框架frame based knowledge representation 框架型知识表示Frame Theory 框架理论free morpheme 自由语素Fregean principle Fregean 原则fricative 擦音F-structure 功能结构full text searching 全文检索function word 功能词Functional Grammar 功能语法functional programming 函数型程序设计 [函数型程序设计]functional sentence perspective 功能句子观functional structure 功能结构functional unification 功能连并 [功能合一]functor 功能符fundamental frequency 基频garden path sentence 花园路径句GB (Government and Binding) 管辖约束geminate 重叠音gender 性Generalized Phrase Structure Grammar 概化词组结构语法 [广义短语结构语法] Generative Grammar 衍生语法Generative Linguistics 衍生语言学 [生成语言学]generic 泛指genetic epistemology 发生认识论genetive marker 属格标记genitive 属格gerund 动名词Government and Binding Theory 管辖约束理论GPSG (Generalized Phrase Structure Grammar) 概化词组结构语法[广义短语结构语法]gradability 可分级性grammar checker 文法检查器grammatical affix 语法词缀grammatical category 语法范畴grammatical function 语法功能grammatical inference 文法推论grammatical relation 语法关系grapheme 字素haplology 类音删略head 中心语head driven phrase structure 中心语驱动词组结构 [中心词驱动词组结构] head feature convention 中心语特征继承原理 [中心词特性继承原理] Head-Driven Phrase Structure Grammar 中心语驱动词组结构律heteronym 同形heuristic parsing 经验式句法剖析Heuristics 经验知识hidden Markov model 隐式马可夫模型hierarchical structure 阶层结构 [层次结构]holophrase 单词句homograph 同形异义词homonym 同音异义词homophone 同音词homophony 同音异义homorganic 同部位音的Horn clause Horn 子句HPSG (Head-Driven Phrase Structure Grammar) 中心语驱动词组结构语法human-machine interface 人机界面hypernym 上位词hypertext 超文件 [超文本]hyponym 下位词hypotactic 主从结构的IC (immediate constituent) 直接成份ICG (Information-based Case Grammar) 讯息为本的格位语法idiom 成语 [熟语]idiosyncrasy 特异性illocutionary 施为性immediate constituent 直接成份imperative 祈使句implicative predicate 蕴含谓词implicature 含意indexical 标引的indirect object 间接宾语indirect speech act 间接言谈行动 [间接言语行为]Indo-European language 印欧语言inductional inference 归纳推理inference machine 推理机器infinitive 不定词 [to 不定式]infix 中缀inflection/inflexion 屈折变化inflectional affix 屈折词缀information extraction 信息撷取information processing 信息处理 [信息处理]information retrieval 信息检索Information Science 信息科学 [信息科学; 情报科学] Information Theory 信息论 [信息论]inherent feature 固有特征inherit 继承inheritance 继承inheritance hierarchy 继承阶层 [继承层次]inheritance of attribute 属性继承innateness position 语法天生假说insertion 中插inside-outside algorithm 里里外外算法instantiation 体现instrumental (case) 工具格integrated parser 集成句法剖析程序integrated theory of discourse analysis 篇章分析综合理论[言谈分析综合理论]intelligence intensive production 知识密集型生产intensifier 加强成分intensional logic 内含逻辑Intensional Semantics 内涵语意学intensional type 内含类型interjection/exclamation 感叹词inter-level 中间成分interlingua 中介语言interlingual 中介语(的)interlocutor 对话者internalise 内化International Phonetic Association (IPA) 国际语音学会internet 网际网络Interpretive Semantics 诠释性语意学intonation 语调intonation unit (IU) 语调单位IPA (International Phonetic Association) 国际语音学会IR (information retrieval) 信息检索IS-A relation IS-A 关系isomorphism 同形现象IU (intonation unit) 语调单位junction 连接keyword in context 上下文中关键词[上下文内关键词] kinesics 体势学knowledge acquisition 知识习得knowledge base 知识库knowledge based machine translation 知识为本之机器翻译knowledge extraction 知识撷取 [知识题取]knowledge representation 知识表示KWIC (keyword in context) 关键词前后文 [上下文内关键词] label 卷标labial 唇音labio-dental 唇齿音labio-velar 软颚唇音LAD (language acquisition device) 语言习得装置lag 发声延迟language acquisition 语言习得language acquisition device 语言习得装置language engineering 语言工程language generation 语言生成language intuition 语感language model 语言模型language technology 语言科技left-corner parsing 左角落剖析 [左角句法剖析]lemma 词元lenis 弱辅音letter-to-phone 字转音lexeme 词汇单位lexical ambiguity 词汇歧义lexical category 词类lexical conceptual structure 词汇概念结构lexical entry 词项lexical entry selection standard 选词标准lexical integrity 词语完整性Lexical Semantics 词汇语意学Lexical-Functional Grammar 词汇功能语法Lexicography 词典学Lexicology 词汇学lexicon 词汇库 [词典;词库]lexis 词汇层LF (logical form) 逻辑形式LFG (Lexical-Functional Grammar) 词汇功能语法liaison 连音linear bounded automaton 线性有限自主机linear precedence 线性次序lingua franca 共通语linguistic decoding 语言译码linguistic unit 语言单位linked list 串行loan 外来语local 局部的localism 方位主义localizer 方位词locus model 轨迹模型locution 惯用语logic 逻辑logic array network 逻辑数组网络logic programming 逻辑程序设计 [逻辑程序设计] logical form 逻辑形式logical operator 逻辑算子 [逻辑算符]Logic-Based Grammar 逻辑为本语法 [基于逻辑的语法] long term memory 长期记忆longest match principle 最长匹配原则 [最长一致法] LR (left-right) parsing LR 剖析machine dictionary 机器词典machine language 机器语言machine learning 机器学习machine translation 机器翻译machine-readable dictionary (MRD) 机读辞典Macrolinguistics 宏观语言学Markov chart 马可夫图Mathematical Linguistics 数理语言学maximum entropy 最大熵M-D (modifier-head) construction 偏正结构mean length of utterance (MLU) 语句平均长度measure of information 讯习测度 [信息测度] memory based 根据记忆的mental lexicon 心理词汇库mental model 心理模型mental process 心理过程 [智力过程;智力处理] metalanguage 超语言metaphor 隐喻metaphorical extension 隐喻扩展metarule 律上律 [元规则]metathesis 语音易位Microlinguistics 微观语言学middle structure 中间式结构minimal pair 最小对Minimalist Program 微言主义MLU (mean length of utterance) 语句平均长度modal 情态词modal auxiliary 情态助动词modal logic 情态逻辑modifier 修饰语Modular Logic Grammar 模块化逻辑语法modular parsing system 模块化句法剖析系统modularity 模块性(理论)module 模块monophthong 单元音monotonic 单调monotonicity 单调性Montague Grammar 蒙泰究语法 [蒙塔格语法]mood 语气morpheme 词素morphological affix 构词词缀morphological decomposition 语素分解morphological pattern 词型morphological processing 词素处理morphological rule 构词律 [词法规则] morphological segmentation 语素切分Morphology 构词学Morphophonemics 词音学 [形态音位学;语素音位学] morphophonological rule 形态音位规则Morphosyntax 词句法Motor Theory 肌动理论movement 移位MRD (machine-readable dictionary) 机读辞典MT (machine translation) 机器翻译multilingual processing system 多语讯息处理系统multilingual translation 多语翻译multimedia 多媒体multi-media communication 多媒体通讯multiple inheritance 多重继承multistate logic 多态逻辑mutation 语音转换mutual exclusion 互斥mutual information 相互讯息nativist position 语法天生假说natural language 自然语言natural language processing (NLP) 自然语言处理natural language understanding 自然语言理解negation 否定negative sentence 否定句neologism 新词语nested structure 套结构network 网络neural network 类神经网络Neurolinguistics 神经语言学neutralization 中立化n-gram n-连词n-gram modeling n-连词模型NLP (natural language processing) 自然语言处理node 节点nominalization 名物化nonce 暂用的non-finite 非限定non-finite clause 非限定式子句non-monotonic reasoning 非单调推理normal distribution 常态分布noun 名词noun phrase 名词组NP (noun phrase) completeness 名词组完全性object 宾语{语言学}/对象{信息科学}object oriented programming 对象导向程序设计 [面向对向的程序设计] official language 官方语言one-place predicate 一元述语on-line dictionary 线上查询词典 [联机词点]onomatopoeia 拟声词onset 节首音ontogeny 个体发生Ontology 本体论open set 开放集operand 操作数 [操作对象]optimization 最佳化 [最优化]overgeneralization 过度概化overgeneration 过度衍生paradigmatic relation 聚合关系paralanguage 附语言parallel construction 并列结构Parallel Corpus 平行语料库parallel distributed processing (PDP) 平行分布处理paraphrase 转述 [释意;意译;同意互训]parole 言语parser 剖析器 [句法剖析程序]parsing 剖析part of speech (POS) 词类particle 语助词PART-OF relation PART-OF 关系part-of-speech tagging 词类标注pattern recognition 型样识别P-C (predicate-complement) insertion 述补中插PDP (parallel distributed processing) 平行分布处理perception 知觉perceptron 感觉器 [感知器]perceptual strategy 感知策略performative 行为句periphrasis 用独立词表达perlocutionary 语效性的permutation 移位Petri Net Grammar Petri 网语法philology 语文学phone 语音phoneme 音素phonemic analysis 因素分析phonemic stratum 音素层Phonetics 语音学phonogram 音标Phonology 声韵学 [音位学;广义语音学]Phonotactics 音位排列理论phrasal verb 词组动词 [短语动词]phrase 词组 [短语]phrase marker 词组标记 [短语标记]pitch 音调pitch contour 调形变化Pivot Grammar 枢轴语法pivotal construction 承轴结构plausibility function 可能性函数PM (phrase marker) 词组标记 [短语标记]polysemy 多义性POS-tagging 词类标记postposition 方位词PP (preposition phrase) attachment 介词依附Pragmatics 语用学Precedence Grammar 优先级语法precision 精确度predicate 述词predicate calculus 述词计算predicate logic 述词逻辑 [谓词逻辑]predicate-argument structure 述词论元结构prefix 前缀premodification 前置修饰preposition 介词Prescriptive Linguistics 规定语言学 [规范语言学]presentative sentence 引介句presupposition 前提Principle of Compositionality 语意合成性原理privative 二元对立的probabilistic parser 概率句法剖析程序problem solving 解决问题program 程序programming language 程序设计语言 [程序设计语言]proofreading system 校对系统proper name 专有名词prosody 节律prototype 原型pseudo-cleft sentence 准分裂句Psycholinguistics 心理语言学punctuation 标点符号pushdown automata 下推自动机pushdown transducer 下推转换器qualification 后置修饰quantification 量化quantifier 范域词Quantitative Linguistics 计量语言学question answering system 问答系统queue 队列radical 字根 [词干;词根;部首;偏旁]radix of tuple 元组数基random access 随机存取rationalism 理性论rationalist (position) 理性论立场 [唯理论观点]reading laboratory 阅读实验室real time 实时real time control 实时控制 [实时控制]recursive transition network 递归转移网络reduplication 重叠词 [重复]reference 指涉referent 指称对象referential indices 指针referring expression 指涉词 [指示短语]register 缓存器 [寄存器]{信息科学}/调高{语音学}/语言的场合层级{社会语言学} regular language 正规语言 [正则语言]relational database 关系型数据库 [关系数据库]relative clause 关系子句relaxation method 松弛法relevance 相关性Restricted Logic Grammar 受限逻辑语法resumptive pronouns 复指代词retroactive inhibition 逆抑制rewriting rule 重写规则rheme 述位rhetorical structure 修辞结构rhetorics 修辞学robust 强健性robust processing 强健性处理robustness 强健性schema 基朴school grammar 教学语法scope 范域 [作用域;范围]script 脚本search mechanism 检索机制search space 检索空间searching route 检索路径 [搜索路径]second order predicate 二阶述词segmentation 分词segmentation marker 分段标志selectional restriction 选择限制semantic field 语意场semantic frame 语意架构semantic network 语意网络semantic representation 语意表征 [语义表示]semantic representation language 语意表征语言semantic restriction 语意限制semantic structure 语意结构Semantics 语意学sememe 意素Semiotics 符号学sender 发送者sensorimotor stage 感觉运动期sensory information 感官讯息 [感觉信息]sentence 句子sentence generator 句子产生器 [句子生成程序]sentence pattern 句型separation of homonyms 同音词区分sequence 序列serial order learning 顺序学习serial verb construction 连动结构set oriented semantic network 集合导向型语意网络 [面向集合型语意网络] SGML (Standard Generalized Markup Language) 结构化通用标记语言shift-reduce parsing 替换简化式剖析short term memory 短程记忆sign 信号signal processing technology 信号处理技术simple word 单纯词situation 情境Situation Semantics 情境语意学situational type 情境类型social context 社会环境sociolinguistics 社会语言学software engineering 软件工程 [软件工程]sort 排序speaker-independent speech recognition 非特定语者语音识别spectrum 频谱speech 口语speech act assignment 言语行为指定speech continuum 言语连续体speech disorder 语言失序 [言语缺失]speech recognition 语音辨识speech retrieval 语音检索speech situation 言谈情境 [言语情境]speech synthesis 语音合成speech translation system 语音翻译系统speech understanding system 语音理解系统spreading activation model 扩散激发模型standard deviation 标准差Standard Generalized Markup Language 标准通用标示语言start-bound complement 接头词state of affairs algebra 事态代数state transition diagram 状态转移图statement kernel 句核static attribute list 静态属性表statistical analysis 统计分析Statistical Linguistics 统计语言学statistical significance 统计意义stem 词干stimulus-response theory 刺激反应理论stochastic approach to parsing 概率式句法剖析 [句法剖析的随机方法] stop 爆破音Stratificational Grammar 阶层语法 [层级语法]string 字符串[串;字符串]string manipulation language 字符串操作语言string matching 字符串匹配 [字符串]structural ambiguity 结构歧义Structural Linguistics 结构语言学structural relation 结构关系structural transfer 结构转换structuralism 结构主义structure 结构structure sharing representation 结构共享表征subcategorization 次类划分 [下位范畴化]subjunctive 假设的sublanguage 子语言subordinate 从属关系subordinate clause 从属子句 [从句;子句]subordination 从属substitution rule 代换规则 [置换规则]substrate 底层语言suffix 后缀superordinate 上位的superstratum 上层语言suppletion 异型[不规则词型变化] suprasegmental 超音段的syllabification 音节划分syllable 音节syllable structure constraint 音节结构限制symbolization and verbalization 符号化与字句化synchronic 同步的synonym 同义词syntactic category 句法类别syntactic constituent 句法成分syntactic rule 语法规律 [句法规则]Syntactic Semantics 句法语意学syntagm 句段syntagmatic 组合关系 [结构段的;组合的]Syntax 句法Systemic Grammar 系统语法tag 标记target language 目标语言 [目标语言]task sharing 课题分享 [任务共享]tautology 套套逻辑 [恒真式;重言式;同义反复] taxonomical hierarchy 分类阶层 [分类层次] telescopic compound 套装合并template 模板temporal inference 循序推理 [时序推理] temporal logic 时间逻辑 [时序逻辑]temporal marker 时貌标记tense 时态terminology 术语text 文本text analyzing 文本分析text coherence 文本一致性text generation 文本生成 [篇章生成]Text Linguistics 文本语言学text planning 文本规划text proofreading 文本校对text retrieval 文本检索text structure 文本结构 [篇章结构]text summarization 文本自动摘要 [篇章摘要]text understanding 文本理解text-to-speech 文本转语音thematic role 题旨角色thematic structure 题旨结构theorem 定理thesaurus 同义词辞典theta role 题旨角色theta-grid 题旨网格token 实类 [标记项]tone 音调tone language 音调语言tone sandhi 连调变换top-down 由上而下 [自顶向下]topic 主题topicalization 主题化 [话题化]trace 痕迹Trace Theory 痕迹理论training 训练transaction 异动 [处理单位]transcription 转写 [抄写;速记翻译]transducer 转换器transfer 转移transfer approach 转换方法transfer framework 转换框架transformation 变形 [转换]Transformational Grammar 变形语法 [转换语法]transitional state term set 转移状态项集合transitivity 及物性translation 翻译translation equivalence 翻译等值性translation memory 翻译记忆transparency 透明性tree 树状结构 [树]Tree Adjoining Grammar 树形加接语法 [树连接语法]treebank 树图数据库[语法关系树库]trigram 三连词t-score t-数turing machine 杜林机 [图灵机]turing test 杜林测试 [图灵试验]type 类型type/token node 标记类型/实类节点type-feature structure 类型特征结构typology 类型学ultimate constituent 终端成分unbounded dependency 无界限依存underlying form 基底型式underlying structure 基底结构unification 连并 [合一]Unification-based Grammar 连并为本的语法 [基于合一的语法] Universal Grammar 普遍性语法universal instantiation 普遍例式universal quantifier 全称范域词unknown word 未知词 [未定义词]unrestricted grammar 非限制型语法usage flag 使用旗标user interface 使用者界面 [用户界面]Valence Grammar 结合价语法Valence Theory 结合价理论valency 结合价variance 变异数 [方差]verb 动词verb phrase 动词组 [动词短语]verb resultative compound 动补复合词verbal association 词语联想verbal phrase 动词组verbal production 言语生成vernacular 本地话V-O construction (verb-object) 动宾结构vocabulary 字汇vocabulary entry 词条vocal track 声道vocative 呼格voice recognition 声音辨识 [语音识别]vowel 元音vowel harmony 元音和谐 [元音和谐]waveform 波形weak verb 弱化动词Whorfian hypothesis Whorfian 假说word 词word frequency 词频word frequency distribution 词频分布word order 词序word segmentation 分词word segmentation standard for Chinese 中文分词规范word segmentation unit 分词单位 [切词单位]word set 词集working memory 工作记忆 [工作存储区]world knowledge 世界知识writing system 书写系统X-Bar Theory X标杠理论 ["x"阶理论]Zipf's Law 利夫规律 [齐普夫定律]阅读。

智能融合2软件FAQs July 2014说明书

SmartFusion2 SoftwareFAQsJuly 2014Table of Contents2SmartFusion2 Software FAQs1.Where can I find information about the DSP flow? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42.Can I use the SmartFusion2 drivers provided by Microsemi together with my own application codeeventually in production? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43.Why is Cortex-M3 processor not running at 166 MHz in my design as published? . . . . . . . . . . 44.What is the speed of a mathblock? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45.Does the MATLAB/Simulink front-end tool have a blockset that uses mathblocks? . . . . . . . . . 46.Can the internal 25 MHz/ 50 MHz SmartFusion2 oscillator be used as the clock source for PCIe?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47.Can the internal 25 MHz/50 MHz SmartFusion2 oscillator be used as the clock source for USB?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48.What is maximum payload size for PCIe? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49.How should the JTAGSEL pin of the SmartFusion2 device be connected? . . . . . . . . . . . . . . . 410.What is the purpose of CoreConfigP core? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 511.For which memories can SECDED protection be enabled? . . . . . . . . . . . . . . . . . . . . . . . . . . . 512.What is the state of SmartFusion2 I/Os during JTAG programming? . . . . . . . . . . . . . . . . . . . . 513.Where can I get the SmartFusion2 peripheral firmware drivers? . . . . . . . . . . . . . . . . . . . . . . . . 714.What is the purpose of POWER_ON_RESET_N signal and what scenarios will assert this? . . 715.What does a mirrored master or mirrored slave port mean? . . . . . . . . . . . . . . . . . . . . . . . . . . . 816.Why is SPLL used for in PCIe? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 817.What is the source for the SPLL clock in SERDES? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 818.Which clock is used for the AHB buses in PCIe? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 819.Can fabric clock be used as reference clock in EPCS mode (In SERDES IP)? . . . . . . . . . . . . 820.Is the "Repair minimum delay violation" option for the router supported for SmartFusion2 device?. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 821.Is it possible to get SmartFusion2 symbol and footprint files for Altium? . . . . . . . . . . . . . . . . . . 822.Does the SERDES simulation model have a feature to reduce simulation run times? . . . . . . . 823.Can the SERDES IP simulation model be used for simulating a PCIe system? . . . . . . . . . . . . 824.Is simulation of serial behavior of SERDES IP supported? . . . . . . . . . . . . . . . . . . . . . . . . . . . . 825.How are SmartFusion2 hardware blocks initialized? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 826.How does cache controller improve the execution time? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 827.What is Zeroization and is it supported by SmartFusion2 device? . . . . . . . . . . . . . . . . . . . . . . 828.How to use MSS clock conditioning circuit (CCC)? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 929.Does Microsemi have plans to support lower core voltage parts? . . . . . . . . . . . . . . . . . . . . . . . 930.Can SmartFusion2 support USB OTG and what type of USB is supported? . . . . . . . . . . . . . . 931.How should unused SERDES pins/power supplies on SmartFusion2 device be connected on theboard? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 932.Do blank devices have ramp rate? What is the default ramp rate? . . . . . . . . . . . . . . . . . . . . . . 933.What is the percentage deviation from power calculator values with the actual silicon results? 934.What is the default toggling rate used by power calculator to calculate the power? . . . . . . . . . 935.How to configure PCIe address parameter of SERDES configurator? . . . . . . . . . . . . . . . . . . 1036.Are IBIS models different for SmartFusion2 and IGLOO2? . . . . . . . . . . . . . . . . . . . . . . . . . . . 1037.How to set seed value for SmartFusion2/IGLOO2 place and route? . . . . . . . . . . . . . . . . . . . . 1138.What does the below RGB error message mean, which is observed during place and route? 1139.Are basic blocks available for SmartFusion2 and IGLOO2? . . . . . . . . . . . . . . . . . . . . . . . . . . 11SmartFusion2 Software FAQs340.How to enable system timers or MSS timers? . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114SmartFusion2 Software FAQs1.Where can I find information about the DSP flow?DSP Quickstart and Design Tutorial document demonstrates the essential flow for directly generating RTL files from the design/higher-level algorithm created in the MathWorks' MATLAB ®/ Simulink ® software.Refer to the DSP Flow For SmartFusion2 SoC FPGA Quickstart and Design Tutorial for more information.To use the DSP flow, you should have the MathWorks MATLAB /Simulink software and license already installed. In addition, you need to install the Synopsys ® Synphony Model Compiler AE. The Synphony Model Compiler AE can only be launched from the MATLAB/Simulink tools.For more information about Synphony Model Compiler AE and the recommended, supported, and compatible MathWorks' tools versions, refer to the Design Software page.2.Can I use the SmartFusion2 drivers provided by Microsemi together with my own application code eventually in production?Yes, you can use SmartFusion2 devices firmware drivers, such as USB and MAC along with your application code for production purpose.3.Why is Cortex-M3 processor not running at 166 MHz in my design as published?When any peripheral is connected to Cortex-M3 processor, the frequency decreases. It might not run at the maximum speed of 166 MHz. The frequency depends on interconnected peripherals.4.What is the speed of a mathblock?A mathblock runs up to 350MHz depending on the application.Refer to Implementation of 9x9 Multiplications, Wide-Multiplier, and Extended Addition Using IGLOO2/SmartFusion2 Mathblock application note for further details.Note:This is applicable only for SmartFusion2/IGLOO2 devices.5.Does the MATLAB/Simulink front-end tool have a blockset that uses mathblocks?A mathblock is available in an IP catalog. Apart from this, you can use mathblocks by using Synphony Model Compiler integrated with the Matlab tool.Refer to the DSP Flow For SmartFusion2 SoC FPGA Quickstart and Design Tutorial for more information.For more information on how to integrate and download Symphony model compiler, refer to the Design Software page.6.Can the internal 25 MHz/ 50 MHz SmartFusion2 oscillator be used as the clock source for PCIe?Yes, refer to SmartFusion2 SoC FPGA Clocking Resources User Guide for more information.7.Can the internal 25 MHz/50 MHz SmartFusion2 oscillator be used as the clock source for USB?Yes, refer to SmartFusion2 SoC FPGA Clocking Resources User Guide for more information.8.What is maximum payload size for PCIe?The maximum payload size for PCIe is 512 bytes.9.How should the JTAGSEL pin of the SmartFusion2 device be connected?JTAGSEL pin of SmartFusion2 device should be pulled high for use with SoftConsole and should be pulled low for use with IAR and Keil products.SmartFusion2 Software FAQs510.What is the purpose of CoreConfigP core?CoreConfigP facilitates the configuration of peripheral blocks (MDDR, FDDR, and SERDESIF) in a SmartFusion2 device.It has a mirrored master APB port and several mirrored slave APB ports. The mirrored master port should be connected to the FIC_2_APB_MASTER master port of the microcontroller subsystem (MSS).For example,The MDDR controller must be configured to match the external DDR memory specifications. The configuration of the MDDR is defined in a file and is imported using the MDDR GUI configurator. The configuration is done through the CoreConfigP soft IP core which is the master of theconfiguration data initialization process. Upon reset, the soft IP core CoreConfigP will copy the data from embedded nonvolatile memory (eNVM) to the configuration registers of the MDDR controller through the FIC_2 advanced peripheral bus (APB) Interface.11.For which memories can SECDED protection be enabled?The single error correct double error detect (SECDED) protection is available for following memories:•Ethernet buffers •CAN message buffers •Cortex-M3 embedded scratch pad memory (eSRAMs)•USB buffers •PCIe buffer •DDR memory controllersRefer to the SmartFusion2 SoC FPGA Reliability and Security User Guide for more information on SECDED.12.What is the state of SmartFusion2 I/Os during JTAG programming?While programming in JTAG mode, the Cortex-M3 processor is in reset. All I/Os (MSIO, MSIOD, and DDRIO) are controlled by boundary scan registers according to IEEE1149.1 and IEEE1532 standards. I/O state can also be configured before programming, in Libero SoC software using the "Specify I/O states during programming window" as shown in Figure 1 on page 6.6SmartFusion2 Software FAQsRefer to the Libero SoC v11.0 User Guide for more information.Figure 1:Specify I/O States During Programming WindowSmartFusion2 Software FAQs713.Where can I get the SmartFusion2 peripheral firmware drivers?The firmware drivers are accessible from the SoftConsole firmware catalog. See Figure 2.14.What is the purpose of POWER_ON_RESET_N signal and what scenarios will assert this?It is a power-on reset from system controller to the FPGA fabric. The system controller initiates reset due to power-on reset, assertion of DEVRST_N input, completion of programming, or completion of Zeroization. POWER_ON_RESET_N signal can be used in the user design as a system power-on-reset for the FPGA fabric. It is an active Low-output signal.The POWER_ON_RESET_N signal is available by instantiating the SYSRESET macro (see Figure 3), from the Libero SoC IP catalog into SmartDesign or by instantiating it directly inside HDL file. Figure 2:Firmware Catalog Figure 3:SYSRESET Macro8SmartFusion2 Software FAQs15.What does a mirrored master or mirrored slave port mean?The mirrored interfaces are complementary interfaces located in the CoreAHB/APB that allow AHB/APB bus masters to connect to AHB/APB slaves through the CoreAHB/APB. The AHB/APB master port gets connected to the mirrored master port on the CoreAHB/APB, and the slave ports get connected to the mirrored slave ports on the CoreAHB/APB. In short, the mirrored ports are same ports as the normal interfaces but the directions of these ports are reversed.16.Why is SPLL used for in PCIe?The SPLL is used to re-time the bridge interface between the fabric and the hardened blocks of the SERDESIF.17.What is the source for the SPLL clock in SERDES?CLK_BASE is the input reference clock (source) of the SPLL.18.Which clock is used for the AHB buses in PCIe?The SPLL output is used as the AXI/AHB bridge clock.19.Can fabric clock be used as reference clock in EPCS mode (In SERDES IP)? Yes, fabric clock can be used as reference clock in the EPCS mode.20.Is the "Repair minimum delay violation" option for the router supported for SmartFusion2 device?This option is currently not supported for the SmartFusion2 device.21.Is it possible to get SmartFusion2 symbol and footprint files for Altium?Altium tool foot print and symbols are currently not available for Smartfusion2 device.22.Does the SERDES simulation model have a feature to reduce simulation run times?Presently, there is no option to bypass the clock and data recovery logic to reduce the simulation run time.23.Can the SERDES IP simulation model be used for simulating a PCIe system? Yes. BFM model can be used where SERDES acts as AXI/AHB bus master and slave. However, serial protocol is not implemented in this case.24.Is simulation of serial behavior of SERDES IP supported?Yes, it is supported. For all SERDES modes, full RTL model is used to simulate the SERDES serial behavior.25.How are SmartFusion2 hardware blocks initialized?SmartFusion2 hardware blocks are initialized through a combination of flash bits and Libero generated logic (CoreConfigP).26.How does cache controller improve the execution time?For details on improving the execution time using Cache Controller, refer to the SmartFusion2 SoC FPGA - Cache Controller Configuration application note.27.What is Zeroization and is it supported by SmartFusion2 device?Zeroization is a system service that destroys the sensitive data in the device and then verifies that the data is gone before allowing any further operations to take place. Yes, SmartFusion2 SoC FPGAs support Zeroization.SmartFusion2 Software FAQs928.How to use MSS clock conditioning circuit (CCC)?Run the following steps:•Instantiate the SmartFusion2 MSS component into your Libero SoC project.•Configure (enable/disable) the MSS components appropriately for the application needs using MSS configurator.•Configure the MSS CCC input and output clock frequencies using the MSS_CCC configurator.•Set the MPLL analog supply voltage to 2.5 V or 3.3 V to match the supply on the board.29.Does Microsemi have plans to support lower core voltage parts?Currently, SmartFusion2 works on 1.2 V core voltage. We are planning for 1.0 V core voltage support in future.30.Can SmartFusion2 support USB OTG and what type of USB is supported?Yes, SmartFusion2 device supports USB OTG. The following USB flash drives are currently supported:•Sandisk Cruzer BladeTM - 16 GB/8 GB/4 GB/1 GB •Kingston DataTraveler ® - 4 GB/2 GB •Kingston ® DataTraveler ®109 - 8 GB •Transcend JetFlash ® - 4 GB31.How should unused SERDES pins/power supplies on SmartFusion2 device be connected on the board?Refer to the Knowledge Base Article to know about handling unused SERDES pins.32.Do blank devices have ramp rate? What is the default ramp rate?No, the blank devices do not have default ramp rate values.Note:The 50 us, 1 ms, 10 ms, and 100 ms ramp rates are not applicable for blank devices, and they are valid only forthe programmed devices.33.What is the percentage deviation from power calculator values with the actual silicon results?The deviation percentage from power calculator with the actual silicon results is less than 10%.34.What is the default toggling rate used by power calculator to calculate the power?The power calculator engine uses inputs at 12.5% toggle rate and provides the power estimation.10SmartFusion2 Software FAQs 35.How to configure PCIe address parameter of SERDES configurator?PCIe address is mapped to bits [31:12] (LSB of Base address AXI Master WindowsX_2) and bits [31:0] (MSB of Base address AXI Master WindowsX_3).The zeros in these fields indicate the offset. For example, If the PCIe address value is set to be 0x1000 in the GUI, then the BAR0 address + 0x1000_000 is mapped to 0x0 of AXI window.36.Are IBIS models different for SmartFusion2 and IGLOO2?IBIS models are identical for SmartFusion2 and IGLOO2 given package.Figure 4: PCIe ConfiguratorTable 1: AXI_MASTER_WINDOW Registers Bit Numbers Name Description[31:12]AXI_MASTER_WINDOWx[0]Base address AXI3 master window x [11:0]Reserved [31:12]AXI_MASTER_WINDOWx[1]Size of AXI3 master window x [11:1]Reserved 0Enable bit of AXI3master window x [31:12]AXI_MASTER_WINDOWx[2]LSB of base address PCIe window x [11:6]Reserved [5:0]Theses bits set the BAR. To select a BAR, set thefollowing values:0*01: BAR0 (32-bit BAR) or BAR0/1 (64-bit BAR)0*02: BAR1 (32-bit BAR) only0*04: BAR2 (32-bit BAR) or BAR2/3 (64-bit BAR)0*08: BAR3 (32-bit BAR) only0*10: BAR4 (32-bit BAR) or BAR4/5 (64-bit BAR)0*20: BAR5 (32-bit BAR) only[31:0]AXI_MASTER_WINDOWx[3]MSB of base address PCIe window xSmartFusion2 Software FAQs1137.How to set seed value for SmartFusion2/IGLOO2 place and route?For example, set a seed value of 6 for place and route.The 'extended_run_lib' Tcl script enables you to set the starting seed value in batch mode from a command line prompt.To set a seed value of 6,<prompt>C:/Microsemi/Libero_v11.3/Designer/bin/libero.exe script:C:/Microsemi/Libero_v11.3/Designer/scripts/extended_run_lib.tcl logfile:extended_run.log "script_args:-root F:/SF2_seed/seed_check/designer/top -n 3 -starting_seed_index 6 -slack_criteria tns -stop_on_success"Refer to the Libero Tcl Commands Reference Guide for more information.Here,•C:/Microsemi/Libero_v11.3/Designer/bin/libero.exe = Libero installation directory •C:/Microsemi/Libero_v11.3/Designer/scripts/extended_run_lib.tcl = Scripts file location in the Libero installation directory •F:/SF2_seed/seed_check/designer/top = Root module location under designer directory in Libero project38.What does the below RGB error message mean, which is observed during place and route?Error: RGB: Cannot place all RGB’s in row 60.RGB stands for row global buffer.The error message indicates that the particular row of FPGA runs out of global resources. Change or edit the placement constraints provided in the PDC file. Refer to the SmartFusion2 Clocking Resources User Guide for more information.39.Are basic blocks available for SmartFusion2 and IGLOO2?Basic blocks are not available for SmartFusion2 and IGLOO2.40.How to enable system timers or MSS timers?System timers or MSS timers are enabled by default, refer to Chapter 18 in MSS User Guide for more information.55800028-1/7.14© 2014 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporate HeadquartersOne Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail:***************************Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense and security, aerospace, and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs, and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif. and has approximately 3,400 employees globally. Learn more at .。

psp硬件规格说明书开发级

TyRaNiD

August 4, 2006

TyRaNiD ()

The Naked PSP

August 4, 2006

1 / 61

What This Presentation Covers

What I am going to talk about: Coding on the PSP using C PSP Internals Development tools What I am not going to talk about: Games Piracy Modchips

TyRaNiD ()

The Naked PSP

August 4, 2006

7 / 61

History of PSP Home brew

Revisions of the PSP

Running Your Own Code

How you run code depends on the firmware revision of the PSP For versions 1.0 and 1.5 build a special EBOOT.PBP file and run directly on the PSP For version 2.0 use eLoader in libTIFF mode For version 2.01+ use Grand Theft Auto UMD plus eLoader For version 2.7+ no known way of developing

TyRaNiD ()

The Naked PSP

August 4, 2006

8 / 61

Alleviation [FWW91]. analyses [TRM91].

![Alleviation [FWW91]. analyses [TRM91].](https://img.taocdn.com/s3/m/c0a45e4ef7ec4afe04a1df66.png)

A Bibliography of Supercomputing’91Nelson H.F.BeebeCenter for Scientific ComputingUniversity of UtahDepartment of Mathematics,322INSCC155S1400E RM233Salt Lake City,UT84112-0090USATel:+18015815254FAX:+18015814148E-mail:beebe@(Internet) WWW URL:/~beebe/25October1998Version1.02AbstractThis bibliography records articles presented at the Supercomputing’91conference.Title word cross-reference 15[MS91].1990[STVS91].2600[SWL+91].3[SWL+91].4[KSY91].’91[IEE91].access[BC91,BS91].accesses[GV91]. across[MMF+91,NGHG+91].adaptive[FGPS91].Albuquerque[IEE91]. algebra[KS91].algorithm[Pug91,TG91,YG91,de91]. algorithms[FGPS91,Nar91].alias[Chi91]. Alleviation[FWW91].analyses[TRM91]. Analysis[Nar91,CV91,Pug91,WL91]. animation[UHP91].aperture[PMG91]. Application[RJCC91].applications[DKMS91,MK91].applied[Chr91].approach[KS91]. approaches[TMB91].Architecture[HQA+91,AFH+91,BP91a, Kar91,KSS+91,Tze91].Architecture-independent[HQA+91]. architectures[BL91,Nar91,TRM91]. array[BL91,GV91,Nar91].arrays[QM91]. arrhythmias[Sad91].auditorialization[HW91].automatic[CP91,KS91].12balance[VN91].balancing[AGM91,KSY91].bank[BU91]. based[BDG+91,Kar91,KSS+91].behavior[FLK+91,MK91].Bell[DKMS91,STVS91].benchmarks[BBB+91,BF91]. benchmarks-summary[BBB+91].block[Chr91,KS91].Boltzmann[Elt91]. bounded[Aln91].bounded-degree[Aln91].Burgers[Elt91]. C[HQA+91,Smi91].cardiac[Sad91].case[HQA+91].CG[Chr91].challenge[CFK+91].Chaotic[Sad91]. Characterizing[GPCJ91].checkpoint[BP91b].chip[BC91].class[Chr91].Climate[Che91,MMF+91]. code[EOS91,HKM91].coherence[CV91]. communicating[IAS+91]. communication[VN91].communications[Koe91,QM91]. community[MW91].Comparison[CV91,NGHG+91,SWL+91]. Compiler[HKT91,Koe91,STVS91,AFH+91].Compiler-time[Koe91]. compilers[Smi91].complex[SBGM91]. computation[Kar91].computational[Elt91].computations[KS91].computer[TRM91]. computers[JH91,RJCC91].Computing[Dan91,SBGM91,IAS+91,TV91,Wil91].concurrent[BDG+91,KWFN91]. conditioned[PF91].conflict[SN91].conflict-free[SN91].connected[Tze91]. Connection[MS91,SDM91].conquer[GK91].consistency[DWB+91]. constant[Aln91].contention[BU91]. contentions[BS91].costs[PBH91].course[TV91].Cray[SWL+91].cube[Tze91].cube-connected[Tze91]. cycles[Tze91].DAGs[YG91].data[BC91,GV91,Kan91,MC91,Nar91]. dataparallel[HQA+91].debate[Can91]. debugging[GH91].decoupled[BU91]. degree[Aln91].Delayed[DWB+91]. dense[Mal91].dependence[Pug91]. Design[Tze91,WL91,CM91,SN91]. Detecting[GV91].detection[MC91]. development[BDG+91].differential[HIS91].dimensional[Elt91,TRM91].directed[BP91a].directory[CV91]. distributed[AGM91,AFH+91,HKT91, IAS+91,Mal91,SY91].distributed-memory[HKT91]. Distributing[NGHG+91].Distribution[MMF+91,KSY91].divide[GK91].divide-and-conquer[GK91].division[QM91,de91].DNA[NGHG+91]. DOACROSS[CY91,SY91].dynamic[Chi91].dynamics[TMB91].effective[BC91].Effects[VN91,DWB+91]. Efficient[SY91,Chr91,TG91,WL91]. element[BL91,TRM91].elliptic[STVS91]. EM-4[KSY91].emerging[KSS+91]. empirical[CY91,LMSS91].environment[Dan91].equation[Elt91,HIS91].Euclidean[de91]. evaluation[CP91].examination[TG91]. execution[SY91].experiments[LG91]. explicit[PBH91].Exploration[Wil91]. Factoring[HSF91].factorization[Mal91,VN91].fast[Pug91,YG91,de91].FFTs[lWR91].finite[Kar91,TRM91].finite-element[TRM91].floating[MMNP91].floating-point[MMNP91].flow[EOS91,SBGM91].fluid[HIS91].fly[MC91].fork[MC91].fork-join[MC91]. format[MMNP91].FORTRAN[Can91,UHP91].3FortranD[HKT91].framework[CM91]. free[SN91].Fujitsu[SWL+91].Fully[FGPS91].Fully-adaptive[FGPS91]. function[KSY91].functions[HIS91]. generation[BL91,HKM91,Koe91]. generator[STVS91].geometries[Kar91,SBGM91].geophysics[Wil91].Gigaflops[MS91]. Gigascale[Mei91].good[Smi91].Gordon[STVS91,DKMS91].GPFP[BL91].Graphical[BDG+91,UHP91].grid[STVS91].GSI[Mei91]. heterogeneous[NGHG+91].hierarchical[WL91].High[GK91,YZ91, CFK+91,CM91,MMF+91].high-performance[CM91].high-speed[MMF+91].highly[Tze91].hot[GPCJ91].hypercubes[lWR91].ill[PF91].ill-conditioned[PF91].image[PMG91].implementation[Chr91,EOS91]. implications[TRM91].independent[HQA+91].information[HW91].Input[MK91].Input/output[MK91].integer[Pug91]. integrated[Chi91].integration[Mei91]. intelligence[MW91].Intelligent[IAS+91]. interactive[CP91].interconnection[FWW91,WL91]. Interprocedural[HKM91].issues[RJCC91].iteration[RS91]. iterative[PF91].join[MC91].K2[AFH+91].language[HIS91].Large[KWFN91,PBH91,RJCC91].lattice[Elt91].lectures[DKMS91].level[GK91].libraries[MMNP91].linear[Chr91,FJ91,KS91,PF91].Load[KSY91,AGM91,VN91].localization[PBH91].lookahead[BU91]. loops[CY91,HSF91].LU[Mal91]. machine[GPCJ91,MS91,SDM91]. machines[HKT91,RS91].management[Chi91].mapping[IAS+91]. Mass[MW91].Massively[TV91,BL91, FLK+91,RJCC91,SBGM91].math[MMNP91].matrix[Kar91,VN91]. Measurement[BS91].mechanism[BP91b].media[EOS91]. memory[AFH+91,BU91,BP91b,BS91, Chi91,GPCJ91,GH91,HKT91,Mal91, PBH91,RS91,SN91,SY91,de91].method[Chr91,Elt91,HSF91,Kan91]. Mexico[IEE91].mid[TV91].mid-course[TV91].milieu[KWFN91]. MIMD[Dan91,GPCJ91,HKT91].miss[DWB+91].model[MMF+91]. modeling[Che91,Dan91,MS91,SDM91]. molecular[TMB91].MOVE[CM91].MP[SWL+91].MTOOL[GH91]. multicomputer[AGM91]. multicomputers[KSS+91]. multidimensional[RS91].multiple[BS91].multiplexed[JH91]. multiprocessor[GH91,Mal91,PBH91, QM91].multiprocessors[SN91,SY91,ZB91]. multistage[FWW91,FJ91].NAS[BBB+91,BF91].NEC[SWL+91]. nested[MC91].Network[KSS+91,BDG+91].Network-based[KSS+91,BDG+91]. networks[Aln91,FWW91,FJ91,MMF+91, WL91].next[BL91].non[CWW91].non-uniform[CWW91].nonshared[RS91].November[IEE91]. number[Aln91,YG91].4Object[LG91].Ocean[SDM91].Omega[Pug91].on-chip[BC91].On-the-fly[MC91].operand[BU91]. operating[AFH+91].optical[JH91,QM91].Optimal[Aln91]. optimizations[HKT91].oriented[LG91]. output[MK91].package[PF91].packet[FGPS91].pairs[TG91].Parallel[TMB91,lWR91, AFH+91,BBB+91,BF91,BL91,CWW91, CP91,Che91,Chr91,DWB+91,EOS91,FLK+91,HKM91,HSF91,Kar91,KSS+91, LG91,PMG91,RJCC91,SBGM91,TG91, TV91,UHP91,Wil91].parallelism[CWW91,GK91,MC91]. parallelization[KS91,STVS91].partial[HIS91].partitioning[BP91a,VN91].patterns[Koe91].PDEQSOL[HIS91]. penalty[BC91].Performance[AGM91,BF91,GH91,CM91, FGPS91,SWL+91,YZ91].permutations[FJ91].PILS[PF91]. pivoting[Mal91].point[MMNP91]. Pointer[LMSS91].porous[EOS91].power[lWR91].power-of-two[lWR91]. practical[HSF91,Pug91].prediction[AGM91].preliminary[BBB+91].preloading[BC91].prime[de91].Prize[DKMS91,STVS91].problem[TV91].problems[HIS91]. Proceedings[IEE91].processes[IAS+91]. processing[BL91,Kan91,KWFN91,PMG91,YZ91].processor[AFH+91,BP91a,BS91,CM91,Nar91,SBGM91]. processors[YG91].profiles[CWW91]. Programming[PBH91,CP91,HQA+91, LG91,Pug91].programs[CWW91,DWB+91,FLK+91,GH91,MC91,UHP91]. projective[Kar91].protein[NGHG+91]. prototype[KSY91].races[MC91].radar[PMG91].Radix[ZB91].range[TMB91].rate[DWB+91].reality[Wil91].recovery[BP91b].reduce[BC91,BU91]. redundant[GV91].references[BU91]. regular[Koe91].rekindled[Can91]. reliable[Tze91].replicated[Nar91]. requirements[MW91].reservoir[KWFN91,RJCC91,YZ91]. resolution[Chi91].results[BBB+91,BF91,Elt91,LG91]. Retire[Can91].robust[HSF91].rollback[BP91b].rounds[Aln91].routing[FGPS91].saturation[FWW91].scale[KWFN91,PBH91,RJCC91]. Scheduling[CWW91,HSF91,VN91,YG91]. scheme[BC91,Chi91].schemes[CV91]. school[CFK+91].scientific[HQA+91,HW91].Seismic[MS91].semantics[BP91a]. semantics-directed[BP91a].sequences[NGHG+91].shared[GPCJ91, GH91,Kan91,PBH91,SY91].shared-memory[SY91].short[TMB91]. simulation[KWFN91,RJCC91,YZ91]. simulations[TMB91].software[CV91]. Solution[HIS91].solver[HIS91,PF91]. sort[ZB91].sorting[Aln91].spaces[RS91].sparse[Kar91,VN91]. speed[MMF+91].spots[GPCJ91].static[YG91].storage[MW91].studies[HQA+91].study[CY91,LMSS91]. summary[BBB+91].supercomputer[BL91,DKMS91]. supercomputers[Che91,NGHG+91,PMG91,SWL+91].Supercomputing[IEE91,BDG+91,CFK+91,MK91].support[BP91b,GK91]. switching[FGPS91].SX[SWL+91].SX-3[SWL+91].symbolic[Kan91]. Synthetic[PMG91].system[AFH+91]. systems[AGM91,BS91,Chr91,IAS+91,REFERENCES5PF91,de91].target[LMSS91].technology[Mei91].test[Pug91].Three[TRM91,HQA+91,SWL+91].Three-dimensional[TRM91].Threshold[Mal91].Tiling[RS91].Time[JH91,QM91,Koe91].Time-division[QM91].tools[BDG+91,CP91].tracking[LMSS91,TV91].tracking-an[LMSS91].transformations[HKM91].translation[BP91b].tree[FWW91]. tridiagonal[Chr91].turbulent[SBGM91]. two[BF91,Elt91,lWR91].two-dimensional[Elt91].ultra[de91].unbounded[YG91].uniform[CWW91].Universal[FJ91]. Using[BU91].Vector[EOS91,BS91,Che91,Kan91,YZ91, ZB91].Vector/parallel[EOS91]. Vectorizing[Smi91].via[FJ91].virtual[BP91b].viscous[Elt91]. Visualizing[FLK+91].VLSI[Aln91].VP[SWL+91].VP-2600[SWL+91].Wide[MMNP91].wormhole[FGPS91].Y-MP[SWL+91].ReferencesAnnaratone:1991:KDM [AFH+91]M.Annaratone,M.Fillo,M.Halbherr,R.Ruhl,Steiner,P.,and M.Viredaz.The K2distributed memory parallel pro-cessor:architecture,compilerand operating system.In IEEE[IEE91],pages900–909.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Ahmad:1991:PPD [AGM91]I.Ahmad, A.Ghafor,andK.Mehrotra.Performance pre-diction of distributed load bal-ancing on multicomputer sys-tems.In IEEE[IEE91],pages830–839.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Alnuweiri:1991:OBV [Aln91]H.M.Alnuweiri.Optimalbounded-degree VLSI networksfor sorting in a constant num-ber of rounds.In IEEE[IEE91],pages732–739.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Bailey:1991:NPB [BBB+91] D.H.Bailey,E.Barszcz,J.T.REFERENCES6Barton, D.S.Browning,R.L.Carter,L.Dagum,R. A.Fa-toohi,P.O.Frederickson,T.A.Lasinski,R.S.Schreiber,H.D.Simon,V.Venkatakrishnan,andS.K.Weeratunga.The NAS par-allel benchmarks-summary andpreliminary results.In IEEE[IEE91],pages158–165.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Baer:1991:EOP [BC91]J.-L.Baer and T.-F.Chen.An effective on-chip preloadingscheme to reduce data accesspenalty.In IEEE[IEE91],pages176–186.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Beguelin:1991:GDT [BDG+91] A.Beguelin,J.J.Dongarra,G.A.Geist,R.Manchek,andV.S.Sunderam.Graphicaldevelopment tools for network-based concurrent supercomput-ing.In IEEE[IEE91],pages435–444.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Bailey:1991:PRT [BF91] D.H.Bailey and P.O.Freder-ickson.Performance results fortwo of the NAS parallel bench-marks.In IEEE[IEE91],pages166–173.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Beal:1991:GAP [BL91] D.Beal and mbrinoudakis.GPFP:an array processing el-ement for the next generationof massively parallel supercom-puter architectures.In IEEE[IEE91],pages348–357.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Bird:1991:SPP [BP91a]P.L.Bird and U. F.Ple-ban.A semantics-directed par-titioning of a processor architec-ture.In IEEE[IEE91],pagesREFERENCES7702–709.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Bowen:1991:VMT [BP91b]N.S.Bowen and D.K.Prad-han.A virtual memory trans-lation mechanism to supportcheckpoint and rollback recov-ery.In IEEE[IEE91],pages890–899.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Bucher:1991:MMA [BS91]I.Y.Bucher and M.L.Simmons.Measurement of memory accesscontentions in multiple vectorprocessor systems.In IEEE[IEE91],pages806–817.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Bird:1991:ULR [BU91]P.L.Bird and -ing lookahead to reduce mem-ory bank contention for decou-pled operand references.In IEEE[IEE91],pages187–196.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Cann:1991:RFD [Can91] D.Cann.Retire FORTRAN?A debate rekindled.In IEEE[IEE91],pages264–272.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Cohen:1991:HSS [CFK+91]M.Cohen,M.Foster,D.Kratzer,P.Malone,and A.Solem.A high school supercomputingchallenge.In IEEE[IEE91],pages68–75.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.REFERENCES8Chervin:1991:CMP [Che91]R.Chervin.Climate model-ing with parallel vector super-computers.In IEEE[IEE91],pages677–??ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Chiueh:1991:IMM [Chi91]T.-C.Chiueh.An integratedmemory management schemefor dynamic alias resolution.In IEEE[IEE91],pages682–691.ISBN0-8186-9158-1(IEEEcase),0-8186-2158-3(IEEE pa-per),0-8186-6158-5(IEEE mi-crofiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACMorder number415913.IEEEComputer Society Press ordernumber2158.IEEE catalognumber91CH3058-5.Chronopoulos:1991:TEP [Chr91] A.T.Chronopoulos.Towardsefficient parallel implementationof the CG method applied to aclass of block tridiagonal linearsystems.In IEEE[IEE91],pages578–587.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Corporal:1991:MFH [CM91]Corporal,H.and H.Mulder.MOVE:a framework for high-performance processor design.In IEEE[IEE91],pages692–701.ISBN0-8186-9158-1(IEEEcase),0-8186-2158-3(IEEE pa-per),0-8186-6158-5(IEEE mi-crofiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACMorder number415913.IEEEComputer Society Press ordernumber2158.IEEE catalognumber91CH3058-5.Cheng:1991:EAI [CP91] D.Y.Cheng and D.M.Pase.An evaluation of automatic andinteractive parallel programmingtools.In IEEE[IEE91],pages412–423.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Chen:1991:CAS [CV91]Y.-C.Chen and A.V.Veiden-parison and anal-ysis of software and directorycoherence schemes.In IEEE[IEE91],pages818–829.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNREFERENCES9QA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Chang:1991:SPP [CWW91]Yao-Jen Chang,J.-L.C.Wu,andJingshown Wu.Scheduling par-allel programs with non-uniformparallelism profiles.In IEEE[IEE91],pages502–511.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Chen:1991:ESD [CY91] D.-K.Chen and P.-C.Yew.Anempirical study on DOACROSSloops.In IEEE[IEE91],pages620–632.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Dannevik:1991:CMM [Dan91]puting mod-eling in a MIMD environment.In IEEE[IEE91],pages678–??ISBN0-8186-9158-1(IEEEcase),0-8186-2158-3(IEEE pa-per),0-8186-6158-5(IEEE mi-crofiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACMorder number415913.IEEEComputer Society Press ordernumber2158.IEEE catalognumber91CH3058-5.deDinechin:1991:UFE [de91] B.D.de Dinechin.A ultra fastEuclidean division algorithm forprime memory systems.In IEEE[IEE91],pages56–65.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Dongarra:1991:GBP [DKMS91]J.J.Dongarra, A.Karp,K.Miura,and H.D.Simon.Gor-don Bell Prize lectures(super-computer applications).In IEEE[IEE91],pages328–337.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Dubois:1991:DCE [DWB+91]M.Dubois,J.-C.Wang,L.A.Barroso,K.Lee,and Y.-S.Chen.Delayed consistency andits effects on the miss rate ofparallel programs.In IEEE[IEE91],pages197–206.ISBNREFERENCES100-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Elton:1991:LBM [Elt91] B.H.Elton.A lattice Boltzmannmethod for a two-dimensionalviscous Burgers equation:com-putational results.In IEEE[IEE91],pages242–252.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Ewing:1991:VPI [EOS91]R.Ewing,P.O’Leary,andJ.Sochacki.Vector/parallel im-plementation of a porous mediaflow code.In IEEE[IEE91],pages294–303.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Felperin:1991:FRP [FGPS91]S.A.Felperin,L.Gravano,G.D.Pifarre,and J.C.L.Sanz.Fully-adaptive routing:packet switch-ing performance and wormholealgorithms.In IEEE[IEE91],pages654–663.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Fiduccia:1991:UMN [FJ91] C.M.Fiduccia and E.M.Ja-cobson.Universal multistagenetworks via linear permuta-tions.In IEEE[IEE91],pages380–389.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Friedell:1991:VBM [FLK+91]M.Friedell,Polla,S.Kochhar,S.Sistare,Juda,and J.Visual-izing the behavior of massivelyparallel programs.In IEEE[IEE91],pages472–480.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-REFERENCES11ber2158.IEEE catalog number91CH3058-5.Farrens:1991:ATS [FWW91]M.Farrens, B.Wetmore,andA.Woodruff.Alleviation of treesaturation in multistage inter-connection networks.In IEEE[IEE91],pages400–409.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Goldberg:1991:PDS [GH91] A.J.Goldberg and J.L.Hen-nessy.Performance debug-ging shared memory multipro-cessor programs with MTOOL.In IEEE[IEE91],pages481–490.ISBN0-8186-9158-1(IEEEcase),0-8186-2158-3(IEEE pa-per),0-8186-6158-5(IEEE mi-crofiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACMorder number415913.IEEEComputer Society Press ordernumber2158.IEEE catalognumber91CH3058-5.Gursoy:1991:HLS [GK91] A.Gursoy and L.V.Kale.Highlevel support for divide-and-conquer parallelism.In IEEE[IEE91],pages283–292.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Glen:1991:CMH [GPCJ91]R.R.Glen,D.V.Pryor,J.M.Conroy,and T.Johnson.Char-acterizing memory hot spots ina shared memory MIMD ma-chine.In IEEE[IEE91],pages554–566.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Granston:1991:DRA [GV91] E.D.Granston and A.V.Vei-denbaum.Detecting redundantaccesses to array data.In IEEE[IEE91],pages854–865.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Hirayama:1991:SFP [HIS91]H.Hirayama,M.Ikeda,andN.Sagawa.Solution functionsof PDEQSOL(partial differen-tial equation solver language)forfluid problems.In IEEE[IEE91],pages218–227.ISBNREFERENCES120-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Hall:1991:ITP [HKM91]M.W.Hall,K.Kennedy,andK.S.McKinley.Interproce-dural transformations for paral-lel code generation.In IEEE[IEE91],pages424–434.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Hiranandani:1991:COF [HKT91]S.Hiranandani,K.Kennedy,and pileroptimizations for FortranD onMIMD distributed-memory ma-chines.In IEEE[IEE91],pages86–100.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Hatcher:1991:ASP [HQA+91]P.J.Hatcher,M.J.Quinn,R.J.Anderso,padula,B.K.Seevers,and A.F.Bennett.Architecture-independent scien-tific programming in dataparallelC:three case studies.In IEEE[IEE91],pages208–217.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Hummel:1991:FPR [HSF91]S. F.Hummel, E.Schonberg,and L. E.Flynn.Factor-ing:a practical and robustmethod for scheduling parallelloops.In IEEE[IEE91],pages610–619.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Hotchkiss:1991:ASI [HW91]R.S.Hotchkiss and C.L.Wampler.The auditorializationof scientific information.In IEEE[IEE91],pages453–461.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-REFERENCES13ber2158.IEEE catalog number91CH3058-5.Ieumwananonthachai:1991:IMC [IAS+91] A.Ieumwananonthachai, A.N.Aizawa,S.R.Schwartz,Wah,B.W.,and J.C.Yan.In-telligent mapping of communi-cating processes in distributedcomputing systems.In IEEE[IEE91],pages512–521.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.IEEE:1991:PSA [IEE91]IEEE,editor.Proceedings,Su-percomputing’91:Albuquerque,New Mexico,November18–22,1991.IEEE Computer SocietyPress,1109Spring Street,Suite300,Silver Spring,MD20910,USA,1991.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Jordan:1991:TMO [JH91]H.F.Jordan and V.P.Heuring.Time multiplexed optical com-puters.In IEEE[IEE91],pages370–378.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Kanada:1991:MVP [Kan91]Y.Kanada.A method of vectorprocessing for shared symbolicdata.In IEEE[IEE91],pages722–731.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCN QA76.5.S8941991.ACM order number415913.IEEE Computer SocietyPress order number2158.IEEEcatalog number91CH3058-5.Karmarkar:1991:NPA [Kar91]N.Karmarkar.A new paral-lel architecture for sparse ma-trix computation based onfiniteprojective geometries.In IEEE[IEE91],pages358–369.ISBN0-8186-9158-1(IEEE case),0-8186-2158-3(IEEE paper),0-8186-6158-5(IEEE microfiche),0-89791-459-7(ACM).LCCNQA76.5.S8941991.ACM or-der number415913.IEEE Com-puter Society Press order num-ber2158.IEEE catalog number91CH3058-5.Koelbel:1991:CGR [Koe91] piler-timegeneration of regular commu-nications patterns.In IEEE[IEE91],pages101–110.ISBN。

计算机英语词汇