赛灵思扩展下一代串行连接产品阵营

Xilinx联盟计划合作伙伴的最新技术

Xilinx联盟计划合作伙伴的最新技术重点介绍了赛灵思联盟合作伙伴生态系统的最新技术更新赛灵思联盟计划是指与赛灵思合作推动全可编程技术发展的认证公司组成的全球性生态系统。

赛灵思创建了这个生态系统,旨在利用开放平台和标准以满足客户需求并致力于帮助它取得长期成功。

包括IP提供商、EDA厂商、嵌入式软件提供商、系统集成商和硬件供应商等在内的赛灵思联盟成员助力提升您的设计生产力,同时最大限度地降低风险。

下面为您分享一些精彩案例。

面向ZYNQ ULTRASCALE+ MPSOC的基于LINUX的多核框架鉴于即将推出的赛灵思Zynq? UltraScale+ ? MPSoC 具备更高的容量、性能和复杂度,因此应用开发人员需要采用新的改进的软件开发范式来有效管理并充分发挥该器件提供的异构处理能力。

Mentor Graphics 的Mentor 嵌入式多核框架作为一种支持基础结构可以管理计算资源的生命周期以及异构多处理环境中的处理器间通信。

Mentor 产品组合的初始集成展示了在管理生命周期和通信的四核ARM?Cortex ? -A53 上运行的SMP Linux。

Nucleus RTOS 运行于采用Mentor 嵌入式多核框架的ARM Cortex-R5 内核上。

Mentor 的Sourcery Codebench 工具可提供一种用来设计非对称多处理(AMP) 系统的集成开发环境。

开发人员在对异构内核上的异构软件环境进行调试和特性描述时需要面对特有的挑战。

Mentor 的嵌入式开发工具为用户避免了这些复杂问题,并使用户深入了解系统运行时间。

这些工具包括如下:用于在AMP 系统中进行资源分区的工具(今年晚些时候供货)用于构建和封装远程固件/ 应用程序的工具用于调试AMP 系统中出现的每个软件环境的IDE能对每个OS/ 应用环境进行特性描述并以统一的时间基准来分析数据的工具如需了解更多信息,敬请访问网址 .MATHWORKS扩大对 ZYNQ-7000全可编程SOC的支持赛灵思联盟计划成员MathWorks在2 0 1 4 b 版本中扩大了对赛灵思Zynq-7000 全可编程SoC 的支持。

赛灵思Vivado设计套件震撼登场

赛灵思Vivado设计套件震撼登场Vivado 设计套件终于震撼登场赛灵思采用先进的EDA 技术和方法,提供了全新的工具套件,可显著提高设计生产力和设计结果质量,使设计者更好、更快地创建系统,而且所用的芯片更少。

历经四年的开发和一年的试用版本测试,赛灵思可编程颠覆之作Vivado 设计套件终于震撼登场,并通过其早期试用计划开始向客户隆重推出。

新的工具套件面向未来十年All-Programmable器件而精心打造,致力于加速其设计生产力。

赛灵思市场营销与公司战略高级副总裁Steve Glaser表示:在过去的几年中,赛灵思把半导体技术的创新推向了一个新的高度,并释放了可编程器件全面的系统级能力。

随着赛灵思在获奖的Zynq-7000 EPP(可扩展式处理平台)器件、革命性的3D Virtex-7堆叠硅片互联(SSI)的技术器件上的部署,除了我们在FPGA技术上的不断创新之外,,我们正开启着一个令人兴奋的新时代一个All-Programmable器件的时代。

All-Programmable器件,将使设计团队不仅能够为他们的设计编程定制逻辑,而且也可以基于ARM和赛灵思处理子系统、算法和I / O进行编程。

总之,这是一个全面的系统级的器件。

Steve Glaser说未来All-Programmable器件要比可编程逻辑设计更多。

他们将是可编程的系统集成,投入的芯片越来越少,而集成的系统功能却越来越多。

Steve Glaser还表示,在利用All-Programmable器件创建系统的时候,设计者所面临的是一套全新的集成和实现设计生产力的瓶颈问题。

一方面从集成的角度讲,其中包括集成算法C和寄存器传输级(RTL)的IP;混合了DSP、嵌入式、连接和逻辑域;验证模块和系统,以及设计和IP的重用等。

实现的瓶颈包括芯片规划和分层;多领域和大量的物理优化;多元的设计与时序收敛;和后期的ECO和设计变更的连锁效应。

正是为了解决集成和实现的瓶颈,使用户能够充分利用这些All-Programmable器件的系统集成能力,赛灵思打造了全新Vivado设计套件。

赛灵思推出ISE设计套件新版本——ISE 12

IE 1 S 2设计套件的高级设计保存功能使设计人 员能够 置技术 ,设计人员能在尽可能小型化 的器件 中集成多种高级

通过可 重复 使用的时序结果快速 实现设计 时序收敛 。设计 应用 ,从而大幅降低系统 成本与功耗 。( 记者 : 胥京宇 ) 圃口

世健科技与首尔半导体签署分销协议 , 正式进军 L D市场 E

世界 电子元器件 2 1 . g ce c .o 0 6 e . c nc m 0

统成本 。 IE 1 S 2设计套件推 出了 F GA业界首款带 自动化分析 P

Sra 规范 。 t m e

部分重配置技术能在不中断其它逻辑工作的情况下下载 部分 b 文件 ,从而动态修改 F G i t P A逻辑块 。IE设计套件 S

与精细粒 度 ( 辑切片 ) 逻 优化 功能的智能 时钟 门控技术 。

赛灵思推出 IE设计套件新版本 S

IE1 S 2

赛灵 思 公 司 日前 推 出 I 。软 件设 计 套件 最 新版 本 人 员不仅 能将设计方 案进行分 区,集 中精 力满足关键模块 SE I 。1 。I SE 2 SE设 计套件首 次利用 “ 智能 ”时钟 门控技术 , 所需 的时序功能 ,而且还可 在进行其他 部分 的设计工作时 将 动态功 耗降低 达 3 %。此外 ,该新 型套件 还提供 了基 将这些模 块锁定 ,以保 存其布局布线 。为推 出即插即用型 0 于 时序 的高 级设 计保 存功 能 、为 即插 即用 设计提 供符 合 F G P A设计 ,赛灵思正对开放式 A MA 4A 4互联协议上 B Xl

新 加 坡 上 市 公 司 世 健科 技 有 限 划和 准备更是赢 得我们分 销权的 重要 能为 L D照 明厂 商提 供 更具 竞争 优 E 公 司 宣布 与首 尔 半 导体 达 成分 销 协 因素。 ” 议 ,授权世 健公 司在 中国、印度 及东

Xilinx演示 56G PAM4 收发器技术迎接下一代以太网部署

Xilinx演示56G PAM4 收发器技术迎接下一代以太网部署2016年3月14日,中国北京——全可技术和器件的全球领先企业赛灵思公司(Xilinx,Inc. (NASDAQ:XLNX))今天宣布运用四级脉冲幅度调制(PAM4)传输机制并采用56G 收发器技术开发了一款16nm FinFET+ 可编程器件。

针对下一代线路速率,PAM4 解决方案是业界公认的最具可扩展性的信令协议,其能够将现有基础架构的带宽提升一倍,从而助力推动新一轮光互联和铜线互联以太网的部署。

赛灵思正在推广与展示超越一般PM4可用性的56G 技术创新,协助培训供应商和生态系统成员,使其为相关技术转型做好准备。

赛灵思公司SerDes 技术部副总裁Ken Chang 指出:“我们的客户早已翘首期盼如何加速下一代应用,这让我们认识到现在必须提升大家对56G PAM4 技术解决方案的认知度,从而帮助他们更好地推进自身设计转型。

我们也很高兴能够藉此展示我们的技术。

”随着云计算、工业物联网和软件定义网络等趋势的持续发展,不断加速并推动着对无限带宽的需求,技术创新必须扩展支持50G、100G、400G 端口以及Tb 接口,以在不增加单位比特成本和功耗的同时最大化端口密度。

标准化线路速率对满足上述不断发展的下一代带宽要求至关重要。

在光互联论坛(OIF)和电气与电子工程师学会(IEEE),赛灵思在56G PAM4 标准化工作中发挥着领导作用。

赛灵思所开发的56G PAM4 收发器技术突破了传统以线路速率传输数据的物理局限性,解决了插入损失和串话等问题。

该技术支持芯片与芯片、模块、直联线缆或背板等应用的铜线和光学互联,支持实现超越Tb级以上线路卡、400G乃至Tb 机架背板的下一代系统设计。

台积公司(TSMC)北美副总裁Sajiv Dala 指出:“台积公司与赛灵思联手打造16nm FinFET+ PAM4 器件。

这一突破性的收发器技术是我们与赛灵思长期良好合作的又一里程碑。

Vishay发布军品级新款零阻值贴片电阻

推 出 的 这 种 系 统 解 决 方 案 具 有 极 高 的 于 50f rl)和信号完整性 ,避免 了 0 iS s l

选件 U NY 还提 供可 选 的相位 噪 声

灵 活性 ,不 受 汽 车 平 台 、配 置 、 输 出 使 用 外 部 调 节 电 路 。 同时 ,其 出 色 的 设置 ,用 以实现 近端 ( 10 H )或 小于 5 k z

■ 国

和 无 线 通 信 系统 的 研 发 和 测 试 工 程 师

的 理发布军品级新款零 h

阻值 贴 片 电阻

日前 ,V sa 宣布 推 出通 过DS C ihy C

检 验的 新款 零 阻值贴 片 电 阻— R CWP M

器 性 能

和 10 p 0 Gb s线 路 卡 的Vitx6HXT re 一 选 件 UNY。该 选 件提 供 优 异 的近 端 和 F GA,并 可 灵 活 配 置 各 种 网 络 速 率 基 准 相 位 噪 声 ,是 从 事 国 防 电子 设 备 P 包 括4 Gb s x0 b s 0Gb s和 0 p 、4 lG p 、10 p 1x 0 p 等 。 此外 ,凭 借其 市场 领 先 0 lGb s

包 和 传 输 、 交换 结 构 、视 频 交 换 和 成 试 ,或 是 对 其 组 成 元 器 件 进 行 分 析 , 像设 备应 用 。

网 . ww w.in om/n xl  ̄c i c

还 是 仅 用 连 续 波 信 号 作 为 本 地 振 荡 器 ,P G 均 可 胜 任 。 如 今 , 安捷 伦 的 S

灯 ;输 出 电压 极 其 灵 活 ,范 围 为 6 V至 最 高 的 串 行 带 宽 ,可 支 持 新 一 代 数 据 频 和 微 波 无 线 系 统 执 行 功 能 和 参 数 测

赛灵思 Alveo U200 U250 数据中心加速器卡用户指南说明书

Alveo U200 和 U250 数据中心加速器卡用户指南UG1289 (v1.0) 2019 年 2 月 15 日条款中英文版本如有歧义,概以英文本为准。

修订历史修订历史下表列出了本文档的修订历史。

目录修订历史 (2)第 1 章: 引言 (4)原理图 (4)卡功能 (5)卡规格 (6)设计流程 (7)第 2 章: 卡建立与配置 (11)静电放电提示 (11)在服务器机箱中安装 Alveo 数据中心加速器卡 (11)FPGA 配置 (11)第 3 章: 卡组件描述 (13)Virtex UltraScale+ FPGA (13)DDR4 DIMM 存储器 (13)Quad SPI 闪存 (13)USB JTAG 接口 (14)FT4232HQ USB-UART 接口 (14)PCI Express 端点 (14)QSFP28 模块连接器 (14)I2C 总线 (15)状态 LED (15)卡电源系统 (15)附录 A: 赛灵思的约束文件 (16)附录 B: 法规合规信息 (17)CE 指令 (17)CE 标准 (17)合规标识 (18)附录 C: 附加资源与法律提示 (19)赛灵思资源 (19)Documentation Navigator 与设计中心 (19)参考资料 (19)请阅读:重要法律提示 (20)第 1 章引言重要提示! 除非另行说明,本用户指南适用于有源与无源版本的 U200 和 U250 卡。

赛灵思 Alveo™ U200/U250 数据中心加速器卡符合外围部件互联 (PCIe®) Gen3 x16 要求,并采用了赛灵思 Virtex®UltraScale+™技术。

这些卡可加速计算密集型应用,如机器学习、数据分析、视频处理等。

Alveo U200/U250 数据中心加速器卡支持被动散热和主动散热配備。

下图展示的是被动散热型 Alveo U200 ES1 加速器卡。

XilinxUltraScale架构-业界首款ASIC级AllProgrammable架构

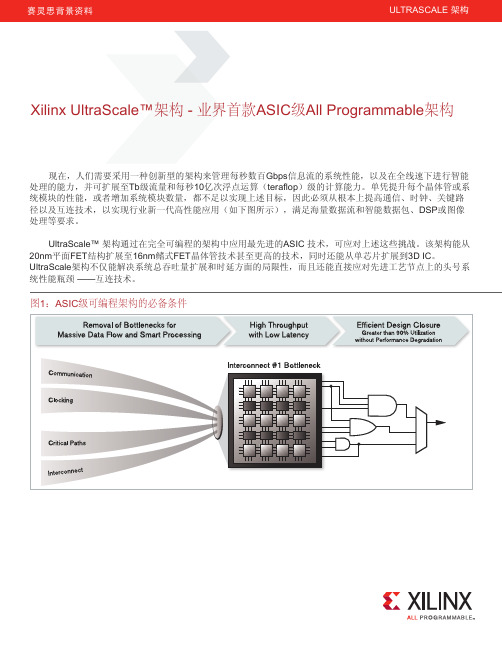

赛灵思背景资料ULTRASCALE 架构Xilinx UltraScale™架构 - 业界首款ASIC级All Programmable架构现在,人们需要采用一种创新型的架构来管理每秒数百Gbps信息流的系统性能,以及在全线速下进行智能处理的能力,并可扩展至Tb级流量和每秒10亿次浮点运算(teraflop)级的计算能力。

单凭提升每个晶体管或系统模块的性能,或者增加系统模块数量,都不足以实现上述目标,因此必须从根本上提高通信、时钟、关键路径以及互连技术,以实现行业新一代高性能应用(如下图所示),满足海量数据流和智能数据包、DSP或图像处理等要求。

UltraScale™ 架构通过在完全可编程的架构中应用最先进的ASIC 技术,可应对上述这些挑战。

该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。

UltraScale架构不仅能解决系统总吞吐量扩展和时延方面的局限性,而且还能直接应对先进工艺节点上的头号系统性能瓶颈 ——互连技术。

图1:ASIC级可编程架构的必备条件• Monolithic to 3D IC • Planar to FinFET • ASIC-class performance图2 :新一代高性能目标应用实图中,高速数据流(Tbps 级的汇聚速率)从左侧进入再从右侧流出。

可通过运行速度为数Gbps 的高速SerDes 收发器进行I/O 传输。

一旦以数Gbps 速度传输的串行数据流进入芯片,就必须扇出(fan out ),以便与片上资源的数据流、路由和处理能力相匹配。

新一代系统要求使用极高的数据速率,因此时钟歪斜、大量总线布置以及系统功耗管理方面的挑战会达到令人生畏的程度。

图3:为您量身定做的新一代架构UltraScale™架构具有无与伦比的高集成度、高容量和ASIC 级系统性能,可满足最严苛应用的要求。

UltraScale 架构经过精调可提供大规模布线能力并且与Vivado ®设计工具进行了协同优化,因此该架构的利用率达到了空前的高水平(超过90%),而且不会降低性能。

赛灵思推出最新Virtex-6/Spartan-6 FPGA连接开发套件

嵌 入式 处 理 、 P, 及 构 建 要 求 高 速 串 行 连 接 功 能 的 系 DS 以

统, 为设 计 团 队提 供 了专 门 针 对设 计 流程 而 精 心 优 化 的 T 具套 件 、 功 能 I 以及 适 合 设 计 人 员 专 业 技 术 领 域 的 通 全 P, 用 的 目标 参 考 设计 。

需 的硬 件 和 软 件 。

客 户提 供 可 在真 实 的 系统 条 件 下实 现 的 高带 宽 运 营支 持 。

S rt V P tai I E F GA 开 发 套 件 基 于 高 性 能 、 密 度 的 x 高

S rt V P S 5 0 F GA。 该 F GA 具 有 5 0 逻 辑 tai I E 4 E 3 P x P 3K 单 元 ( E 。S rt V 4 E 3 P L ) tai I EP S 5 0F GA 所 具 有 的 性 能 和 x 密度优势 , 让使 用 S rtxI E F GA 开 发 套 件 的 广 大 用 tai V P

合 其 符 合 I EE 8 2 1 . E 0 . 5 4的 2 4 GHzMRF 4 4 . 2 J 0收 发 器 和 经 机 构 认 证 的 收 发 器 模 块 , co hp还 提 供 了一 个 高 Mi c i r

效 、 具 成 本 效 益 的 平 台 , 于在 R 极 便 F遥 控 器 和 设 备 中 实

( o ) 发 阶段 的 低 功 耗 水 平 。这 些 最 新 套 件 主 要 针 对 SC 开

布 , 符 合 Z B eR 4 E 的 平 台 已经 获 得 认 证 , 够 实 其 i e FC g 能

现新 一 代 RF 遥 控 器 和 消 费 电 子 产 品 。 该 平 台 包 括 Mir c i co hp的 n n W at ao t XL 超 低 功 耗 P C 单 片 机 、 P I

赛灵思7系列FPGA统一可扩展架构

及 3.V 3

18 .V、25 及 33 .V .V

65 p 串行连接性 .存储器和逻 辑性能 ,而且 . Gb s 还 实现 了信 号处 理性 能 、功耗 和成 本 的极佳 平 衡 ,能支持长 期演进( T ) L E 无线 网络部署 ,满 足

新一 代高清3 D平 板 显 示 器 严 格 的 功 耗 和 成 本 要

能和带宽 。

构相 融合 ,不 仅使新的F GA器件 比上 一代产品 P 的总功耗锐 降5 %,性价 比和 系统 性能双双提 升 0 2 ,同时还集成 了2 0 倍 0 万个逻辑单 元的F GA, P 与前代产 品相 比容量提升 了25 。 . 倍 汤 立 人 认 为 ,低 功 耗 作 为 一种 普遍 性 要 求 ,将 影 响F GA在众 多市场领 域 的使 用 。功 P 耗更 是可编 程逻 辑 向最新AS C I S 应用 和 I  ̄ AS P 市场 扩展的主要 制约 因素 。新的7 系列从 架构 、 工 艺以 及软 件等 方面使 产 品的功 耗大大 降低 。 相对 于前代F GA系列产 品而言 ,Arx7 F G P t 一 P A i 的功 耗  ̄S a tn6F GA 少 了一半 ,成本降 g p ra 一 P 减

37 p 5Gb s

3 OGb s p

Gen1x4

1 .1 5Gb s 03 2 p

3 0Gb s 3 p

Gen 2X8

1 . Gb s 31 p +

1 b s .T p 9

Gen 3X8

存储 器 接 口 l 引脚 / O

l 电压 / o

提供 诸如 大批 量 1 G光学 有线 通信 设备等 各种 0

应用 所 需 的高性 能 1 .Gb 低成 本 优 化的 3 P或 0 s

迈入28nm阵营,Xilinx 7系列FPGA打造完整可编程产品组合

统一架 构 、将整体 功耗 降低一 半且具 言 ,Ar - P .mm焊球间距的低成本 t 7F GA的 功耗 比 S a a - 片级封装和 10 i x p r n6 t

C 有业界最 高容量 ( 多达 2 0万个逻 辑 F G 减 少 了 一 半 , 成 本 降 低 了 P B制造封装 。 0 PA

E cu 一 s■ t v 一 e ’ e n r 一 x t i v l e i 。 ew

迈入 2 n 阵营 ,Xl x7系列 F G 8m i i n P A打 造 完整可编程产 品组合 ■ 记者 :韩霜

P S 在赛灵思公司看来 ,当今的全球经 可编 程解 决方 案 ,而 此前 只有 A SP 低 功耗 、最 低 成本 的 F GA,采用小 济形势为可编程芯片发展提供了天时地 和 A I 能 做 到 这 一 点 。 S C才

p r 一 P A速度 快 a 争取更大的市场份额,往往意味着竞争 构 的 基 础 上 ,推 出 了三 款 全 新 统 一 元不 等 ,比 S atn6F G 者要 跑步 前 进。如今 在 F G P A领 域,

2n 8 m开始成为厂商们的竞争高地。

赛灵 思公司此次推 出的全新 7系 ( 逻辑结构 、Bo kR lc AM、时钟技术 、

工艺 ,与其代工厂伙伴合作 ,协助定义 万 个逻辑 单元 ,在 降低一 半功耗 的情 1 V的新 一代车 载信息娱 乐系统 的小 2 新工艺以达到 F G P A性能的要求。 同时, 况 下实现 了系统 性能 翻番。赛灵思 制 型 、低功 耗要求 ,还能满足 军用航 空 还采用创新型架构增强技术 ,以降低逻 定 了 E s P t WAPC要求 。 . a y ah成本降低计划 ,可确保 电子和通信设备严格 的 S

赛灵思 Alveo

总结赛灵思 Alveo ™ U50 数据中心加速器卡(如下图所示)采用单插槽、小外形尺寸被动散热卡,运行时最大功耗限制为 75W 。

它支持PCI Express ® (PCIe ®) Gen3 x16 或双 Gen4 x8,配备 8 GB 高带宽存储器 (HBM2) 和以太网网络功能。

Alveo U50 旨在加速金融计算、机器学习、计算存储以及数据搜索和分析中的存储器受限、计算密集型应用。

符合部署条件的 U50 量产卡包含一个支持 4x25G 的 QSFP28 连接器。

图 1:Alveo U50量产数据中心加速器卡Alveo U50 数据中心加速器卡数据手册条款中英文版本如有歧义,概以英文版本为准。

U50DD ES3 卡有两个 SFP-DD(小型可插拔-双密度)连接器,每个连接器都支持 2x25G 的性能。

图 2:Alveo U50DD ES3 数据中心加速器卡该卡可搭配赛灵思Vitis™统一软件平台和旨在简化设计流程并支持使用 C、C++ 和 OpenCL™等高级语言的目标平台一起使用。

此类平台支持通过板载闪存对该卡进行配置并通过 PCI Express 对其进行升级。

对于经验丰富的可编程逻辑开发者而言,该卡可搭配 Vivado®Design Suite 使用,利用其中提供的可编程逻辑器件的全部资源来进行开发活动。

如需了解更多信息,请参阅《Alveo U50 数据中心加速器卡用户指南》(UG1371)。

Alveo 产品详细介绍表 1:Alveo U50 加速器卡产品详细介绍规格U50DD ES31, 2U50 量产产品 SKU A-U50DD-P00G-ES3-G A-U50-P00G-PQ-G卡总耗电量375W75W散热解决方案被动被动重量278g 到 287g300g 到 325g外形尺寸半高、半长半高、半长网络接口2x SFP-DD1x QSFP28PCIe 接口4, 5Gen3 x16、Gen4 x8 和 CCIX Gen3 x16、Gen4 x8 和 CCIXHBM2 总容量8 GB8 GBHBM2 带宽201 GB/s6201 GB/s6查找表 (LUT)872K872K寄存器1,743K1,743KDSP slice5,9525,952最高分布 RAM24.6 Mb24.6 Mb36 Kb 块 RAM1344 (47.3 Mb)1344 (47.3 Mb)288 Kb UltraRAM640 (180.0 Mb)640 (180.0 Mb)表 1:Alveo U50 加速器卡产品详细介绍 (续)规格U50DD ES31, 2U50 量产GTY 收发器2020符合部署条件无有注释:1.具有 SFP-DD 接口 (A-U50DD-P00G-ES3-G) 的 Alveo™ U50DD 卡不符合量产条件。

赛灵思打造FPGA巨无霸——基于2.5D堆叠硅片互联技术的Virtex-72000T系列问世

业 夼

Ee uv snev w x c t e tri i I e

需 要投 入 5 0 0 0万到 6 0 0 0万美金 ,比 4 n SC投 资增 为 25 0mA I .D技术 的采用提供 可靠性 的保 障,将 以前做原型设计 加了 4 % 0 其次 。 i x 0 0 Vr 一 2 0T在集成度方面非常成功 , t 7 e 在功 耗 、 性能 、 成本方面具有 良好的性价比。 需 要的十几个 小时缩短 为 3 - ̄ 右 ,平行编译 时间加 个4 u左 , 快 4 。而智能 系统设 计工具 ,让设 计更容易 。赛灵思 目 倍

司在 2 1 年 1 01 0月共 同推 出的一种新 的封装技术 ,通过采 l C放在 一起 ,散 热就 成为很 大 的问题。而 25 . D技 术 的硅 用3 D封装技 术和硅 通孔 (S ) 术 ,在单 个封装 中集成 中介层是被动 的 , TV技 不存在 T V应力 以及散热问题 。Vne t S i n c 多个 F G P A芯片 ,实现突破性 的容量 、带 宽和功耗优 势 , 还 强调 ,25 . D技术 并不是 3 D技 术 中间的过渡技术 ,也不

芯 片本 身的膨胀 系数不一样 ,会产生应 力 ,对 中间连 接的

mco u p 成影 响。第 二 ,硅通孔 (S ) i pm 造 r T V 有应力在 ,会

堆 叠硅片 互联技 术 ( S )是赛灵 思公 司与 T MC公 影 响周 围晶体管 的性 能 。第三 ,热 管理 问题 ,两个主动 的 SI S

以满足那些需要高密度晶体管和逻辑,以及需要高处理能 是 说 3 D就一定比 25 . D好 ,而是各有各的应用市场 。 目 前

力和带 宽性能 的应 用 ,该封装 工艺计 划将赛 灵思 2 n 的 3 8m D技术仅用 于存储器 的集成。赛灵 思也在 与合作伙伴研发 Vr x7 列的 4 F G i -系 t e 个 P A芯片 通过 S I S 封装技 术集 成到 真正 的 3 D技 术。

Xilinx扩展All Programmable SoC产品线

3 . 3 数字 P I D控 制算 法 [ 4 ]

控 制 算 法 是 控 制 软件 中很 重 要 的一 部 分 , 算 法 的 选 用

行 P I D 控制 参 数解 算 , 控制舵机摆舵令 。

[ 4 ]杨 宗 杰 , 乔朝 阳, 伦 涛. 一种基 于 D S P +C P L D 的 舵 机 控 制 器 设计研究[ J ] .科 技论 坛 , 2 0 1 0 ( 2 8 ) : 2 5 , 2 5 0 .

囊 i≯ 誊 秘 般 垂 薯¨ x 篝

机 的 转 向及 停 止 位 置 。实 际 使 用 条 件 下 , 由于 干 扰 或 飞 控

1

1、

、

异常时 , 电动 舵 机 接 收 到 的脉 冲 信 号 有 可 能 超 出 范 围 , 对

此, 软 件 上 进 行 了专 门处 理 。 当接 收 到 的脉 冲宽 度 在 0 . 7

k时 的输 出值 , e ( k ) 为 采 样 时刻 k时 的偏 差 值 , e ( k 一1 ) 为 采样时刻 k 一1 时 的偏 差 值 。 这里控制算法采用分段 、 P I D 算 法 。具 体 是 根 据 控 制

指 令 和 舵 偏 角 的偏 差 大 小 , 选择不 同的 k 。 、 T。 系数 。

由于 位 置 反 馈 电位 器 的线 性 输 出 范 围 为 O 。 ~3 3 0 。 , 而 电 动 舵 机 实 际使 用 的 转 角 范 围 为 ± 6 5 。 。另 外 考 虑 到 位 置

Xilinx进一步扩展All Programmable Artix-7 FPGA系列

Xilinx进一步扩展All Programmable Artix-7 FPGA系列佚名

【期刊名称】《单片机与嵌入式系统应用》

【年(卷),期】2014(14)4

【摘要】赛灵思公司宣布针对汽车应用进一步扩展其Artix-7现场可编程门阵列(FPGA)系列。

全新的XAArtix-7FPGA产品组合,进一步丰富了赛灵思市场领先的AEC—Q100质量认证的汽车(XA)FPGA产品系列。

该系列器件可为高级驾驶员辅助系统(ADAS)、车载汽车娱乐(IVI)系统和驾驶员信息(DI)系统提供业界一流的单位功耗性能。

除了性能优势外,

【总页数】1页(P86-86)

【关键词】Xilinx;驾驶员辅助系统;现场可编程门阵列;汽车应用;性能优势;赛灵思公司;产品组合;质量认证

【正文语种】中文

【中图分类】TN4

【相关文献】

1.Xilinx扩展Spartan-3A FPGA系列 [J], 无

2.Xilinx——从FPGA到处理器推出行业第一个可扩展处理平台Zynq-7000产品系列 [J], 徐俊毅

3.Xilinx——从FPGA到处理器推出行业第一个可扩展处理平台Zynq-7000产品系列 [J], 徐俊毅

4.泰克与躐合作为XILINX FPGA提供实时逻辑调试方案泰克TLA系列逻辑分析

仪和FS2 FPGA View软件为XILINX FPGA提供完整的调试套件 [J],

5.Xilinx推出基于可扩展架构的7大系列FPGA [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

Xilinx发布新型CoolRunner-II CPLD

Xilinx 发布新型CoolRunner-II CPLD全球领先的可编程逻辑解决方案供应商赛灵思公司(Xilinx, Inc. (NASDAQ:XLNX))宣布推出两款新的CoolRunner-II™ CPLD 系列产品。

这两款产品是CoolRunner-IIA 的XC2C32A 和XC2C64A 器件,分别具有32 和64 宏单元密度,均装有一个额外的I/O 组,以支持电压转换和器件接口连接-同时仍保留CoolRunner-II 系列产品的成本优化、低功耗的特点。

赛灵思还为这两种器件提供了更小尺寸的焊盘和更低成本的封装。

可选的新型微引线框架(MLF)芯片级封装减小了器件焊盘的尺寸,其价格可与标准的方型扁平封装(QFP)的价格相比拟(从发展历史来看,芯片级封装一直比较昂贵,因而不是大批量应用的很好选择)。

赛灵思公司CPLD 部门副总裁兼总经理Patrick Little 说,“客户对具有成本效益、低功耗及小焊盘尺寸解决方案的强烈需求是赛灵思公司开发CoolRunner- IIA 产品的催化剂,对多个I/O 组的支持增加了集成度,节约了客户成本。

我们非常高兴能够扩展我们的CPLD 产品种类,以响应大批量应用客户的专门需求。

”探究CoolRunner-IIA市场对在单个器件中集成多个电路功能的需求非常迫切-尤其是在当今的高集成手持设备中。

XC2C32A 和XC2C64A 器件的新特性,可以在广泛的应用领域中实现这种集成。

这两种器件非常适于在使用变化电压和标准的接口总线和设备中,作为标准产品和ASIC 的补充或扩展来使用。

另外,采用赛灵思公司特有的RealDigital 技术实现的低功耗和高性能,使得这些新产品成为对低功耗很敏感的手持设备设计的最终定制逻辑。

对电压转换的需求在许多系统中是很常见的。

有众多的分立逻辑解决方案可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[ ]Mo o n u t e e rh A s c t n 3 trI d sr R sa c s o i i .MI R e e p n y ao S A D v l me t o

筹 兼 顾 ” 角 度 和 大 家 一 起 学 习 讨 论 了 MIRA C++: 的 S

20 0 8中关 于 类 、 生 类 、 员 访 问 的 控 制 、 殊 的 成 员 函 派 成 特

面 对 莫 名 其 妙 的 问 题 时 , 回过 头 来 寻 找 原 因 , 能 一 筹 再 只

莫 展 。如 果 在 程 序 设 计 时 就 遵 循 MI RA +:0 8中相 S c+ 2 0

关的规则 , 自然 可 以避 免 这 样 的 困 扰 。

trs[ ] e n M .Nu etn nao :MI A Lmtd 2 0 . R i e , 08

这 样 的 问 题 往 往 在 程 序 设 计 初 期 不 会 引 起 重 视 , 到 等

参 考 文 献

[ ]Moo n utyReerh A sc t n MIRA C++: 0 8 1 trId sr sac soi i . ao S — 2 0

Gui l sf r t u e oft + + lngu ge i rtc l ys dei o he s he C ne a a n c iia s

G i l e frV hc ae ot r M] ud i s o e ieB sdS f en l wae[ .Nu etn MI n ao : —

R A m t d,1 4. Li e 99

数 以及模 版 的 相 关 规 则 。其 中 一 一 展 开 叙 述 了 。请 继 续 关 注 本 系 列 讲 座 的 就

E]郑 莉 , 渊 .c s 董 ++语 言 程 序 设 计 [ ] 2版 .北 京 : 华 大 学 M . 清

出 版 社 ,0 1 20.

( 稿 日期 : 0 9060 ) 收 2 0 — 1

E c p u a n a d I h rt n e o a s n a s l t o n n e i a c f Cl s i

4 小 结

本 文 是 学 习 MI RA ++系 列 连 载 讲 座 之 三 。 从 “ S C 统

[ ]I 0/ E .I 0/E 4 8 : 0 3 s .Ne o k 2 S I c s I c 1 8 2 2 0 ] E w Y r :Amei n r a c

Na ina a a ds I s iu e,20 . to lSt nd r n tt t 03

aec n etd t r u h acran ca s r o n ce h o g e ti ls .Th d p ino ls n a csp oe ts ft y me n fe c p ua in F rh r r ,te i— ea o t fca se h n e rjc a ey b a so n a s lt . u t emo e h n o o

匝

Pto 可作为嵌入式 系统 的开发语言 ( N k 智能 yhn 在 oi a

2 . 007

手 机所 采用 的 S mba 作 系 统上 已得 到 证 明) y i n操 。它 最 大 的 优 势是 能够很 轻松 地 把使 用其 他语 言 制 作 的各 种 模块 ( 其 尤

是 CC / ++) 松地 联 结 在 一起 。由此 , 可 以直 接 使 用 P — 轻 既 y to h n编 写简单 的界 面 动画 , 可 以将 对速 度 要 求 更 高 的复 杂 也

E ]De e H M , e e PJ ++ 序 设 计 教 程 [ . 万 鹏 , 4 i l D i l .c t t 程 M] 薛 等

译 . 京 : 械 工 业 出版 社 , 0 0 北 机 20.

第 4 : 常 机 制 的使 用 。 讲 异

编 者 注 : 文 为 期 刊 缩 略 版 , 文 见 本 刊 网站 www. 本 全 Ien tc r. n n s e. o c 。l n

h rt nc ea i ns p be we n de i d ca s a s ls v sex r lxi lt o C+ + l n e ia e r lto hi t e rve ls nd ba e ca sgi e t a fe biiy t a gua e H owe e g. v r,i r e o ke a e y n o d r t ep s f t — r l t d pr e sawa e a e oblm y.gr a a e ne d o b xe cs d whe sng ca s M I e tc r e s t e e r ie n u i ls . SRA C+ + s ows UShow o a o d t s r ps h t v i he e ta . Ke r cas e c ps l ton; ihe ia e; I A y wo ds l s; n a u a i n rt nc M SR C+ +

T snghu n ve s t i a U i r iy

.

Li ,S o Be b i n Yi ha i e

̄ src Th o cp fca si ru h ou yo jc r n e rg a b ta t ec n e to ls sb o g tt sb b to i td p o rmmig ( e e n OOP)ln u g u h a a g a es c sC++. Smi ro jcs i l bet a