赛灵思ZYNQ-7000架构

基于Zynq—7000的多种以太网实现方案

基于Zynq—7000的多种以太网实现方案作者:刘佳钱瑞杰李洋来源:《中国科技纵横》2017年第09期摘要:Zynq是Xilinx公司推出的第一个可扩展处理平台,将双核ARMCortex A9处理器与可编程逻辑架构结合,充分体现软硬件协同设计。

以太网是当今通信领域广泛应用的接口,在Zynq中提供了两路千兆以太网控制器,结合MIO、EMIO、AXI、PL等资源,可提供多种以太网实现方案。

关键词:Zynq可扩展处理平台;软硬件协同设计;以太网中图分类号:TP391.41 文献标识码:A 文章编号:1671-2064(2017)09-0040-021 引言随着技术的发展,SOC受到了更多人的关注和推行,Xilinx公司的Zynq作为该领域的领跑者,已被运用到许多场合。

Zynq-7000 系列基于 Xilinx 的可扩展处理平台结构,在单芯片内集成了具有丰富特点的双核 ARM Cortex A9处理器系统(Processing System,PS)和 Xilinx可编程逻辑(Programmable Logic,PL)。

其中,Cortex A9 双核处理器是整个架构的核心,外部存储器接口、及丰富的外设资源都挂载在 ARM上,PL可看做完全可编程的外设。

本文基于以太网接口的大量使用,充分考虑到不同应用场景接口形态的差异,如光口以太网、电口以太网。

结合Zynq所具备的丰富设计资源,提出了基于Zynq-7000的多种以太网实现方案。

2 方案原理Zynq-7000内部有很多常见的I/O外设和存储器接口,是PS的重要组成部分。

这些外设包括GPIO、USB控制器、SPI控制器、UART控制器、千兆以太网控制器等。

这些外设除具备通用功能外,还针对Zynq-7000做了改动。

使其能很好的支持PS+PL的架构,灵活使用PL。

Zynq-7000中还提出了两个新概念,MIO(Multiuse I/O)和EMIO(Extendable Multiplexed I/O)。

zynq原理

zynq原理

Zynq是一款由Xilinx开发的可编程逻辑器件(FPGA)和ARM处理器(通常是Cortex-A9)集成在一起的系统级芯片(SoC)。

Zynq芯片结合了可编程逻辑的灵活性和ARM处理器的处理能力,使得它可以用于各种应用领域,包括通信、工业控制、嵌入式视觉等。

Zynq芯片采用了一种称为Programmable System Integration(PSI)的架构,该架构将FPGA和ARM处理器集成在一起,通过高速片内总线(AXI总线)进行通信。

Zynq芯片的主要组成部分是可编程逻辑部分和处理器系统部分。

可编程逻辑部分由Xilinx FPGA实现,可以根据用户的需求进行配置和重构。

处理器系统部分包括ARM Cortex-A9处理器、存储器控制器、高速IO接口等。

ARM Cortex-A9处理器是Zynq芯片的主处理器,它具有高性能和低功耗的特点。

它可以运行各种操作系统,如Linux和RTOS,提供强大的处理能力和丰富的软件支持。

Zynq芯片还包括一些外设接口,如以太网接口、USB接口、SD卡接口等,以便与外部设备进行通信和数据交换。

Zynq芯片的设计和开发可以使用Xilinx提供的开发工具套件,如Vivado 和SDSoC。

这些工具提供了完整的设计流程,包括硬件设计、软件开发和系统集成,使开发人员能够快速、高效地开发基于Zynq的应用系统。

Xilinx宣布Zynq

Xilinx宣布Zynq

拥有业经验证的高性能、最低功耗和无与伦比生产力的最智能的解决方案

2013年2月26日,中国北京- All Programmable技术和器件的全球领先企业赛灵思公司(Xilinx,Inc. (NASDAQ:XLNX))今天宣布其Zynq™-7000 All Programmable片上系统(SoC)器件系列全线量产,实现了又一个重大里程碑。

Zynq-7000 All Programmable SoC的市场需求非常强劲,目前已有350家不同客户采用该产品进行设计开发,自2011年12月以来赛灵思和安富利(Avnet)已经发货20,000多个器件和4000多个开发板。

各项设计方案广泛应用于包括汽车、工业、通信、数据中心等众多领域。

赛灵思公司处理平台副总裁Larry Getman指出:很明显,赛灵思在规范制定、设计支持、生态系统开发、客户设计和生产交付等各个方面都领先于竞争对手整整一代的水平。

随着对于可以提供软/硬件和I/O可编程功能的高度集成智能与安全SoC器件的需求不断增长,Zynq-7000平台的应用势头也在不断加速。

zynq命名规则

zynq命名规则

Zynq是Xilinx公司推出的一款高性能SoC芯片,其命名规则遵循一定的规则和约定,下面介绍一下Zynq命名的规则。

1. 型号命名

Zynq型号由两部分组成,第一部分为Zynq-,第二部分为数字和字母的组合,表示不同的型号和性能等级。

例如,Zynq-7000系列包括Zynq-7010、Zynq-7020、Zynq-7030、Zynq-7040、Zynq-7100、Zynq-7200等型号,其中数字和字母的组合表示不同的芯片性能等级。

2. 芯片包装形式

Zynq芯片的包装形式一般分为两种,即BGA和FBGA。

其中,BGA为球格阵列封装,球的数量较少,外观为正方形或长方形;FBGA为焊球阵列封装,球的数量较多,外观为圆形。

3. 芯片工艺

Zynq芯片的工艺一般分为两种,即28nm和20nm。

其中,28nm工艺的芯片性能较低,功耗较高,价格相对便宜;20nm工艺的芯片性能更高,功耗更低,价格相对较贵。

4. 芯片功能

Zynq芯片的功能主要分为两类,即PS和PL。

其中,PS为处理系统,包括ARM Cortex-A9处理器、DDR3控制器、SD/SDIO控制器、USB控制器等;PL为可编程逻辑,包括FPGA、DSP、高速串行接口等。

总之,Zynq命名规则是一个比较复杂的体系,需要了解不同的数字和字母组合所代表的含义,才能更好地理解和使用Zynq芯片。

XilinxZYNQ-7000平台简介

XilinxZYNQ-7000平台简介平台介绍Zynq7000是赛灵思公司(Xilinx)推出的⾏业第⼀个可扩展处理平台Zynq系列。

旨在为视频监视、汽车驾驶员辅助以及⼯⼚⾃动化等⾼端嵌⼊式应⽤提供所需的处理与计算性能⽔平。

在2010年4⽉硅⾕举⾏的嵌⼊式系统⼤会上,赛灵思发布了可扩展处理平台的架构详情,这款基于⽆处不在的ARM处理器的SoC可满⾜复杂嵌⼊式系统的⾼性能、低功耗和多核处理能⼒要求。

赛灵思可扩展处理平台芯⽚硬件的核⼼本质就是将通⽤基础双ARMCortex-A9MPCore 处理器系统作为“主系统”,结合低功耗28nm⼯艺技术,以实现⾼度的灵活性、强⼤的配置功能和⾼性能。

由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的⼀致性,同时也⽅便⽇后本系列新产品的命名。

Zynq-7000系列的可编程逻辑完全基于赛灵思7系列FPGA架构来设计,可确保28nm系列器件的IP核、⼯具和性能100%兼容。

最⼩型的Zynq-7000、Zynq-7010和Zynq-7020均基于专门针对低成本和低功耗优化的Artix-7系列;较⼤型的Zynq-7030和Zynq-7040器件基于包括4⾄12个10.3Gbps收发器通道,可⽀持⾼速⽚外连接的中端Kintex-7系列。

所有四款产品均采⽤基于2个12位1MspsADC(模数转换器)模块的新型模拟混合信号模块。

Zynq®-7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上⾼度集成 CPU、DSP、ASSP 以及混合信号功能。

Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗性价⽐最⾼的全⾯可扩展的 SoC 平台,可充分满⾜您的独特应⽤需求。

ZYNQ7000开发平台用户手册说明书

文档版本控制目录文档版本控制 (2)一、开发板简介 (6)二、AC7Z020核心板 (8)(一)简介 (8)(二)ZYNQ芯片 (9)(三)DDR3 DRAM (11)(四)QSPI Flash (14)(五)时钟配置 (16)(六)电源 (17)(七)结构图 (18)(八)连接器管脚定义 (19)三、扩展板 (23)(一)简介 (23)(二)CAN通信接口 (24)(三)485通信接口 (24)(四)千兆以太网接口 (25)(五)USB2.0 Host接口 (27)(六)USB转串口 (28)(七)AD输入接口 (29)(八)HDMI输出接口 (30)(九)MIPI摄像头接口(仅AX7Z020使用) (32)(十)SD卡槽 (33)(十一)EEPROM (34)(十二)实时时钟 (34)(十三)温度传感器 (35)(十四)JTAG接口 (36)(十五)用户LED灯 (36)(十六)用户按键 (37)(十七)扩展口 (38)(十八)供电电源 (40)(十九)底板结构图 (41)芯驿电子科技(上海)有限公司 基于XILINX ZYNQ7000开发平台的开发板(型号: AX7Z020B )2022款正式发布了,为了让您对此开发平台可以快速了解,我们编写了此用户手册。

这款ZYNQ7000 FPGA 开发平台采用核心板加扩展板的模式,方便用户对核心板的二次开发利用。

核心板使用XILINX 的Zynq7000 SOC 芯片的解决方案,它采用ARM+FPGA SOC 技术将双核ARM Cortex-A9 和FPGA 可编程逻辑集成在一颗芯片上。

另外核心板上含有2片共512MB 高速DDR3 SDRAM 芯片和1片256Mb 的QSPI FLASH 芯片。

在底板设计上我们为用户扩展了丰富的外围接口,比如2路CAN 通信接口,2路485通信接口,2路XADC 输入接口, 1路千兆以太网接口,1路USB2.0 HOST 接口,1路HDMI输出接口,Uart 通信接口,SD 卡座,40针扩展接口等等。

Xilinx Vivado zynq7000 入门笔记

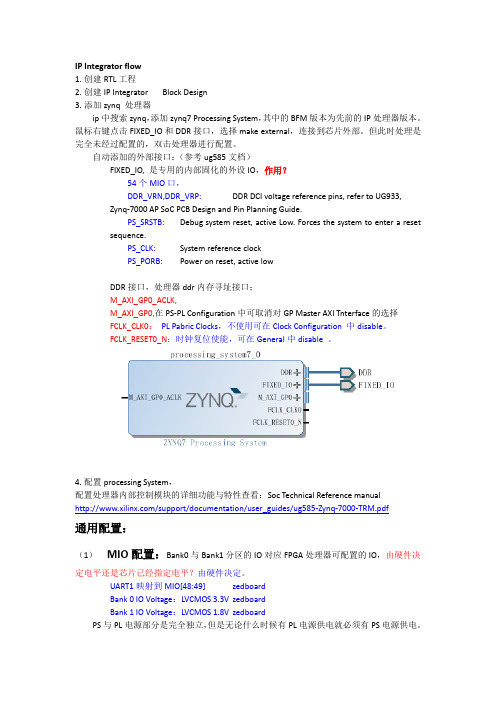

IP Integrator flow1.创建RTL工程2.创建IP Integrator Block Design3.添加zynq 处理器ip中搜索zynq,添加zynq7 Processing System,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FIXED_IO和DDR接口,选择make external,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FIXED_IO, 是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP: DDR DCI voltage reference pins, refer to UG933, Zynq-7000 AP SoC PCB Design and Pin Planning Guide.PS_SRSTB: Debug system reset, active Low. Forces the system to enter a reset sequence.PS_CLK: System reference clockPS_PORB: Power on reset, active lowDDR接口,处理器ddr内存寻址接口;M_AXI_GP0_ACLK,M_AXI_GP0,在PS-PL Configuration中可取消对GP Master AXI Tnterface的选择FCLK_CLK0:PL Pabric Clocks,不使用可在Clock Configuration 中disable。

FCLK_RESET0_N:时钟复位使能,可在General中disable 。

4.配置processing System,配置处理器内部控制模块的详细功能与特性查看:Soc Technical Reference manual/support/documentation/user_guides/ug585-Zynq-7000-TRM.pdf通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

AUMO ALINX ZYNQ-7000产品手册说明书

ZYNQ-7000产品手册ZYNQ-7000 Product Guide2023关于我们官方合作伙伴业务范围芯驿电子科技(上海)有限公司,成立于2012年,总部位于上海松江临港科技城,是一家车载智能产品和FPGA 技术方案公司,拥有“AUMO”和“ALINX”两大品牌,其中AUMO 品牌专注车载智能产品,ALINX 品牌专注于FPGA 产品和方案定制。

经历十年发展,公司产品已经远销海外30多个国家。

2018年,公司通过高新技术企业认证,并通过ISO9001质量体系认证;2019年,荣获上海市松江区九亭镇“科技创新奖”;2020年,荣获上海市“专精特新企业“称号;2021年,申请通过上海市科技型中小企业技术创新资金项目,通过了国家级科技型中小企业认定,并通过了高新技术企业认证复审;2022年获得上海市张江国家自主创新示范区专项发展资金并通过“上海市创新型中小企业”认证。

ALINX 是全球的FPGA 芯片龙头企业XILINX 官方合作伙伴,国内FPGA 芯片龙头企业紫光同创官方合作伙伴,同时作为百度AI 合作伙伴,为百度定制了国产AI飞桨系统的Edgeboard 系列边缘设备。

通过多年的研发投入,已经推出100多款FPGA SoM 模组和配套板卡,积累了1000多家企业批量用户,上万个独立开发者,市场占有率遥遥领先。

通过产品+定制化服务的经营方式,ALINX 将继续加大对产品研发和技术研究的投入,不断与垂直行业客户合作,聚焦高端设备领域,协助客户解决行业的技术难题。

主要聚焦于FPGA + AI 解决方案,FPGA 国产化,FPGA 开发套件, ALINX 自有品牌产品。

公司提供的设计解决方案涉及人工智能、自动驾驶、轨道交通、半导体、5G 通信、医疗设备、工业互联、仪器仪表、数据中心、机器视觉、视频图像处理等行业。

紫光同创国内唯一的FPGA 板卡官方合作伙伴,XILINX 官方重要合作伙伴,百度AI合作伙伴。

XiIinx宣布Zynq-7000AJJProgrammabIeSoC系列全线量产

而 ,利用 每 一 片 3 0 0毫 米薄 晶 圆所 能生 产 出的芯 片

数量可增加至 2 . 5 倍 。这项新技术带来 了随时可得 的更高产能和更高生产 率 ,这将令客户获益匪浅 。

( 来 自英 飞凌科 技 )

品。 ( 来自L S I )

发板 。各项设计方案广泛应用于包括汽车、 工业 、 通

Z y n q 一 7 0 0 0系列支 持 客户 为 其 系统 提供 更 先 进 的软件 智 能 , 包 括控 制 、 通信 、 安全、 系统管 理与 分 析

过基站 、 蜂窝站路 由器、 网关和移动回程设备为网络 信 、 数据中心等众多领域。

Z y n q ~ 7 0 0 0 A l l P r o ra g mm a b l e S o C的市 场需 求非 常 强 劲 , 目前 已有 3 5 0家不 同客户 采用 该产 品进行 设 计

开发 , 自 2 0 1 1年 1 2月 以 来 赛 灵 思 和 安 富 利

( A v n e t ) 已经 发货 2 0 , 0 0 0多 个 器件 和 4 0 0 0多 个 开

L S I推 出采用 A R M领先技 术的 全新通信处理器

L S I 公 司 日前推 出了 A x x i a  ̄5 5 0 0通信处理器

产 品 系列 ,旨在 提 高多 频无 线 基 站 和 4 G / L T E无 线 网络 的性 能和 功率 效率 。L S I  ̄A x x i a 5 5 0 0系列产 品

l R推 出车 用

A U I R 3 2 0 0 S M O S F E T马 区 动 l C

国际整流 器公 司 ( I n t e na r t i o n a l R e c t i f i e r , 简 称 Mi c r o c h i p T e c h n o l o g y I n c . ( 美 国微 芯 科技 公 司 ) 宣 布 ,推 出全球第 一 款数 字增 强 型 电源模拟 控 制器

第4章Zynq-7000可编程逻辑资源

PL可以全部地重新配置或者在使用的时候部分动态地重新配 置(Partial Reconfiguration, PR)。

PR允许只配置PL的一部分。这使得可以选择对设计进行修改,比如: 更新系数或者在必要的时候,替换算法来实现时分复用PL资源。后者 类似于动态地加载和卸载软件模块。PL的配置数据称为比特流。

24

可编程逻辑资源功能

--块存储器

可编程数据宽度

每个端口可以配置为32K×1、16K×2、8K×4、4K×9(或 者8)、2K×18(或者16)、1K×36(或者32)、或者512×72 (或者64)。两个端口可以有不同的宽度,并且没有任何限制。

每个BRAM能分割为两个完全独立的18Kb BRAM。每个 BRAM能配置成任何长宽比,范围从16K×1到512×36。前面描述 的用于36Kb的BRAM的所有内容也可以应用到每个较小的18Kb BRAM。

19

可编程逻辑资源功能

--时钟管理

全局时钟线可以通过全局时钟缓冲区驱动,该缓冲区能执 行无毛刺的时钟复用和时钟使能功能。通常由CMT驱动全 局时钟,它能彻底的消除基本时钟分配延迟。

20

可编程逻辑资源功能

--时钟管理

区域时钟

区域时钟能驱动它所在区域内的所有时钟。 注:一个区域定义为任何一个区域,这个区域有50个I/O,以 及50 个CLB高及一半的器件宽度。 Zynq-7000 EPP器件有8~24个区域。在每个区域有4个区域时 钟跟踪。每个区域时钟缓冲区可以由4个时钟功能输入引脚中的 一个驱动,可选择从1-8中的任何一个整数对该时钟分频。

它们都能作为一个频率合成器,用于宽范围的频率和输入 时钟的抖动过滤器。

基于AD9371及Zynq-7000的软件无线电硬件平台设计

线电硬件平台的设计。基于该设计,工程人员通过软件的动态重构可实现灵活多变的通信体制和

通信功能,可广泛应用于个人移动通信、军事通信、雷达系统等领域。

关键词:软件无线电;AD9371;Zynq-7000 FPGA;JESD204B 接口;软件重构

中图分类号:T021)14-0001-06

基于以上原因,文中提出了一种基于 ADI 公司 的 集 成 RF 芯 片 AD9371 和 Xilinx Zynq- 7000 FPGA 的 多 通 道 通 用 软 件 无 线 电 硬 件 平 台 设 计 方 案 ,硬 件 平台原理框图如图 1 所示。该硬件方案以 AD9371 和 Zynq-7000 系 列 的 XC7Z045 为 核 心 电 路 ,其 工 作 频率范围为 300 MHz~6 GHz,包含 2 路发射通道和 2 路 接 收 通 道 功 能 的 MIMO 收 发 器 ,可 支 持 FDD 及 TDD 两种工作模式。工程设计人员通过软件的动态 重构可适应多种通信体制和通信功能。该硬件平台 的 电 路 单 元 包 括 射 频 收 发 单 元 AD9371 电 路 、以 Zynq-7000 FPGA XC7Z045 为核心的数字信号处理 电路、时钟锁相电路单元、DDR3 存储电路、电源转换 网络相关电路及接口电路等 。 [4] 1.2 主要硬件电路单元的设计与实现 1.2.1 射频收发器单元 AD9371 电路的设计与实现

摘要:文中基于软件无线电的技术原理及思路,提出了一种基于 AD9371 及 Xilinx Zynq-7000 FPGA

的软件无线电通用硬件平台的设计方案及工程实现方法。该硬件平台工作频率为 300 MHz~6 GHz,

包含了 2 路发射通道和 2 路接收通道功能,支持 FDD 及 TDD 两种工作模式,适用于多种应用场景。

Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCV应用

如何使用Vivado HLS视频库加速Zynq-7000 All Programmable SoC OpenCVg p应用2013年9月11日© Copyright 2013 XilinxOpenCV简介机(p)机开源计算机视觉(OpenCV) 被广泛用于开发计算机视觉应用–包含2500多个优化的视频函数的函数库–专门针对台式机处理器和GPU进行优化–用户成千上万–无需修改即可在Zynq器件的ARM处理器上运行但是–利用OpenCV实现的高清处理经常受外部存储器的限制–存储带宽会成为性能瓶颈–存储访问会限制功耗效率Zynq All-programmable SOC是实现嵌入式计算机视觉应用的极好方法–性能高、功耗低实时计算机视觉应用计算机视觉应用实时分析功能高级驾驶员安全辅助车道或行人检测安防监视敌我识别高速物体检测用于工厂自动化的机器视觉非侵入式医疗成像技术肿瘤检测实时视频分析处理基于帧的基于像素的Pixel based 4Kx2K 特征处理与决策图像处理与特征提取Image processing and FeatureextractionF11080p F2 F3720p480…..480p每像素数百次运算每特性数10000次运算800万次处理x每帧100次运算= 数百亿次运算每秒处理数1000个特征= 数百万次运算实时视频分析的异构实现基于帧的基于像素的图像处理与特征Pixel based 4Kx2K特征处理与判定提取Image processing and Featureextraction F11080pF2F3软件域(ARM)硬件域(FPGA)720p480…..480p每像素数百次运算每特性数10000次运算800万次处理x 每帧100次运算= 数百亿次运算每秒处理数1000个特征= 数百万次运算赛灵思实时图像分析的实现:Zynq All Programmable SoC Programmable SoCFrame based Feature processing and 基于像素的图像处理与特征Pixel based 4Kx2KFeature processing and decision making提取基于帧的特征处理与判定Image processing and FeatureextractionF11080pF2F3720p480…..480p每像素数百次运算每特性数10000次运算1000800万次处理x 每帧100次运算= 数百亿次运算每秒处理数个特征= 数百万次运算Vivado:提高OpenCV应用的效率高清视频算法(每秒约1帧)的C语言仿真–高清视频(每小时1 帧)的RTL仿真实时FPGA实现方案高达60fpsZynq 视频参考设计架构DDR3DDR3外部存储器处理系统DDR 存储控制器SD 卡双核Cortex-A9硬化的外设S_AXI_GP 32b 位S_AXI_HP 64 位AXI4S AXI 互联AXI4 Stream IP 核HDMIHDMI视频输入Xylon 显示控制器HLS 生成的流水线AXI VDMA使用64位高性能端口实现对外部存储器的视频访问使用32位通用端口实现控制寄存器访问使用AXI4-Stream 实现的视频流以IP 为中心的设计流程更快速的IP生成与集成基于C 语言的IP 创建用户首选的系统集成环境C 、C++ 或SystemCDSP 系统生成器(System Generator)C 函数库•浮点math.h •定点VHDL V il •视频VHDL 或Verilog 以及软件驱动Vivado IP 集成器IP 子系统赛灵思IP 第三方IP Vivado RTL 集成用户IP在FPGA 设计中使用OpenCV纯集成的O CVO CV 图像文件读取OpenCV 应用OpenCV 应用OpenCV 参考加速的OpenCV 应用图像文件读取(OpenCV)(OImage penCV)OpenCV2AXIvideo 实时视频输入实时视频输入O CV 函数链AXIvideo2Mat模块O CV 函数链AXIvideo2Mat模块OpenCV HLS 视频库函数链Mat2AXIvideo可综合的OpenCVHLS 视频库函数链Mat2AXIvideo可综合的图像文件写入(OpenCV)AXIvideo2OpenCV 图像文件写入实时视频输出实时视频输出(OpenCV)DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)12345SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线DDR3处理系统DDR 存储控制器DDR3DDR3外部存储器图像文件读取(OpenCV)SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设HDMIHDMIXylon 显示AXI VDMAAXI 互联图像文件写入(OpenCV)视频输入y 控制器HLS 生成的流水线集成的OpenCV 应用DDR3处理系统DDR 存储控制器DDR3DDR3 外部存储器实时视频输入12345SD卡双核Cortex-A9OpenCV 函数链Cortex A9硬化的外设p HDMIHDMIXylon显示AXI VDMAAXI 互联实时视频输出视频输入y 控制器HLS 生成的流水线OpenCV 参考/软件执行DDR3图像文件读取处理系统DDR 存储控制器DDR3DDR3外部存储器12345(OImage penCV)OpenCV2AXIvideo SD卡双核Cortex-A9AXIvideo2MatCortex A9硬化的外设HLS 视频库函数链Mat2AXIvideoHDMIHDMIXylon 显示AXI VDMAAXI 互联AXIvideo2OpenCV图像文件写入视频输入y 控制器HLS 生成的流水线(OpenCV)OpenCV 参考/系统测试DDR3图像文件读取处理系统DDR 存储控制器DDR3DDR3外部存储器(OImage penCV)OpenCV2AXIvideo 12SD卡双核Cortex-A9AXIvideo2MatCortex A9硬化的外设HLS 视频库函数链Mat2AXIvideoHDMIHDMIXylon 显示AXI VDMAAXI 互联AXIvideo2OpenCV图像文件写入视频输入y 控制器HLS 生成的流水线(OpenCV)加速的OpenCV 应用DDR3处理系统DDR 存储控制器DDR3DDR3 外部存储器实时视频输入12SD卡双核Cortex-A9AXIvideo2Mat视频库函数链Cortex A9硬化的外设HLS Mat2AXIvideoHDMIHDMI视频输入Xylon显示AXI VDMAAXI 互联实时视频输出y 控制器HLS 生成的流水线OpenCV设计流程OpenCV模块A1)在台式机上开发OpenCV应用2)无需修改即可在ARM内核上运行OpenCV应OpenCV模块B用3)使用I/O函数抽象FPGA部分O CV 4)用可综合代码代替OpenCV函数调用5)运行HLS以生成FPGA加速器OpenCV模块C6)用FPGA加速器调用代替可综合代码调用OpenCV模块DOpenCV 应用的软硬划分opencv2AXIvideo OpenCV 模块AAXIvideo2HLSOpenCV 模块BHLS 模块BO CV HLS 模块C同步OpenCV模块C HLS2AXIvideoOpenCV 模块DAXIvideo2opencv综合OpenCV设计中的权衡OpenCV图像处理是基于存储器帧缓存而构建的–访问局部性较差-> 小容量高速缓存性能不足–架构比较复杂(出于性能考虑)-> 功耗更高–似乎足以满足很多应用的要求•分辨率或帧速率低•在更大的图像中对需要的特征或区域进行处理基于视频流的架构能提供高性能和低功耗–链条化的图像处理函数能减少外部存储器访问针对视频优化的行缓存和窗缓存比处理器高速缓存更简单–针对视频优化的行缓存和窗口缓存比处理器高速缓存更简单–可使用HLS中的数据流优化来实现–需要将代码转换为可综合的代码HLS视频库OpenCV函数不能直接通过HLS进行综合O C S–动态内存分配–浮点–假设图像在外部存储器中修改HLS视频库用于替换很多基本的OpenCV函数–与OpenCV具有相似的接口和算法–主要针对在FPGA架构中实现的图像处理函数–包含专门面向FPGA的优化•定点运算而非浮点运算•片上的行缓存和窗口缓存–不必精确到比特位赛灵思HLS 视频库2013.2AXI4-Stream IO 函数视频数据建模Li b ff ClWi d ClOpenCV 接口函数cvMat2AXIvideo AXIvideo2cvMat cvMat2hlsMat hlsMat2cvMat I lI 2AXI id AXI id 2I lI I lI 2hl M t hl M t2I lI AXIvideo2MatMat2AXIvideoLinebuffer Class Window Class 视频函数Duplicate MaxS Remap IplImage2AXIvideo AXIvideo2IplImage IplImage2hlsMat hlsMat2IplImage CvMat2AXIvideo AXIvideo2CvMat CvMat2hlsMathlsMat2CvMat AbsDiff AddSEqualizeHist Mean Resize AddWeighted Erode Merge Scale And FASTX MinSet Avg Filter2DMinMaxLoc Sobel AvgSdv GaussianBlur MinS Split Cmp HarrisMul SubRS CmpSHoughLines2NotSubS CornerHarris IntegralPaintMask SumCvtColor InitUndistortRectifyMap Range Threshold DilateMaxReduceZero如需了解函数的详情,敬请阅读HLS 用户指南UG 902视频库函数#include “hls video h”包含在hls 命名空间内的C++代码。

Xilinx Zynq 7000-总结

用鼠标点击配置界面上方的Main、Device Initialization、STDIO Connection、

Profile Options、Debugger Options和Common标签,查看这些标签界面下的,配 置内容。

点击运行配置界面下方的“RUN”按钮,运行程序。

23

主要内容

AXI_GP

四个通用接口(两主两从),每个位宽为32,可访问PS的DDR3控制器、PS的片上 RAM资源和其他从设备

AXI_ACP

用于PL的一个加速一致性主端口。提供快速访问CPU,可选的与L1或L2缓存一致 性

7

Zynq7000平台简介

Zynq-7000系统的互联资源

8

Zynq7000平台简介

在SDK主界面左侧的Project Explorer窗口下,右键选中peripheral_tests_0条目,点击 鼠标右键出现浮动菜单,在浮动菜单内选择Run As->Run Configurations…

出现运行配置界面。在该配置界面下,选择Xilinx C/C++ELF选项,点击鼠标右键,出 现浮动菜单,选择New。生成新的运行配置界面。

12

Zc702基本系统的建立和运行

Zc702 基本系统的建立

选择board为ZC702,next 去掉默认添加的IP, BTNs_5Bits、LEDs_8Bits 和SWs_8Bits,next 向导流程完成后,可以选择Generate Bitstream,来 获得下载到PL的位流码文件

5

Zynq7000平台简介

Zynq-7000系统的逻辑资源:PL

PL资源

Artix7 : 7z010、7z020 Kintex7:7z030、7z045、7z100

赛灵思 Zynq器件要点

找PFGA上赛灵思半导体(深圳)赛灵思Zynq器件要点目前赛灵思zynq器件刮起了一阵SoC风,正在全国如火如荼的推行。

Zynq-7000 系列处理基于赛灵思的可扩展处理平台Extensible ProcessingPlatform,EPP)结构,该结构在单芯片内集成了基于具有丰富特点的双核ARMCortex-A9 MPCore 多核处理器的处理系统(Processing System,PS)和赛灵思可编程逻辑(Programmable Logic,PL)。

其中,Cortex-A9 双核处理器是整个架构的核心,外部存储器接口、及丰富的外设资源(PL可看做完全可编程的外设)都挂载在ARM上。

1 ZYNQ 处理器概述从Zynq 处理器的结构框图(图1-1)可以看到PS位于整个架构的核心,PL 通过各数据互联接口与PS进行交互。

1.1 处理器系统(PS)处理器系统主要由应用处理单元(APU)、通用外设、时钟复位系统及互联接口构成。

1.1.1 应用处理单元(APU)应用处理单元(APU)包括:(1)两个独立的ARM Cortex-A9(ARMv7)处理器内核与两个Neon 协处理器,他们共享512KB 的L2 缓存。

各处理的L1 级缓存是独立的,因此两个处理器可以单独运行各自的任务。

Neon技术主要用于加速多媒体和信号处理算法(如视频编解码、3D图形、图像处理技术、游戏加速等),Neon可认为是128bit矢量DSP,可执行打包的SIMD 指令,最高支持64bit单精度浮点运算。

(2)8 通道DMA 控制器。

64bit位宽,支持M-toM,其中四个通道支持PL请求。

(3)L1 和L2 级Cache。

512KB L2 级Cache为两个处理器共有,32KB D-Cache 和I-Cache 为每个处理器私有。

(4)GIC(Generic Interrupt Controller)。

管理95 中断信号,需要注意的是,PL-PS 的中断有对应各自处理器的快速中断和普通的F2P IRQ。

Zynq-7000 All Programmable SoC工业自动化方案

P r o g r a m m a b l e解 决 方 案 ,以应 对 高 赛 灵 思 与其 联 盟 汁 划 成 员 QDE S YS 以太 网套件结 合使 用 ,开发 出业 界一

级 运 动 控 制 、实 时 工 业 网 络 、机 器 公 司 提 供 了 基 于 Z y n q . 7 0 0 0 Al l 流的双 核锁步 马达控 制应 用的企 业 。 视 觉 以及 其 他 新 一 代 工 业 自动 化 应 P r o g r a mma b l e S o C智能 驱动 平 台 的 该 应 用 将 帮 助 设 计 者 实 现 其 系 统 的 用 的 挑 战。 赛 灵 思 以 Z y n q - 7 0 0 0 Al 高性能运 动控 制应用 ,可 以实 现千 兆 I l E C6 1 5 0 8功能安全认证 。

随 着设 备综合效 率 ( OE E)的 模 型 ( C OM)接 口的支持下 ,设计 人 计 ,可加 速工业 嵌入式 控制 系统 的设 不 断提 高 ,工业 自动化 市场需 要实现 员能对运动系统进行深入分析和控制 , 计与 实现进程 。该平 台非常适 合要 求 S P解决方 案而 言实 单芯 片高性能 马达控 制和 工业 网络功 更高生产 力 ,降低总拥 有成本 ,同时 相对于传 统 的 AS 还 需要提 高安 全性和 系统功 能 。要满 现了性能的提 升。 足上述 要求 ,系统 的计 算性能 必须 更 能的设 计。赛灵思提 供 Z y n q - 7 0 0 0 A l l

P r o g r a mma b l e S o C为 核 心 的系统 开 位 以太 网紧密 集成 网络 、采用 创新型

赛 灵 思 与 其 联 盟 成 员共 同 推 出

发软 / 硬 件技 术 ,不 仅能 加 速设 计生 低 E MI 功率调制 方案 的高级 马达和运 的 新 Z y n q 一 7 0 0 0 Al l P og r r a mma b l e 产 力 ,同时还 可通 过单 芯片系统 集成 动控制 。在面 向 Wi n d o ws 应用 的图形 S o C智能驱 动器平 台提供 了必要 的硬 提升 系统 的性能和安全性 。 用户 界面 ( GU I )和 强大 的组 件 对 象 件 、设计 工具 、马达 、I P核和 参考 设

基于单核Zynq 7Z007S的MiniZed

基于单核Zynq 7Z007S的MiniZed™ 开发套件

全球可编程平台领导厂商赛灵思公司(Xilinx,Inc.)推出行业第一个可扩展的处理平台Zynq®-7000全可编程SoC (AP SoC)系列。

与传统的FPGA相比,Zynq-7000系列最大的特点是将处理系统PS和可编程资源

PL分离开来,固化了PS系统的存在,实现了真正意义上的SOC(System

On Chip)。

同时,这种软硬件均可编程的全可编程SoC集成了ARM®处理器的软件可编程性与FPGA的硬件可编程性,不仅可实现算法的硬件加速,还在

单个器件上高度集成CPU、DSP slice,高速收发器以及模拟信号处理等功能。

为展示Zynq 功能及为入门级用户提供一种低成本Zynq 开发环境和培训、原型设计和概念验证的演示平台,有代理商推出了基于单核Zynq 7Z007S的MiniZed™ 开发套件。

板同其名,整个开发板的尺寸只有76mm X 71mm. 而其售价也仅89美元。

尽管是一款低成本、小型的开发平台,可无论是主控芯片,还是其外设资源,MiniZed开发板的配置都可圈可点。

在提

供一种高效的硬件参考设计的同时,也可用来运行实验课和教程。

下面将透

过其特色和目标应用进行介绍:。

Zynq-7000可扩展处理平台

可扩 展性和 F G P A的可扩 展性 ,在管理风 险上有优势 ,总

Z n . 0 0处 理 器 是 一 套 完 整 的 系 统 ,硬 核 的 部 分 和 体 来看 ,Z n .0 0会有 比较长 的生命周 期 ,是 比较 新的 yq70 y q7 0 软核 的部 分是互相 协同的工 作方式 ,由于 存在可编程 逻辑 解 决 方 粟 。

设计环境 , 具有 完整的软件编程模型 ,

SCs 案来搭 建下一 代的处理 器系统 。多芯 同时 A I 有 技术风险 和生产方面 的 还 有大家 非常熟悉 的软件 和硬件 的设

片方案 成本较 高 ,功耗 大 ,占用更多 风 险 ,研发 周期相 对 比较长 ,在 上市 计 流程。它们具有 灵活 的加 速器

的部件 ,大 家在应对下 一代 的应 用需求或 者对现有需 求进

行延 伸扩展 时有 非常大 的灵活 性 。同时 A RM 的处理 方面

是工业标 准的部件 ,可 以用 以前 的代码和 以前的 设 汁,也 可以 引用很 多业界上 先进的设 计 ,是很好 的处理器 ,希 望 大家可 以从 网站上进行更多深入的了解 。

可编程逻辑 的部分

可编程 逻辑 的部 分通常会包含相

在处理器 子系统框 图的上边的部 当数 量的逻辑单元 ,A I SC设计工程师 分 ,有 S1 D1的 控制 器 ,S1控制 可 能会把 它理解 成最新 配置 ,同时也 和

FG P A的部 分用于扩 展 子系统 ,有 丰 器 或者 说 静态 存储 器 包含 多 个接 口, 包含 了 D B单元大块的 R M ,或者 S A 富 的扩展 能 力 ,有超 过 3 0 0 0个 内部 互联 ,提供 的带 宽非常 丰富 。此 外在 I O整 件 方 面 ,F GA的优 点 是 l P O可 以充 分 自定义 ,可 以在 F G P A部分提 供 集成高速 的 串行 口,执行 多种 串行 标 准。同时在 F GA内集 成了一个硬 P 核 ,即模数 转换器 ,这些总体 部件共

zynq-7000简介

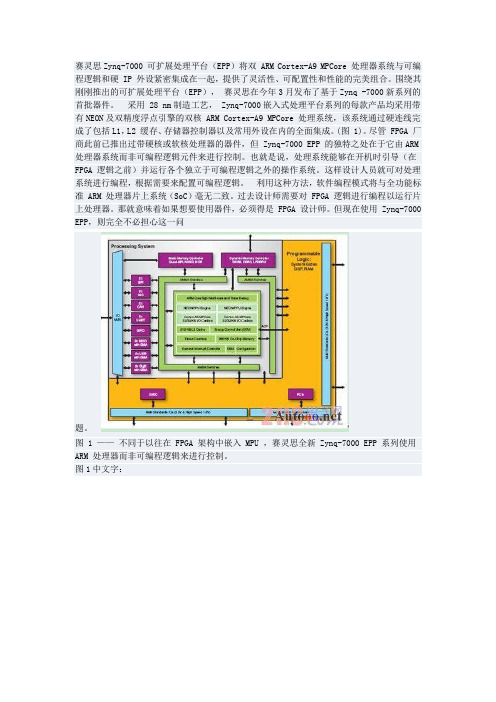

赛灵思Zynq-7000 可扩展处理平台(EPP)将双 ARM Cortex-A9 MPCore 处理器系统与可编程逻辑和硬 IP 外设紧密集成在一起,提供了灵活性、可配置性和性能的完美组合。

围绕其刚刚推出的可扩展处理平台(EPP),赛灵思在今年3月发布了基于Zynq -7000新系列的首批器件。

采用 28 nm制造工艺, Zynq-7000嵌入式处理平台系列的每款产品均采用带有NEON及双精度浮点引擎的双核 ARM Cortex-A9 MPCore 处理系统,该系统通过硬连线完成了包括L1,L2 缓存、存储器控制器以及常用外设在内的全面集成。

(图 1)。

尽管 FPGA 厂商此前已推出过带硬核或软核处理器的器件,但 Zynq-7000 EPP 的独特之处在于它由ARM 处理器系统而非可编程逻辑元件来进行控制。

也就是说,处理系统能够在开机时引导(在FPGA 逻辑之前)并运行各个独立于可编程逻辑之外的操作系统。

这样设计人员就可对处理系统进行编程,根据需要来配置可编程逻辑。

利用这种方法,软件编程模式将与全功能标准 ARM 处理器片上系统(SoC)毫无二致。

过去设计师需要对 FPGA 逻辑进行编程以运行片上处理器。

那就意味着如果想要使用器件,必须得是 FPGA 设计师。

但现在使用 Zynq-7000 EPP,则完全不必担心这一问题。

图 1 ——不同于以往在 FPGA 架构中嵌入 MPU ,赛灵思全新 Zynq-7000 EPP 系列使用ARM 处理器而非可编程逻辑来进行控制。

图1中文字:Multi Gigabit Transceivers 多个千兆位收发器新产品系列消除了延迟和从头设计芯片的风险,这意味着系统设计团队可以利用其先进的高级软硬件编程多功能性简便快速创建创新型片上系统,而这是其他任何半导体器件都无法实现的。

这样,Zynq -7000 EPP 能够为广大的创新者带来无法比拟的益处,无论是专业的硬件、软件、系统设计师或仅是单纯的“制造商”,他们都可以探讨处理能力与编程逻辑结合的可能性,进而创建出从未想象过的创新应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

赛灵思ZYNQ-7000架构

该文章的硬件平台是:ZC702(XC7Z020-1CLG484CES )。

所用软件包括:PlanAhead、Xilinx Platform Studio、Xilinx Software Development Kit,版本均为14.4。

串口工具为Tera Term。

ZYNQ-7000是Xilinx推出的一款全可编程片上系统(All Programmable SoC),该芯片集成了ARM Cortex A9双核与FPGA,所以ZYNQ是一款SoPC芯片。

其架构如下图:

图中的Processing System(一般简称为PS)即为处理器(ARM Cortex A9 MPCore)部分,里面资源非常的丰富,具体可参看Xilinx官方文档。

Programmable Logic(一般简称为PL)即可编程部分(FPGA),该部分的资源随SoC芯片级别高低不同而不同,最低的是ArTIx-7(Zynq-7010和Zynq-7020),最高的是Kintex-7(Zynq-7030和Zynq-7045)。

当然,后续可能SoC中的FPGA会使用更高的Virtex系列,这个就不得而知了。

PS和PL的关系:PS的实质就是一个ARM Cortex A9 MPcore,所以如果我们不使用可编程部分,我们完全可以只使用PS部分。

也就是说,对于ZYNQ芯片,PS部分可以完全独立使用,不依赖PL部分。

PL部分的实质是Xilinx FPGA。

在ZYNQ中,我们可以把PL看成是PS的另一个具有可重配置特点的外设,它可以作为PS部分的一个从设备,受ARM处理器控制。

比如ARM (PS)的串口数量不够时,以太网接口不够时,或者需要视频接口时都可以用PL部分扩展。

当然我们也可以把PL部分看成一个不受ARM处理器控制,与ARM处理器对等的主设备,主动完成与外部芯片、接口的数据交互。

更甚至PL部分也可以作为整个系统的主设备,主动从APU部分的存储器中获取、存储数据,并可控制ARM处理器的运算。

所以,理论上PL部分也可以像PS部分那样独立运行。

但限制是必须使用JTAG接口对PL 部分进行配置。

如果没有JTAG接口,就无法独立运行,因为ZYNQ的PS部分和PL部分都必须依靠PS来完成芯片的初始化配置。

随着嵌入式系统越来越复杂,功能越来越强大,往往在设计中既需要非常灵活的FPGA,。