低复杂度部分传输序列算法及其现场可编程门阵列实现

基于FPGA的串口通信设计与实现

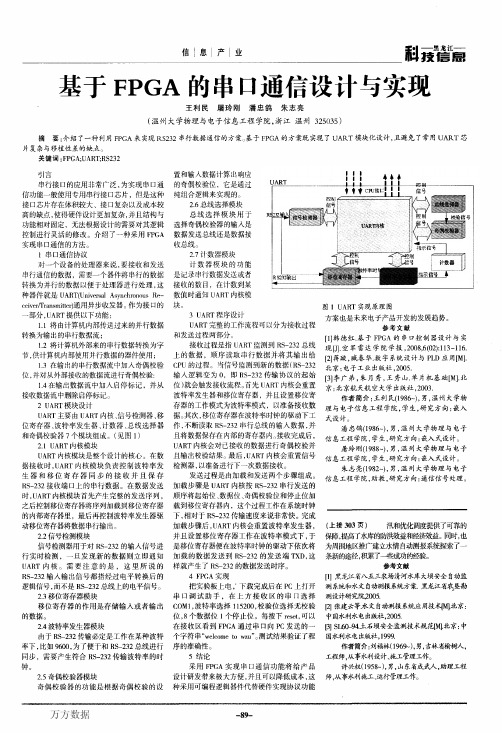

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

论现场可编程门阵列的数字信号处理算法

• 73•闪,使学生见了后相当快地对学习产生强烈的兴趣。

为了让这一次的综合实训能够有所强化,把它的实训时间特地设定为四节课课程连上,让时间得以有好的保障,以使得每一位同学在课上均能够实际动手地参与实践,以免有的学生过于懒散。

教师在整个实训的过程中,给以了科学而且合理的指导,一些内容给学生留下了思考的空间,或是让其可预先地预习,完成知识准备这一必要工作。

对学习较为优秀的学生,对其加以引导,使其对项目中的电路设计予以改进,进行创新以及完善。

譬如说就温度报警器而言,实训中所采纳的是ptc电阻,倘若以ntc电阻来替换之,这一电路会有特别的改变吗?再则是,门磁入侵型式的报警器中具体配给的常闭干簧管,倘若以常开式干簧管来替换它,整个电路又将怎么改变?对于光控灯而言,其电路属于直流供电式的电路,倘若在实际的应用时,将其换作交流供电,又应当如何地设计?要在教学的过程中,全面地考量到学习能力各异的学生们的需求,要能够全面地因材施教,令每一名同学均可在课上有自己的任务。

在期末,安排好7天的课程设计,要求学生们每5至6人组为一个组,一同地完成一综合项目,对于成绩优秀以及成绩一般的学生,要合理地安排,由学习优秀的组长来对任务予以安排,把该综合项目全面完成,譬如说家庭保全这一方案,详细的内容,学生应当依教师所给以的主导来自行决定,最后再由教师依照功能的鞍山度、系统的可靠性以及经济性、实现的难易度来予以评分。

让学生们切实地经历了整个大型项目的整个研发过程,使学生大有收获。

为了对正常的理论以及实践性教学给以必要的补充,我们还借助于业余时间对实验室进行了开放,以作此次实践的第二课堂。

学生借助于学校所供给的慧鱼传感器专用开发包(德国)来展开自主的学习以及实践,学生可以在第二课堂对传感器电路展开具体的设计以及制作、开发。

使学生能够在其学习积极性以及学习主动性上明确提高。

5 结语通过多个学期所展开的教学改革活动以及创新,使学生除了能够在实践的能力上切实提高外,还能够在创新能力上明确提高。

PCI-E 密码卡 SM2 算法侧信道攻击缓解技术设计与研究

近年来,随着市场对高安全性的愈发重视,国家密码管理局颁布了安全三级密码模块相关标准,增加了对物理安全、环境失效性检测、抗侧信道攻击3 个方面的要求。

其中,抗侧信道攻击涉及对国密算法的研究和改造,因而难度较大,而国密算法中,又以非对称算法SM2 的原理和实现最为复杂。

行业内典型设计架构的外设组件互联高速总线(Peripheral Component Interconnect Express,PCI-E)密码卡一般采用多芯片设计架构,即采用一颗专用安全一级算法芯片来负责SM2 算法加速,一颗主控芯片来负责任务调度和敏感数据管理。

该架构下,多数算法专用芯片没有针对侧信道攻击进行加固,且密码卡在进行密码算法运算时,存在关键安全参数在芯片间传输等问题。

因此,研究缓解侧信道攻击的典型架构PCI-E 密码卡的SM2 算法设计,可使得现存的典型架构的PCI-E 密码卡在未来的市场应用上继续发挥作用。

本文首先简要地介绍PCI-E 密码卡的典型设计架构以及架构面临侧信道攻击时可能存在的风险;其次分别从SM2 算法的攻击原理[2]、抗侧信道攻击的针对性改造方法、Inspetor 工具验证3 个方面详细说明缓解技术的设计。

通过本文的介绍,可以填补典型架构的PCI-E密码卡在抗侧信道攻击方面的设计空缺,也可以指导安全二级PCI-E 密码卡的升级改造,使其具有安全三级的实用价值,满足国密检测规范和市场需求。

1典型PCI-E 密码卡设计架构因此,典型PCI-E 密码卡在更高级别安全要求下存在架构上的缺陷,可能导致关键安全参数在跨芯片传输时存在泄露的风险。

2SM2 算法攻击原理分析标准SM2 数字签名算法流程如图3 所示。

在签名过程中,设待签名的消息为M,它的数字签名(r,s),签名者A 的公私钥分别为为长度为v 比特的密码杂凑算法,G 为椭圆曲线的一个基点,其阶为素数,k 为临时私钥。

同时,攻击者也可以通过计时攻击,构建不同比特序列的伪密钥k' 对相同的消息M 进行签名运算,由于点乘运算中的点加运算次数与k 中比特1的位数相关,所以可以通过统计k'p 与kp 运算的时间来推测k 中1 的比特位,进而推断出密钥k。

存储器复杂可编程器件和现场可编程门阵列课件

市场挑战与机遇分析

市场竞争猛烈

随着技术的发展,存储器复杂可编程器件和现场可编程门 阵列市场竞争日益猛烈,企业需要不断提高技术水平和创 新能力,以保持市场竞争力。

市场需求多样化

不同应用领域对存储器复杂可编程器件和现场可编程门阵 列的需求多样化,企业需要针对不同领域提供定制化的解 决方案。

机遇与挑战并存

技术特点比较

支持多种编程语言和开发工具。

现场可编程门阵列(Field Programmable Gate Array)

以可编程逻辑单元为中心,灵活 性强,适用于多种应用场景。

技术特点比较

01

采用查找表(LUT)或可编程逻 辑单元(PLB)实现逻辑功能。

02

支持在系统重构,具有较快的重 构速度。

应用领域比较

存储器复杂可编程 器件和现场可编程 门阵列课件

目 录

• 存储器复杂可编程器件概述 • 存储器复杂可编程器件技术原理 • 现场可编程门阵列技术原理及应用 • 存储器复杂可编程器件与现场可编程门阵列比

较分析 • 存储器复杂可编程器件与现场GUE

存储器复杂可编程器件概述

介绍对存储器复杂可编程器件进行测 试的方法,包括功能测试、性能测试 等。

讨论如何采取措施提高存储器复杂可 编程器件的可靠性,如冗余设计、错 误检测与纠正等。

可靠性分析

阐述如何对存储器复杂可编程器件进 行可靠性分析,包括故障模式与影响 分析(FMEA)、故障树分析(FTA) 等。

03

CATALOGUE

技术不断创新,未来将有更高的性能和更低的功耗。

现场可编程门阵列

随着物联网、人工智能等技术的快速发展,对灵活性和可 重构性的需求不断增加,市场前景广阔。

《循环码教学》课件

在检测过程中,接收端将接收到的码字左移r位,然后除以生成多项式。如果余数为零,则认为传输过程中没有 发生错误;如果余数不为零,则认为传输过程中发生了错误。通过这种方式,循环码可以检测到单个或多个比特 错误。

03

循环码的编码与解码

编码过程

01

02

03

04

05

定义

选择生成多项式

生成多项式与信 息比特序…

编码与解码的实例演示

确定错误的位置为第4位(从右 往左数)。

纠正错误,将第4位由0改为1 ,得到纠正后的码字比特序列 1010101101。

将纠正后的码字比特序列与生 成多项式进行模2除法运算,得 到恢复的信息比特序列 1011001。

04

循环码的性能分析

误码率分析

误码率定义

影响因素

误码率是指接收端接收到的错误码元 与总码元数的比值,是衡量循环码性 能的重要指标。

影响循环码误码率的因素包括信噪比 、码长、编码方式和传输通道特性等 。

误码率计算

通过理论分析和仿真实验,可以计算 出不同条件下循环码的误码率,从而 评估其性能。

抗干扰性能分析

抗干扰能力评估

循环码具有良好的抗干扰性能, 能够有效地抵抗信道中的噪声和

干扰。

干扰抑制机制

循环码通过引入冗余和校验位,利 用编码规则对干扰进行检测和纠正 ,从而降低误码率。

添加校验位

得到码字比特序 列

循环码是一种线性码,其 编码过程是将信息比特序 列与一个生成多项式序列 进行模2除法运算,得到码 字比特序列。

根据给定的码长和纠错能 力,选择合适的生成多项 式。

将生成多项式与信息比特 序列逐位相乘,得到中间 比特序列。

根据中间比特序列和生成 多项式的系数,计算校验 位,并将其添加到中间比 特序列的末尾。

fpga面试题目及答案(3篇)

第1篇1. FPGA是什么?FPGA(现场可编程门阵列)是一种可编程逻辑器件,它可以根据用户的需求进行编程,实现各种数字电路功能。

FPGA具有高灵活性、高集成度、低功耗等优点,广泛应用于通信、工业控制、消费电子等领域。

答案:FPGA是一种可编程逻辑器件,可以根据用户需求进行编程,实现各种数字电路功能。

2. VHDL和Verilog的区别是什么?VHDL和Verilog都是硬件描述语言,用于描述数字电路和系统。

两者在语法和功能上存在一些差异:- VHDL是一种强类型语言,具有丰富的数据类型和操作符,易于编写复杂的数字电路描述。

- Verilog是一种弱类型语言,数据类型较为简单,但具有简洁的语法,便于快速编写代码。

答案:VHDL和Verilog的区别在于数据类型和语法,VHDL是强类型语言,Verilog 是弱类型语言。

3. 什么是FPGA的时钟域交叉问题?FPGA的时钟域交叉问题是指当多个时钟域的信号进行交互时,可能会出现信号竞争、数据丢失等现象,导致系统性能下降或功能失效。

答案:FPGA的时钟域交叉问题是指当多个时钟域的信号进行交互时,可能会出现信号竞争、数据丢失等现象。

4. 如何处理FPGA的时序问题?处理FPGA的时序问题主要包括以下几个方面:- 设计合理的时钟树,确保时钟信号在各个模块之间稳定传播。

- 合理设置时钟分频、倍频等参数,避免时钟抖动。

- 优化模块设计,减少信号路径长度,降低信号传播延迟。

- 进行时序仿真,确保满足设计要求。

答案:处理FPGA的时序问题主要包括设计合理的时钟树、设置时钟参数、优化模块设计和进行时序仿真。

5. FPGA的配置过程是怎样的?FPGA的配置过程主要包括以下几个步骤:- 编写配置文件:使用VHDL或Verilog等硬件描述语言编写配置文件,描述FPGA 内部电路的结构和功能。

- 编译配置文件:使用FPGA厂商提供的编译工具对配置文件进行编译,生成门级网表。

现场可编程门阵列(FPGA)芯片技术简述

现场可编程门阵列(FPGA)芯片技术简述杨海钢1前言从1947年第一支晶体管在贝尔实验室诞生,到1958年德克萨斯仪器公司(TI)研究小组研制出第一块集成电路,直至今天甚大规模集成电路继续遵循著名的摩尔定律(Moore’s law)不断向前发展,人类社会已经从电子时代步入以微纳技术为基础的信息时代,集成电路也已渗透到了我们日常生活的每一方面。

图1第一支晶体管及其发明者图2第一块集成电路现场可编程门阵列(Field Programmable Gate Array,FPGA)是半导体技术发展的重要产物,与CPU、DSP一样,是大规模集成电路最重要的组成部分。

它是一种可编程使用的信号处理器件,用户可通过改变配置信息的方式实现所需逻辑功能,而不必依赖由芯片制造商设计和制造的专用芯片。

在过去短短二十多年里,FPGA已从电子设计的外围器件逐渐演变为数字系统的核心,在互联网、通信、图像处理、汽车电子、航空航天和现代军事装备等诸多领域都得到了广泛的应用。

图3 大规模集成电路芯片FPGA的主要特征有:(1)具有可编程逻辑功能模块结构;(2)具有可编程输入/输出模块结构;(3)具有可编程互连资源结构;(4)具有专用EDA(Electronic Design Automation,电子设计自动化)软件对其进行配置和下载。

与传统数字电路系统相比,FPGA具有可编程、高集成度、高速和高可靠性等优点。

通过配置器件内部的逻辑功能和输入/输出端口,将原来电路板级的设计放在芯片中进行,提高了电路性能,大大减轻了印刷电路板设计的工作量和难度,有效提高了设计的灵活性和效率。

与ASIC(专用集成电路,Application Specific Integrated Circuit)相比,FPGA 开发周期短、前期投资风险小、产品上市速度快、市场适应能力强和硬件升级空间大。

当产品定型和扩大产量后,在FPGA中实现的设计也可迅速定制为ASIC 进行投产。

现场可编程门阵列

的生物医学工程应用

应用于医学信号检测与处理由于现场可编程门阵列性能出众,速度快,因此广泛用于信号采集与处理,可实 现信号采集控制以及信号处理。在便携式心电图仪的设计中,设计者采用现场可编程门阵列Cyclone IC6作为控 制核心,嵌入Nios微处理器,加入DMA以及Memory Controller模块,实现了在心电Holter模式下心电信号采集 与存储。由于现场可编程门阵列芯片可编程,因此具体在实现时,是在现场可编程门阵列中用硬件的方法实现 DMA控制器以及 CF卡读 a写控制器,实现高速数据采集时的导联切换和数据存储控制。并由现场可编程门阵列实 现了数字滤波、信号整形等处理 。

现场可编程门阵列

新型可编程逻辑器件

目录

01

03பைடு நூலகம்的生物医学工程应用

02

的基本结构和工作原 理

04 发展

现代生物医学仪器正在向着微型化、多功能化、系列化等方向发展,系统中的数字部分越来越重要。现场可 编程门阵列是一种新型可编程逻辑器件,性能优良,应用于生物医学工程领域,可显著降低数字系统的开发成本。

在很多情况下,要求生物医学系统具有实时处理信号的能力,如心电信号的实时滤波和压缩处理对于心电图 的分析研究具有很大的意义。信号的实时处理也对器件提出了更高的要求,目前现场可编程门阵列正处于革命性 的数字信号处理技术前沿,可以满足采集量大、运算复杂实时性要求高的应用系统 。

在数字信号实时处理方面,前端的可编程数字信号处理系统一般都是由 ASIC或DSP等构建的,或者是由DSP 和现场可编程门阵列组成主从结构实现,以DSP为主机,完成大量复杂的信号处理算法,而现场可编程门阵列为 从机,主要实现逻辑功能控制。随着现场可编程门阵列技术的进步,现代的现场可编程门阵列系列都提供了支持 以低系统开销、低成本实现高速乘-累加超前进位链的 DSO算法,使得现场可编程门阵列在前端数字信号处理领 域逐渐替代DSP,直接由现场可编程门阵列实现数字信号实时处理以及逻辑功能控制。

并行程序设计导论第四章课后题答案-2024鲜版

分布性

数据分布在多个处理单元中。

8

常见并行计算模型介绍

共享内存模型

所有处理器共享同一物理内存, 通过读写共享内存实现处理器间 的通信和同步。

消息传递模型

处理器拥有自己独立的内存空间 ,通过发送和接收消息实现处理 器间的通信和同步。

数据并行模型

数据被划分为多个子集,每个子 集分配给一个处理器进行处理, 处理器之间无需通信和同步。

02

2024/3/28

03

任务同步

在并行执行任务过程中,需要确保任 务之间的同步和协调,以避免任务之 间的干扰和错误。

13

混合并行编程策略探讨

2024/3/28

混合并行模式

结合数据并行和任务并行的优点,将数据划分和任务划分相结合, 实现更高效的并行处理。

并行算法设计

针对具体问题和应用场景,设计合适的并行算法,以充分利用混合 并行的优势。

并行性能优化

通过分析并行程序的性能瓶颈,采用合适的优化策略,如减少通信 开销、提高缓存利用率等,提高并行程序的执行效率。

14

04 同步与通信机制在并行程 序中的应用

2024/3/28

15

同步机制原理及作用

2024/3/28

同步机制原理

通过设定同步点或同步操作,确保并 行程序中的各个进程或线程在关键点 上达到一致状态,避免数据竞争和结 果不确定性。

重点复习并行程序设计的基本概念、原理和方法,理解并掌握相关术语和定义。通过对比和分析选项,找出 正确答案。

简答题

在理解基本概念的基础上,结合实际应用场景和问题背景,进行深入分析和思考。注意答案的条理性和逻辑 性,尽量用简洁明了的语言进行表述。

编程题

汽车电子工程师招聘笔试题与参考答案

招聘汽车电子工程师笔试题与参考答案一、单项选择题(本大题有10小题,每小题2分,共20分)1、以下哪个部件不属于汽车电子控制单元(ECU)的输入信号?A、车速传感器B、发动机转速传感器C、氧传感器D、轮胎气压传感器答案:D解析:轮胎气压传感器通常不属于ECU的输入信号,因为它主要用于监测车辆轮胎的气压状态,而ECU主要负责控制车辆的发动机、传动系统等电子控制系统。

车速传感器、发动机转速传感器和氧传感器则是ECU常见的输入信号,用于获取车辆运行的重要数据。

2、在汽车电子系统中,下列哪种信号通常采用差分信号传输?A、车速信号B、点火信号C、制动信号D、CAN总线信号答案:D解析:CAN(控制器局域网)总线信号通常采用差分信号传输。

差分信号传输具有抗干扰能力强、信号传输距离远等优点,这使得CAN总线成为汽车电子系统中用于高速数据传输的理想选择。

车速信号、点火信号和制动信号通常使用单端信号传输。

3、在汽车电子控制系统中,ECU(电子控制单元)接收传感器信号并根据预设程序做出决策,下列哪个不是ECU常用的输出设备?A. 发动机喷油器B. 点火模块C. 车速表D. 刹车助力泵【答案】C. 车速表【解析】车速表是一个显示车辆行驶速度的仪表,并不是一个由ECU直接控制的输出设备。

ECU主要控制的是发动机管理系统中的组件如喷油器、点火系统等,以及一些安全系统的执行器,如刹车助力泵。

4、在CAN(控制器局域网络)总线通信协议中,错误帧由哪些部分组成?A. 错误标志和错误界定符B. 错误标志和仲裁场C. 错误界定符和CRC序列D. 错误标志和数据场【答案】A. 错误标志和错误界定符【解析】在CAN总线协议中,错误帧包括错误标志(Error Flag)和错误界定符(Error Delimiter)。

当检测到错误时,任何节点都可以发送错误帧来通知网络上的其他节点。

5、以下哪种传感器在汽车电子领域主要用于测量发动机的转速?A. 光电传感器B. 气压传感器C. 温度传感器D. 磁电传感器答案:D解析:磁电传感器(也称为霍尔传感器)在汽车电子领域广泛应用于测量发动机的转速。

RIS_辅助去蜂窝大规模MIMO_系统低复杂度预编码算法设计

doi:10.3969/j.issn.1003-3114.2024.02.004引用格式:胡亚婷,史恩宇,许柏恺,等.RIS辅助去蜂窝大规模MIMO系统低复杂度预编码算法设计[J].无线电通信技术,2024,50(2):245-252.[HUYating,SHIEnyu,XUBokai,etal.LowComplexityPrecodingAlgorithmDesignforRIS aidedCell freeMassiveMIMOSystems[J].RadioCommunicationsTechnology,2024,50(2):245-252.]RIS辅助去蜂窝大规模MIMO系统低复杂度预编码算法设计胡亚婷,史恩宇,许柏恺,郑家康,章嘉懿,艾 渤(北京交通大学电子信息工程学院,北京100044)摘 要:构思了一种智能超表面(ReconfigurableIntelligentSurface,RIS)辅助去蜂窝大规模多输入多输出(Cell freeMassiveMultiple InputMultiple Output,CFmMIMO)通信系统,提出了一种低复杂度预编码和RIS反射相位交替优化(AlternatingOptimization,AO)算法。

对于传统正则化迫零(RegularizedZeroForcing,RZF)预编码算法复杂度过高的问题,利用共轭梯度(ConjugateGradients,CG)法,提出一种低复杂度的RZF CG预编码算法,将RZF预编码的逆矩阵转换为线性方程组最小化问题,推导算法的残差以更新搜索方向,迭代求解逆矩阵。

以最大化系统用户的总频谱效率为目标,推导了RIS相位闭合表达式,基于统计的信道状态信息提出一种低复杂度的投影梯度上升(ProjectedGradientAscent,PGA)算法。

仿真结果表明,所提的AO算法能有效地提升系统性能,算法复杂度降低了约73.2%。

基于FPGA的HDLC设计实现

基于FPGA的HDLC设计实现李晓娟;黄翌【摘要】根据某雷达的实际要求在FPGA中设计了HDLC协议处理器,并详述了该协议器的设计构想及具体功能模块的实现.该设计采用分块处理的方法使设计简单灵活,适合于系统移植和借用.试验结果证明设计可行有效,可以满足系统要求.同时对主要功能模块进行了仿真和测试,提供了关键结点仿真波形图及部分原代码.【期刊名称】《现代电子技术》【年(卷),期】2007(030)006【总页数】3页(P35-37)【关键词】雷达;HDLC;FPGA;系统移植【作者】李晓娟;黄翌【作者单位】中国电子科技集团第38研究所,安徽,合肥,230031;中国电子科技集团第38研究所,安徽,合肥,230031【正文语种】中文【中图分类】TN951 引言高级数据链路控制规程(High Level Data Link Control,HDLC)是面向比特的同步通信协议,具有差错检测能力强大、高效和同步传输的特点,应用于各种高速数据传输系统中。

实现HDLC通常可采用软件编程或ASIC器件。

软件编程方法功能灵活,通过修改程序就可以适用于不同的HDLC应用。

但程序运行占用处理器资源多,执行速度慢,对信号的时延和同步性不易预测。

软件编程方法一般只能用于个别路数的低速信号处理。

ASIC器件实现方法简单、功能针对性强。

但由于HDLC标准的文本较多,ASIC器件出于专用性的目的难以通用于不同版本,缺乏应用灵活性。

而且,专用于HDLC的ASIC芯片其片内数据存储器(FIFO)容量有限,当需要扩大数据缓存的容量时,只能对ASIC芯片外接存储器或其他电路,使ASIC的简单易用性大大降低。

某雷达要求采用HDLC协议对外传输大量数据,由于系统同时要求在高集成的控制板上完成整机时序、整机控制、信息融合及多类数据传输等功能。

根据实际情况,设计了基于FPGA的HDLC协议控制器。

现场可编程门阵列(Field Programmable Gate Array,FPGA)是采用硬件技术处理信号,又可以通过软件反复编程使用,能够兼顾速度和灵活性,并能并行处理多路信号,实时性能够预测和仿真。

QPSK调制解调器的设计及FPGA实现

QPSK调制解调器的设计及FPGA实现一、本文概述随着无线通信技术的飞速发展,调制解调器作为信息传输的关键部分,其性能对整个通信系统的稳定性和可靠性有着至关重要的影响。

四相相移键控(Quadrature Phase Shift Keying,QPSK)作为一种高效且稳定的调制方式,在无线通信中得到了广泛应用。

本文旨在深入研究QPSK调制解调器的设计,并探讨其在现场可编程门阵列(Field Programmable Gate Array,FPGA)上的实现方法。

本文首先将对QPSK调制解调的基本原理进行详细阐述,包括其信号处理方式、调制解调流程以及关键性能指标。

在此基础上,我们将探讨QPSK调制解调器的设计方法,包括调制器与解调器的结构选择、参数优化等。

同时,我们还将分析影响QPSK调制解调器性能的关键因素,如噪声、失真等,并提出相应的优化策略。

为了实现QPSK调制解调器的硬件化,本文将重点研究其在FPGA 上的实现方法。

我们将首先分析FPGA在数字信号处理方面的优势,然后详细介绍如何在FPGA上设计并实现QPSK调制解调器,包括硬件架构的选择、关键模块的设计与实现、以及资源优化等方面的内容。

我们还将讨论如何在实际应用中测试和优化FPGA实现的QPSK调制解调器,以确保其性能达到最佳状态。

本文旨在深入研究QPSK调制解调器的设计及其在FPGA上的实现方法,为无线通信系统的优化和升级提供理论支持和技术指导。

通过本文的研究,我们期望能够为相关领域的工程师和研究人员提供有益的参考和启示,推动QPSK调制解调技术的发展和应用。

二、QPSK调制原理QPSK,即四相相移键控(Quadrature Phase Shift Keying),是一种数字调制方式,它在每一符号周期内通过改变载波信号的相位来传递信息。

QPSK调制利用四个不同的相位状态来表示两个不同的比特组合,从而实现了更高的数据传输效率。

在QPSK调制中,每个符号通常代表两个比特的信息。

基于现场可编程门阵列战术数据链中自适应轮询接入控制协议的设计与实现

Abstract: In the tactical data link system, the tactical unit may be destroyed at any time to cause the dynamic changes in the network topology, resulting in reduced system service efficiency. In order to solve this problem, an adaptive polling access control protocol ( APACP) is proposed based on the idea of dynamically adjusting the polling order. The system is modeled by the probability generating function method and the embedded Markov chain theory to obtain the analytical solution of average queue length and average polling period of system. Then the MATLAB and field programmable gate array ( FPGA) are used to verify the protocol in simulation. The simulated results show that the APACP protocol can auto鄄 matically adjust the polling order according to the dynamic changes of the tactical data link network topology, which significantly reduces the average queue length and average polling period of system, and

UFMC发射机的低复杂度实现方案设计

信息通信

INFORMATION & COMMUNICATIONS

2019 (Sum. No 197)

UFMC发射机的低复杂度实现方案设计

郭振津,高 凯,李泰立,朱 江,王世练

(国防科技大学电子科学学院,湖南长沙410073)

摘要:通用滤波多载波(Universal Filtered Multi-Carrier,UFMC)^一种新型的多载波技术,是公知的5G多载波体制,结合

本原理叫注意,在文献切中提出了在频域中执行滤波的替代 发射机结构,这样可以显著降低复杂度。用于用户k的特定 多载波符号的时域发射向量y*是子带方式滤波分量的叠加, 其中滤波器长度L和FFT长度为N(为了简单起见,时间索引 k被忽略)。

(1) 对于索引为i的B个子带中的每一个子带,通过IDFT矩

信息通信

Guo Zhenjin, Gao Kai, Li Taili, Zhu Jiang, Wang Shilian (College of Electronic Science, National University of Defense Technology, Changsha 410073, China) Abstract:Universal Filtered Multi-Carrier (UFMC) is a new type of multi-carrier technology. It is a well-known 5G multi-carrier system combined with some advantages of Filtered Orthogonal Frequency Division Multiplexing (F-OFDM) and Filter Band Multi-Carrier (FBMC). However, the classical UFMC transmitter structure has problems such as high computational complexity and difficulty in implementation. This paper aims to optimize the UFMC transmitter structure and reduce the computational complexity of the UFMC transmitter. Key words:UFMC; lightweight; low complexity; transmitter; interpolation structure

低复杂度部分传输序列算法及其现场可编程门阵列实现

低复杂度部分传输序列算法及其现场可编程门阵列实现刘军君;袁著;马腾;周建红【摘要】在传统的部分传输序列(Prs)算法中,计算复杂度高,且需传送边带信息,不利于硬件实现.针对传统PTS算法的这些缺点,设计出一种基于导频信息传送相位旋转因子并结合m序列降低复杂度的PTS算法.其中,m序列作为相位旋转因子,可以降低序列产生硬件实现资源的消耗;导频传送相位旋转因子可以免除边带信息的发送.采用Matlab仿真验证了该算法的可行性,并设计出适合在现场可编程门阵列(FPGA)中实现的正交频分复用( OFDM)系统峰均比抑制模块.通过硬件测试,此模块在降低OFDM系统的复杂度的同时,也能够很好完成峰均比抑制功能.%The conventional Partial Transmit Sequence (PTS) approaches get high computational complexity and need to transmit side information, which is difficult for hardware implementation. Concerning these problems, this paper proposed an algorithm of using m sequences as phase rotation factors and transferring them by pilot information. The m sequence can reduce the complexity of Field Programmable Gate Array ( FPGA) implementation and the pilot transferring phase rotation factor need no side information. The Matlab simulation proves the algorithm is effective. Meanwhile, a Peak-to-Average Power Ratio (PAPR) suppression module was designed to be implemented on FPGA, and the results show that this module not only reduces the complexity of OFDM systems, but also works well in PAPR suppression.【期刊名称】《计算机应用》【年(卷),期】2011(031)012【总页数】4页(P3226-3229)【关键词】正交频分复用;峰均功率比;部分传输序列;m序列;导频【作者】刘军君;袁著;马腾;周建红【作者单位】电子科技大学电子科学技术研究院,成都 610054;电子科技大学电子科学技术研究院,成都 610054;电子科技大学电子科学技术研究院,成都 610054;电子科技大学电子科学技术研究院,成都 610054【正文语种】中文【中图分类】TP3930 引言正交频分复用(OrthogonalFrequencyDivision Multiplexing,OFDM)[1]作为一项多载波调制(Multi-Carrier Modulation,MCM)技术,在无线通信领域得到了广泛的应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LU Jnjn Y A h , e g Z O inh n I u - , U N Z u MA T n , H U J -og u a

( e ac ntu l t n c neadTcnl y U i rt l t ncSinea dTcn l yo hn , hnd i un60 5 , hn ) R s r Istto Ee r i Si c n eh o g , nv syo Ee r i c c n eh oo C ia C eg uSc a 10 4 C ia e h i ef co c e o e i f co e gf h

r d c s t e c mpe i fOF M y tms b tas o k eli AP u p e so . e u e h o lx t o D s s y e , u o w r s w l n P R s p r s in l

R t P P )sprsi ouew s ei e ei l ne nF G ,adter u s hwta ti mouent ny ao( A R u pes nm d l a ds ndt b i o g o mpe t o P A n sl o ths d l o ol me d h e ts h

f co e d n i ei omain a trn e o s n r t .T e Malb smua in p o e h g r h i f c ie d f o h t i lt rv st e a o i m sef t .Me n h l ,a P a ・ — e a e P w r a o l t e v aw i e e k t Av rg o e o

d i1 .74 S ..0 7 2 1 .3 2 o:0 32 / P J 18 .0 0 26 1

低 复 杂 度 部分 传 输序 列 算 法 及 其 现 场 可 编 程 门 阵 列 实现

刘军君 , 袁 著, 腾, 马 周建红

( 电子科技大学 电子科学技术研究 院, 成都 6 0 5 10 4)

( F M) O D 系统峰 均比抑制模 块。通过硬件测试 , 此模块在 降低 O D 系统的复杂度 的同时 , FM 也能够很好 完成峰均 比抑

制 功能。

关键词 : 交频分复 用; 均功率比 ; 正 峰 部分传输序 列; m序 列 ; 导频

中 图分 类 号 : P 9 T33 文献标志码 : A

Lo c m p e iy pa ta r ns i e ue c l o ihm w o lx t ri lta m ts q n e a g rt a e lz to n ed p o r m m a e g t r a nd r aia i n o f l r g a i bl a e a r y

(jf@ 16 cn yf c 2 .o ) c

摘

要: 在传统的部分传输序列 (T ) 法 中, 算复 杂度 高, 需传送 边带信 息 , PS算 计 且 不利 于硬件 实现 。针 对传 统

Hale Waihona Puke 算法的这些缺点 , 设计 出一种基 于导频信 息传送相 位旋 转 因子 并结合 m序 列降低 复杂度 的 P S算 法。其 中, T m 序 列作 为相位旋 转因子, 以降低序列产生硬件 实现资 源的消耗 ; 可 导频传 送相位旋 转 因子 可以免除边 带信 息的发送 。 采 用 M t b仿真 验 证 了该 算 法的 可 行 性 , 设 计 出适 合在 现 场 可编 程 门 阵列 ( P A)中 实现 的 正 交 频 分 复 用 al a 并 FG

Abtat h ovni a P  ̄a Tas t eu ne( T )apoce e hg o p t i a cm l i n edt s c:T ecnet nl a i rnmiSq ec P S p r hsgt i cm ua ol o p xt adne r o l a h tn e y o

r uetecm lx yo i dPormm b aeAry( P A)i pe et i n h i tt nfrn hs oa o e c h o pei fFe rg d t l a al G t r e a FG m lm nao adtepl r s r gpaer tn tn o a ei ti

第 3 卷第 1 1 2期

21年 1 01 2月

计算机应 用

J un lo mp trAp l ain o ra fCo ue pi t s c o

V0 _ No. 2 l3l 1 De . 0l1 c2

文章编号 : 0 —9 8 ( 0 1 1 3 2 0 1 1 0 1 2 1 ) 2— 2 6— 4 0