CPLD选型指南

5分钟学会使用CPLD

5分钟学会使用CPLD当今社会,随着电子行业的发展,大规模集成电路的运用越来越普遍,用CPLD/FPGA 来开发新产品是当前很多实际情况的需求。

在此本人结合到自己的所学,利用业余时间草写了一个简单的使用说明,不要求有丰富经验的大虾来驻足观望,只希望对吾辈刚入门的菜鸟们起到一个抛砖引玉的作用。

由于水平有限,文中错误在所难免,望各位提出宝贵的意见。

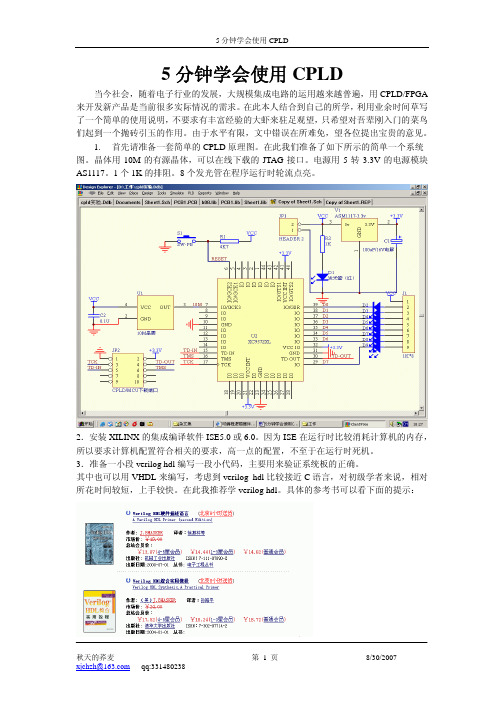

1.首先请准备一套简单的CPLD原理图。

在此我们准备了如下所示的简单一个系统图。

晶体用10M的有源晶体,可以在线下载的JTAG接口。

电源用5转3.3V的电源模块AS1117。

1个1K的排阻。

8个发光管在程序运行时轮流点亮。

2.安装XILINX的集成编译软件ISE5.0或6.0。

因为ISE在运行时比较消耗计算机的内存,所以要求计算机配置符合相关的要求,高一点的配置,不至于在运行时死机。

3.准备一小段verilog hdl编写一段小代码,主要用来验证系统板的正确。

其中也可以用VHDL来编写,考虑到verilog hdl比较接近C语言,对初级学者来说,相对所花时间较短,上手较快。

在此我推荐学verilog hdl。

具体的参考书可以看下面的提示:4.此我们用下面的一小段代码作为范例:其功能是驱动8个发光管轮流点亮,因为是采用了10M频率晶体的边沿触发,所以速度很快,为了使我们肉眼能够看的清楚其工作的流程,我们在里面安放了一个计数器,计数器计每次满一次就点亮一个发光管,依次类推。

其源程序如下:/* 流水灯的Verilog-HDL描述 */module LEDWATER(reset,CLK,LED);input reset, CLK;output [7:0] LED;[7:0]LED;//=8'b11111111;regreg [17:0] buffer;//=0;exchange;regalways@(posedge CLK)if(reset==0) //如果复位了就熄灭全部的灯beginLED=8'b1111_1111;buffer=0;exchange=0;endelsebeginif(exchange==0)begin+1);buffer=(buffer17'b111111111111111111111111)==if(bufferbeginbuffer=0;LED=(LED-1);if(LED==8'b0000_0000)beginLED=8'b1111_1111;exchange=1;endendendif(exchange==1)beginbuffer=(buffer+1);==buffer17'b111111111111111111111111)(ifbeginbuffer=0;LED=(LED>>1);if(LED==8'b00000000)beginLED=8'b1111_1111;exchange=0;endendendendendmodule注意:VERILOG HDL的代码编写风格,begin end 代替了C语言中的大括号{}。

CPLD应用设计平台 调试说明(1)

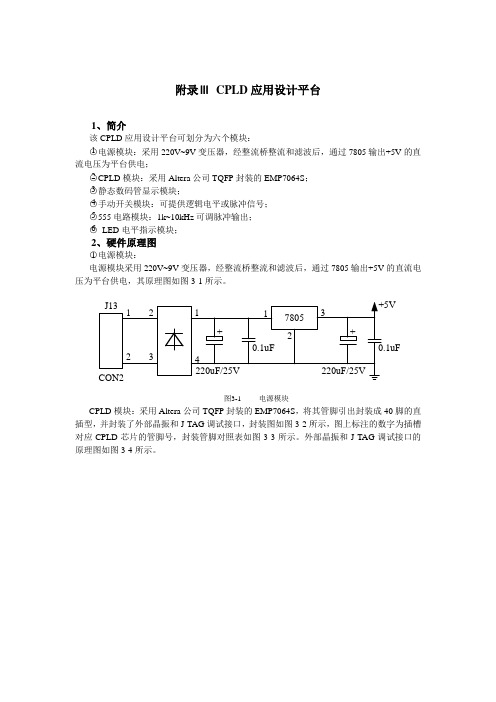

附录ⅢCPLD应用设计平台1、简介该CPLD应用设计平台可划分为六个模块:○1电源模块:采用220V~9V变压器,经整流桥整流和滤波后,通过7805输出+5V的直流电压为平台供电;○2CPLD模块:采用Altera公司TQFP封装的EMP7064S;○3静态数码管显示模块;○4手动开关模块:可提供逻辑电平或脉冲信号;○5555电路模块:1k~10kHz可调脉冲输出;○6LED电平指示模块;2、硬件原理图○1电源模块:电源模块采用220V~9V变压器,经整流桥整流和滤波后,通过7805输出+5V的直流电压为平台供电,其原理图如图3-1所示。

图3-1电源模块CPLD模块:采用Altera公司TQFP封装的EMP7064S,将其管脚引出封装成40脚的直插型,并封装了外部晶振和J-TAG调试接口,封装图如图3-2所示,图上标注的数字为插槽对应CPLD芯片的管脚号,封装管脚对照表如图3-3所示。

外部晶振和J-TAG调试接口的原理图如图3-4所示。

图3-2封装图图3-3封装管脚对照表图3-4外部晶振和J-TAG调试接口○3数码管显示模块,采用共阳极数码管静态显示,用74LS47译码和驱动参阅第4章。

在图3-5中,将最高位的74LS47的/RBI接地,/BI/RBO接到低一位的/RBI引脚,最低位/BI/RBO接高电平,这样级联即可实现灭零显示。

图3-5数码管显示模块○4逻辑开关模块:采用RS触发器74LS279从而消抖并提供逻辑电平或脉冲信号,如图3-6所示,逻辑开关模块如图3-7所示。

图3-6 74LS279管脚图图3-7逻辑开关模块○5555电路模块:555电路模块可实现1k~10kHz 可调脉冲输出,其原理图如图3-8所示。

图中,R A =10k,R B =50k(可调电位器),输出频率范围1k~10kHz 可调脉冲输出。

+V CCR BC 17U +5VU +5V U +5V U +5V 图3-8 555电路模块图3-9 LED 模块○6LED 模块,低电平时点亮,如图3-9所示。

CPLD设计

随着单片机和微型计算机[26]的高速发展,伺服系统逐渐向智能化方向的发展,并伴随外围电路专用集成电路的出现,促进了直流伺服电动机控制技术的显著进步。

当这些技术领域发展到一定程度就构成快响应、高精度的直流伺服系统,进而电力半导体驱动装置逐步取代了电液驱动,比如军用伺服系统。

正因为直流电机容易进行调速,并能在大范围内实现精密的位置控制和速度控制,所以直流伺服系统广泛应用于要求系统性能高的场合;直流伺服电机具有良好的机械性,能在大范围内实现启动、制动、平滑调速和正反转等,在传动领域中仍占有很重要的地位;从传动系统来看,随着直流电机调速系统的不断更新与发展,作为控制系统的核心部件的微机,具有控制、监视、检测、故障诊断与故障处理的多功能电气传动系统正在形成。

由于近年来电力电子技术和微电子的快速发展,使得各种伺服电机控制的智能化功率集成电路系统正朝着模块化、数字化的方向发展[21~25]。

概括的说,伺服系统的发展趋势可以体现在以下几个方面:第一:全数字化。

新的伺服系统是高度集成化的、多功能的控制单元;同一个控制单元中,只要通过软件设置参数,就能改变其性能。

它可以通过接口与外部位置传感器或速度传感器构成高精度全闭环控制系统,也可以使用电机本身配置的传感器构成半闭环控制系统;高度的集成还大大地缩小了整个系统的体积,简化了伺服系统的安装与调试。

第二:智能化。

智能化是工业控制设备的趋势,伺服驱动系统也逐渐向智能化方向发展。

伺服控制单元的智能化主要有以下几个特点:首先它们都具有记忆功能,所有系统的运行参数都保存在伺服单元的内部,这些参数都可以通过通信接口在计算机上修改,使用起来很方便;其次它们都有故障诊断的功能,当系统出现故障时,可以通过计算机把故障的类型以及故障的原因清楚地显示出来,极大地减少了维修与调试的时间;其次,某些伺服系统还具有特定的参数自整定功能,该伺服单元可以通过几次运行,将系统的参数整定出来,进而实现其最优化控制。

《CPLD FPGA设计与应用高级教程》随书光盘第2章 CPLDFPGA硬件结构

图4-2为采用乘积项结构来表示的逻辑示意图。

图5-2为真实的CPLD乘积项结构状态。当逻辑表达式在乘积项中 完成以后,还需要通过可编程触发器以及输出电路把信号输出到 芯片管脚,这样才完成了编程。这一系列的过程都是由软件自动 完成的。

EPROM型:它全称为可擦可编程存取器(Erasable PROM),采 用紫外线擦除,电可编程,但编程电压较高,可多次编程。如果 要重复编程则需要先用紫外线擦除。有时为降低生产成本,在制 造时不加用于紫外线擦除的石英窗口,就只能编程一次,也被称 为OTP器件。 EEPROM型:它是电可擦可编程只读存取器的英文缩写,是采用 浮栅技术生产的可编程存取器。图2-2为浮栅技术的示意图,浮栅 延长区与漏区之间的交叠处有一个厚度约为80埃的绝缘层。当漏 极接地,控制栅极加上足够大的电压的时候,交叠区将产生一个 很强的电场,从而使电子通过这个薄绝缘层到达栅极,这样就使 浮栅带上负电荷,也就是所谓的隧道效应;相反,如果在漏极加 上正电压时,则使浮栅放电。这样通过利用浮栅是否积累有负电 荷来存取二进制数据。因为采用电可擦除,所以速度较EPROM快 。

5.3查找表结构的基本原理 查找表结构的基本原理

查找表(LUT)结构本质上是一个RAM,它类似于一块有4个输入 、16个输出的16bit的存取器(当然也有5输入的结构), 这个存 取器里面储存了所有可能的结果,然后由输入来选择哪个结果应 该输出。当用户通过原理图或者HDL语言来描述一个逻辑电路时 ,PLD/FPGA的综合软件和布局布线软件会自动计算逻辑电路中所 有可能的结果,并且把结果事先写入RAM。这样对输入信号进行 逻辑运算就相当于输入一个地址进行查表,找出并输出地址对应 的内容。如果把输出的D触发器旁路而直接输出,则便实现了组 合逻辑,反之,如果有D触发器则实现了时序逻辑。

第1章cpld学习教程课件

PLD的分类

• CPLD/FPGA不仅受到系统设计者的青睐, 而且在半导体领域中呈现出一支独秀的增 长态势,成为系统级平台设计的首选。随 着PLD向更高速、更高集成度、更强功能 和更灵活的方向发展,使CPLD/FPGA器件 既适用于短研制周期、小批量产品开发, 也可用于大批量产品的样品研制,且项目 开发前期费用低,开发时间短,有利于新 产品占领市场,是目前ASIC设计所使用的 最主要的器件。

第1章cpld学习教程

2023/10/8

第1章cpld学习教程

二、什么叫EDA

. EDA:

电子设计自动化(

Electroni

Design Automation )是电子设计技术和

电子制造技术的核心, EDA技术的发展

和推广应用极大的推动了电子信息行业

的发展。

第1章cpld学习教程

我们认识的EDA技术

Foundation 、PAC) . 5.IC设计 . 6.SOC设计

第1章cpld学习教程

第一节 EDA技术的发展及其未来

. EDA技术是现代电子信息工程领域的一门新技术; . 今天的EDA技术更多的是指芯片内的电子系统设计自动

化,即片上系统(SOC ,System On Chip)设计。 . 在SOC设计过程中,除系统级设计、行为级描述及对功

能的描述以外均可由计算机自动完成,同时设计人员借 助开发软件的帮助,可以将设计过程中的许多细节问题 抛开,而将注意力集中在电子系统的总体开发上。这样 大大减轻了工作人员的工作量,提高了设计效率,减少 了以往复杂的工序,缩短了开发周期,实现了真正意义 上的电子设计自动化。

第1章cpld学习教程

一、EDA技术的发展进程

(完整版)CPLD选型

经过几十年的发展,全球各大开发商和供货商都开发出了多种可编程逻辑器件 . 比较典型的就是Xilinx 公司的FPGA 器件和Altera 公司的CPLD 器件系列,他们开发较早,占有大部分市场?在欧洲用Xilinx 的人多,而Altera 公司占有日本和亚太地区的大部分市场,在美国则是平分秋色。

以上两家公司占有了全球60% 以上的市场份额,他们共同决定了PLD 技术的发展方向。

Lattice 公司在1999 年收购了Vantis ,成为第三大PLD 供应商。

其它供货商还有Actel ,Quicklogic ,Lucent 等等,下面作一简要介绍:Altera 公司是90 年代以后发展最快、最大的可编程逻辑器件供应商之一。

主要产品有: MAX3000/7000 ,FLEX10K ,APEX20K ,ACEX1K ,Stratix ,Cyclone 等;开发软件为MaxplusⅡ和QuartusⅡ。

其中MaxplusⅡ是公认的最成功的PLD 开发平台之一,配合使用Altera 公司提供的免费OEM HDL 综合工具可以达到最高的效率。

公司提供免费试用版或演示版( 当然商业版大都要收费的) ,可以免费从其公司网站上下载MaxplusⅡ(BASELINE 版或学生版) ,或向其代理商索取该软件,然后再从其专业网站上申请注册文件license 进行注册以后便可使用。

这套软件能够满足一般学习和简单开发的要求?Xilinx 公司是FPGA 的发明者,也是全球最大的可编程逻辑器件的供应商之一。

产品种类较全,主要有:XC9500/4000 ,Coolrunner(XPLA3) ,Spartan ,Virtex 等;开发软件为Foundation 和ISE 。

ISE(Integrated System Configuration) 提供从设计输入、仿真、编译、布局布线和下载的全程功能,其最新版本为6 .1 版,支持Xilinx 公司推出的所有最新的FPGA 器件,如Virtex-ⅡPro ,Virtex-Ⅱ,Spartan-ⅡE 和coolrunner-Ⅱ。

脑电波信号采集及传输电路

关键词:脑电波,嵌入式系统,信号采集,无线传输,CPLD

第 II 页

脑电波信号采集及传输电路

THE ACQUISITION AND TRANSMISSION CIRCUIT FOR EEG SIGNAL

ABSTRACT

With the continuous development of industries and the economy, the total number of vehicles all over the world are increasing constantly, which brings a major concern for all countries — the traffic safety. Of all the major causes of traffic accidents, fatigue driving is one of the most prominent. Therefore, the studies of fatigue driving have become an important topic of some related subjects, such as neural science, cognitive science, artificial intelligence, intelligent sensing and sensor, and so on. It not only has a very high theoretical value, but also has important practical significance. Most importantly, it is an urgent task to remedy those drivers who are driving their cars in the state of fatigue, which is a threat to passengers' lives. Also, because of cable transmission, its application is often subject to environment constraints. The common practice to judge the degree of fatigue of the driver is to test his alertness. Compared with other physiological signals, for example the frequency of wink, skin impedance, body temperature and blood pressure, electroencephalogram (EEG) signals reflect the activities of the brain more directly, and have a higher time resolution; therefore, the EEG is currently the most objective physiological indicator in the study of alertness. Although a large number of research institutions are dedicated to related researches, the traditional EEG signal collecting apparatus are wet electrode based wireline equipments. The complicated operation process sets barriers for the wide application. In recent years, with the advancement of micro-electrode technology, there appears a new type of EEG acquisition equipment based on wireless and dry electrode. This approach is not only more efficient, but also can acquire the EEG signal more effectively than the EEG signal acquisition equipment that based on wet electrode. Besides, the new device adopts the wireless transmission mode, which helps the EEG signal acquisition go beyond limitations of the environment, leading the application of the EEG signal to go out of lab, and to be more close to the general users. The project of the Shanghai Committee on Science and Technology — the wireless wearable dry electrode EEG cap and observation system for driver’s alertness — requires a kind of portable wireless wearable dry electrode EEG cap to ensure the convenient and stable acquisition of the EEG signal that can last long during the driving, and ultimately provides accurate in-time monitoring of alertness and early warning techniques for other areas such as aerospace, aviation and automotive. This issue is the project's sub-topic – the embedded subsystem for EEG signal wireless transmission. It is required to design embedded multi-channel high-resolution EEG signal processing and transmission circuits with low power consumption, high reliability and high

CPLDFPGA实用教程

PROM PLA

改

进

器

的

件

和

CPLD FPGA GAL

PLA

器 件

器 件

器 件器

器 件

件

70年代

80年代

内嵌复杂 功能模块 的SoPC

90年代

学习方法

一、掌握好数字逻辑电路技术 二、理论联系实践,多动手

EDA技术与VHDL实用教程

21

在广义的EDA技术中,CAA技术和 PCB-CAD技术不具备逻辑综合和逻辑适配 的功能,因此它并不能称为真正意义上的 EDA技术。

4

狭义的EDA技术,就是以大规模可编 程逻辑器件为设计载体,以硬件描述语言 为系统逻辑描述的主要表达方式,以计算 机、大规模可编程逻辑器件的开发软件及 实验开发系统为设计开发工具的EDA技 术。

CPLD/FPGA知识概述

1

主要术语

2 CPLD/FPGA与传统设计方法比较

3

发展历程

4

主要学习方法

1

主要术语:

EDA:电子设计自动化Electronic design automation PLD:可编程逻辑器件 Programmable logical device CPLD:复杂可编程逻辑器件 complex programmable logical device FPGA:现场可编程门阵列 field programmable gates array ISP:在系统可编程 in system programmable ASIC:专用集成电路 Application specific integrated circuits SOC:片上系统 System On Chip SOPC:可编程片上系统 System On Chip IP:经过测试和优化的功能复杂的电路 Intellectual

CPLD及FPGA选型

MAX7000 I/O支持

器件

核

输入电压

输出电压

高级I/O支持

电

压

SSTL 66bit

1.8V 2.5V 3.3V 5.0V 1.8V 2.5V 3.3V 5.0V GTL+

2/3 66MHzPCI

MAX7000S 5.0V

∨∨

∨∨

MAX7000AE 3.3V

∨∨∨

∨∨

MAX7000B 2.5V ∨ ∨ ∨

Cyclone器件的特性

特性 成本优化的架构 嵌入式存储器 外部存储器接口 支持LVDS I/O

支持单端I/O

时钟管理电路 接口和协议

说

明

具有多达20060个逻辑单元,容量是以往低成本FPGA的四倍,可用来实现复杂的应用。

Cyclone器件中M4K存储块提供288kbit存储容量,能够被配置来支持多种操作模式,包

括RAM、ROM、FIFO及单口和双口模式。

具有高级外部存储器接口,允许设计者将外部单数据率(SDR)SDRAM,双数据率(DDR)、

84、84、120、 5、7、10

164、164

120、176、212 7、10、12

ALTERA器件封装

PLCC :塑封J引线芯片封装 TQFP :薄塑封四角扁平封装 PQFP :塑封四角扁平封装 RQFP :高效四角扁平封装 BGA :球栅阵列 FBGA : 1.0毫米间距球栅阵列 UBGA :0.8毫米间距球栅阵列

44-PinTQFP,49-PinBGA,100-PinTQFP, 100-PinBGA

84-Pin PLCC,100-Pin PQFP/TQFP,160-Pin PQFP 84-Pin PLCC,100-Pin TQFP/BGA,144-Pin PQFP,256-Pin BGA 208-Pin PQFP/RQFP 100-Pin TQFP/BGA,144-Pin TQFP,208-Pin PQFP,256-Pin BGA 144-Pin TQFP,208-Pin PQFP,256-Pin BGA

cpld和fpga的选用标准

cpld和fpga的选用标准CPLD(可编程逻辑器件)和FPGA(现场可编程门阵列)是两种可编程逻辑器件,它们在数字电路设计中有不同的特点和应用场景。

在选择使用 CPLD 还是 FPGA 时,可以考虑以下一些标准:1. 规模和复杂性:• CPLD 通常适用于相对较小且不太复杂的数字逻辑设计。

它们通常有较少的逻辑单元和资源。

• FPGA 则更适用于大规模、复杂的数字电路设计,因为它们提供了更多的逻辑单元、存储器和其他资源。

2. 功耗:• CPLD 通常具有较低的功耗,特别是在低复杂性设计的情况下。

• FPGA 的功耗可能较高,尤其是在需要大量资源和高性能的设计中。

3. 速度和性能:• FPGA 在处理速度和性能方面通常更优越。

它们提供更多的逻辑资源和硬件资源,适用于高性能的应用。

• CPLD 虽然速度也很快,但相对 FPGA 而言在处理复杂逻辑时可能性能较低。

4. 设计周期和原型开发:• CPLD 通常具有较短的设计周期,因为它们不需要复杂的编译过程,并且适用于原型开发和快速验证。

• FPGA 在设计和编译方面可能需要更多的时间,适用于更复杂的设计和大规模项目。

5. 成本:• CPLD 通常相对较便宜,适用于低成本设计。

• FPGA 的成本可能较高,适用于对性能和资源要求较高的应用。

6. 适用场景:• CPLD 适用于控制逻辑、序列逻辑和简单的数字处理任务。

• FPGA 适用于图像处理、信号处理、通信系统、高级控制系统等复杂应用。

选择CPLD 还是FPGA 取决于具体的项目需求和约束。

在制定选用标准时,需综合考虑设计的规模、复杂性、功耗、性能、设计周期、成本和适用场景等因素。

经典平台CPLD接口说明书

博创科技经典平台CPLD接口说明2008-7-10经典平台上有两片CPLD,第1片控制网卡、IDE的逻辑、串口选择、CF卡逻辑等。

第2片控制音频和触摸屏选择、LED矩阵和数码管等。

对软件而言,两片CPLD可以看作同一外设,有的寄存器分开放在两片CPLD内的。

一、网卡、IDE、复位等逻辑和原来经典平台一样,对软件透明,无需设置。

1、网卡1和网卡2,对于270和2410核心板,都在Bank2上。

当nGCS2为0时,A2为0则选中网卡1,A2为1则选中网卡2。

对于每个网卡芯片,A1为0访问INDEX端口,A1为1访问DATA端口。

物理地址:2410核心板:网卡1:INDEX:0x1000 0000 DATA::0x1000 0002网卡2:INDEX:0x1000 0004 DATA::0x1000 0006 270核心板:网卡1:INDEX:0x0800 0000 DATA::0x0800 0002网卡2:INDEX:0x0800 0004 DATA::0x0800 00062、IDE接口和其他一些资源占用同一个Bank,2410核心板是Bank1,270核心板是Bank4。

当A8为0时选中IDE接口,A8为1时选中其他资源,后面逐步说明。

物理地址范围:2410核心板:IDE接口:0x0800 0000---0x0800 00FF其他设备:0x0800 0100---0x0800 011E270核心板: IDE接口:0x1000 0000---0x1000 00FF其他设备:0x1000 0100---0x1000 011E3、复位逻辑仅提供各复位电平之间的逻辑与关系。

二、CPLD内部包括核心板选择寄存器,并据此对音频和触摸屏等资源进行选择,以及控制串口选择的寄存器,数码管和矩阵LED寄存器,还有270核心板下的CF卡相关寄存器。

这些寄存器都和IDE接口共享同一个Bank,2410核心板是Bank1,270核心板是Bank4。

SSMEC 1K CPLD设计入门

HDL文件 .v

文本编辑器

原理图文件 .sch

ispLever

功能仿真

仿真验证逻辑设计功能是否正确: 1. 创建测试平台源文件(testbench) 2. 仿真

testbench .v

文本编辑器

仿真

Modelsim

逻辑实现

逻辑实现流程: 1. 分配管脚 2. 设置约束 3. 自动布局布线 4. 查看布局布线结果报告 5. 静态时序分析

安 装 modelsim

ModelSim SE 6.1f 安装 安装步骤: 1.正常安装软件(Setup.exe),选择Full Product 2.在弹出对话框中,单击YES,安装key Driver 3.将license复制到c:\flexlm目录下 4.设置系统环境变量,添加lm_license_file变量,其值

IO单元可配置为输入、输出、双向IO。

时钟网络构架

1024 1032 1048

1016

逻辑设计示例

逻辑设计示例功能要求

设计一个逻辑:使数码管计数显示0、1、2 …7的数 字。 要求: 1. 复位后,数码管显示数字0。 2. 可以初始化数码管计数值。 3. 可以开始和停止数码管计数。

设计方法

按键

安装license 1.把license.dat复制到c:\flexlm中去 2.设置环境变量lm_license_file=

c:\flexlm\license.dat

安 装 ispVM 软 件

安装ispLever软件时,默认会安装ispVM软件,不需 要单独安装

软件使用流程

打 开 ispLever 界 面

SM 1K CPLD 特 性

2. 高性能E2CMOS芯片工艺 最大时钟速度60MHz TTL接口电平 5V电源 E2CMOS编程技术,编程次数10000次,保 持20年 100%的生产测试

第5章 CPLD基础

图5.10 输入输出块框图

2.高速接续交换阵 (Fast Connect Switch Matrix) 高速接续交换阵功能就是对功能块的输入信号实施控制。该接续阵连接所有 的I/O端口信号和功能块的输出信号,由控制程序指定输入功能块的信号,功能 块的输出信号也可由AND逻辑缓冲器接入功能块的输入端。该设计使得功能块的 输入信号选择更灵活。另外是否使用缓冲器可由开发软件自动选择,据图见图 5.11所示。

图5.5 PIA信号布线到LAB的方式

5.I/O控制块 I/O控制块允许每个I/O引脚单独地配置成输入/输出和双向工作方式。所有I/O引脚都有 一个三态缓冲器,它能由全局输出使能信号中的一个控制,或者把使能端直接连接到地 (GND)或电源(VCC)上。MAX7000系列器件的I/O控制框图如图5.6所示。MAX7000 器件有6个全局输出使能信号,它们可以由以下信号驱动:两个输出使能信号、一个I/O引 脚的集合、一个I/O宏单元的集合,或者是它“反相”后的信号。 当三态缓冲器的控制端接地(GND)时,其输出为高阻态,而且I/O引脚可作为专用输 入引脚。当三态缓冲器的控制端接电源(VCC)时,输出使能有效。 MAX7000结构提供了双I/O反馈,且宏单元和引脚的反馈是相互独立的。当I/O引脚配置 成输入时,有关的宏单元可以用于隐含逻辑。

图5.4 并联扩展项馈送方式

4.可编程连线阵列PIA 通过可编程连线阵列可将各LAB相互连接构成所需的逻辑。这个全局总线是可编程的 通道,它能把器件中任何信号源连到其目的地。所有MAX7000系列器件的专用输入、 I/O引脚和宏单元输出均馈送到PIA,PIA可把这些信号送到整个器件内的各个地方。 只有每个LAB所需的信号才真正给它布置从PIA到该LAB的连线,如图5.5是PIA信号布 线到LAB的方式。

第6章CPLD配置讲稿

第6章CPLD配置讲稿

用微处理器对FPGA进行PPS方式配置。

l 在PPS方式配置(被动并行同步配置)方式中,从PC机的并口发出编程数 据, nCONFIG引脚被智能主机(如单片机)所控制。

第6章CPLD配置讲稿

JTAG接口

l JTAG接口使用TDI、TDO、TCK、TMS四个管脚。 其中:

l TDI:串行数据输入端, l TDO:串行数据输出端, l TCLK:串行时钟, l TMS:JTAG状态机模式控制端。 l TDI、TDO、TMS的数据在TCLK时钟的配合下,将

数据串行移位到CPLD内部JTAG移位寄存器中。

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

第6章CPLD配置讲稿

被动串行配置(PS)方式

l 在被动串行配置(PS)方式中,从PC机的串口发出 编程数据,由BitBlaster下载电缆或接口微处理器产 生一个由低到高的跳变送到nCONFIG引脚,然后微 处理器或编程硬件将配置数据送到DATA0引脚,该 数据被琐存,直至CONF_DONE变为高电平。它先 将每字节的最低位LSB送到FPGA器件。

2)被动配置方式。 在这种配置方式下,由外部CPU或控制器(如单片机) 控制配置的过程。

第6章CPLD配置讲稿

FLEXl0K/ EP1K系列器件有五种配置方式:

第6章CPLD配置讲稿

CPLD和FPGA的选用 - 电子技术

CPLD和FPGA的选用 - 电子技术从以下几个方面进行选择 :1.逻辑单元CPLD中的逻辑单元是大单元,通常其变量数约20~28个。

由于这样的单元功能强大,一般的逻辑在单元内均可实现,因而其互连关系简单,一般通过集总总线即可实现。

电路的延时通常在数纳秒至十数纳秒。

与同样集成规模的FPGA芯片相比内部触发器的数量较少。

大单元的CPLD较适合逻辑型系统,如控制器等,这种系统逻辑复杂,输入变量多,但对触发器的需求量相对较少。

FPGA逻辑单元是小单元,其输入变量数通常只有几个,因而采用查表结构(即PROM形式),每单元只有1~2个触发器。

这样的工艺结构占用芯片面积小,速度高,每块芯片上能集成的单元数多,但逻辑单元的功能较弱。

如欲实现一个较复杂的逻辑功能,需要几个这样的单元组合才能完成。

电路的延时时间不定,互连关系也较复杂。

小单元的FPGA较适合数据型系统,这种系统所需的触发器数多,但逻辑相对简单。

2.内部互连资源与连线结构FPGA单元小、互连关系复杂,所以使用的互连方式较多, FPGA的分段式互连结构是利用不同长度的几种金属线通过旁路晶体管或反熔丝的连接,把各个功能单元连接起来;有单长线、双长线、长线等方式。

所以FPGA在使用时,除了逻辑设计外,还要进行延时设计。

通常需经数次设计,方可找出最佳方案。

CPLD单元大。

CPLD不采用分段互连方式,它的连续式互连结构是利用具有同样长度的一些金属线实现功能单元之间的互连,即使用的是集总总线,所以其总线上任意一对输入端与输出端之间的延时相等,且是可预测的,产品可以给出引脚到引脚的最大延迟时间。

此外,CPLD还具有很宽的输入结构,适合于实现高级的有限状态机。

CPLD的主要缺点是功耗大,15000门以上的CPLD的功耗要高于FPGA、门阵列和分立器件。

3.编程工艺CPLD属于只读(ROM)型编程,可以反复编程,但它们一经编程,片内逻辑就被固定,如果数据改变就要进行重新擦写。

MaxplusII软件CPLD电路设计入门

基于CPLD扩展的单片机系统设计与应用(连载文章)基于Max+PlusII软件CPLD电路设计入门随着电子技术的不断发展,大规模集成电路的运用越来越普遍,用CPLD/FPGA来开发新产品是电子技术发展必然趋势。

在这个专题,我们将介绍基于Max+plusII软件平台的CPLD开发过程。

Max+plusII是Altera公司推出的的第三代PLD开发系统(Altera第四代PLD开发系统被称为:QuartusII,主要用于设计新器件和大规模CPLD/FPGA)。

使用Max+plusII的设计者不需精通器件内部的复杂结构。

设计者可以用自己熟悉的设计工具(如原理图输入或硬件描述语言)建立设计,Max+plusII把这些设计自动转换成最终所需的格式。

特别是在原理图输入方面,Max+plusII被公认为是最易使用,人机界面最友善的PLD开发软件,特别适合初学者使用。

在Max+plusII环境可以完成电路设计输入、电路的编译与适配、电路仿真与时序分析、管脚分配与定位到器件编程下载全过程。

电路设计输入一般有原理图输入方式和硬件描述语言输入方式,也可以采用原理图和硬件描述语言混合输入,对于初学者,学会一门硬件描述语言不是一朝一夕的事,但对于原理图输入应该是快速易学的,只要掌握软件使用技巧,直接将电路图绘制出来,添加输入输出引脚即可。

在单片机扩展电路当中,使用CPLD更是灵活自如。

下面将通过一个设计任务实现的完整过程来学习CPLD开发过程。

一、设计任务ADC0809实验成为学单片机必上的一课,图1是单片机与ADC0809经典接口电路,该电路来自早期《单片机原理及实用技术》一书,从图中可以看出,单片机与ADC0809之间有4种分离元器件,分别非门是7404、D触发器7474、锁存器74373、或非门7402。

图1 经典单片机与ADC0809接口电路这里请大家跟我一起学习用CPLD替代分离逻辑器件,实现单片机与ADC0809的接口,电路如图2所示。

Xilinx CPLD 在线编程参考指南

Xilinx CPLD 在线编程参考指南广州致远电子股份有限公司目录1. Xilinx CPLD简介 (1)2. AK100Pro-4P简介 (2)3. 准备条件 (4)3.1准备待烧写板 (4)3.2安装KFlashPro软件 (4)3.3连接待烧写板至AK100Pro-4P (5)4. 基本烧写 (7)4.1创建工程 (7)4.2参数配置 (7)4.2.1硬件选择 (7)4.2.2主要设置 (8)4.2.3程序烧写 (9)4.3烧写配置 (10)4.4进行烧写 (11)5. 高级烧写 (12)5.1量产烧写配置 (13)5.2加密与解密 (14)5.2.1加密 (14)5.2.2解密 (15)6. 技术支持 (16)7. 订购信息 (17)1. Xilinx CPLD简介Xilinx的CPLD有CoolRunner TM-Ⅱ家族和XC9500XL家族的芯片。

被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中。

CoolRunner TM-Ⅱ家族的芯片具有小封装、高性能、低功耗的特点。

采用0.18微米制造工艺,核心电压1.8V,IO口兼容1.5V、1.8V、2.5V和3.3V操作。

Xilinx CoolRunner TM-ⅡCPLD器件提供高运算速度,易于与XC9500/XL/XV系列CPLD联合使用。

在单一CPLD 里,消耗极低的功率可实现XPLA3TM系列多功能性。

这一点意味着通过系统内可编程功能使得原来同一部分可被用作数据高速通信、计算系统以及使得便携式产品达到其领先技术水平。

功率的低功耗和运算的高速度结合于同一器件中,使得运用更容易、花费更有效。

已经获得Xilinx专利的FZP(Fast Zero Power TM)结构提供固有的低功率性能,而不需要任何专门的设计措施。

Clocking技术和其他的能量节省特性延伸了用户的功率预算。

XC9500XL家族的芯片采用闪存储技术(FastFLASH),符合PCI总线规范。

cpld整理

(一)数字电子系统:简称为数字系统。

是可以完成某种(或多种)特定的、功能不单一的一种电子系统。

一般应包含某种控制器及受控单元。

数字器件:即数字ic芯片。

是构成数字系统的基本部件,是数字系统的“元素”或“细胞”主要区别:看其是否具有控制和受控单元。

soc 和sopc:在单一半导体芯片上设计、制造百万个以上的晶体管,这种高集成度的ic芯片具备一个数字系统的全部特性与功能,即为“单片系统”(soc system on a chip)和sopc单片系统集成度高、低功耗、功能强大、工作可靠构建数字系统的方法以及他们的特点:1.标准化的中、小规模数字集成电路特点:简单易用、价格低廉,应用广泛,集成度较低,功能受限。

系统构成复杂、功耗高、可靠性偏低。

2.基于lsi或vlsi的微处理器特点cpu、mcu、dsp依靠执行指令(软件)可以方便的实现几乎任意的数字逻辑功能,其应用灵活性极强。

3.基于lsi或vlsi的专用集成电路asic asic(application specific integrated circuits )是一种为完成某种特定的电路功能而专门设计、生产的ic器件。

特点:需要专门设计/定制,大规模集成。

性能强、功耗低、工作可靠性高、保密性高、大批量应用时成本也较低;功能专一且不能改变。

总之,使用asic进行数字系统设计需要较高的开发费用、设计与制造周期也较长。

所以asic只适合在大批量工业应用的场合中使用。

4.基于lsi/vlsi的可编程逻辑器件pld特点:由用户自定义器件的功能、大规模集成。

设计周期短、设计风险低、应用灵活、系统功能强大、功耗低用pld来进行数字系统的开发与设计已成为现代电子设计的一种方向与潮流。

可编程逻辑器件pld(什么是pld、为什么会发展pld、pld器件的优点、pld的发展趋势);可编程逻辑器件(pld--programmable logic device)是一种通用的电子器件,其功能不是固定不变的,而是可根据用户的需要而进行改变,即:可通过编程设计的方法来定义器件的逻辑功能. 出现的背景原因(1)传统设计方法的局限(不宜设计复杂数字系统)⑵中小规模器件:面积大,芯片多,功耗大,可靠性低⑶微处理器系统:需要一定的数字接口器件相配合才能有效工作;工作速度相对较慢,在一些需要高速、实时工作的应用场合受到一定的限制。

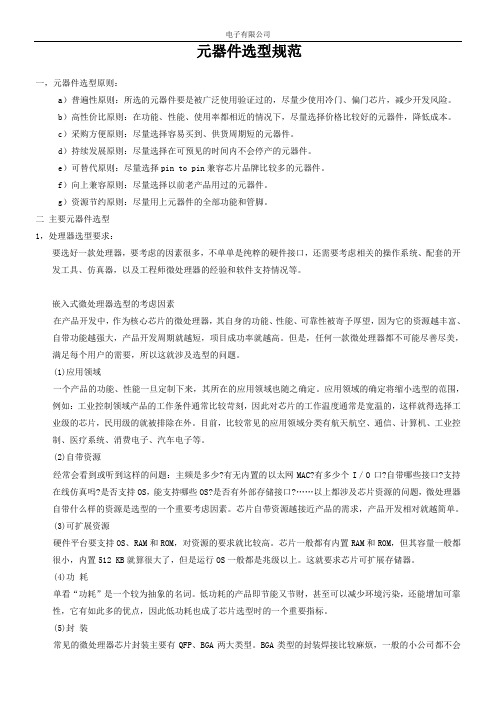

电子元器件选型规范

元器件选型规范一,元器件选型原则:a)普遍性原则:所选的元器件要是被广泛使用验证过的,尽量少使用冷门、偏门芯片,减少开发风险。

b)高性价比原则:在功能、性能、使用率都相近的情况下,尽量选择价格比较好的元器件,降低成本。

c)采购方便原则:尽量选择容易买到、供货周期短的元器件。

d)持续发展原则:尽量选择在可预见的时间内不会停产的元器件。

e)可替代原则:尽量选择pin to pin兼容芯片品牌比较多的元器件。

f)向上兼容原则:尽量选择以前老产品用过的元器件。

g)资源节约原则:尽量用上元器件的全部功能和管脚。

二主要元器件选型1,处理器选型要求:要选好一款处理器,要考虑的因素很多,不单单是纯粹的硬件接口,还需要考虑相关的操作系统、配套的开发工具、仿真器,以及工程师微处理器的经验和软件支持情况等。

嵌入式微处理器选型的考虑因素在产品开发中,作为核心芯片的微处理器,其自身的功能、性能、可靠性被寄予厚望,因为它的资源越丰富、自带功能越强大,产品开发周期就越短,项目成功率就越高。

但是,任何一款微处理器都不可能尽善尽美,满足每个用户的需要,所以这就涉及选型的问题。

(1)应用领域一个产品的功能、性能一旦定制下来,其所在的应用领域也随之确定。

应用领域的确定将缩小选型的范围,例如:工业控制领域产品的工作条件通常比较苛刻,因此对芯片的工作温度通常是宽温的,这样就得选择工业级的芯片,民用级的就被排除在外。

目前,比较常见的应用领域分类有航天航空、通信、计算机、工业控制、医疗系统、消费电子、汽车电子等。

(2)自带资源经常会看到或听到这样的问题:主频是多少?有无内置的以太网MAC?有多少个I/O口?自带哪些接口?支持在线仿真吗?是否支持OS,能支持哪些OS?是否有外部存储接口?……以上都涉及芯片资源的问题,微处理器自带什么样的资源是选型的一个重要考虑因素。

芯片自带资源越接近产品的需求,产品开发相对就越简单。

(3)可扩展资源硬件平台要支持OS、RAM和ROM,对资源的要求就比较高。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BGA Packages (BG) – wire-bond standard BGA (1.27 mm ball spacing) 256 352 27 x 27 mm 35.0 x 35.0 mm 192 166 192

-7 -10 -15 -20 NA -10 -15 -10 -15 -20 -15 -20 NA NA NA

18 18 18 18

FBGA Packages (FG) – wire-bond Fine-line BGA (1.0 mm ball spacing) 256 17 x 17 mm 192 192

160 208

XC9572

108 133 133 166 168

VQFP Packages (VQ) – very thin TQFP (0.5 mm lead spacing)

117 2 192 4

44 64

12.0 x 12.0 mm 12.0 x 12.0 mm3434源自34 3634 52

34

XC9500 Family – 5 Volt

XC9536 XC9572 XC95108 XC95144 XC95216 XC95288 800 1,600 2,400 3,200 4,800 6,400 36 72 108 144 216 288 90 90 90 90 90 90 5 5 5 5 5 5 5 5 5 5 5 5 36 72 108 133 166 192 10 10 10 10 10 10 -5 -6 -10 -15 -7 -10 -15 -7 -10 -15 -20 -7 -10 -15 -10 -15 -20 -10 -15 -20 -7 -10 -15 -10 -15 -15 -15 3 3 3 3 3 3 18 18

XC2C512 XCR3512XL

XC2C32A

XC2C64A

XC2C128

XC2C256

XC2C384

XC2C512

Product Selection Matrix – 9500 Series

I/O Features Min. Pin-to-pin Logic Delay (ns)

Package Options and User I/O

CoolRunner XPLA3 Family – 3.3 Volt

XCR3032XL XCR3064XL XCR3128XL XCR3256XL XCR3384XL XCR3512XL 750 1,500 3,000 6,000 9,000 12,000 32 64 128 256 384 512 48 48 48 48 48 48 3.3/5 3.3/5 3.3/5 3.3/5 3.3/5 3.3/5 3.3 3.3 3.3 3.3 3.3 3.3 36 68 108 164 220 260 5 6 6 7.5 7.5 7.5 -5 -7 -10 -6 -7 -10 -6 -7 -10 -7 -10 -12 -7 -10 -12 -7 -10 -12 -7 -10 -7 -10 -7 -10 -10 -12 -10 -12 -10 -12 -10 -10 -10 -12 -12 -12 4 4 4 4 4 4 16 16 16 16 16 16

Product Terms per Macrocell

Output Voltage Compatible

XCR3032XL

XCR3064XL

XCR3128XL

XCR3256XL

XCR3384XL

Commercial Speed Grades (fastest to slowest)

Input Voltage Compatible

CoolRunner-II Family – 1.8 Volt

XC2C32A XC2C64A XC2C128 XC2C256 XC2C384 XC2C512 750 1,500 3,000 6,000 9,000 12,000 32 64 128 256 384 512 56 56 56 56 56 56 1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 1.5/1.8/2.5/3.3 33 1.5/1.8/2.5/3.3 64 2 2 3.8 4.6 5.7 5.7 7.1 7.1 -4 -6 -5 -7 -6 -7 -6 -7 -7 -10 -7 -10 -6 -7 -7 -7 -10 -10 -6 -7 -7 -7 -10 -10 3 3 3 3 3 3 16 16 16 16 16 16

Speed

Clocking

XC9500XV XC95144XV XC95288XV XC9536XV XC9572XV

Commercial Speed Grades (fastest to slowest) Product Term Clocks per Function Block

XC9500XL XC95144XL XC95288XL XC9536XL XC9572XL

XC9500XL Family – 3.3 Volt

XC9536XL XC9572XL XC95144XL XC95288XL 800 1,600 3,200 6,400 36 72 144 288 90 90 90 90 2.5/3.3/5 2.5/3.3/5 2.5/3.3/5 2.5/3.3/5 2.5/3.3 2.5/3.3 2.5/3.3 2.5/3.3 36 72 117 192 5 5 5 6 -5 -7 -10 -5 -7 -10 -5 -7 -10 -6 -7 -10 -7 -10 -7 -10 -7 -10 -7 -10 -10 -10 NA NA 3 3 3 3 18 18 18 18

Product Term Clocks per Function Block

Industrial Speed Grades (fastest to slowest)

IQ Speed Grade

Pins

Area1

Global Clocks

System Gates

Maximum I/O

I/O Banking

Pins

Area1

IQ Speed Grade

Global Clocks

System Gates

Maximum I/O

PLCC Packages (PC) – wire-bond plastic chip carrier (1.27 mm lead spacing) 44 84 17.5 x 17.5 mm 30.2 x 30.2 mm 34 34 34 34 34 69 69

14

Product Selection Matrix – CoolRunner ™ Series

I/O Features Speed Clocking

Package Options and User I/O

Min. Pin-to-pin Logic Delay (ns)

CoolRunner-II

CoolRunner XPLA3

XC9500XV Family – 2.5 Volt

XC9536XV XC9572XV XC95144XV XC95288XV 800 1,600 3,200 6,400 36 72 144 288 90 90 90 90 2.5/3.3 2.5/3.3 2.5/3.3 2.5/3.3 1.8/2.5/3.3 1.8/2.5/3.3 1.8/2.5/3.3 1.8/2.5/3.3 36 72 1 1 5 5 5 6 -5 -7 -5 -7 -5 -7 -6 -7 -10 -7 -7 -7 -7 -10 NA NA NA NA 3 3 3 3 18 18 18 18

XC9500 XC95108 XC95144 XC95216 XC95288 XC9536

34

Product Terms per Macrocell

Output Voltage Compatible

Input Voltage Compatible

Industrial Speed Grades (fastest to slowest)

TQFP Packages (TQ) – thin QFP (0.5 mm lead spacing) 100 144 16.0 x 16.0 mm 22.0 x 22.0 mm 72 81 117 117 72 81 117 117 72 81 81

Chip Scale Packages (CS) – wire-bond chip-scale BGA (0.8 mm ball spacing) 48 144 280 7 x 7 mm 12 x 12 mm 16 x 16 mm 36 38 117 192 36 38 117 192 34

I/O Banking

Macrocells

PQFP Packages (PQ) – wire-bond plastic QFP (0.5 mm lead spacing) 100 23.3 x 17.2 mm 31.2 x 31.2 mm 30.6 x 30.6 mm 168 168 72 81 81

* JTAG pins and port enable are not pin compatible in this package for this member of the family. Note 1: Area dimensions for lead-frame products are inclusive of the leads.

1.5/1.8/2.5/3.3 100 2 1.5/1.8/2.5/3.3 184 2 1.5/1.8/2.5/3.3 240 4 1.5/1.8/2.5/3.3 270 4