学习vivadoHLS第7章例程中文版

学习VivadoHLS第4章 例程中文版

学习Vivado第4章lab1——接口综合概述接口综合是将RTL接口添加到C设计的过程。

另外还把物理接口添加到RTL设计中,接口综合包括了相关联的I/O 协议,容许数据通过接口传输并自动与内部优化的逻辑同步。

本教程由4实验练习组成涵盖的主要功能和接口综合。

•Lab1: 查看函数的返回和块级协议•Lab2: 理解默认端口的I/O协议,并学会怎么选择I/O协议•Lab3: 查看一下数组端口实现,可以进行分区。

•Lab4: 为设计创建一个优化的实现并添加AXI4接口教程设计描述从xilinx网站下载教程的设计文件,参考信息中获取教程设计。

本教程使用教程目录中的设计文件Vivado_HLS_Tutorial\ Interface_Synthesis。

关于实验•使用前两个实验室在本教程中的示例的设计很简单,这有助于将焦点保持在接口。

•最后两个实验练习使用多通道累加器。

•本教程介绍如何实现采用高层次综合实现I/O端口和协议。

•在实验4中,创建一个在Lab3中使用最优实现的设计接口综合lab1:块级I/O协议概述这个实验解释了什么是块级I/O协议,并控制它们重点:在本教程中的图片和命令假定了教程数据目录Vivado_HLS_Tutorial被解压并放置在c:\vivado_HLS_Tutorial如果教程数据路径解压到不同的位置,或者在linux系统上,调整路径名称指向你选择放置Vivado_HLS_Tutorial目录位置。

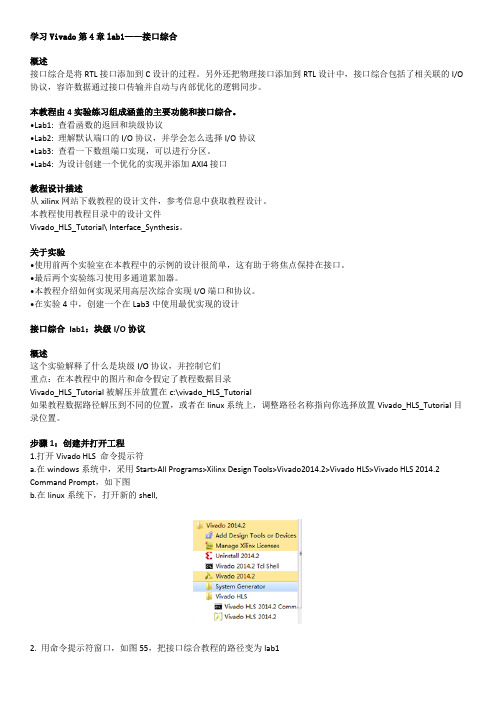

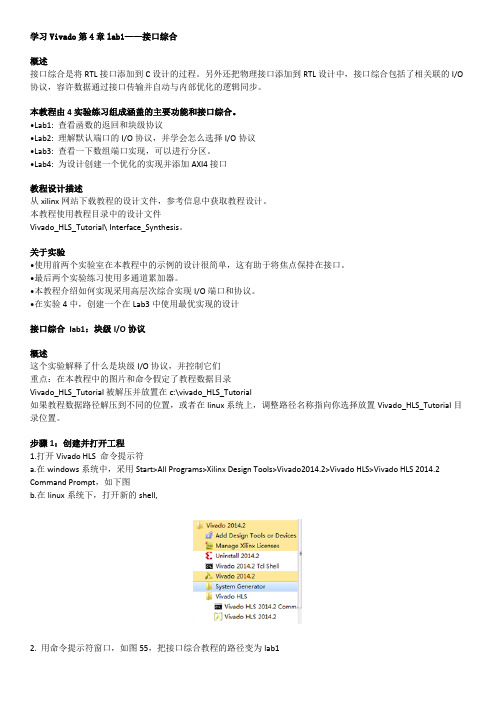

步骤1:创建并打开工程1.打开Vivado HLS 命令提示符a.在windows系统中,采用Start>All Programs>Xilinx Design Tools>Vivado2014.2>Vivado HLS>Vivado HLS 2014.2 Command Prompt,如下图b.在linux系统下,打开新的shell,2. 用命令提示符窗口,如图55,把接口综合教程的路径变为lab13. 执行TCL并建立vivado HLS Project,采用的是vivado_hls–f run_hls.tcl如图55所示4. 当vivado HLS 完成,在用户界面里打开工程。

关于vivado hls的书籍

关于vivado hls的书籍Vivado HLS(High-Level Synthesis)是一种高级综合工具,可以将C、C++等高级语言的算法描述转化为硬件描述语言(HDL),以便在FPGA(Field-Programmable Gate Array)上进行实现。

本文将介绍关于Vivado HLS的书籍及其相关内容。

一、《Vivado HLS教程》《Vivado HLS教程》是一本入门级的教程书籍,适合刚开始学习Vivado HLS的读者。

该书从Vivado HLS的概述开始,介绍了其基本原理和工作流程。

然后,通过一系列实例,详细讲解了如何使用Vivado HLS进行算法描述和优化。

此外,该书还介绍了Vivado HLS的调试技巧和常见问题解决方法,帮助读者更好地应用该工具进行FPGA开发。

二、《Vivado HLS高级教程》《Vivado HLS高级教程》是一本进阶级的教程书籍,适合已经具备一定Vivado HLS基础的读者。

该书主要讲解了Vivado HLS的高级特性和高级优化技巧。

其中包括如何使用指令级并行和数据级并行优化算法,如何使用流水线和状态机优化状态导向的算法,以及如何使用数据流分析和控制流分析进行性能优化。

此外,该书还介绍了如何在Vivado HLS中使用IP核和接口,以及如何进行系统级设计和验证。

三、《Vivado HLS实战指南》《Vivado HLS实战指南》是一本实战型的书籍,适合已经具备一定Vivado HLS基础并希望深入实践的读者。

该书通过一系列实战项目,介绍了如何使用Vivado HLS解决实际问题。

其中包括图像处理、数字信号处理、通信系统等领域的应用示例。

每个实战项目都详细讲解了算法描述、优化技巧、性能评估和验证方法,帮助读者更好地理解和应用Vivado HLS。

四、《Vivado HLS开发指南》《Vivado HLS开发指南》是一本综合性的开发手册,适合从事FPGA开发的工程师和研究人员。

vivado使用手册

Vivado是一款由Xilinx公司开发的集成开发环境(IDE),主要用于FPGA的设计和开发。

以下是Vivado的基本使用手册:

1. 打开Vivado软件,创建一个新工程:点击“Create New Project”,在弹出的界面上填写工程名并选择保存位置。

在选择工程类型时,选择RTL Project(一般为RTL工程)。

2. 在新工程中添加源文件:在新建的工程中,右键点击工程名,选择“Add Sources”来添加Verilog源文件。

在弹出的对话框中选择“OK”和“Yes”完成设计文件的新建。

3. 编写代码:在Sources文件夹中双击新建的设计文件,即可在右边的代码编辑区进行代码的编写。

4. 运行仿真:在编写完代码后,需要进行仿真测试。

在工程名上右键选择“New Run Block”,选择仿真语言为混合语言,然后点击“OK”。

在仿真界面中设置仿真参数,然后点击“Run”开始仿真。

5. 生成比特流:在仿真通过后,需要生成比特流文件以便将设计烧录到FPGA芯片中。

在工程名上右键选择“Generate Bitstream”,在弹出的界面中选择目标语言为Verilog,然后点击“OK”。

等待生成比特流文件的完成。

6. 下载到FPGA:将生成的比特流文件下载到FPGA芯片中进行实际测试。

可以使用Vivado提供的Tcl命令或者第三方工具进行下载。

以上是Vivado的基本使用流程,具体操作可能会根据不同的版本和实际需求有所不同。

建议参考Xilinx提供的官方文档和教程进行学习。

vivado交通灯课程设计

vivado交通灯课程设计一、课程目标知识目标:1. 理解交通灯工作原理,掌握交通灯控制系统的基础知识。

2. 学习使用Vivado软件进行基本的数字电路设计和仿真。

3. 了解Verilog HDL语言的基本结构,能运用其编写简单的交通灯控制程序。

技能目标:4. 能够运用Vivado软件进行电路设计,完成交通灯控制电路的搭建。

5. 能够利用Verilog HDL语言实现交通灯的定时切换和紧急车辆优先通过功能。

6. 培养动手实践能力,通过实际操作解决交通灯控制系统中的问题。

情感态度价值观目标:7. 培养学生对电子设计工程的兴趣,激发创新意识和探索精神。

8. 增强团队合作意识,学会在项目实施中分工合作,共同解决问题。

9. 认识到科技在生活中的应用,理解技术对提高社会生活质量的重要性。

课程性质:本课程为实践性强的课程设计项目,旨在通过实际操作让学生将理论知识与实际应用相结合。

学生特点:学生应为具有一定电子工程基础知识和Verilog HDL语言基础的年级学生,具备基本的逻辑思维能力和动手操作能力。

教学要求:课程要求学生在教师的指导下,独立完成交通灯控制系统的设计、编程、仿真与调试。

通过本课程的学习,学生应能够展示出对知识的应用能力和解决实际问题的能力。

二、教学内容1. 交通灯控制系统原理介绍:讲解交通灯的工作机制,包括信号灯的定时控制、相位差设置、紧急车辆优先通行等基础知识。

- 相关教材章节:第五章“交通控制系统概述”2. Vivado软件操作:学习Vivado设计环境的基本操作,包括创建工程、添加源文件、配置硬件和仿真。

- 相关教材章节:第三章“数字电路设计工具介绍”3. Verilog HDL语言基础:回顾Verilog HDL的基本语法,包括数据类型、运算符、控制语句等。

- 相关教材章节:第四章“Verilog HDL基础”4. 交通灯控制模块设计:- 定时控制模块设计:设计实现交通灯的定时切换功能。

VIVADO教程

VIVADO教程Vivado是美国赛灵思公司(Xilinx)推出的一款可视化集成环境(IDE),用于FPGA(现场可编程门阵列)和SoC(系统级芯片)的设计和开发。

它提供了一个完整的设计流程,从设计输入到最终的实现和验证,为FPGA和SoC设计师提供了强大的工具和功能。

下面是一个简要的Vivado教程,介绍了其基本功能和使用方法。

第一步:安装Vivado第二步:创建新项目在Vivado中,您需要创建一个新的项目来开始您的设计。

选择“File”菜单中的“New Project”,然后按照指示进行操作。

在创建项目的过程中,您需要选择项目的目录、名称和基本设置,以及FPGA或SoC的型号。

第三步:设计输入在新项目中,您可以添加设计文件、约束文件和仿真文件。

设计文件可以是VHDL或Verilog代码,约束文件用于设置时序和引脚约束,而仿真文件用于验证设计。

第四步:约束设置第五步:综合和实现在设计输入和约束设置完成后,您可以对设计进行综合和实现。

综合将设计转化为逻辑门级别,实现则将逻辑门级别映射到FPGA或SoC中的具体资源和连接。

这个过程需要一定的时间,取决于设计的复杂性和目标设备的类型。

第六步:比特流生成第七步:验证在比特流生成之后,您可以对设计进行验证。

Vivado提供了一些强大的仿真工具,可以用于验证设计的功能和性能。

您可以通过添加测试向量来进行仿真,并检查设计的输出是否正确。

第八步:生成硬件描述文件在验证之后,您可以生成硬件描述文件,以便与软件进行集成。

硬件描述文件可以是RTL级别的VHDL或Verilog代码,也可以是系统级别的IP核。

第九步:导出设计在项目开发完成后,您可以将设计导出到其他工具中进行后续处理。

Vivado支持将设计导出为EDIF、NGC、VHDL、Verilog等格式。

您可以根据需要选择最适合的格式。

总结:以上是一个简要的Vivado教程,介绍了其基本功能和使用方法。

Vivado是一个功能强大的FPGA和SoC开发工具,提供了完整的设计流程和一系列的工具和功能。

Vivado入门学习资料整理与备忘

Vivado入门学习资料整理与备忘新的博客,新的起点!打算学习Xilinx最近大力推广的开发环境Vivado,到网上搜了一下资料,发现一个叫cuter的网友写了一系列关于Vivado的文章,从简单的HDL设计到系统设计都有相关介绍,而且步骤详细,非常适合小白入门。

重要的是基于ZedBoard实现,正好手头也有一块,能够完成文章提到的所有实验。

这里把他的文章整理出来,以备使用时查看。

1、Vivado实现纯逻辑开发——从最简单的开始这篇笔记介绍了如何使用Vivado进行基于HDL的逻辑设计,记录了从编码到最后比特流的生成流程。

2、基于Vivado的嵌入式开发——PS+PL实践这篇笔记介绍了如何在Vivado平台下实现zynq ps+pl设计,侧重点在于block design的创建,IP核的添加。

3、Vivado轻松实现IP封装这篇笔记介绍了如何在Vivado环境下将设计好的HDL资源打包成IP核,供Vivado调用。

举一反三:在Vivado环境下新建IP核流程也是类似的。

介绍完基础的工具操作之后,作者给出了一个设计实例,是一个等精度频率计。

1、Vivado设计实战——等精度频率计(概述篇)2、Vivado设计实战——等精度频率计(原理篇)3、Vivado设计实战——等精度频率计(完结篇)接下来是Vivado HLS的使用,前面的设计实例和ISE还有所关联,我还略知一二。

HLS这个东东,我是从来没接触过了。

盗用一下原作者的摘要吧。

1、Vivado HLS初体验1.1、前言该笔记主要是Vivado HLS开发流程的学习心得,掌握HLS开发的全流程:从工程创建到算法仿真到综合再到设计实现,由于截图较多,暂时只写到前两部分。

1.2、目标1)熟悉Vivado HLS GUI的使用2)如何进行C/C++算法仿真2、自己设计简单算法,进一步熟悉HLS《Vivado HLS初体验》一文中,使用别人设计的yuv_filter demo文件新建工程,添加了文件,基本掌握了新建工程和算法仿真的流程,由于没有完全按照现有的教程进行学习,所以对整个流程有了较好的理解。

Vivado 设计流程指导手册 (含安装流程与仿真)

Vivado设计流程指导手册——2013.4Vivado设计分为Project Mode和Non-project Mode两种模式,一般简单设计中,我们常用的是Project Mode。

在本手册中,我们将以一个简单的实验案例,一步一步的完成Vivado 的整个设计流程。

一、新建工程1、打开Vivado 2013.4开发工具,可通过桌面快捷方式或开始菜单中Xilinx Design Tools->Vivado 2013.4下的Vivado 2013.4打开软件,开启后,软件如下所示:2、单击上述界面中Create New Project图标,弹出新建工程向导,点击Next。

3、输入工程名称、选择工程存储路径,并勾选Create project subdirectory选项,为工程在指定存储路径下建立独立的文件夹。

设置完成后,点击Next。

注意:工程名称和存储路径中不能出现中文和空格,建议工程名称以字母、数字、下划线来组成。

4、选择RTL Project一项,并勾选Do not specify sources at this time,勾选该选项是为了跳过在新建工程的过程中添加设计源文件。

点击Next。

5、根据使用的FPGA开发平台,选择对应的FPGA目标器件。

(在本手册中,以Xilinx官方开发板KC705为例,Nexys4开发板请选择Artix-7 XC7A100TCSG324-2的器件,即Family和Subfamily均为Artix-7,封装形式(Package)为CSG324,速度等级(Speed grade)为-1,温度等级(Temp Grade)为C)。

点击Next。

6、确认相关信息与设计所用的的FPGA器件信息是否一致,一致请点击Finish,不一致,请返回上一步修改。

7、得到如下的空白Vivado工程界面,完成空白工程新建。

二、设计文件输入1、如下图所示,点击Flow Navigator下的Project Manager->Add Sources或中间Sources中的对话框打开设计文件导入添加对话框。

vivado_实验指导书

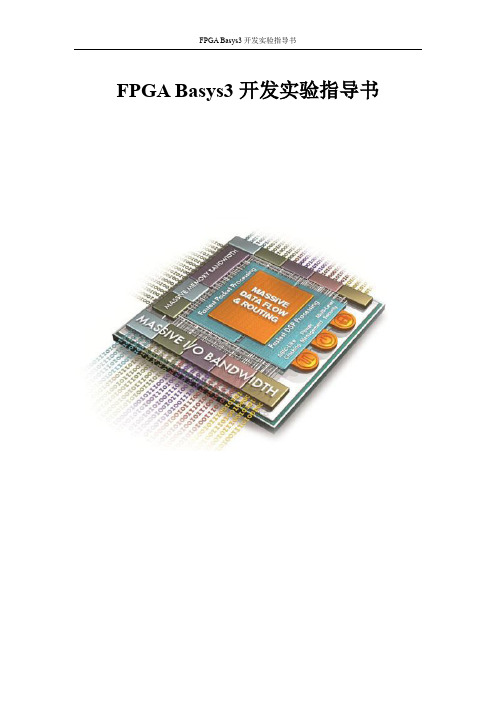

FPGA Basys3开发实验指导书安全使用规范●使用扩展接口扩展电路应用前请关闭电路板总开关,避免损坏器件。

●电路板建议在绝缘平台上使用,否则可能引起电路板损坏。

●电路使用时应防止静电。

●液晶显示器件或模块结雾时,不要通电工作,防止电极化学反应,产生断线。

●电源正负极、输入/输出端口定义时需谨慎,避免应接反引起开发板的损坏。

●保持电路板的表面清洁。

●小心轻放,避免不必要的硬件损伤目录实验一:熟悉VIV ADO编译环境(一) (1)一、实验目的 (1)二、实验内容 (1)三、实验要求 (1)四、实验步骤 (1)实验二:组合逻辑电路设计 (15)一、实验目的 (15)二、实验内容 (15)三、实验要求 (15)四、实验步骤 (15)五、实验结果 (19)实验三:时序逻辑电路设计 (21)一、实验目的 (21)二、实验内容 (21)三、实验要求 (21)四、实验步骤 (21)五、实验结果 (30)实验四:状态机 (32)一、实验目的 (32)二、实验内容 (32)三、实验要求 (32)四、实验步骤 (32)五、实验结果 (37)实验五:模块化调用 (38)一、实验目的 (38)二、实验内容 (38)三、实验要求 (38)实验六:数码管显示 (41)一、实验目的 (41)二、实验内容 (41)三、实验要求 (41)四、实验背景知识 (41)五、实验方案及实现 (43)六、实验结果 (45)实验七:交通灯 (47)一、实验目的 (47)二、实验内容 (47)三、实验要求 (47)四、实验方案及实现 (47)五、实验结果 (52)实验八:秒表的设计 (54)一、实验目的 (54)二、实验内容 (54)三、实验要求 (54)四、实验方案及实现 (54)五、实验结果 (57)实验九: 蜂鸣器演奏实验 (59)一、实验目的 (59)二、实验内容 (59)三、实验要求 (59)四、实验背景知识 (59)五、实验结果 (64)实验十:字符型LCM 驱动 (65)一、实验目的 (65)二、实验内容 (65)三、实验要求 (65)五、实验程序实现 (69)六、实验结果 (74)实验十一:VGA (76)一、实验目的 (76)二、实验内容 (76)三、实验要求 (76)四、实验背景知识 (76)五、实验结果 (80)实验十二:PS/2接口控制 (81)一、实验目的 (81)二、实验内容 (81)三、实验要求 (81)四、实验背景知识 (81)五、实验方案及实现: (84)六、实验结果 (90)实验一:熟悉VIVADO编译环境(一)一、实验目的1.熟悉VIV ADO的编译环境;2.了解在VIV ADO环境下运用Verilog HDL 语言的编程开发流程,包括源程序的编写、编译、模拟仿真及程序下载。

学习VivadoHLS第4章 例程中文版

学习Vivado第4章lab1——接口综合概述接口综合是将RTL接口添加到C设计的过程。

另外还把物理接口添加到RTL设计中,接口综合包括了相关联的I/O 协议,容许数据通过接口传输并自动与内部优化的逻辑同步。

本教程由4实验练习组成涵盖的主要功能和接口综合。

•Lab1: 查看函数的返回和块级协议•Lab2: 理解默认端口的I/O协议,并学会怎么选择I/O协议•Lab3: 查看一下数组端口实现,可以进行分区。

•Lab4: 为设计创建一个优化的实现并添加AXI4接口教程设计描述从xilinx网站下载教程的设计文件,参考信息中获取教程设计。

本教程使用教程目录中的设计文件Vivado_HLS_Tutorial\ Interface_Synthesis。

关于实验•使用前两个实验室在本教程中的示例的设计很简单,这有助于将焦点保持在接口。

•最后两个实验练习使用多通道累加器。

•本教程介绍如何实现采用高层次综合实现I/O端口和协议。

•在实验4中,创建一个在Lab3中使用最优实现的设计接口综合lab1:块级I/O协议概述这个实验解释了什么是块级I/O协议,并控制它们重点:在本教程中的图片和命令假定了教程数据目录Vivado_HLS_Tutorial被解压并放置在c:\vivado_HLS_Tutorial如果教程数据路径解压到不同的位置,或者在linux系统上,调整路径名称指向你选择放置Vivado_HLS_Tutorial目录位置。

步骤1:创建并打开工程1.打开Vivado HLS 命令提示符a.在windows系统中,采用Start>All Programs>Xilinx Design Tools>Vivado2014.2>Vivado HLS>Vivado HLS 2014.2 Command Prompt,如下图b.在linux系统下,打开新的shell,2. 用命令提示符窗口,如图55,把接口综合教程的路径变为lab13. 执行TCL并建立vivado HLS Project,采用的是vivado_hls–f run_hls.tcl如图55所示4. 当vivado HLS 完成,在用户界面里打开工程。

【Vivado那些事】如何查找官网例程及如何使用官网例程

【Vivado那些事】如何查找官⽹例程及如何使⽤官⽹例程有的时候需要查找⼀些官⽹的例程进⾏学习和参考,但是总感觉⽆从下⼿,今天就教⼤家怎么利⽤官⽹和Vivado的Documention进⾏相关的操作。

不清楚使⽤哪些IP或者不清楚需要参考哪个⽂档⾸先点击Help-->Documention and Tutorials就可以打开XIlinx Documention浏览器了。

打开后如下:主要分为:1、分类窗⼝;2、⽂件选择窗⼝;3、设置窗⼝;4、选择窗⼝;可以在3窗⼝进⾏搜索。

假如现在我需要查找⼀下7系列FPGA中关于HLS的使⽤,那么我可以通过1窗⼝进⾏分类选择,如下:就可以在2窗⼝得到我想要的⽂档:点击进去就可以阅读,如果想要下载也可以,这⾥可以进⾏两种设置,⼀是下载路径设置⼆是打开⽂档的阅读器设置,具体位置如下图所⽰:可以按照⾃⼰的需求进⾏设置。

找到了或者已知使⽤哪种或者哪个IP怎么下载例程这⾥提供两种⽅式:1、使⽤Xilinx Doc直接搜索相关的Doc,这⾥举例AXI ethernet,相关的应⽤⼿册是xapp1082(还有其他的参考,这⾥以⽐较常见的举例),直接搜索这个⽂档,打开后如下图所⽰:这两个位置可以下载相关参考例程,直接点击下载即可,建议该⽂档直接使⽤Chrome打开,点击链接会知道跳转,其他PDF阅读器也可。

2、在IP管理器⾥找到该IP双击进⼊其中左上⾓的Documentation,有Product Guide等⽂档,其中Change Log(修改BUG记录)、Product Webpage和Answer Records都是⽐较重要的⽂档,对使⽤好该IP都有很重要的作⽤,因为与本篇⽂章不想关,这⾥就不展开描述了,点击Product Guide就能通过Xilinx Documentation打开这个⽂档,这个⽂档相当相当重要,包括整个IP的使⽤说明,每个参数的说明,时序相关,以及⼀些Debug,仿真相关说明,如果在使⽤该IP时出现问题,请仔细阅读该⽂档,同时该⽂档会提供参考⽰例链接(这个IP⽐较特殊,是两个IP结合在⼀起的,所以没有refence(疯狂翻车))。

Vivado-HLS学习-复合数据类型

Vivado-HLS学习-复合数据类型struct结构体优化:1、 scalar:标量arguments:参数vector:⽮量复合数据类型中的struct。

(1)当结构体被当做参数⽤于顶层函数的时候,scalar成员被映射为标量端⼝;数组成员被映射为memory端⼝;(2)最好将结构体在头⽂件中定义。

(3)结构体中的元素HLS提供了相应的优化⽅式,2、结构体中元素优化⽰例。

为什么是5byte,4bit+4*4bit=20bit,为什么是5byte---file_level优化过的原因。

3、优化⽅式操作。

4、pad:覆盖;file_level优化模式,将每个变量封装成以8bit为边界。

⽐如,变量A是4bit,那么⼩扩展到8bit。

由于数组元素和A变量都定义的4bit,因此,都扩展到8bit。

如下图RTL综合后结构体变量中的元素总⼤⼩为(4bit+4bit)*5=5byte=40bit。

5、struct_level优化模式,将struct类型的⼀个变量中的所有元素放到内存中,所有元素所占总位宽若不是8bit的倍数,那么补充到8bit倍数。

如下图RTL综合后结构体变量中的元素总⼤⼩为4+4*4=20bit+4=3byte=24bit。

6、两种优化⽅式的⽐较。

可看到两种优化⽅式所得效果基本⼀致。

两种data_pack(数据封装)的对于struct的优化⽅式能减少时延、提⾼吞吐率,原因在与data_pack是将for循环展开得到的。

7、波形检查。

---------------------------------------------------------------------------------------------------------------enume枚举类型1、枚举类型介绍。

2、⽰例3、总结。

学习vivadoHLS第7章例程中文版

学习vivado第7章Lab1——设计优化概述创建高质量RTL设计的一个关键部分是采用高层次综合拥有优化C代码的能力。

高层次综合经常尝试减少循环和函数的延迟。

在循环和函数中为了获得这种目的,高层次综合尝试执行尽可能多的并行操作。

在函数层,高层次综合经常尝试执行并行函数。

除了这些自动优化,指令用于:•并行执行多个任务,例如,相同的函数多次执行或相同的循环多次迭代。

采用流水线。

•调整数组(块RAM),,函数,循环和端口的物理实现用以提高数据的利用率和帮助数据流尽快通过设计。

•提供的数据相依性的信息,或缺少这些信息,从而可进行更多优化。

最终的优化技术是修改的C源代码,以删除非预期依赖关系的代码,这种代码可能限制了硬件的性能教程是由两个实验练习组成。

你可以在这些实验练习中用Analysis perspective来执行分析。

前提条件是完成了本教程的Design Analysis教程Lab1参照循环和函数流水线的使用来创建的设计能够在一个时钟处理一个样本。

这个实验包括一些例子,这些例子给您机会去分析两个通常引起不能满足性能要求导致设计失败的原因:循环依赖关系和数据流限制或瓶颈。

Lab2这个实验展示了怎么从lab1中修改代码来帮助克服一些在代码中无意识存在的内在的性能限制。

教程设计描述从xilinx网站下载教程设计文件,在教程设计中查看信息。

教程所用的设计文件在教程目录vivado_HLS_Tutorial\Design_Optimization你在实验练习中使用的样本设计是一个矩阵乘法功能。

设计目标是在每个时钟周期处理一个新的采样,实现的接口作为数据流传输接口。

Lab1:优化矩阵乘法器这个练习使用矩阵乘法器设计用以展示你如何全面优化设计重点是在循环设计上,设计的目标是用FIFO接口在每个时钟周期读一个样本,同时使用最少资源。

这个分析包括了在使用函数级优化的循环级优化方法的比较。

这个练习解释了用户分析界面视角的基本操作,还有你如何用这个界面来驱动设计优化。

vivado hls设计流程

Vivado HLS的设计流程主要包含以下几个步骤:

1. 使用Xilinx提供的特有C语言库进行算法设计。

这是高层次综合(High-level Synthesis)的核心部分,通常包括C、C++等高层次语言的使用。

2. 使用编译器进行C语言源码语法检查,确保代码的正确性。

3. 编写C语言的test bench,用于验证C算法功能的正确性,并在C/RTL协同仿真时生成RTL 验证的test bench。

4. 进行C仿真和基于C语言test bench的RTL级仿真,以确认设计的正确性和性能。

5. 查看并分析仿真结果,根据需要进行设计优化。

6. IP核打包和导出:产生的IP核可以导入到Vivado IDE中进行其他类别的项目开发。

7. 最终输出包括IP(在Vivado的IP Catalog中)、DCP(RTL代码综合后的网表文件)、SysGen (HLS之后的结果可以导入SysGen中使用)。

vivadoHLS优化

vivadoHLS优 化

//HLS数据类型: ap_fixed<总位宽,整数位宽> -------------------------------------------------------------------------(优化)Directive (函数/类 -> 变量/对象)Insert Directive (优化措施 ug902->design optimization)Directive :DATA_PACK 对结构体打包 :INTERFACE 对接口优化 :RESOURCE :STREAM Destination :Source File 对工程下所有solution :Directive File 对当前solution Options :mode->ap_ovld(对应优化措施) //:register //:depth :port->led_o(userport) //:clock name -------------------------------------------------------------------------Run simulation->C simulation dialog->Options:Clean Build

协同modelsim仿真:solution->run c/rtl simulation->Co simulation dialog ->simulator select:modelsim /rtl select:verilog /options->dump trace 输出目录:explorer->solution->sim->... --------------------------------------------------------------------------(HLS导出ip)工具栏->Export RTL->dialog->configure->name:[ip_name]

vivado交通灯课程设计

vivado交通灯课程设计一、课程目标知识目标:1. 学生能理解并掌握交通灯的基本原理,包括红绿灯变换逻辑及其控制方式。

2. 学生能够运用已学的数字逻辑知识,设计并实现一个基于vivado的交通灯控制系统。

3. 学生能了解并描述交通灯控制系统在现实生活中的应用。

技能目标:1. 学生能够使用vivado软件进行基本的电路设计和仿真。

2. 学生通过实践操作,掌握基本的硬件编程技巧,实现交通灯控制逻辑。

3. 学生能够通过小组合作,进行问题分析、方案设计、调试及优化,形成解决实际问题的能力。

情感态度价值观目标:1. 学生通过课程学习,增强对工程实践的兴趣,培养创新意识和动手能力。

2. 学生在小组合作中,培养团队合作精神,学会相互尊重和沟通协调。

3. 学生能够认识到科技在生活中的应用,增强社会责任感和科技伦理意识。

课程性质分析:本课程为实践性强的课程设计项目,旨在通过实际操作,将理论知识与实际应用紧密结合,提高学生的实践能力和创新能力。

学生特点分析:考虑到学生所在年级,已具备一定的数字逻辑基础和编程能力,对新鲜事物充满好奇,喜欢动手实践。

教学要求:根据学生特点和课程性质,将课程目标具体分解为可操作的学习成果,通过任务驱动、小组合作等教学方法,引导学生主动探究,确保教学的有效性和实用性。

二、教学内容1. 交通灯控制系统原理介绍:包括交通灯工作原理、控制逻辑及其在实际生活中的应用。

相关教材章节:第三章 数字逻辑设计,第五节 交通灯控制器设计原理。

2. Vivado软件使用培训:基本操作、电路设计、仿真及硬件描述语言编程。

相关教材章节:第二章 电子设计自动化工具,第一节 Vivado软件入门。

3. 交通灯控制电路设计:基于FPGA的硬件电路设计,包括红绿灯控制逻辑、时序设计等。

相关教材章节:第三章 数字逻辑设计,第四节 时序逻辑设计。

4. 小组项目实践:分组进行交通灯控制系统设计,包括方案讨论、电路设计、仿真、编程及调试。

vivado入门教程-峰哥版

Xilinx zynq 7010clg400-1 sopc 基于zybo 开发板之gpio 使用Vivado 2015.4SDK 2015.4如峰2016 年6 月7 日20:10:33版本说明目录Vivado 搭建底层硬件系统 (4)二、sdk 使用 ........................................................................................................................................................................ 2..6 ...........三、总结................................................................................................................................................................................... 3..8 ........... 附录程序................................................................................................................................................................................... 3..8 ...........Vivado 搭建底层硬件系统首先使用vivado 搭建一个底层硬件系统,具体操作过程如下,用图的方式来说明,直观方便打开vivado 2015.4 如下单击create new project ,如下图,单击next继续单击next ,如下如,解释一下1:工程的名字2:工程在电脑中的位置,不要中文,不要空格3:打上勾表示在2 的位置基础上创建一个子目录,不勾就表示不创建,我一般都是按大类zingsk 的文件夹, zybo 的文件夹,所以我都勾上,我的位置如设置好了之后继续单击 next ,这里是说创建一个什么养的工程一般都是 rtl 的工程, 其他的我还没研究过,直接看官方文档学的,做 fpga 或者 soc ,sopc , 都是 rtl 工程。

HLS 用户手册中文版

HTTP实时流媒体分析器与监测系统Mocomsoft版本1.12013.05MOCOMSOFT HLS Analyzer™用户指南 版权所有:Mocomsoft保留所有权利。

未经Mocomsoft公司明确的书面许可,不得以任何方式复制或转载本文档的任何部分。

公告:Mocomsoft公司已作出一切努力,确保本指南中的信息是有用和准确的。

但Mocomsoft不能保证所含信息的准确性,本指南中描述的产品若有变更,恕不另行通知。

文件中有任何遗漏或不正确的信息,Mocomsoft不承担任何法律责任。

Mocomsoft, Inc1330 Route 206, Suite 103-175Skillman, NJ 08558, USA电话:614-270-9617网址:信息:info@销售:sales@目录第1章:引言 (5)1.1 参考文献 (5)第2章:系统设置 (6)2.1安装软件 (6)2.2 卸载软件 (6)2.3检查HLS Analyzer服务 (6)第3章:安装和运行TSM100远程视图 (8)第4章:输入控制 (11)4.1 HTTP直播 (11)4.2 传输流录制 (12)第5章:传输流监测 (14)5.1 视频缩略图和TR 101 290错误摘要 (14)5.1.1 视频缩略图和播放 (14)5.1.2 传输流错误总结 (15)5.2 PID分析 (16)5.3 节目分析 (17)5.3.1 PCR分析 (17)5.3.2 基本流缓冲区分析 (18)5.4 元数据表分析 (19)5.5 电子节目指南 (21)5.6 历史 (22)5.7 传输流模版 (23)5.8报警 (25)5.8.1 配置邮件服务器 (25)5.8.2 添加电子邮件接收 (26)5.9报告 (27)5.9.1 错误总结 (27)5.9.2传输流质量 (28)5.9.2传输流快照 (29)第6章HTTP会话和播放列表分析 (30)6.1 流 (30)6.2 媒体传输 (31)6.3 HTTP分析历史 (31)6.4 HTTP配置 (32)6.5 HTTP报告 (33)附录:TSM100错误代码一览表 (34)第1章:引言Mocomsoft(摩通)HLS分析仪是一个专业的实时HTTP实时流(HLS)分析系统,用于验证HLS格式和MPEG传输流质量和信号的标准符合性,适用于测试HLS视频基础服务和服务内容。

wp7汉化教程-HexWorkshop之初级入门

最近看了一点odee的汉化教程,很不错啊。

写的很细,基本上照他的教程,没有人不会用的。

闲着没事儿做,我也写一个教程吧,此教程只针对Hex Workshop。

前言:你在看这个教程之前,你要做好准备,因为我不打算截图,也不想截图(必要时候还是有的)。

看到你不知道的名词或者其他,不要停,继续看,括号内会给你通俗解释,我不会把初级入门写复杂(要是真没有解释,回帖问吧)。

后面提到的非标准资源,不知道的就以此贴的说法为准,知道的你就不必看下去了(但是哥们,在懂的人面前别用我给你说的解释,这里只是简化它,不让你看着头大如斗)。

首先,算是第一章吧。

Hex Workshop是一个16进制查看器,应该说来是最好的16进制查看器了。

(暂时无人能超越)其次,算是第二章吧。

很多论坛教汉化的时候,都说:想用16进制查看器必须要了解16进制。

其实我说:了解16进制,固然上手速度快。

但是并非必须会,因为条条大路通罗马!(比起当年在IOI做SP的ROM的时候手算进制数来说,这个浮云尔)不会16进制,一样可以玩转。

在开讲之前,你确实不会16进制,也不知道什么是16进制,但是你有一颗汉化的心,那么好吧,记住这几句真言:1、16进制,就是0、1、2、3、4、5、6、7、8、9、0、A、B、C、D、E、F。

这10个数字+6个字母的各种搭配。

2、他们最少都是2个一组2个一组的出现。

不落单!3、任何东西都可以16进制表示。

包括图片,文档和你的裤衩。

第三章,针对Windows Phone 7的汉化为什么说是针对?因为扯多了你会头晕,你会XX掉我的教程贴,你会说跟你将指针、讲偏移是在激发你的瞌睡。

所以将所有不必要的知识抛弃掉,你说和Windows Phone 7汉化相关的。

这里算是真正的正式开始了:汉化分标准资源和非标准资源2个情况(就不要问什么叫标准和非标准是什么了,你就当是2个代号)。

标准资源,会智能ABC的7岁孩子+ResHacker或者PE Explorer都可以基本搞定(你也不要问真的吗?嗯,确实是真的,但是这个7岁孩子得算半个天才)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

学习vivado第7章Lab1——设计优化

概述

创建高质量RTL设计的一个关键部分是采用高层次综合拥有优化C代码的能力。

高层次综合经常尝试减少循环和函数的延迟。

在循环和函数中为了获得这种目的,高层次综合尝试执行尽可能多的并行操作。

在函数层,高层次综合经常尝试执行并行函数。

除了这些自动优化,指令用于:

•并行执行多个任务,例如,相同的函数多次执行或相同的循环多次迭代。

采用流水线。

•调整数组(块RAM),,函数,循环和端口的物理实现用以提高数据的利用率和帮助数据流尽快通过设计。

•提供的数据相依性的信息,或缺少这些信息,从而可进行更多优化。

最终的优化技术是修改的C源代码,以删除非预期依赖关系的代码,这种代码可能限制了硬件的性能

教程是由两个实验练习组成。

你可以在这些实验练习中用Analysis perspective来执行分析。

前提条件是完成了本教程的Design Analysis教程

Lab1

参照循环和函数流水线的使用来创建的设计能够在一个时钟处理一个样本。

这个实验包括一些例子,这些例子给您机会去分析两个通常引起不能满足性能要求导致设计失败的原因:循环依赖关系和数据流限制或瓶颈。

Lab2

这个实验展示了怎么从lab1中修改代码来帮助克服一些在代码中无意识存在的内在的性能限制。

教程设计描述

从xilinx网站下载教程设计文件,在教程设计中查看信息。

教程所用的设计文件在教程目录vivado_HLS_Tutorial\Design_Optimization

你在实验练习中使用的样本设计是一个矩阵乘法功能。

设计目标是在每个时钟周期处理一个新的采样,实现的接口作为数据流传输接口。

Lab1:优化矩阵乘法器

这个练习使用矩阵乘法器设计用以展示你如何全面优化设计重点是在循环设计上,设计的目标是用FIFO接口在每个时钟周期读一个样本,同时使用最少资源。

这个分析包括了在使用函数级优化的循环级优化方法的比较。

这个练习解释了用户分析界面视角的基本操作,还有你如何用这个界面来驱动设计优化。

重要:在教程中的图片和命令假设教程数据路径vivado_HLS_Tutorial被解压放置在c:\vivado_HLS_Tutorial中。

如果教程数据目录解压缩到不同的位置,或者在Linux系统上,调整一些路径名引用到的位置您选择放置Vivado_HLS_Tutorial目录。

步骤1:创建并打开工程

1.打开Vivado HLS 命令提示符

a.在windows系统中,采用Start>All Programs>Xilinx Design

Tools>Vivado2014.2>Vivado HLS>Vivado HLS 2014.2 Command Prompt,如下图

b.在linux系统下,打开新的shell,

2. 用命令提示符窗口,如图142,从lab1中将目录切换到RTL Verification教程。

3. 执行TCL并建立vivado HLS Project,采用的是vivado_hls–f run_hls.tcl如图142所示

4. 当vivado HLS 完成,在用户界面里打开工程。

用vivado_hls–p matrixmul_prj 命令打开,如图143

5. 在资源管理器中打开Source文件夹,并双击matrixmul.cpp文件如图144的源代码

向下滚动文件,查看源代码有两个输入数组a和b,并输出数组。

将鼠标停在宏(如图144),看看每个是3×3共9个元素。

步骤2:综合分析设计

1. 在工具栏中点击Run C Synthesis按钮,并把设计综合成RTL。

当综合完成,综合报告打开图145,性能估计显示:

•间隔是80个时钟,因为在每个输入数组中有九个元素,设计在输入读时大约花费9时钟。

•间隔比延迟时间的长一个周期,因此在这一点上的硬件不是对应的。

•延迟/间隔是由于内嵌的循环:

内部循环调用

- 2时钟的延迟

- 所有的迭代花费6个时钟周期

Col循环。