数字电路第5章1

第5章数字逻辑电路.ppt

(2)逻辑关系式表示:F=A·B·C

(3)真值表表示:如图表5-1所示

下一页 返回

5.4 基本逻辑门电路

2.“或”逻辑关系 当决定事件的各个条件中只要有一个或一个以上具备时事件就

会发生 图5-10所示,F和A、B、C之间就存在“或”逻辑关系 “或”逻辑也有如上三种表示方法: (1)图5-11所示为“或”逻辑图形符号 (2)逻辑表达式:F=A+B+C (3)真值表:见表5-2

下一页 返回

5.2 数制

5.2.2 二进制数

二进制数只有0和1两个符号。只要能区分两种状态的元件即 可实现。

计数的基数为2,各位数的权是2的幂,计数规律是“逢二进 一”

N位二进制整数的表达示为:

例5.1 一个二进制数10101000, 试求对应的十进制数

上一页 下一页 返回

5.2 数制

图5-23是利用三态与非门组成的双向传输通路,改变控制端C 的电平,就可控制信号的传输方向。

上一页 下一页 返回

5.4 基本逻辑门电路

3. CMOS门电路 CMOS门电路是由PMOS管和NMOS管构成的一种互补对称场效

应管集成门电路。 下面是几种常用的CMOS门电路的结构和工作原理的简要说明 (1)CMOS与非门:如图5-24所示 当A、B全为1时,T1和T2同时导通,T3和T4同时截止,F=0 当输入端由一个或全为0时,串联的T1和T2必有一个或两个全部截

上一页 下一页 返回

5.4 基本逻辑门电路

(5)TTL三态输出与非门电路。简称三态门,图5-20是其逻辑 图形符号。A、B是输入端,C是控制端,F为输出端。输出端除 了可以实现高低电平外,还可以出现高阻状态。

数电第5章

第五章 触 发 器

图 5 – 7 由与非门构成的基本RS触发器

第五章 触 发 器

1. 功能描述 (1) 当Rd=1, Sd=0时,不管触发器原来处于什么状态, 其次态一定为“1”,即Qn+1=1,故触发器处于置位状态。 (2) 当Rd=0, Sd=1时,Qn+1=0,触发器处于复位状态。 (3) 当Rd=Sd=1 时,触发器状态不变,处于维持状态, 即Qn+1=Qn。 (4) 当Rd=Sd=0 时,Qn+1=Q n+1=1,破坏了触发器的正常 工作,使触发器失效。而且当输入条件同时消失时,触发 器是“0”态还是“1”态是不定的,这种情况在触发器工作 时是不允许出现的。因此使用这种触发器时, 禁止 Rd=Sd=0出现。

发生的。这种电路中没有统一的时钟脉冲。任何输入信

号的变化都可能立刻引起异步时序电路状态的变依从关系来分,又可分为米里 (Mealy)型和莫尔(Moore)型两类。米里型电路的输出是输 入变量及现态的函数,即

F (t ) f [ x(t ),Qn (t )]

器和JK触发器。在基本RS触发器的基础上, 加两个与非

门即可构成钟控RS触发器, 如图 5-10 所示。

第五章 触 发 器

图 5 – 10 钟控RS触发器

第五章 触 发 器

1. 功能描述 当CP=0时,触发器不工作,此时C、D门输出均为 1, 基本RS触发器处于保持态。此时无论R、S如何变化,均 不会改变C、D门的输出,故对状态无影响。 当CP=1 时,触发器工作,其逻辑功能如下: R=0, S=1, Qn+1=1,触发器置“1”; R=1, S=0, Q n+1=0,触发器置“0”; R=S=0, Qn+1=Qn,触发器状态不变; R=S=1, 触发器失效,工作时不允许。

第五章数字电路基本知识

首页

电工电子技术 (3)二进制与十六进制之间的相互转换:

①二进制数转换为十六进制数:将二进制数由小数点开始, 整数部分向左,小数部分向右,每4位分成一组,不够4位补 零,则每组二进制数便是一位八进制数。

(0 0 0 1 1 1 1 0 0 1 0 0 . 0 1 1 0)2 = (1E4.6)16

这也正是数字电路得到广泛应用的原因 。

首页

电工电子技术

数字电路的分类:

数字电路的种类很多,常用的一般按下列几种方法来分 类: ① 按电路组成结构来分:可分为分立组件电路和集成电路。 ② 按集成电路的集成度来分:可分为小规模集成电路 (SSI)、中规模集成电路(MSI)、大规模集成电路(LSI)和超 大规模集成电路(VLSI)。 ③ 按构成电路的器件来分类:可分为双极型电路和单极型 电路。 ④ 按电路中元器件有无记忆功能(逻辑功能):可分为组 合逻辑电路和时序逻辑电路。

首页

电工电子技术

在两个稳定状态之间作阶跃式变化的信号称为数字信号 ,数字信号在时间上和数值上都是离散的。例如生产线中 的产品,只能在一些离散的瞬间完成,而且产品的个数也 只能逐个增减,它们的转换信号就是数字信号。

u

逻辑1

逻辑1

逻辑1

Vm

逻辑0

逻辑0

逻辑0

t

0

tw

T

占空比:q(%)= tw/T*100%

(364.5)10=( 101101100.1 )2=(16C.8 )16 =( 554.4 )8 (74)10=( 1001010 )2=( 4A )16 =( 112 )8

首页

电工电子技术 (5)二进制代码

第五章(8259)

采用I/O独立编址方式(但地址线与存储器共用) 地址线上的地址信号用 IO/M来区分:

IO/M=1 时为I/O地址

I/O操作只使用20根地址线中的16根: A15 ~ A0 可寻址的I/O端口数为64K(65536)个 I/O地址范围为0~FFFFH IBM PC只使用了1024个I/O地址(0~3FFH)

符号 ’0’ ’1’ ’2’ ’3’ ’4’ ’5’ ’6’ ’7’

应用例子:发光二极管接口

+5V

D0 | D7 Q0

D0~D7

A0~A15 M/IO

译 码 器

. . .

Q7

=1 . . . =1

R

. . .

. . .

R

CP

WR

74LS373

I/O接口综合应用例

根据开关状态在7段数码管上显示数字或符号 设输出接口的地址为F0H

设输入接口地址为F1H

当开关的状态分别为0000~1111时,在7段数 码管上对应显示’0’和内存地址空间相互独立。 优点:内存地址空间不受I/O编址的影响 缺点:I/O指令功能较弱,使用不同的读写控制 信号

内存地址空间 I/O地址空间 0000H FFFFH

内存空间 (1MB)

00000H

I/O空间 (64KB)

FFFFFH

8088/8086 CPU的I/O编址方式

第5章 数字量输入输出

5.1 概述 1.I/O信号形式 通常有以下4种类型: (1) 数字量: 二进制形式的数据,最小单位为 “位”(bit),8位称为一个字节(BYTE)。 (2) 模拟量: (3) 开关量: 用一位二进制数表示。 (4) 脉冲量:

第5章 锁存器与触发器

《数字电路与逻辑设计》

3) 状态转换图与激励表

将锁存器两个状态之间的转换及其所需要的输 入条件用图形的方式表示称为状态转换图(简称为 状态图),用表格的形式表示则称为激励表。

基本SR锁存器的状态图如下图所示,表5-2为 其激励表。

表5-2 基本SR锁存器的激励表

SD=0

RD=´

0

SD=1 RD=0

《数字电路与逻辑设计》

第5章 锁存器与触发器

本章主要内容

5.1 基本锁存器及其描述方法 5.2 门控锁存器 5.3 脉冲触发器 5.4 边沿触发器 5.5 逻辑功能和动作特点

《数字电路与逻辑设计》

本章重点:

掌握锁存器与触发器的电路结构、逻辑 功能和动作特点

本章难点:

触发器的工作原理

《数字电路与逻辑设计》

此外,锁存器的功能还可以用状态转换图和激 励表表示。

《数字电路与逻辑设计》

1) 特性表(真值表) 基本锁存器的特性表如表5-1所示。

表5-1 基本SR锁存器特性表 与非门构成的锁存器 或非门构成的锁存器 SD RD Q Q* SD RD Q Q* 1 1 0 0 0000 1 1 1 1 0011 1 0 0 0 0100 1 0 1 0 0110 0 1 0 1 1001 0 1 1 1 1011 0 0 0 × 1 1 0× 0 0 1 × 1 1 1×

《数字电路与逻辑设计》

(2) CLK为高电平时, 由于SD=(S·CLK)=S、RD=(R·CLK)=R,因 此门控锁存器将根据输入信号S和R实现其相应的 功能。

将SD=S、RD=R代入到基本锁存器的特性方 程Q*=SD+RD·Q,可得到门控锁存器的特性方程为

Q*=S+R·Q

铜陵学院 数字电子技术第5章习题解答

铜陵学院 数字电子技术 石建平第5章习题解答5-1.为什么基本RS 触发器的输入信号需要遵守S D ’+R D ’=1的约束条件?解:基本RS 触发器的输入信号同时为0时,触发器输出端Q =Q ’=1,这时我们称为11态。

但是,若S D ’和R D ’同时无效回到1后,基本RS 触发器的输出状态将由两个与非门的传输延迟时间决定,即输出状态将无法确定。

因此,此状态称为不定状态,使用时应避免这种情况发生。

5-2.试问电平触发的SR 触发器和基本RS 触发器在电路结构和动作特点上有哪些不同? 解:电平触发的SR 触发器电路结构中有时钟信号,输入端是在时钟信号的控制下对触发器作用,只有当时钟信号在有效状态下,输入信号才能使触发器接收信号建立状态,而基本RS 触发器电路结构中没有时钟信号,输入信号直接对触发器作用。

5-3.试问电平触发方式的触发器能构成具有翻转功能的触发器吗?为什么?解:不能。

电平触发方式的触发器,在整个电平有效期间内,均可以接收信号建立状态,因此,若构成具有翻转功能的触发器,将会在整个电平有效期间内不断地接收信号实现翻转,会出现空翻现象。

5-4.已知基本RS 触发器电路中,输入信号端R D ’和S D ’的电压波形如图5-1所示,试画出图示电路的输出端Q 和Q ’端的电压波形。

’S D ’G 2G 1R D ’S D ’R D ’解:(1)标出所有输入信号变化的边沿,在每一段内根据基本RS 触发器的输入输出画出Q 和Q ’端波形;(2)输入端RD ’=0,SD ’=1,Q =0,Q ’=1;随后RD ’=SD ’=0,触发器输出为11态; (3)输入端RD ’=1,SD ’=0,Q =1,Q ’=0;随后RD ’=0,SD ’=1,Q =0,Q ’=1;在RD ’=SD ’=1,触发器输出保持不变;(4)输入端RD ’=1,SD ’=0,Q =1,Q ’=0;随后RD ’=SD ’=0,触发器输出为11态;最后RD ’=0,SD ’=1,Q =0,Q ’=1。

《数电》教材习题答案 第5章习题答案

思考题与习题5-1 在如图5-1所示的四位移位寄存器中,假定开始时Q3Q2Q1Q0为1101状态。

若串行输入序列101101与CP脉冲同步地加在D SR串行输入端时,请对应画出各触发器Q 3Q2Q1Q端的输出波形。

图T5-15-2 图T5-2电路中各触发器的初始状态均为0,请对应输入CP和IN的波形,画各触发器Q端的输出波形。

图T5-25-3 试用两片74LS194电路构成一个八位移位寄存器,并画出逻辑电路图。

5-4 请用上升沿触发的D触发器构成一个异步三位二进制加法计数器。

并对应CP画出Q1、Q2、Q3的波形。

图T5-45-5 请用JK 触发器构成一个脉冲反馈式异步六进制加法计数器,并画出对应于CP 脉冲的工作波形。

图T5-5用三位JK 触发器构成八进制计数器,然后在状态110时利用与非门反馈至清零端构成六进制计数器,图略。

5-6请分析如图T5-6所示的阻塞反馈式异步计数器电路的逻辑功能,指出该计数器为几进制,并画出计数状态转换图。

图T5-6解:(1)驱动方程:J I =3Q ,K 1=1; J 2=1,K 2=1;J 3=nQ n Q 21,K 3=1;代入得状态方程: (CP 脉冲下降沿时刻)(Q 1下降沿时刻) (CP 脉冲下降沿时刻)列出状态转换图(略)分析得出该计数器为5进制计数器,状态从000-100,其它的三个状态下一状态均为000,因此该电路是异步五进制计数器,具有自启动功能。

5-7 分析图T5-7同步计数器电路的逻辑功能。

图T5-7nn n n n Q K ,Q J Q K ,Q J Q K ,J 232312323111====== n Q n Q Q n 1311=+n Q Q n 221=+n Q n Q n Q Q n 31231=+nn n nn n nn n n n n n n n n n Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q Q 23232132123123113111=⋅+⋅=⋅+⋅=+=⋅+=+++n n n Q Q Q 123 111213+++n n n Q Q Q0 0 0 0 0 1 0 0 1 0 0 0 0 1 0 1 0 1 0 1 1 1 1 0 1 0 0 0 1 1 1 0 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 1因为该计数器设计了清零端,因此可实现从000开始进入循环圈的2进制计数器的功能,但我们也发现,它也可以实现三进制。

数电第五章

D 1D E E1

E

Q

D Q

Q

Q

可见,D锁存器存在“空翻 ”现象。

3. 锁存器的动态特性

ቤተ መጻሕፍቲ ባይዱ

D

tSU

tH

C D TG TG

G1

1

Q

E

tW

tpLH

1C C

TG C

tpHL

TG

2

1

Q

Q

G2

建立时间tSU :表示D信号对E下降沿的最少时间提前量。

脉冲宽度tW :为保证D信号正确传送到Q和 Q

保持时间tH :确保数据的可靠锁存的最少时间。 延迟时间tpLH:输出从低电平到高电平的延迟时间;

1 G1

R

≥1

G2 ≥1 S

1

0

10

Q

当S、R 同时回到0时,由于两个与非

门的延迟时间无法确定,使得触发器 最终稳定状态也不能确定。

Q

0

约束条件: SR = 0

2)逻辑符号与逻辑功能

逻辑功能表

SR

Qn

Q n1

00

0

00

1

01

0

01

1

0

不变

1

0 置0

0

10

0

1

置1

10

1

1

11

0

不确定 不确定

11

1

不确定

延迟时间tpHL:高电平到低电平的延迟时间。

4. 典型集成电路

CMOS八D锁存器- 74HC/HCT373

传输门控 D 锁存器

传输门控 制D0

D1

…

D7

1

1

…1

1D

数字电路与逻辑设计第5章时序逻辑电路

图5-1时序逻辑电路的组成框图

根据图5-1,可以列出以下3个逻辑 方程组:

(5-1) (5-2) (5-3)

其中,式(5-1)称为输出方程,式 (5-2)称为驱动方程(或激励方程), 式(5-3)称为状态方程。

qn1,qn2,…,qnj表示存储电路每个触发 器的初态,qn+11,qn+12,…,qn+1j表示存 储电路每个触发器的次态。

表5-2 74LS175的状态转换表

图5-7 74LS175的引脚排列图

5.3.2移位寄存器

在数字电路系统中,由于运算的需 要,常常要求输入寄存器的数码能逐位 移动,这种具有移位功能的寄存器,称 为移位寄存器。

移位寄存器的逻辑功能和电路结构 形式较多。

根据移位方向可分为单向移位寄存 器和双向移位寄存器两种;根据接收数 据的方式可分为串行输入和并行输入两 种;根据输出方式可分为串行输出和并 行输出。

所谓串行输入,是指将数码从一个 输入端逐位输入到寄存器中,而串行输 出是指数码在末位输出端逐位出现。

1.单向移位寄存器

单向移位寄存器,是指数码仅能作 单一方向移动的寄存器。可分为左移寄 存器和右移寄存器。如图5-8所示是由D 触发器组成的4位串行输入、串并行输出 的左移寄存器。

图5-8 4位左移寄存器

分析同步时逻辑电路的一般步骤如 下。

(1)写出存储电路中每个触发器的驱 动方程; (2)将驱动方程分别代入各触发器的 特性方程,得出每个触发器的状态方 程; (3)根据逻辑电路写出输出方程。

5.2.2时序逻辑电路的一般分析方法

实际上,从驱动方程、状态方程和 输出方程这3个方程中,还不能对时序逻 辑电路的逻辑功能有一个完全的了解, 还需要通过另外一些更直观的方法来分 析和描述时序逻辑电路的逻辑功能。这 里主要介绍3种比较重要而且常用的方法 ,分别是状态转移表、状态转移图、时 序图。

数字电子技术 第5章 时序逻辑电路的分析

40

5.8异步计数器

1.异步计数器的概念:异步计数器中的 触发器不会同时改变状态,因为它们没 有共同的时钟脉冲

41

2. 三位异步二进制计数器

42

波形图

Q0:2分频 Q1:4分频 Q2:8分频

Q0 Q1’ Q2

43

3.四位异步十进制计数器

1 CP 2 3 4 5 6 7 8 9 10

起译码 作用

电路分析: Di输入的数据,在cp 上升沿作用下,逐位 向左移动,经过4个 脉冲,将把输入的第 1个数传送到输出D0。

电压波形

34

5.5.MSI移位寄存器

M=0 M=1

串行输出

74LS95右移 移位寄存器

并 行 输 出

(1)电路形式:电路接成串行移位右移,并行输入,并行输出。 (2)工作原理:当方式控制M=1时,允许数据以并行方式输入,在cp2作用下,并 行存入J-K FF,并以并行方式输出Data.Q0~Q3。当M=0时,并行输入被禁止, 允许串行输入到J-K FF,在cp1作用下逐位右移。

1

1

1

1

4位异步二进制计数器(74LS93)

电路特点: 74LS93是一个MSI.模2×8进制计数器。从电路形式上看,第1 个FF为2进制,第2~4个FF是8进制计数器。采用两个时钟脉冲 CPA,CPB,有2个复位输入端,为方便灵活使用。

46

74LS93应用

用74LS93构成模16计数器。 将QA(第一级FF输出)作为CPB 使用,成为模16计数器。

(4)将驱动方程分别代入J-K FF的特性方程:

001 000 (2)时序电路的输出为Q3Q2Q1

(3)各FF的驱动方程: J1=Q3 K1=1 J2=1 K2=1 J3=Q2Q1 K3=1

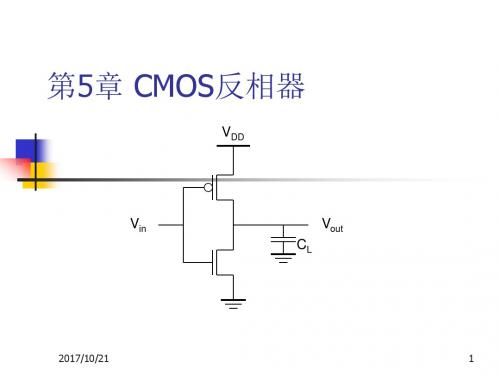

数字集成电路设计 第5章 cmos反相器..

2017/10/21

27

即使电源电压很低时,晶体管仍能导通,仍然 具有反相器的特性,因为亚阈值电流足以使该门在 低电平和高电平之间切换,并提供足够的增益从而 得到可接受的VTC。

但使得门的特性变的很差。VOL和VOH不再等于 电源的两个电平,并且过渡区的增益接近1。 为了能得到足够的增益以用于数字电路,必须使 电源为热电势的两倍,否则就只能降低热电势,即 降低环境温度,冷却该电路

(W/L)p kn’VDSATn(VM-VTn-VDSATn/2) = (W/L)n kp’VDSATp(VDD-VM+VTp+VDSATp/2)

2017/10/21 16

1.5 1.4 1.3 1.2 1.1 1 0.9 0.8 0.1 1

~3.4

VM 对于器件比值的变化 相对来说是不敏感的。

2017/10/21 9

当NMOS和PMOS器件的电流相等时,一个直流(dc) 工作点成立。因此dc工作点必须处在两条相应负载线 的交点上。 所有的交点(工作点)不是在高输出电平就是在低输 出电平上。因此反相器的VTC曲线显示出具有非常窄 的过渡区。 在过渡区内,两管同时导通且处于饱和状态。

2017/10/21

2017/10/21 24

2、降低电源电压

2.5

0.2

2

0.15

Vout (V)

1.5 1 0.5 0 0 0.5 1

Vin (V)

降低VDD改善了增益

2017/10/21

Vout (V)

0.1

0.05

增益=-1

0

1.5

2

2.5

0

0.05

0.1

0.15

0.2

数字电子技术 第5章

锁存器电路图

(1)

E CP 1D 1

(11) 1

C1

(3)

1D Q

C1

EN

(2) 1Q

1

EN

(4) 2D

1D C1 Q

(5) 2 Q

1

EN

(6)

D

3Q

1

& ≥1 Q

(7) 3D

19) 4 Q

1D C1

Q

1

& ≥1

(12)

Q

5Q

EN

5D

(13)

1D C1 Q

1

CP

图5-13 一位D锁存器逻辑图

EN

(15)

6D

(14)

6Q

1D C1

Q

1

EN

(16)

7D

(17)

1D C1

Q

1

7Q

EN

8D

(18)

(19)

1D

Q

1

8Q

(3)移位寄存器

移位寄存器不仅可以存储代码,还可以将代码移位。 ⑴四位右移移位寄存器的原理:

并行输出

Q0 DI FF0 1D Q C1 CP FF1 1D Q1 FF2 1D Q C1 Q2 FF3 1D C1 Q Q3 DO

表5-4 74194的工作状态表

Rd

0 1 1 1 1

S1 S0 × 0 0 1 1 × 0 1 0 1

工作状态 清零 保持 右移 左移 送数

CP A

& & & & & & &

1

并行输出

FA QA Q 1 FB QB Q 1 1S C1 1R R FC Q C Q 1 FD QD Q 1S C1 1R R

74161的逻辑符号

数字电子技术第5章

(4)逻辑功能分析:当Q1Q0=11时,输出Z=1;当取 其它值时,输出Z=0;在一个循环过程中,Z=1只出现一次, 故为进位输出信号。所以,此电路是带进位输出的同步4 进制加法计数器电路。

EXIT EXIT

第5章 时序逻辑电路

分析举例

【例5.1.2】图所示电路是异步时序逻辑电路的逻辑图, 试分析它的逻辑功能。

3. 求出对应状态值

设电路初始状态为 Q3Q2Q1 Q0 =0000 当某触发器时钟 条件满足时,计算 其状态方程的值; 触发器时钟没有到 来时,则不用计算 其状态方程的值, 保持原有状态。

演 示 文 稿 Presentation

0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1

EXIT EXIT

第5章 时序逻辑电路

画状态图和时序图

演 示 文 稿 Presentation

随着CP脉冲的递 1010至1111在 增,不论从电路输 计数循环外, 出的哪一个状态开 但可以进入计 始,触发器输出的 数循环,称为 变化都会进入同一 自启动 个循环过程

(4)逻辑功能分析:由状态图和时序图 可知,该电路是十进制计数器,或10分频器。

EXIT EXIT

第5章 时序逻辑电路

5.1.2 时序逻辑电路的分析方法

演 示 文 稿 Presentation

基本步骤:

1. 根据给定的电路,写出它的输出方程和驱动方程,并求 状态方程。 时序电路的输出逻辑表达式。 2. 列状态转换真值表。 各触发器输入信号的逻辑表达式。 将驱动方程代入相应触发器的特性方程中所得到的方程 3. 分析逻辑功能。 简称状态转换表,是反映电路状态转换的规律与条件的表格。 方法:将电路现态的各种取值代入状态方程和输 出方程进行计算,求出相应的次态和输出,从而列出 4. 根据状态转换真值表来说明电路逻辑功能。 画状态转换图和时序图。 状态转换表。 如现态起始值已给定,则从给定值开始计算。如 用圆圈及其内的标注表示电路的所有稳态, 没有给定,则可设定一个现态起始值依次进行计算。 在时钟脉冲 CP作用下,各触发器状态变化的波形图。 用箭头表示状态转换的方向,箭头旁的标注表示 状态转换的条件,从而得到的状态转换示意图。 EXIT EXIT

数字电路与逻辑设计05-1

目前随着半导体工业的飞速发展,中规模集 成电路已经逐渐淡出历史舞台,取而代之的 是集成度更高,功能更为强大,使用更为灵 活的CPLD/FPGA器件或者专用的ASIC器件。但 中规模集成电路中采用的一些常用的逻辑功 能,对于数字系统的设计和模块划分仍然具 有指导借鉴意义。 为了兼顾通用性,中规模集成电路的逻辑功 能多是根据实际应用中的功能需求为基础而 设计出来的,如同高级程序设计语言中的顺 序,选择,循环三大类控制语句一样。

常用逻辑功能模块

译码器

编码器

数据选择器 全加器

比较器

5-2

组合逻辑电路分析

依据给定逻辑电路,找出其输出与输入之间的 逻辑关系。通过分析,评价电路设计的优劣, 吸取优秀的设计思想或者给出改进意见。

• 组合逻辑电路分析的一般步骤:

依据电路写出输出函数表达式,对表达式进行 化简,列写真值表,对其功能进行评述。

注意:分析组合逻辑电路,应熟悉常用的各种逻 辑符号(如逻辑门符号以及中规模电路符号)及 其功能。

数字电路与逻辑设计

张林行

带着问题去学习

1、什么是组合逻辑电路?有何特点? 2、如何分析给定组合逻辑电路的功能? 3、组合逻辑的设计步骤? 4、在组合逻辑设计过程中, design 与synthesis有什么不同? 5、实现组合逻辑有哪些方式?针对不同的实 现方式,设计方法有什么不同?

吉林大学仪器科学与电气工程学院:数字电路与逻辑设计

组合逻辑电路特点:

1. 功能:任意时刻的输出仅取决于输入 2. 电路结构:不含存储或记忆元件

a1 a2

组合逻辑电路

y1

y2

an

组合逻辑电路的框图

ym

组合逻辑电路的输入/输出关 系可以用逻辑函数来表示。

数字电子技术第五章 触发器

0

1

10 0 0

10 1 0

11 0 0

11 1 1

与非门SR锁存器的约束条件: R’D+S’D =1即 RDSD =0 。

SD ' RD ' Q Q *

0 0 0 1① 0 0 1 1① 10 00 10 10 01 01 01 11 11 00 11 11

不允许

置0 置1 保持

激励信号输入端低电平有效。

反相器

0

门电路不具备记忆功能

用G2门将VO1反相,并接G1的 另一个输入端;则VI1信号消 失,VO1的低电平和VO2的高

电平也能保持。

SR锁存器

SR锁存器 原理图

符号

SR锁存器:是各种触发器的基本组成部分,有两个

能自行保持的稳定状态。

SD、RD为激励输入端,定义输出端的Q=1、Q’=0 为锁存器的1状态,Q=0、Q’=1为锁存器的0状态。

1 0 01 1 1 1 00 1

Q*=1 置1 1 1 01 1

1 0 10 0 Q*=0 置0

1 0 11 0

1 1 1 0 1①

1

1 1 1 1①

不允许

约束条件SR=0。否则当S、R同时由1变为0,或者S=R=1 时CLK回到0,触发器的次态将无法确定。

图形符号:C1表示编号为1的一个CLK控制信号。1S和 1R表示受C1控制的两个输入信号,只有在C1为有效电平

时,1S和1R信号才起作用。输入端处没有小圆圈表示CLK高

电平有效,有小圆圈则低电平有效。

SD’ 异步置1输入端和RD’ 异步置0输入端,可立即将触

发器置1或置0,不受时钟信号的控制。异步置位复位输入 端低电平有效,正常工作时应使其无效(处于高电平)。

数字集成电路5章[1]习题1

![数字集成电路5章[1]习题1](https://img.taocdn.com/s3/m/1d84a8ea710abb68a98271fe910ef12d2af9a9cc.png)

说明:[难度等级(E容易M中等C难),需要的设计工具,与之相关的章节]第5章CMOS反相器4. [E, None, 3.3.3]对于图5.3中的输出负载为3pF的反相器:a. 计算t plh,t phl和t pb. 上升延时和下降延时是否相等?为什么?c. 计算静态和动态功耗,假设门的时钟频率尽可能的快。

图5.3 电阻负载反相器7. 考虑图5.5中的电路。

器件M1是一个标准的NMOS器件。

器件M2除了阈值电压为负并且其值为-0.4V之外,和M1有共同的特性。

假设耗尽型器件M2的所有电流公式和不等式(来决定工作模式)与规范的NMOS器件相同。

并假设输入IN有0V到2.5V的摆幅。

图5.5 一个耗尽型负载的NMOS反相器a.器件M2的栅极和源极相连。

如果V IN =0V,那么输出电压是多少?在稳态,对于这个输入,器件M2的工作模式是什么?b.计算V IN =2.5V时的输出电压。

为简化计算,你可以假设V OUT很小。

在稳态,对于这个输入,器件M2的工作模式是什么?c.假设Pr(LN=0)=0.3,这个电路的静态功耗是多少?8. [M, None, 3.3.3]一个NMOS晶体管用来向一个大电容充电,如图5.6所示:a. 确定这个电路的t pLH,假设输入节点有一个0到2.5V的理想阶跃信号。

b. 假设一个5kΩ的电阻R S用来对电容放电至地,确定t pHL的值。

c. 确定在对电容充电期间从电源得到多少能量。

其中多少能量在M1中被消耗?在放电期间,多少能量在下拉电阻上消耗?当R S减小至1kΩ时又是多少?d. NMOS晶体管用一个PMOS器件代替,k p和原先NMOS的k n相等。

替换后的结构是否比以前快?解释为什么。

图5.6 注明W/L比的电路图12. 考虑图5.9的低摆幅驱动:a. 输出节点(V out)的电压摆幅是多少?假设γ =0。

b. 输入端有一个从0V 到2.5V的翻转,估算(i)来自于电源的能量和(ii)能量损耗。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

④电路功能描述:该电路是一个3位串行 输入移位寄存器。

2.代数分析法的一般步骤 ①写出输出函数表达式和激励函数表达式。 ②把激励函数表达式代入触发器的次态方 程,导出电路的次态方程组。 ③根据次态方程组和输出函数表达式作出 同步时序电路的状态表,画出状态图。 ④拟定一典型输入序列画出时间图,并用 文字描述电路的逻辑功能。

5.2.2 分析举例 例5.1 用表格法分析如图5.6所示的同 步时序逻辑电路。 ①写出输出函数表达 式和激励函数表达式。 J1=K1=1 J2=K2=x⊕y1

根据状态响应序列,可作出时间图

例5.2 分析如图所示的同步时 序电路。

①写出输出函数和 激励函数的表达式。 Z=xy2y1 D2=x+y2+y1 =xy2y1 D1=x

②列出电路次态真值表。

③作出状态表和状态图。

④作出时间图

该电路是一个“101”序列检测器。

例5.3用代数分析法分析电路

X

②列出电路次态真值表。

③作出状态表和状态图。

④用时间图和文字描述电路的 逻辑功能

电路是一个2位二进制数可逆计数器。 当电路输入x=0时,可逆计数器进行加1计数, 其计数序列为 00 01 10 11 当输入x=1时,可逆计数器进行减1计数,其计 数序列为 00 11 10 01

设电路初始状态为y2yl=00,输入x为电平信号, 典型输入序列为111100000,则电路的状态响应 序列如下。 CP: 1 2 3 4 5 6 7 8 9 x: 1 l 1 1 0 0 0 0 0 y2: 0 1 1 0 0 0 1 1 0 y1: 0 1 0 1 0 1 0 1 0 y2(n+1): 1 1 0 0 0 1 1 0 0 y1(n+1): 1 0 1 0 1 0 1 0 1

④画出时间图,并说明电路的逻辑功能。 设电路初态为“0”,输入x1为00110110, 输入x2为01011100,电路的输出和状态 响应序列如下。 时钟节拍: 1 2 3 4 5 6 7 8 输入xl: 0 0 1 1 0 1 1 0 输入x2: 0 1 0 1 1 1 0 0 状态y: “0” 0 0 0 1 1 1 1 输出Z: 0 1 1 0 0 1 0 1

第五章 同步时序逻辑电路

5.1 概述 5.1.1 时序逻辑电路的结构

5.1.2 时序逻辑电路的分类

的 按 工 照 作 电 方 路 式

与 根 输 据 入 输 直 出 接 是 相 否 关

同步时序逻辑电路

异步时序逻辑电路 Mealy

Moore

根据输入 信号形式

脉பைடு நூலகம்型 电平型

5.1.3 同步时序逻辑电路的 描述方法

电路功能:实现串行加法器 X1:被加数; x2:加数; y:进位;

Z:和 ;

例5.4 分析图示同步时序逻辑电路

①写出输出函数和 激励函数表达式 Z=y2⊕y1⊕y0 T2=y2⊕y1 T1=y1⊕y0 T0=y0⊕x

②写出电路的次态方程组 y2(n+1)=y2⊕T2= y2⊕y2⊕y1=y1 y1(n+1)=y1⊕T1= y1⊕y1⊕y0=y0 y0(n+1)=y0⊕T0= y0⊕y0⊕x=x ③作出电路的状态表和状态图

①写出输出函数和 激励函数的表达式: Z=xl⊕x2⊕y J=x1x2 K=x1+x2

②把激励函数表达式代入触发器的次 态方程,得到电路的次态方程组

y(n+1)=Jy+Ky =xlx2y+x1+x2y =xlx2y+xly+x2y =xlx2+xly+x2y

③根据次态方程和输出函数表 达式作出状态表和状态图。

1.逻辑函数表达式 (1)输出函数表达式 (2)激励函数表达式 (3)次态函数表达式

2.状态表

3.状态图 4.时间图

5.2 同步时序逻辑电路分析

5.2.1同步时序逻辑电路分析的方法和步骤 1、表格分析法的一般步骤 ①写出输出函数和激励函数表达式。 ②列出电路次态真值表。 ③根据次态真值表和输出函数表达式,作 出给定电路的状态表和状态图 ④画出时间图,用文字描述电路的逻辑功 能。