双口RAM应用

双口RAM在雷达数据处理中的应用

( e 7 3 I s iu e o I Ya g h u 2 5 01 Ch n ) Th 2 n tt t f CS C, n z o 2 0 , i a

Ab ta t Th s p pe e e t he s r t e o ua— r s r c : i a rpr s n s t t uc ur f d lpo t RAM ,nt o c s t i r du e he bus og c o y l i f du lp r a — o t RAM , nd i t o c sm anl h he y a d me h a n r du e i y t e t or n t od ofCPU t t i da a s orng, a a e — d t x c ng ng a a a s a i hr gh du lpo tRAM wo CPU n d t oc s o h a。 ha i nd d t h rng t ou a・ r ・ oft i a a pr e s roft e r 。

da e m i a . rt r n 1 Ke r s du lp r y wo d : a — o tRA M ; t ag i ; d e sar ir to og c; om p r t s or e un t a dr s b t a i n l i c a a or

双口R AM 有 2路 完全 独立 的 数据 总 线 、 地

收 稿 日期 :2 0 0 5一O 4—1 3Leabharlann 维普资讯 维普资讯

20 0 6年 8月

舰 船 电 子 对 抗

SH I PB( A RD ) ELECTR (N I C( U N TERM EASUR E ) C )

双口RAM在嵌入式系统调试中的应用

路 板面 积 。配台 IA总 线采 用 中 S

不仅可 满 足上 位 机 多任务控 制 系统 的需要

, ,

还

可 提 高本 系统 实时数 据 的处 理时 1l I 序 中 睦 时 效

。

I 7 3 ( ) 上位机 地址 DT 1 0U6 在

信方式, 或因结构复杂, 或因 传递

B

,

种 插 卡 式 可 编程 控 制 器 a该 嵌 入 式

I T 10 美 国I T 司采用 高 为与 上位机 共享 的通信 数据 区 如 图 D 73 是 D 公 P C实 质是 一个 智能 化 I L / O接 口卡 , 性 能 的 c s Mo 工艺生 产 的高速 1 K 2 所示 i 轰器件 的高集 成 度大大 简化

维普资讯

、

\

置 与 ] ■ 茸 结 E :

双 口 RAM 在 嵌 入 式 系 统 调 试 中 的 应 用

羲 毫 文 台 牡 曲 点 夼 t 渔 八 P 毒 辕 | 本 蛄 糕 采 特 , 甥 它 嵌 成 L 蜕 硬 I e

:: #

j

该片用别同的断志 芯 运 有 于 类 中标 进

行总线仲裁: 存储阵列中的 ×3E FH

和 ×3F F H单元被用做通信 “ 邮箱 ,

择调磷 竹萋席 怠媾了 _ 《 霉溉 箕罐虢攫神 强 鲥 调,

黪嚣 l中嘲貔蔫戮婚 . 谚 试 最。

j 嘲 R M ^ { 统 试 ≤ | 藏口 ^ j 或 摹 调 嵌

芯片却 独具特 点 :①具 有两套 完垒

卜 上 — — 003 、 8:04F - — — — 一 0.F 00003 — 0-F D 00-F - 0 - 1

00 00

~

双口RAM在DSP与红外干涉仪通信系统中的应用

j霉 鳜 国 《 碡

・

__ 0 毒

文章 编 号 。 17—7520)400—5 6288 ( 60—05 0 0

双 口 RAM 在 D S P与 红 外 干 涉 仪 通 信 系统 中 的应用

黄 烨 ,方 勇华 ,熊 伟 ,董大 明

( 中国科学院安徽光学精密机械研 究所,合肥, 20 3) 30 1

摘 要 : 出了利 用双 口 R M 实现 D P与红 外干涉仪并行 接 口的设计 方 案,以使双 方 提 A S

进行高速 通信。介 绍 了双 口 R M 器件 I T 04的原 理 与使 用规 则,并针 对设 计方 案给 A D 72 出了接 口 电路 和 软件 流程 。最后,针对 二者 交换 数据 的仲 裁方 式,提 出 了三种解 决 冲

( S ) n ni ef o ee ipeetd i odr oea lte S o D P a da tr rm trs rs e ,n re t n b P t cmmu i t i e nef — n e n eh D o nc e t t tr r a w h h i e

t r v n h o f c ft y t m s ̄ c r n o t e a bir t d a c s o t a a e c a g d b t e o p e e t t e c n i to wo s s e l o di g t h r t a e c e s t he d t x h n e e we n

t e d sg ,t ei t ra e crui a d f w h r r lo p ee t d.Fia l, h e t o s a epr p s d h e in h n e fc ic t n o c a ta e as r s n e l n l t r e me h d r o o e y

双口RAM在DSP与ICCD通信系统中的应用

程 。针 对二 者 交换 数 据 的 仲 裁 方 式 , 出 了解 决 冲 突 争 端 的 方 法 。 整 体 系统 通 过 调 试 , 明 文 中采 取 的 中断 , 逻 提 证 忙

辑, 软件协调三种模式 , 有效解决 了两个 系统之 问的通信 争端。信 息处理 系统与 IC C D可 良好 协调 工作 , 系统 运行

SM E H H

输 出 L0 ,0 高 阻 数 据输 入

功 能 休 眠模 式 写 存 储 器

L

X

H

X

X

H

H

X

数据输 出

高 阻

读存储器

输 出不 允 许

( )两套完全独立 的数据 线 、 址线 、 写控 制线 , 1 地 读/ 允

许 两 个 C U对 双 端 口存 储 器 的 同 一 单元 进 行 同 时 存 取 ; P ( )有 两 套 完 全 独 立 的 中断 逻 辑 来 实 现 两 个 C U之 间 2 P

子系统之间的高速通信。

1 双 口 R M 器件 I T7 o A D O 7介绍

11 器件简介 .总线 ຫໍສະໝຸດ 称 描述 总线名称

描述

D 1 0 [5— 】

数据信号

C# E

片选信号

IT70 D 0 7是 美 国 IT公 司 采 用 高 性 能 的 C S工 艺 生 D MO

产的高速 3 2k×8bt i双端 口静态 R M, A 典型功 耗 8 0m ; 5 w 最大存取时 间:5n ; 1 s 工作 环境 : 5℃ ~+8 ; 一4 5 工作 电

口宽 度 , 址 线 l 地 2位 , 寻 址 空 间 应 为 3 8bt 可 2k× i 。

双口RAM在CAN与PROFIBUS-DP网关中的应用研究

两个 L C 1 8微控 制 器和 双 口 R M 设 计 C N 与 P O IU — P网 关 的方 案 ,介 绍 了利 用双 口 P23 A A R FB SD

R M 实现 双 C U之 间的 通信 的 实用 、高效 的方法 。这种设 计方 案对 其他 现 场 总线之 间的 网关设 A P

计具 有重要 的借鉴 意义 。 关键 词 :双 口 R M;P O IU — P A A R FB SD ;C N;总线

Ap l a in o u 1p r p i to fd a . o tRAM n t e CAN nd c i h a PROFI BUS. DP a e y g t wa

D P与 C N总线 网关 可 以实 现这 两种 不 同总线 之 间 A

d a P i e u e o u l o u lC U w t t s fd a — r RAM.T i e i r g a o t e ed u ae y b t e e hh pt h s d sg p o ms fr o r f l b s g t n r h i wa ewe n t h

P O IU 是 符 合 德 国 国家 标 准 D N 94 R FB S I 125和 欧洲标 准 E 5 10的 现 场 总线 , P O IU — P N07 由 R FB SD 、

P O I U .A和 P O IU —MS三个部 分 组成 , R FB S P R FB SF 广

灵活。

F ANG iz e , C L .h n HENG a g h ‘ W ANG o 1 Gu n . e , Ma .i ,L Gu . u V o h a ,

( .S a d n o ue c n eC ne ,ia 0 1 C ia 1 h n o gC mp t Si c e t J n2 04, hn ; r e r n 5 2 S a d n s tt f ih d sr ,ia 05 , hl ) .h n o gI t ueo g t n utyJn n2 3 3 C ia ni L I 5 l

利用双口RAM实现DSP与上位机的数据交换

【 yw r sD P; ulpr R M ; a xhn e Itr c Ke o d 】 S D a ot A D t E ca g ; e ae — a n f

O 引 言

在 某 雷 达 自动 测 试 系统 中 . 控信 号 源 的 本 地 控 制 器 采 用 的 D P 程 S

Th t c a eBewe n DS a d pe mpu e i h a - o tRAM eDaa Ex h ng t e P n Up rCo trUsngt eDu lg

【 bta tB sdo h hrceiiso MS 2 V 5 0 n D 7 2 1 tew y o aaeca g spou e ew e P a d U p r A sr c]ae ntec aatr t fT 3 0 C 4 2 a dI T 0 6 , h a fdt xh ne i rd cd bt enDS n p e sc

I DT7 61 02

7 VC1 45 4L 62 A

T 320 54 MS  ̄C 02

( L

㈣ l

碡 )

^3 C —= O E - 舡 ( ) R )

厂

c D

D D V D

上 传 给上 位 机 。 此 C 4 2与 上 位 机 之 间 的 数 据 交换 是 系 统要 解 决 的 因 50

主 要 问题 之 一 。

而 (

L)

丽( ) R

R/ () lI iR

土 I C P S U S 雎

一 — — — —

本 文 将 主要 介绍 一 种 利 用 双 口 R D 7 2 1 实 现 C 4 2与 上 AM IT 0 6 , 50 位 机数 据 交 换 的实 现 方 法 。

IDT7007高速双端口RAM及其应用

PDF 文件使用 "pdfFactory Pro" 试用版本创建

来获得标志。一旦右边使用完毕而显示复位标志(置标志为 1),则左边立即置标 志为 0 以获得使用权,旗语通讯标志总是通过置位——测试的序列来进行的。旗

语通讯标志为低电平有效,申请标志应向锁存器写 0,释放标志时写 1。这八个锁 存器可通过 SEM、OE、R/W、A0~A2 像 RAM 单元一样来进行读写,只是读或

表 6 典型旗语通讯序列

功能

左端口

申请寄存

D0

器

右端口

申请寄存

D0

器

状态

旗语通讯

无动作

1

1

1

1

自由

左端口写

0

0

1

左端置标

1

志

无变化,右

右端口写

0

0

1

0

端保留申

请标志

右端获得

左端口写

1

1

0

0

标志

右端口写

1

1

1

旗语通讯

1

自由

PDF 文件使用 "pdfFactory Pro" 试用版本创建

INTL x

=H 功能

x

x

不相等

H

H

正常

H

x

相等

H

H

正常

x

H

相等

H

H

正常

L

L

表 5 旗语通讯读/写操作

输

相等 入

CE

R/W

OE

(2)

(2) 写禁止(3)

SEM

输出 I/O0-7

模式

H

Linux内核中双口RAM驱动开发及在大圆机控制系统中的应用

De v e l o pm e nt o f Du a l — po r t RAM Dr i v e r i n Li n u x Ke r n e l a nd Appl i c a t i o n i n Co nt r ol S y s t e m of Ci r c ul a r Ma c hi n e

W ANG Yi l i ,H 【 , Xu d o n g,H UAN G Bi n ( F a c u l t y o f Me c h a n i c a l E n g i n e e r i n g a n d Au t o m a t i o n , Z h  ̄ i n a g S c b T e c h Un i v e r s i t y ,Ha n g z h o u 3 1 0 0 1 8 , C h i n a )

d i a me t e r j a c q u a r d c i r c u l a r k n i t t i n g ma c h i n e .T h e e x p e r i me n t a l r e s u l t s h o ws t h a t t h e c o n t r o l

s y s t e m o f c i r c u l a r ma c h i n e c a n l o a d d u a l — — p o r t RA M d r i v e r a n d c o r r e c t l y i d e n t i f y d u a l _ ’ p o r t RAM wh e n s t a r t i n g;i t c a n r e a l i z e p a r a me t e r t r a n s f e r o f u p p e r a n d l o we r c o mp u t e r s t h r o u g h

CPLD和双口RAM在图像采集系统的设计应用

的特 点。而基 于 C L P D和双 口 R AM 的图像采 集系统 为解

决这个 问题提供 了有效 的途径 。本文就数据采集 系统的组

为了提高 图像采 集 系统 对来 自 C D组 件输 的高速 数 C 据流运算处理能力 , 系统设计 时 , 采用了并行处理技 术 。也 就是让 图像 的存取和微 处理器 的采集 运算 同时进 行 , 图像 的存取过程 , 微处 理器 不参 与控制 , 而是 由硬件 电路 ( 口 双

锦 州 1 10 ) 20 0 ( 北 电 子技 术 研 究 所 东

摘

要

针对 C D组件输 出图像数据流的特点, C 提出了一种基于 C LD芯片、 口 RAM 存储器等相关控制电路构成 的图像采集处理 P 双

C D组 件 ; P D ̄ C C L RAM TN9 7

系统 。阐述了图像采集 系统 的工作原理, 以及 C L P D芯片 、 口 R 双 AM 存储器的具体操作方式 。

通信 的方式将 目标信号 的坐标 置 、 度等 级等参 数上传 给 灰

上位机 。

出的图像数据流量大 、 流程快 , 这要求图像 采集处理 系统在 对 图像数据流进行处 理时 , 要具 备高速 性 、 实时性 、 准确 性

3 系统 工作 流 程 控 制

3 图 像 并 行 处 理设 计 .

系统 的初始化 及对 已经 采集 的 图像数 据进 行 软件 后续 处

理[ 。

基 于上述原则 , 系统设计 时采 用两 片双 口 R AM 数 据 存储器 ( 口 R 双 AM1 双 口 R 、 AM2 , ) 以乒乓 间歇 的工作方式

板上 , 并辅 以微处理器模块、 预处理转换电路和通信 电路完

R AM、 P D 自动 完 成 。微 处 理 器 模 块 的工 作 主 要 是 完 成 EL )

双口RAM应用实例

双端口RAM在高速数据采集中的应用利用传统方法设计的高速数据采集系统由于集成度低、电路复杂,高速运行电路干扰大,电路可靠性低,难以满足高速数据采集工作的要求。

应用FPGA可以把数据采集电路中的数据缓存、控制时序逻辑、地址译码、总线接口等电路全部集成进一片芯片中,高集成性增强了系统的稳定性,为高速数据采集提供了理想的解决方案。

下面以一个高速数据采集系统为例介绍双端口RAM的应用。

该系统要求实现对频率为5MHz的信号进行采样,系统的计算处理需要对信号进行波形分析,信号采样时间为25μs。

根据设计要求,为保证采样波形不失真,A/D采样频率用80MHz,采样精度为8位数据宽度。

计算得出存储容量需要2K字节。

其系统结构框图如图3所示,图4给出了具体电路连接图。

根据设计要求,双端口RAM的LPM_WIDTH参数设置为8,LPM_WIDTHAD 参数设置为11(211=2048),使用读写使能端及读写时钟。

ADCLK、WRCLK和地址发生器的计数频率为80MHz。

A/D转换值对双端口RAM的写时序为顺序写方式,每完成一次A/D转换,存储一次数据,地址加1指向下一单元,因此写地址发生器(RAM_CONTROL)采用递增计数器实现,计数频率与ADCLK、WRCLK一致以保证数据写入时序的正确性。

写操作时序由地址和时钟发生器、A/D转换时钟和双端口RAM的写时钟产生。

停止采样时AD_STOP有效,写地址发生器停止计数,同时停止对RAM的写操作。

将地址发生器的计数值接至DSP总线可以获取采样的首尾指针。

地址发生器单元一般用(VHDL)语言编程实现,然后生成符号文件RAM_CONTROL在上层文件调用。

其部分VHDL语言程序如下:对双端口RAM的读操作采用存储器映像方式,其读出端口接DSP的外扩RAM 总线,DSP可随机读取双端口RAM的任一单元数据,以方便波形分析。

由于LPM_RAM_DP模块的读端数据总线q不具有三态特性,因此调用三态缓冲器74244,通过其将输出数据连接到DSP数据总线上。

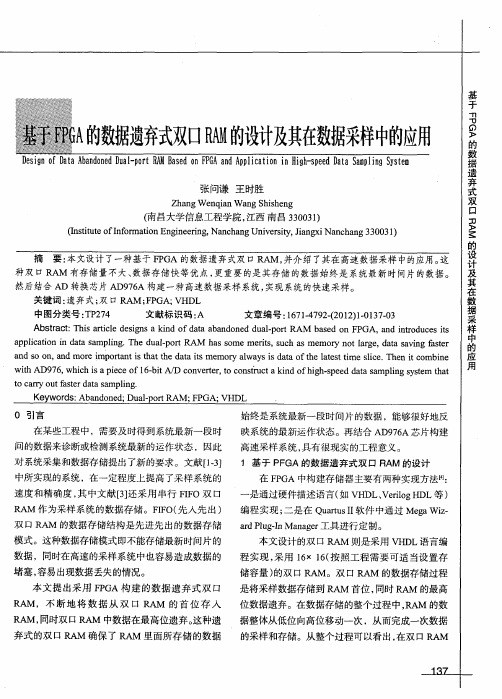

基于FPGA的数据遗弃式双口RAM的设计及其在数据采样中的应用

Ke wo d : a d n d Du 1 o AM ; P y r s Ab n o e ; a . r R p t F GA; VHDL

0 引言 在 某些工程 中 ,需要及 时得 到 系统最 新一 段 时 问的数 据来诊 断或检测 系统 最新 的运作 状 态 ,因此 对 系统采 集和数 据存储 提 出 了新 的要求 。 文献 【—] 13 中所 实 现的系统 ,在一 定程 度上 提高 了采 样系 统 的 速 度 和精 确 度 , 中文献 [] 其 3还采 用 串行 FF IO双 口 R M 作 为采 样 系统 的数 据存 储 。FF 先 入 先 出 ) A IO(

双 口R AM 的数据存储结构是先进先出的数据存储 模式。这种数据存储模式 即不能存储最新 时问片的 数据 ,同时在高速的采样系统 中也容易造成数据的 堵塞 , 容易出现数据丢失的情况。 本文提 出采用 F G P A构建 的数据遗弃式 双 口 R M,不 断地 将数 据 从 双 口 R M 的 首 位存 入 A A R M, A 同时双 口R M 中数据在最高位遗弃。 A 这种遗

wi D9 6 w i pe e f bt D o v r rt o s- t ido i . edd t smpigss m a t A 7 , hc i a ic 一iA/ c n et 。oc nt c kn f g s e aa a l t t t h hs o1 6 e i a u h h p n ye h

基

于

-1 T

_ D

A 数 遗 式 口 A的 计 其 数 采 中 应 的据 弃双 R 设及在据 样的用 M

双口RAM原理及应用实例

1.CPU并行工作(双单片机系统 )方式得到广泛应用。 为了使2个单片机能够快速有效交换信息,充分利 用系统资源,采用双口 RAM实现存储器共享是目 前较为流行的方法。

2.大容量、高速 FPGA 器件具有集成度高、体积小、

灵活可重配置、实验风险小等优点,在复杂数字系 统中得到越来越广泛的应用。用 FPGA来实现双口 RAM的功能可以很好地解决并行性和速度问题, 而且其灵活的可配置特性使得基于 FPGA的双口 RAM易于进行修改、测试及系统升级,可降低设 计成本,缩短开发周期。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在 PAL、GAL、CPLD等可编程器件的基础上

所以,内部仲裁控制逻辑 相应的提供以下功能: 1.对同一地址单元访问的时序控制; 2.存储单元数据块的访问权限分配; 3.信令交换逻辑。

当左右端口不对同一地址单元存取时, BUSY R=H, BUSY L=H,可正常存储;当左右端口对同一地址单元 存储时,有一个端口的 BUSY=L,禁止数据的存取,此 时,两个端口中先出现的存储请求信号对应的 BUSY=H,允许存储。后出现的存储请求信号对应的 BUSY=L,禁止存储(注意:两端口间的存储请求信号 出现时间差应满足仲裁最小时间间隔 TAPS(IDT7132 为5ns),否则仲裁逻辑无法判定哪一个端口的存储请 求信号在前);在无法判定哪个端口先出现存储请求信 号时,控制线BUSY L和BUSY R只有一个为低电平,不 会同时为低电平,这样就避免了双端口存取出现错误。

双口RAM在数字系统中应用广泛。高速数据采集系统

中,一般的数据传输系统在大数据量情况下会造成数据堵塞现 象。在一些实时控制场合,实时算法经常需要由几个 DSP串行 或并行工作以提高系统的运行速度和实时性。以双口 RAM构 成的数据接口可以在两个处理器之间进行高速可靠的信息传输。 此外,双口 RAM可以应用在智能总线适配卡、网络适配卡中 作为高速数据传输的接口。在许多宽带信号处理领域 (如无线 通信、多媒体系统、卫星通信、雷达系统等 ),FPGA技术已代 替DSP实现许多前端的数字信号处理算法。用 FPGA来实现数 字信号处理能很好地解决并行性和速度问题,而且其灵活的可 配置特性,使得 FPGA构成的数字信号处理系统易于修改、测 试及系统升级,降低设计成本,缩短开发周期。任何一种自动 控制系统都离不开数据采集系统,数据采集系统的质量直接影 响整体系统的工作性能。数据采集系统高速、实时发展趋势, 对数据的传输和控制速度提出较高要求。而采用双口 RAM可 有效提高速度,解决速度匹配问题。

true dual port ram 的用法

true dual port ram 的用法

True Dual Port RAM的用法是指同时允许两个独立的数据写入或读取,并不会有数据冲突。

它是数字电路设计中的一种非常重要的电子器件,主要应用于数据缓冲、图像数据处理、信号生成等领域。

其被广泛地

应用于数据传输和处理芯片中。

True Dual Port RAM的设计基本结构类似于一种显存,但其有两个独

立的端口,分别由不同的控制线进行控制。

以Cypress公司的

CYD7446GN为例,其具有两个读取端口和两个写入端口。

其中,每个端口都可以独立地访问内存快,并且每个内存单元都由一个相应的读取

端口和写入端口控制。

这样可以让两个独立的设备同时访问同一块内存,彼此之间不会互相干扰。

True Dual Port RAM的应用非常广泛。

首先,它可以作为数据缓冲器

使用,让数据通过一条线路被多个处理器同时读取,以实现数据存取

的高效性。

其次,它还可用于图像和音频处理器中,被用于保持音频

和视频数据的像素值或颜色。

另外,True Dual Port RAM还可以用于

信号处理电路的数据保存和恢复,例如,车载系统中的雷达信号处理

模块,采样时,从两个端口同时读取数据。

总而言之,True Dual Port RAM的应用领域非常广泛,在工业、航空、航天、通信等各个领域都有广泛的应用。

其能够同时处理多条数据,

并且保证数据的正确性和独立性,为当今的数字电路设计提供了先进

而灵活的功能。

双端口RAM在高速电脑提花机中的应用

双端口RAM在高速电脑提花机中的应用黄金波(桂林空军学院541003)摘 要 介绍了双端口RAM ID T7005的仲裁方法,以及ID T7005在提花机控制系统中的应用,较好地解决了提花机实时、高速选针控制与在线花型修改的矛盾,使大提花机的伺服系统轻松实现8000纬/mi n(1344针)以上,对各种提花机均能满足要求。

关键词 提花机 双端口RAM 工控机 单片机1 前言在高速大提花机伺服系统中,采用单个CPU (通常是工控机)实现对提花选针的实时控制,同时又要实现在线花型的显示、局部放大、编辑修改,有时还要实现组网生产管理而必须与管理中心服务器进行通信,这给伺服系统的设计带来很大的困难。

一方面要求硬件设计要采用速度较高的工控主板,使伺服系统硬件成本大幅度上升;另一方面使软件的开发难度增大,且受系统资源限制,软件在运行时必然要频繁地打开、关闭花型文件等,使软件的运行效率较低,难以实现大提花机的多任务、实时高速的伺服控制。

采用多CPU架构是解决这类问题最有效的方法。

本系统采用工控机主板+单片机模式进行设计,工控机负责人机交互,磁盘文件的管理,花型文件的显示、局部放大、编辑修改,数据的预处理,织机的状态显示,工控机与单片机的数据通信及与网络管理中心服务器的通信等任务;单片机负责提花龙头选针控制,织机的伺服控制等实时性任务。

由于花型文件较大时(比如达到8M),将系统设计成开机时一次性传送整个文件是不经济的,而且难以实现在线修改后传送。

因此,合理地解决工控机与单片机间的数据通信是本系统设计中的关键。

CPU之间的通信可采用以下几种方式:串行通信;并行通信;利用共享式存储器实现。

串行通信时要占用双方CPU时间,并行通信是在CPU之间增加缓冲器或锁存器实现双机通信,由于通信的数据量较大且要求实时,工控机的负担并没有因为增加单片机而得到明显减轻,这两种方式对解决本问题效果不理想。

共享式存储器有用普通存储器构成的DMA方式和用多端口存储器构成的新的通信方式,采用DMA方式能够达到数据的高速传输,但不能同时访问存储器,CPU必须等待总线,不利于实时控制;利用多端口存储器,例如双口RAM和F IFO 就是常用的两种多端口的存储器,它允许多CPU同时访问存储器,大大提高了通信效率,同时CPU间运行时的相互牵制达到最小,是解决本问题最理想图 主界面设置界面设计具有故障自动显示功能,电气参数和工艺参数可进行加密设置,即可设置使用者的优先权。

fpga双端口bram的用法

FPGA双端口BRAM的用法在现代的数字设计领域中,FPGA(Field-Programmable Gate Array)技术已经得到了广泛的应用。

FPGA是一种可编程的逻辑器件,可以通过编程来实现不同的数字电路功能。

而BRAM(Block RAM)是FPGA中的一种重要资源,用于存储数据和临时变量。

在FPGA设计中,双端口BRAM是一种非常有用的资源,能够提高设计的性能和灵活性。

1. 双端口BRAM的基本概念双端口BRAM是指具有两个读写端口的块RAM。

这意味着它可以同时进行读和写操作,而不会出现数据冲突。

这种特性使得双端口BRAM非常适合在FPGA设计中用于存储和处理大量的数据。

在图像处理、信号处理和深度学习等领域,双端口BRAM可以有效地提高算法的性能和并行处理能力。

2. 双端口BRAM的应用双端口BRAM在FPGA设计中有多种应用方式,可以用于实现数据缓冲、数据通路和状态机等功能。

在数据缓冲方面,双端口BRAM可以用于存储输入和输出数据,同时进行读写操作,以实现数据的缓冲和流水线处理。

在数据通路方面,双端口BRAM可以用于实现数据的交换和共享,以便多个模块能够同时访问和处理数据。

在状态机方面,双端口BRAM可以用于存储状态变量和控制信号,以实现复杂的状态机和状态转换逻辑。

3. 如何使用双端口BRAM在FPGA设计中,使用双端口BRAM需要首先进行资源分配和位置区域映射。

然后需要进行读写控制和数据流控制,以确保数据的正确读写和流水线处理。

需要根据具体的应用场景和性能要求,进行数据路径和控制逻辑的优化和调整。

使用双端口BRAM需要充分理解其工作原理和时序要求,以确保设计的正确性和稳定性。

4. 个人观点和总结作为FPGA设计领域的一名从业者,我认为双端口BRAM是一种非常有价值的资源,能够大大提高FPGA设计的性能和灵活性。

通过合理的应用和设计,双端口BRAM可以在信号处理、图像处理和人工智能等领域起到重要作用,为项目的成功实现提供了有力支持。

继电保护装置中的双口RAM

/ E CL L

左端口 / L OE X

A2.0 l AL L 1 F FF

/NT I L X

R WR / X

/ E CR X

右 端 口 / E OR X

A2・ 0 l AR R X

/ NT I R L

功能 设 置 / NT I R

双 口存 储 器 ,它 有 两 套 地 址

图 1 MC 8 3 6 3 2与,  ̄s 2 w 4 r 3o o接口示意 图

维普资讯

《 气自 化 2 6 电 动 ) 0年第2卷第2 0 8 期

微 电脑 应 用

表 1 邮箱 中 断真 值 表

R /WL L

O t 数 据 缓 冲器 , 加 上 一 u) 再

1 S 2 F4 ¨ 3 0 2o

些必要的控制信号线 ,这样

处 理 器 之 间 可 以 按 照 先 进

先 出的顺序原则 , 通过 FF IO

器 件 实 现 相 互 通 讯 。但 是 这 种 方 式 主 要 适 合 于 每 次 所 要 交 换 的 数 据 较 少 、要 求 处 理 器 问 的 数 据 交 换 尽 可 能

线和两套数据线 ,有关控制逻辑保证 每时每刻 只有一套地址线和

一

套数据线通过带三态的缓 冲器对全局存储器进行读 、 写操作 。

在我们研制 的继 电保护 系统 中 , 采用 摩托罗拉3 位 高性 能单 2 片机 MC 8 3 负责对 整个 系统 中运行 的各个 任 务的 管理 和调 6 3 2,

度, 人机 对话 , 开关 量 的采 集 、 出等任 务 ; 输 而数 据 采集模 块 的 C U则采用 德州 仪器公 司 T 3 0 2 0 D P 模 块 的具 体工 作流 P MS 2 F 4 S 。 程分 两路 : 一路是 经开关柜 在线检测 电路 , 进入 D P内置 的两片 S A D转 换器进行转 换 ; 另一路 由外 部二次侧 电压 、 电流 经过电压 、 电流互 感器 , 信号调理 电路 , 转换为 ± V交 流信号 , 5 再经 过 A/ D 转换 器 MA 2 模数转 换 , 换结果 由 D P读 取 。 X15 转 S 然后 再 由 D P S 进行 各种必 要 的计 算处理 , 并将 结果送 到双 E R M 供 MC 8 3 1 A 632 使用 。 C 8 3 需要使 用大量 由 D P处理完 成 的各种数据 , M 632 S 由于 有 实时处 理的要 求 , S D P不 能被 动地用作 从处理 器 , MC 8 3 在 6 32

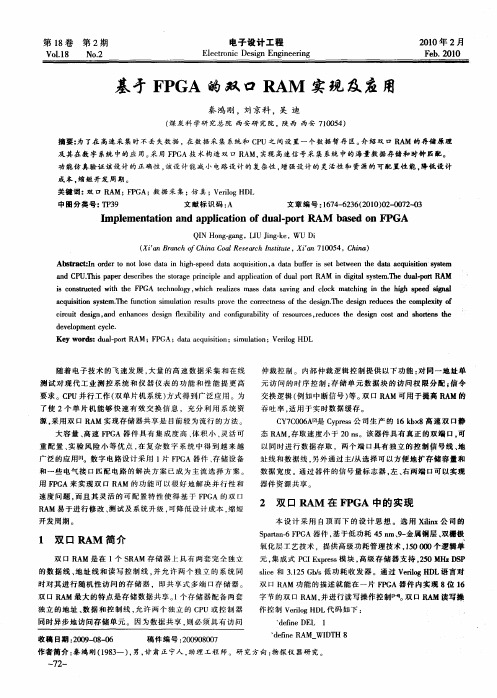

基于FPGA的双口RAM实现及应用

功能 仿 真验 证 该 设 计 的正 确 性 , 设 计 能减 小 电路设 计 的复 杂 性 , 强设 计 的灵 活 性 和 资 源 的 可配 置 性 能 . 该 增 降低 设 计

成 本 . 短 开 发周 期 。 缩 关键 词 :双 口 R M;F GA;数 据 采 集 ;仿 真 ;V rlgHDL A P ei o

随 着 电 子技 术 的 飞速 发 展 , 大量 的高 速 数 据 采 集 和在 线 测 试对 现 代 工业 测 控 系 统 和 仪 器 仪表 的 功 能 和 性 能 提 更 高

仲裁 控 制 。 内部 仲 裁 逻辑 控 制 提 供 以下 功 能 : 同一 地 址 单 对 元 访 问 的 时 序 控 制 ; 储 单 元 数 据 块 的 访 问权 限 分 配 : 令 存 信

要 求 。C U 并行 工 作 ( 单 片 机 系统 ) P 双 方式 得 到 广泛 应 用 。为

了使 2个 单 片机 能 够 快 速 有 效 交 换 信 息 ,充 分 利 用 系 统 资

源 , 用 双 口 R M 实 现存 储 器 共 享 是 目前 较 为 流行 的方 法 。 采 A

交 换 逻 辑 ( 如 中断 信 号 ) 。 口 R M 可 用 于 提高 R M 的 例 等 双 A A

a q i t n s se T e f n t n smu ain r s l r v e c re t e s o e d sg . e d s n r d c s te c mpe i f c s i y tm. h u ci i l t e u t p o e t o rc n s ft e i nT e i e u e h o lx t o u io o o s h h h g y cr u td s , n n a c s d sg e i i t n o f u a i t f r s u c s r d c s t e d s n c s a d s o tn h i i e i a d e h n e e in f x bl y a d c n g r b l y o e o r e , u e h e i o t n h r s t e c n g l i i i e g e

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IDT7026 的内部功能框图如图 1 所示。

IDT7026 的管脚分布如图 2 所示。各管脚的功能见表 1 所列。 3 工作原理 3.1 双端口数据存取工作原理

IDT7026 的核心部分是用于数据存储的存储器阵列,可为左右两个端口所共用。这样,位于两个端 口的左右处理单元就可共享一个存储器。当两个端口对双口 RAM 存取时,存在以下 4 种情况:

关键词:双口 RAM 高速并行接口 信号处理

1 概述 在高速数据采集和处理系统中,随着采样数据量的增大及信息处理任务的增加,对数据传送的要求

也越来越高。在系统或模块间如果没有能够高速传送数据的接口,则在数据传送时极易造成瓶颈堵塞现 象,从而影响整个系统对数据的处理能力。所以,高速并行数据接口的研制在信息处理系统中占有非常 重要的地位。利用高性能双口 RAM 能够方便地构成各种工作方式的高速数据传送接口,不管是在并行 处理网络中的数据共享,还是在流水方式中的高速数据传送中,高性能双口 RAM 都发挥着重要作用, 从而保证数据通路的畅通。

若两端口同时写入 0,仲裁逻辑电路只使得其中一个为 0,另一个为 1。标志器输出状态只能有一个 为 0,即共享存储器在某一时刻只能为其中一边的端口所使用。需要注意的是:使用标志锁存器传送数 据时,当某个端口完成对双口 RAM 的存取,或存取制造后,一定要再给标志锁存器写 1,否则双口 RAM 将一直被占用,另一端口无法对双口 RAM 进行存取。另外,对标志锁存器应“先写后读”,不要 “先读后写”,以避免出现争夺系统总线的现象。因为标志锁存器有 8 个,它最多可以把双口 RAM 划分 成 8 块,每块存储器的容量由用户任意设定。例如,可将容量均分为 4 块,每块有 2k×16bits 位的容量, 当左端口送数时,它先写 0 到标志器 0,若读取的状态值为 1,则说明第 1 个 2k 双口 RAM 正被右端口 使用;其可再写 0 到标志器 1,若读取的状态值为 0,则第 2 个双口 RAM 处于未被使用的空闲状态,左 端口可把其数据写入。若读取的状态值仍为 1,则可继续查询第 3、第 4 个 2k 双口 RAM,直至把数据写 入,图 4 为 IDT7026 的标志锁存器示意图。

3.2 标识器的工作原理

利用双口 RAM 的“BUSY”信号线,虽然可以保证左右两个端口能可靠地完成数据的传送,但当两个 端口对同一地址单元同时存取数据时,其中一个端噪口处于等待状态。对于高速接口电路来说,插入等 待状态会降低其数据通过率,这在某些情况下是不能接受的。IDT7026 提供有标识器电路,可把一个端 口使用双口 RAM 的状态传送到另一个端口。通过标识器电路传送数据,可实现数据的高速无等待状态 的传送。IDT7026 标识器电路实际上是 8 个锁存器,且与双口 RAM 相独立,用作 两个端口间的标志传送,以表明共享的 双口 RAM 是否在使用。在标识器工作模 式,控制脚 SEM 用作 8 个标志锁存器的 “片选”信号,地址线 A2~A0 用于 8 个标 志锁存器的寻址,数据线 D0 用作标志锁 存器状态的写入和读出,其工作状态见 表 2。

SEMR UBR LBR BUSYR

标志控制端 高 8 位存储单元选择端 低 8 位存储单元选择端 忙信号标志端 主或从存储器选择端 电源 地

表 2 标志锁存器的工作状态

操作 无操作 左端写 0 右端写 0 左端写 1 左端写 1 右端写 0 左端写 1 右端写 1 右端写 1 左端写 0 左端写 1

利用 IDT7026 的“BUSY”忙信号标志端可以实现多片 IDT7026 的级联,以扩展存储器位数和容量。 具体级联电路如图 3 所示。当 M/S 端为高电平时,该片 IDT7026 为主存储器,其 BUSY 端为输出。当该 片 IDT7026 为主存储器,其 BUSY 端为输出。当 M/S 端为低电平时,该片 IDT7026 为从存储器,其 BUSY 端为输入。

左端读出 1 0 0 1 1 0 1 1 1 0 1

左端口 D0~D15 1 0 1 1 1 0 1 1 0 1 1

右端读出 1 1 1 0 0 1 1 0 1 1 1

右端口 D0~D15 1 1 1 权 无变化 右端获得使用权 无变化 左端获得使用权 标志器空 右端获得使用权 标志器空 左端获得使用权 标志器空

高速双口 RAM IDT7026 的原理和应用

作者:合肥电子工程学院 刘春生 来源:《国外电子元器件》

摘要:IDT7026 是美国 IDT 公司开发研制的高速 16k×16bit 的双口静态 RAM。它 可允许两个端口同时进行高速读写数据,内含主/从控制脚,并具有标识器功能。 文中介绍了 IDT7026 的内部组成、功能及原理,并给出具体的应用电路框图。

4 应用

在研制通用雷达半实物仿真系统中,笔者用 TMS320C31 作为主处理器,用高速双口 RAMIDT7026 作为数据传送和数据共享的接口芯片,从而很好地完成了雷达信号的数据采集和处理任务。电路连接如 图 5 所示。

通常,雷达信号处理系统一次要处理几个或十几个重复周期的信号数据。在完成对数据的处理和检 测任务后,相应的数据要送入 PC 机进行适当的处理,并在 PC 机平 面位置显示器和距离显示器的窗口 上进行显示。信号处理系统输出的 数据可先写入双口 RAM。待数据 全部写入 IDT7026 后,系统再向 PC 机发出中断请求,PC 机响应中 断后,在中断服务子程序里把数据 读入内存,此时的双口 RAM 相当 于 PC 机的个 16 位高速并行接 口。

表 1 IDT7026 的管脚功能表

左端口 CEL R/WL OEL

A0L-A13L I/O0L-I/O15L

右端口 CER R/WR OER

A0R-A13R I/O0R-I/O15R

功能 片选信号端 读写信号端 输出控制端 地址线 数据输入输出端

SEML UBL LBL BUSYL

M/S Vcc GND

当左端口要使用双口 RAM 时,它先写 0 到标示锁存器,然后读标志锁存器的状态,若读到的值为 1,表明右端口正在使用双口 RAM 的相同单元。此时,左端口要么循环检查标志锁存器的状态,直到右 端口结束使用,再对双口 RAM 存取;要么撤消请求,即写 1 到标志锁存器,转去执行其它操作。同 理,若右端口使用双口 RAM 时,也按上述步骤进行。IDT7026 为了避免出现左右端口同时向标志锁存 器写入 0 而出现的错误,标志锁存器采用了如图 3 所示的电路结构。

(1)两个端口不同时对同一地址单元存取数据; (2)两个端口同时对同一地址单元读出数据; (3)两个端口同时对一地址单元写入数据;

(4)两个端口同时同一地址单 元,一个写入数据,另一个读出数 据。

在第一、第二种情况时,两个 端口的存取不会出现错误,第三种情 况会出现写入错误,第四种情况会出 现读出错误。为避免第三、四种错误 情况的出现,IDT7026 芯片设计有硬 件“BUSY”功能输出,其工作原理如 下:当左右端口不对同一地址单元存 取时,BUSY R=H,BUSY L=H,可 正常存储。当左右端口对同一地址单 元存储时,有一个端口的 BUSY=L,禁止数据的存取。此时,两个端口中,哪个存取诸求信号出现在 前,则其对应的 BUSY=H,允许存取;哪个存取请求信号出现在后,则其对应的 BUSY 求信号出现在 后,则其对应的 BUSY=L,禁止其写入数据。需要注意的是,两端口间的存取请求信号出现时间要相差 在 5ns 以上,否则仲裁逻辑无法判定哪一个端口的存取请求信号在前;在无法判定哪个端口先出现存取 请求信号时,控制线 BUSY L 和 BUSY R 只有一个为低电平,不会同时为低电平。这样,就能保证一个 对应于 BUSY=H 的端口能进行正常存取,对庆于 BUSY=L 的端口不存取,从而避免双端口存取出现错 误。