双口RAM系列.doc

双口RAM应用

IDT7026 的内部功能框图如图 1 所示。

IDT7026 的管脚分布如图 2 所示。各管脚的功能见表 1 所列。 3 工作原理 3.1 双端口数据存取工作原理

IDT7026 的核心部分是用于数据存储的存储器阵列,可为左右两个端口所共用。这样,位于两个端 口的左右处理单元就可共享一个存储器。当两个端口对双口 RAM 存取时,存在以下 4 种情况:

关键词:双口 RAM 高速并行接口 信号处理

1 概述 在高速数据采集和处理系统中,随着采样数据量的增大及信息处理任务的增加,对数据传送的要求

也越来越高。在系统或模块间如果没有能够高速传送数据的接口,则在数据传送时极易造成瓶颈堵塞现 象,从而影响整个系统对数据的处理能力。所以,高速并行数据接口的研制在信息处理系统中占有非常 重要的地位。利用高性能双口 RAM 能够方便地构成各种工作方式的高速数据传送接口,不管是在并行 处理网络中的数据共享,还是在流水方式中的高速数据传送中,高性能双口 RAM 都发挥着重要作用, 从而保证数据通路的畅通。

若两端口同时写入 0,仲裁逻辑电路只使得其中一个为 0,另一个为 1。标志器输出状态只能有一个 为 0,即共享存储器在某一时刻只能为其中一边的端口所使用。需要注意的是:使用标志锁存器传送数 据时,当某个端口完成对双口 RAM 的存取,或存取制造后,一定要再给标志锁存器写 1,否则双口 RAM 将一直被占用,另一端口无法对双口 RAM 进行存取。另外,对标志锁存器应“先写后读”,不要 “先读后写”,以避免出现争夺系统总线的现象。因为标志锁存器有 8 个,它最多可以把双口 RAM 划分 成 8 块,每块存储器的容量由用户任意设定。例如,可将容量均分为 4 块,每块有 2k×16bits 位的容量, 当左端口送数时,它先写 0 到标志器 0,若读取的状态值为 1,则说明第 1 个 2k 双口 RAM 正被右端口 使用;其可再写 0 到标志器 1,若读取的状态值为 0,则第 2 个双口 RAM 处于未被使用的空闲状态,左 端口可把其数据写入。若读取的状态值仍为 1,则可继续查询第 3、第 4 个 2k 双口 RAM,直至把数据写 入,图 4 为 IDT7026 的标志锁存器示意图。

双口RAM(精)

1 引言ARCNET协议应用于高速动车组列车通信网络时,产生中央控制单元处理器PXA270与专用协议控制器件COM20020相连的时序不匹配问题,若用通用数字电路模块进行时序转换,PXA270需占用PXA270专门的资源(CPU时间片)对COM20020的寄存器、数据包缓冲区进行低速读写访问(对COM20020的相邻两次读操作相隔至少300 ns),这样将增加处理器的负担。

基于这种现状,提出一种基于FPGA的PXA270外设时序转换接口设计方案,以FPGA为桥梁进行时序转换,并增加存储器直接访问DMA(Direct Memory Aeeess)功能,即FPGA自动完成数据包的收发工作,PXA270则只需高速读写访问FPGA中的同步双口RAM。

2 时序转换接口整体设计2.1 FPGA对外接白采用FPGA连接PXA270处理器与外设以解决PXA270处理器与外设直接连接时的时序不匹配问题。

如图1所示,FPGA从PXA270处理器获得地址总线(ADDRBUS[17..14], ADDRBUS[9..0]),片选信号(SYSCS5),读允许(SYSOE),写允许(SYSWE),并提供双向数据端口DATABUS[7..0] (可根据实际应用修改为32位或16位等),中断(interrupt);同时,FPGA向COM20020提供特定的总线接口,包括 COM20020_DS,COM20020_CS,COM20020_DIR,COM20020_DATABUS [7..0],COM20020_ADDRBUS[2..0]等。

2.2 内部功能实现PXA270和外设之间的连接是将FPGA中的双口RAM作为数据中转站,以此间接相连。

该设计由以下4个功能模块组成。

(1)PXA270对外设指定寄存器单次写操作PXA270先将所要写的数据送人双口RAM,然后PXA270向FPGA的命令寄存器写入对该外设指定寄存器的单次写指令,然后FP-GA根据接收到的命令将RAM中的数据输出到外设数据总线,同时给出对外设的写时序。

基于FPGA的双口RAM在双CPU通信中的应用及设计

摘要本文从现代通信系统的要求出发,详细研究了利用双口RAM来实现双 CPU之间高速的并行数据通信,指出了设计中需要解决的几个关键问题并给出了相应的解决方法。

随着电子技术的飞速发展,大量的高速数据采集和在线测试对现代工业测控系统和仪器仪表的功能和性能提出了更高的要求,双CPU并行工作双单片机系统方式得到广泛应用。

为了使2个单片机能够快速有效交换信息充分利用系统资源,采用双口RAM实现存储器共享是目前较为流行的方法。

大容量高速FPGA 器件具有集成度高、体积小、灵活可重配置、实验风险小等优点。

在复杂数字系统中得到越来越广泛的应用,数字电路设计采用 1 片FPGA 器件存储设备和一些电气接口匹配电路的解决方案已成为主流选择方案。

用FPGA来实现双口 RAM 的功能可以很好地解决并行性和速度问题,而且其灵活的可配置特性使得基于FPGA的双口RAM易于进行修改测试及系统升级可降低设计成本和缩短开发周期。

在嵌入式多CPU系统中,CPU间的通信可以采用串行、并行、系统总线及双口RAM等方式。

前三种通信方式存在的共同特点是传输速度慢,在大数据量的情况下可能造成数据处理时间延长,实时性差,甚至出现数据拥塞现象。

因此采用双口RAM的方式在系统间数据交换是一种简便有效的方法。

由于“基于FPGA的双口RAM”对我国嵌入式多CPU系统中CPU间的通信有重大影响,所以相关的研究比较多,综合起来主要是对“基于FPGA的双口RAM”背景下我国嵌入式多CPU系统中CPU间的通信所面临的机遇与挑战以及应对策略进行了论述。

本文主要研究的是在现代智能控制系统中,因为信息量的增加和实时性要求的提高,经常需要对信息或数据的高速采集和处理,提高控制系统的信息处理能力,避免极易造成数据处理中的“瓶颈”现象,在嵌入式多CPU系统中,数据通信问题成为制约其性能提高的主要因素,然而基于FPGA的双口RAM的高速数据通信和共享能力为解决在双CPU通信中的问题提供了方便。

双口RAM应用实例

双端口RAM在高速数据采集中的应用利用传统方法设计的高速数据采集系统由于集成度低、电路复杂,高速运行电路干扰大,电路可靠性低,难以满足高速数据采集工作的要求。

应用FPGA可以把数据采集电路中的数据缓存、控制时序逻辑、地址译码、总线接口等电路全部集成进一片芯片中,高集成性增强了系统的稳定性,为高速数据采集提供了理想的解决方案。

下面以一个高速数据采集系统为例介绍双端口RAM的应用。

该系统要求实现对频率为5MHz的信号进行采样,系统的计算处理需要对信号进行波形分析,信号采样时间为25μs。

根据设计要求,为保证采样波形不失真,A/D采样频率用80MHz,采样精度为8位数据宽度。

计算得出存储容量需要2K字节。

其系统结构框图如图3所示,图4给出了具体电路连接图。

根据设计要求,双端口RAM的LPM_WIDTH参数设置为8,LPM_WIDTHAD 参数设置为11(211=2048),使用读写使能端及读写时钟。

ADCLK、WRCLK和地址发生器的计数频率为80MHz。

A/D转换值对双端口RAM的写时序为顺序写方式,每完成一次A/D转换,存储一次数据,地址加1指向下一单元,因此写地址发生器(RAM_CONTROL)采用递增计数器实现,计数频率与ADCLK、WRCLK一致以保证数据写入时序的正确性。

写操作时序由地址和时钟发生器、A/D转换时钟和双端口RAM的写时钟产生。

停止采样时AD_STOP有效,写地址发生器停止计数,同时停止对RAM的写操作。

将地址发生器的计数值接至DSP总线可以获取采样的首尾指针。

地址发生器单元一般用(VHDL)语言编程实现,然后生成符号文件RAM_CONTROL在上层文件调用。

其部分VHDL语言程序如下:对双端口RAM的读操作采用存储器映像方式,其读出端口接DSP的外扩RAM 总线,DSP可随机读取双端口RAM的任一单元数据,以方便波形分析。

由于LPM_RAM_DP模块的读端数据总线q不具有三态特性,因此调用三态缓冲器74244,通过其将输出数据连接到DSP数据总线上。

双端口RAM在单片机系统中的应用

摘要阐述了双端口RAM使用的一种方法,当其应用于双机容错系统时,可简化电路,提高系统的可靠性。

本方案经实践证明是有效且实用的。

关键词双端口RAM 双机容错切换系统硬件冗余1引言在对产品可靠性要求高的系统中,往往需要硬件冗余。

有些设备不仅要求其在各种恶劣的天气下工作,而且要求长期不间断工作。

为提高可靠性往往采用双CPU系统。

平时主单片机系统工作,并将所处理的数据存储在外存,一旦主CPU系统出现故障,副CPU可切换上来,并利用公共外存的数据继续工作,而不需要人工干预。

这时双端口RAM做为外存就是两个CPU之间信息传递的最好渠道。

本文以美国IDT公司生产的IDT7130为例,阐述双端口RAM在最常用的80C31双机系统中的应用。

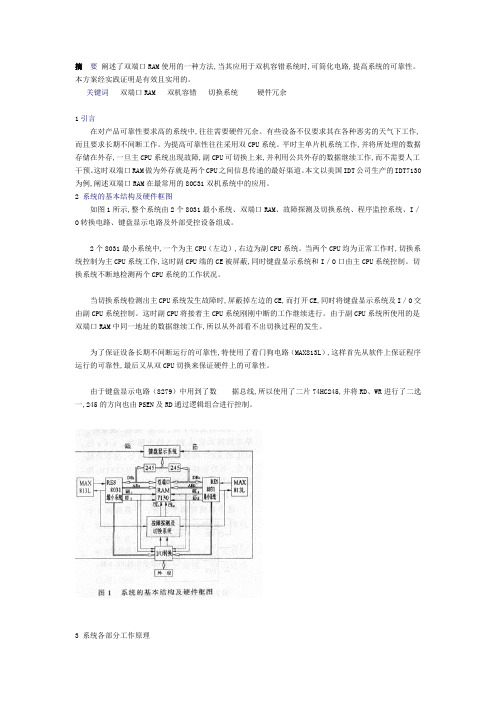

2 系统的基本结构及硬件框图如图1所示,整个系统由2个8031最小系统、双端口RAM、故障探测及切换系统、程序监控系统、I/O转换电路、键盘显示电路及外部受控设备组成。

2个8031最小系统中,一个为主CPU(左边),右边为副CPU系统。

当两个CPU均为正常工作时,切换系统控制为主CPU系统工作,这时副CPU端的CE被屏蔽,同时键盘显示系统和I/O口由主CPU系统控制。

切换系统不断地检测两个CPU系统的工作状况。

当切换系统检测出主CPU系统发生故障时,屏蔽掉左边的CE,而打开CE,同时将键盘显示系统及I/O交由副CPU系统控制。

这时副CPU将接着主CPU系统刚刚中断的工作继续进行。

由于副CPU系统所使用的是双端口RAM中同一地址的数据继续工作,所以从外部看不出切换过程的发生。

为了保证设备长期不间断运行的可靠性,特使用了看门狗电路(MAX813L),这样首先从软件上保证程序运行的可靠性,最后又从双CPU切换来保证硬件上的可靠性。

由于键盘显示电路(8279)中用到了数据总线,所以使用了二片74HC245,并将RD、WR进行了二选一,245的方向也由PSEN及RD通过逻辑组合进行控制。

一款双口RAM芯片介绍

双口RAM引言由工业计算机通过PCI总线控制的前端数据采集系统在工业控制领域中得到了广泛的应用,一般的数据传送系统在大数据量的情况下会造成数据堵塞现象。

在系统设计的过程中经过多方面的比较,最后采用高数双口RAM构成的高速数据交换接口成功地解决了此问题。

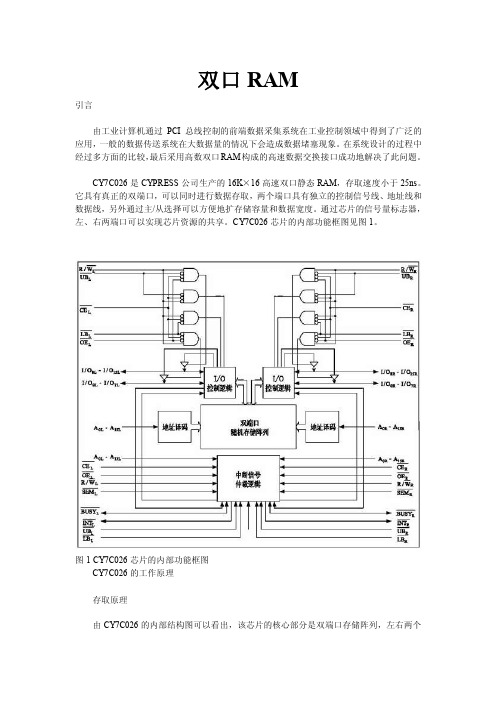

CY7C026是CYPRESS公司生产的16K×16高速双口静态RAM,存取速度小于25ns。

它具有真正的双端口,可以同时进行数据存取,两个端口具有独立的控制信号线、地址线和数据线,另外通过主/从选择可以方便地扩存储容量和数据宽度。

通过芯片的信号量标志器,左、右两端口可以实现芯片资源的共享。

CY7C026芯片的内部功能框图见图1。

图1 CY7C026芯片的内部功能框图CY7C026的工作原理存取原理由CY7C026的内部结构图可以看出,该芯片的核心部分是双端口存储阵列,左右两个端口可以共用该存储阵列,并且拥有各自的控制线,在单独存取数据时,和普通的RAM相同。

同时读取不同存储空间的数据和同时读取相同数据空间的数据时,左右端口可以同时进行。

若同时对相同的数据空间做写操作,或一端口对一数据空间作读操作的同时另一端口对该数据空间作写操作,左右端口将发生冲突。

为此,CY7C026通过BUSY管脚来处理这两种情况。

当左右端口对不同存储空间进行读写操作时,可同时存取。

此时,左右端口的BUSY 信号同时置高。

若对同一存储空间同时进行存储操作时,哪一端的存储请求信号先出现,则该端的BUSY信号置高,允许存储。

哪一端的存储信号出现在后,则这一端BUSY信号置低,禁止存储。

值得注意的是,左右两端存取请求信号出现的时间差必须大于5ns,不然仲裁逻辑无法判断哪一边的存取请求信号出现在前。

如果出现两端存取请求信号出现的时间差小于5ns 的情况,仲裁逻辑将一边的BUSY信号置高,将另一边的BUSY信号置低,从而保证两个端口一个执行数据存储,另一端口进行数据读取,避免了冲突。

双口RAM

双口RAM1.模块功能:双口RAM模块主要采用IDT7132等器件,它是一种特殊的数据存储芯片,它既可以用于单片机存储大容量的数据,也可以以双口RAM为共享存储器来实现两个处理器之间的通信和数据传输。

双口RAM的优点是提供了两条完全独立的端口,每个端口都有完整的地址、数据和控制总线,允许两个CPU对双端口存储器的同一单元进行同时存取;具有两套完全独立的终端逻辑来实现两个CPU 之间的握手控制信号;具有两套独立的“忙”逻辑,保证两个CPU同时对同一单元进行读/写操作的正确性。

对于单个CPU而言,双口RAM同普通RAM没有什么明显的区别。

本模块原理图见图1。

图13.主要器件:(1)IDT7132:(a)器件功能:IDT7132是高速2k*8端口静态RAM,可提供图2.1.3 IDT7132引脚图两个拥有独立的控制总线、地址总线和I/O总线端口,允许CPU独立访问内部的任何存储单元。

当/CE 引脚出现下降沿时,选中DPRAM即可通过控制OE 或R/W来访问内部存储单元。

(b) 器件引脚:IDT7132的引脚图如图2所示。

/CE、/CER:(左、右)片选控制信号。

R/WL、R/WR:(左、右)读写控制信号。

/OEL、/OER:(左、右)使能控制信号。

/BUSYL、/BUSYR:(左、右)繁忙查询控制信号。

A0L—A9L、A0R—A9R:(左、右)地址总线。

I/O0L—I/O7L、I/O0R—I/O7R:(左、右)输入/输出总线。

VCC:电源。

(c) 工作原理:IDT7132的工作时序如图3所示。

它与RAM的读写时序非常类似。

当CPU选中DPRAM时/CE引脚出现下降沿,当控制线/OE为高且R/W为低时,CPU对内部存储单元进行写操作;而当控制线OE为低且R/W为高时,CPU对内部存储单元进行读操作。

当外部CPU通过两个端口对双口RAM内部的同一个存储单元进行操作时,系统将出现竞图 2争。

这种竞争一般有如下两种模式:(1)如果两个端口的总线访问地址相同,并先于片选信号/CE有效,则片内逻辑将在CEL与CER之间发生竞争。

双口RAM

3.3V 4K/8K/16K x 16/18 Dual-Port Static RAMCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AVFeatures•True dual-ported memory cells which allowsimultaneous access of the same memory location •4/8/16K × 16 organization (CY7C024AV/025AV/026AV)•4/8K × 18 organization (CY7C0241AV/0251AV)•16K × 18 organization (CY7C036AV)•0.35-micron CMOS for optimum speed/power •High-speed access: 20 and 25 ns •Low operating power—Active: I CC = 115 mA (typical)—Standby: I SB3 = 10 µA (typical)•Fully asynchronous operation •Automatic power-down•Expandable data bus to 32/36 bits or more using Master/Slave chip select when using more than one device•On-chip arbitration logic•Semaphores included to permit software handshaking between ports•INT flag for port-to-port communication •Separate upper-byte and lower-byte control •Pin select for Master or Slave•Commercial and industrial temperature ranges •Available in 100-pin TQFPNotes:1.I/O 8–I/O 15 for x16 devices; I/O 9–I/O 17 for x18 devices.2.I/O 0–I/O 7 for x16 devices; I/O 0–I/O 8 for x18 devices.3.A 0–A 11 for 4K devices; A 0–A 12 for 8K devices; A 0–A 13 for 16K devices.4.BUSY is an output in master mode and an input in slave mode.R/W L OE LI/O 8/9L –I/O 15/17LI/O Control Address DecodeA 0L –A 11/12/13L CE L OE L R/W LBUSY L I/O ControlCE L Interrupt Semaphore ArbitrationSEM L INT L M/SUB LLB L I/O 0L –I/O 7/8LR/W R OE RI/O 8/9L –I/O 15/17RCE R UB RLB R I/O 0L –I/O 7/8RUB L LB LLogic Block DiagramA 0L –A 11/1213LTrue Dual-Ported RAM Array A 0R –A 11/12/13RCE R OE R R/W R BUSY R SEM RINT R UB R LB RAddress DecodeA 0R –A 11/12/13R[1][1][2][2][4][4]12/13/148/98/912/13/148/98/912/13/1412/13/14[3][3][3][3]Pin ConfigurationsNotes:5.A12L on the CY7C025AV.6.A12R on the CY7C025AV.Top View100-Pin TQFP100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NCNCNCNCA5LA4LINT LA2LA0LLGNDINT RA0RA1L NCNCNCNCI/O10LI/O11LI/O15LV CCGNDI/O1RI/O2RV CC9091A3LM/SR I/O14LGNDI/O12LI/O13LA1RA2RA3RA4RNCNCNCNCI/O3RI/O4RI/O5RI/O6RNCNCNCNC18192021222324258382818079787776585756555453525143444546 47484950I/O9LI/O8LI/O7LI/O6LI/O5LI/O4LI/O3LI/O2LGNDI/O1LI/OLOELSEM LVCCCELUBLLBLNCA11LA1LA9LA8LA7LA6LI/O0RI/O7RI/O8RI/O9RI/O1RI/O11RI/O12RI/O13RI/O14RGNDI/O15RŒRRWRGNDSEMRCERUBRLBRNCA11RA1RA9RA8RA7RA6RA5RCY7C024AV (4K × 16)R/W L[5][6CY7C025AV (8K × 16)Notes:7.A 12L on the CY7C0251AV.8.A 12R on the CY7C0251AVC.Pin Configurations (continued)Top View100-Pin TQFP100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NC NC NC NC A 5L A 4L INT L A 2L A 0L BUSY L GND INT R A 0R A 1L NC NC I/O 11L I/O 12L I/O 16L V CC GND I/O 1R I/O 2R V CC 9091A 3L M/S BUSY R I/O 15L GND I/O 13L I/O 14L A 1R A 2R A 3R A 4R NC NC NC NCI/O 3R I/O 4R I/O 5R I/O 6R NC NC18192021222324258382818079787776585756555453525143444546 47484950I /O 9LI /O 7LI /O 6LI /O 5LI /O 4LI /O 3LI /O 2LI /O 10LG N DI /O 1LI /O 0LO E LS E M LV C CC E LU B LL B LN C A 11LA 10LA 9LA 8LA 7LA 6LI/O 0R I /O 7RI /O 16RI /O 9RI /O 10RI /O 11RI /O 12RI /O 13RI /O 14RG N D I /O 15RO E RR W R G N D S E M R C E R U B R L B R N C A 11R A 10R A 9R A 8RA 7R A 6RA 5RCY7C0241AV (4K × 18)I/O 8L I/O 17L I/O 8R I/O 17RR /W L[8][7]1329291908485878688898382817678777980939495969798991005960616766646563626869707573747271NC NC NC A6L A5L A4L INTL A2L A0L GND M/S A0R A1R A1L A3L BUSYR INTR A2R A3R A4R A5R NC NC NCBUSYL 5857565554535251CY7C026AV (16K × 16)NC NC NC NC I/O10L I/O11L I/O15L I/O13L I/O14L GND I/O0R VCC I/O3R GND I/O12L I/O1R I/O2R I/O4R I/O5R I/O6R NC NC NC NCVCC 17161591012111314876451819202122232425I /O 9L I /O 8L I /O 7L I /O 6L I /O 5L I /O 4L I /O 0L I /O 2L I /O 1L V C C R W L U B L L B L G N D I /O 3L S E M L C E L A 113L A 12L A 11L A 10L A 9L A 8L A 7LO E L 3435364241394038374344455048494746A 6R A 7R A 8R A 9R A 10R A 11R C E R A 13R U B R G N D R W R G N D I /O 14R L B R A 12R O E R I /O 15R I /O 13R I /O 12R I /O 11R I /O 10R I /O 9R I /O 8R I /O 7R S E M R 3332313029282726CY7C0251AV (8K × 18)Pin Configurations (continued)Top View100-Pin TQFP 100 9997989623142415960611213151416454039959417269108761127283029313235343637383367666465636268697075737472718988868785939284NC NC NC A 5L A 4L INT L A 2L A 0L BUSY L GND INT R A 0R A 1L NC NC I/O 11L I/O 12L I/O 16L V CC GND I/O 1R I/O 2R V CC 9091A 3L R I/O 15L GND I/O 13L I/O 14L A 1R A 2R A 3R A 4R NC NC NCI/O 3R I/O 4R I/O 5R I/O 6R NC NC18192021222324258382818079787776585756555453525143444546 47484950I /O 9LI /O 7LI /O 6LI /O 5LI /O 4LI /O 3LI /O 2LI /O 10LG N DI /O 1LI /O 0LO E LS E M LV C CC E LU B LL B L A 11LA 10LA 9LA 8LA 7L A 6LI/O 0R I /O 7RI /O 16RI /O 9RI /O 10RI /O 11RI /O 12RI /O 13RI /O 14RG N D I /O 15RO E R R W R G N D S E M RC E RU B RL B RA 11RA 10RA 9R A 8RA 7RA 6RA 5RI/O 8L I/O 17L I/O 8R I/O 17RR /W LCY7C036AV (16K × 18)A 13L A 13R A 12LA 12RSelection GuideCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV-20CY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV-25Unit Maximum Access Time 2025ns Typical Operating Current 120115mA Typical Standby Current for I SB1(Both ports TTL Level)3530mA Typical Standby Current for I SB3(Both ports CMOS Level)1010µAArchitectureThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV consist of an array of 4K, 8K, and 16K words of 16 and 18 bits each of dual-port RAM cells, I/O and address lines, and control signals (CE, OE, R/W). These control pins permit independent access for reads or writes to any location in memory. To handle simultaneous writes/reads to the same location, a BUSY pin is provided on each port. Two Interrupt (INT) pins can be utilized for port-to-port communication. Two Semaphore (SEM) control pins are used for allocating shared resources. With the M/S pin, the devices can function as a master (BUSY pins are outputs) or as a slave (BUSY pins are inputs). The devices also have an automatic power-down feature controlled by CE. Each port is provided with its own output enable control (OE), which allows data to be read from the device.Functional DescriptionThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV /036AV are low-power CMOS 4K, 8K, and 16K ×16/18 dual-port static RAMs. Various arbitration schemes are included on the devices to handle situations when multiple processors access the same piece of data. Two ports are provided, permitting independent, asynchronous access for reads and writes to any location in memory. The devices can be utilized as standalone 16/18-bit dual-port static RAMs or multiple devices can be combined in order to function as a 32/36-bit or wider master/slave dual-port static RAM. An M/S pin is provided for implementing 32/36-bit or wider memory applications without the need for separate master and slave devices or additional discrete logic. Application areas include interprocessor/multiprocessor designs, communications status buffering, and dual-port video/graphics memory. Each port has independent control pins: Chip Enable (CE), Read or Write Enable (R/W), and Output Enable (OE). Two flags are provided on each port (BUSY and INT). BUSY signals that the port is trying to access the same location currently being accessed by the other port. The Interrupt flag (INT) permits communication between ports or systems by means of a mail box. The semaphores are used to pass a flag, or token, from one port to the other to indicate that a shared resource is in use. The semaphore logic is comprised of eight shared latches. Only one side can control the latch (semaphore) at any time. Control of a semaphore indicates that a shared resource is in use. An automatic power-down feature is controlled independently on each port by a Chip Select (CE) pin.The CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV are available in 100-pin Thin Quad Plastic Flatpacks (TQFP).Write OperationData must be set up for a duration of t SD before the rising edge of R/W in order to guarantee a valid write. A write operation is controlled by either the R/W pin (see Write Cycle No. 1 waveform) or the CE pin (see Write Cycle No. 2 waveform). Required inputs for non-contention operations are summarized in Table1.If a location is being written to by one port and the opposite port attempts to read that location, a port-to-port flowthrough delay must occur before the data is read on the output; otherwise the data read is not deterministic. Data will be valid on the port t DDD after the data is presented on the other port. Read OperationWhen reading the device, the user must assert both the OE and CE pins. Data will be available t ACE after CE or t DOE after OE is asserted. If the user wishes to access a semaphore flag, then the SEM pin must be asserted instead of the CE pin, and OE must also be asserted.Pin DefinitionsLeft Port Right Port DescriptionCE L CE R Chip Enable.R/W L R/W R Read/Write Enable.OE L OE R Output Enable.A0L–A13L A0R–A13R Address (A0–A11 for 4K devices; A0–A12 for 8K devices; A0–A13 for16K).I/O0L–I/O17L I/O0R–I/O17R Data Bus Input/Output.SEM L SEM R Semaphore Enable.UB L UB R Upper Byte Select (I/O8–I/O15 for x16 devices; I/O9–I/O17 for x18devices).LB L LB R Lower Byte Select (I/O0–I/O7 for x16 devices; I/O0–I/O8 for x18devices).INT L INT R Interrupt Flag.BUSY L BUSY R Busy Flag.M/S Master or Slave Select.V CC Power.GND Ground.NC No Connect.InterruptsThe upper two memory locations may be used for message passing. The highest memory location (FFF for the CY7C024AV/41AV, 1FFF for the CY7C025AV/51AV, 3FFF for the CY7C026AV/36AV) is the mailbox for the right port and the second-highest memory location (FFE for the CY7C024AV/ 41AV, 1FFE for the CY7C025AV/51AV, 3FFE for the CY7C026AV/36AV) is the mailbox for the left port. When one port writes to the other port’s mailbox, an interrupt is generated to the owner. The interrupt is reset when the owner reads the contents of the mailbox. The message is user defined.Each port can read the other port’s mailbox without resetting the interrupt. The active state of the busy signal (to a port) prevents the port from setting the interrupt to the winning port. Also, an active busy to a port prevents that port from reading its own mailbox and, thus, resetting the interrupt to it.If an application does not require message passing, do not connect the interrupt pin to the processor’s interrupt request input pin.The operation of the interrupts and their interaction with Busy are summarized in Table2.BusyThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV provide on-chip arbitration to resolve simultaneous memory location access (contention). If both ports’ CEs are asserted and an address match occurs within t PS of each other, the busy logic will determine which port has access. If t PS is violated, one port will definitely gain permission to the location, but it is not predictable which port will get that permission. BUSY will be asserted t BLA after an address match or t BLC after CE is taken LOW.Master/SlaveA M/S pin is provided in order to expand the word width by configuring the device as either a master or a slave. The BUSY output of the master is connected to the BUSY input of the slave. This will allow the device to interface to a master device with no external components. Writing to slave devices must be delayed until after the BUSY input has settled (t BLC or t BLA), otherwise, the slave chip may begin a write cycle during a contention situation. When tied HIGH, the M/S pin allows the device to be used as a master and, therefore, the BUSY line is an output. BUSY can then be used to send the arbitration outcome to a slave.Semaphore OperationThe CY7C024AV/025AV/026AV and CY7C0241AV/0251AV/ 036AV provide eight semaphore latches, which are separate from the dual-port memory locations. Semaphores are used to reserve resources that are shared between the two ports. The state of the semaphore indicates that a resource is in use. For example, if the left port wants to request a given resource, it sets a latch by writing a zero to a semaphore location. The left port then verifies its success in setting the latch by reading it. After writing to the semaphore, SEM or OE must be deasserted for t SOP before attempting to read the semaphore. The semaphore value will be available t SWRD + t DOE after the rising edge of the semaphore write. If the left port was successful (reads a zero), it assumes control of the shared resource, otherwise (reads a one) it assumes the right port has control and continues to poll the semaphore. When the right side has relinquished control of the semaphore (by writing a one), the left side will succeed in gaining control of the semaphore. If the left side no longer requires the semaphore, a one is written to cancel its request.Semaphores are accessed by asserting SEM LOW. The SEM pin functions as a chip select for the semaphore latches (CE must remain HIGH during SEM LOW). A0–2 represents the semaphore address. OE and R/W are used in the same manner as a normal memory access. When writing or reading a semaphore, the other address pins have no effect.When writing to the semaphore, only I/O0 is used. If a zero is written to the left port of an available semaphore, a one will appear at the same semaphore address on the right port. That semaphore can now only be modified by the side showing zero (the left port in this case). If the left port now relinquishes control by writing a one to the semaphore, the semaphore will be set to one for both sides. However, if the right port had requested the semaphore (written a zero) while the left port had control, the right port would immediately own the semaphore as soon as the left port released it. Table 3 shows sample semaphore operations.When reading a semaphore, all sixteen/eighteen data lines output the semaphore value. The read value is latched in an output register to prevent the semaphore from changing state during a write from the other port. If both ports attempt to access the semaphore within t SPS of each other, the semaphore will definitely be obtained by one side or the other, but there is no guarantee which side will control the semaphore.Table 1.Non-Contending Read/WriteInputs OutputsCE R/W OE UB LB SEM I/O9–I/O17I/O0–I/O8OperationH X X X X H High Z High Z Deselected: Power-DownX X X H H H High Z High Z Deselected: Power-Down L L X L H H Data In High Z Write to Upper Byte Only L L X H L H High Z Data In Write to Lower Byte Only L L X L L H Data In Data In Write to Both BytesL H L L H H Data Out High Z Read Upper Byte OnlyL H L H L H High Z Data Out Read Lower Byte OnlyL H L L L H Data Out Data Out Read Both BytesX X H X X X High Z High Z Outputs DisabledH H L X X L Data Out Data Out Read Data in Semaphore FlagX H L H H L Data Out Data Out Read Data in Semaphore FlagH X X X L Data In Data In Write D IN0 into Semaphore FlagX X H H L Data In Data In Write D IN0 into Semaphore Flag L X X L X L Not AllowedL X X X L L Not AllowedTable 2.Interrupt Operation Example (assumes BUSY L = BUSY R = HIGH)[9]Left Port Right Port Function R/W L CE L OE L A0L–13L INT L R/W R CE R OE R A0R–13R INT R Set Right INT R Flag L L X FFF[12]X X X X X L[11] Reset Right INT R Flag X X X X X X L L FFF (or 1/3FFF)H[10] Set Left INT L Flag X X X X L[10]L L X1FFE (or 1/3FFE)X Reset Left INT L Flag X L L1FFE[12]H[11]X X X X X Table 3.Semaphore Operation ExampleFunction I/O0–I/O17 Left I/O0–I/O17 Right StatusNo action11Semaphore-freeLeft port writes 0 to semaphore01Left Port has semaphore tokenRight port writes 0 to semaphore01No change. Right side has no write access to semaphore Left port writes 1 to semaphore10Right port obtains semaphore tokenLeft port writes 0 to semaphore10No change. Left port has no write access to semaphore Right port writes 1 to semaphore01Left port obtains semaphore tokenLeft port writes 1 to semaphore11Semaphore-freeRight port writes 0 to semaphore10Right port has semaphore tokenRight port writes 1 to semaphore11Semaphore freeLeft port writes 0 to semaphore01Left port has semaphore tokenLeft port writes 1 to semaphore11Semaphore-freeNotes:9.See Functional Description for specific highest memory locations by device.10.If BUSY R=L, then no change.11.If BUSY L=L, then no change.12.See Functional Description for specific addresses by device.Maximum Ratings [13](Above which the useful life may be impaired. For user guide-lines, not tested.)Storage Temperature .................................–65°C to +150°C Ambient Temperature withPower Applied.............................................–55°C to +125°C Supply Voltage to Ground Potential...............–0.5V to +4.6V DC Voltage Applied toOutputs in High-Z State..........................–0.5V to V CC + 0.5V DC Input Voltage[14]...............................–0.5V to V CC + 0.5V Output Current into Outputs (LOW).............................20 mA Static Discharge Voltage.......................................... > 2001V Latch-up Current.................................................... > 200 mA Operating RangeRange Ambient Temperature V CC Commercial0°C to +70°C 3.3V ± 300 mV Industrial[15]–40°C to +85°C 3.3V ± 300 mVElectrical Characteristics Over the Operating RangeParameter DescriptionCY7C024AV/025AV/026AVCY7C0241AV/0251AV/036AVUnit -20-25Min.Typ.Max.Min.Typ.Max.V OH Output HIGH Voltage (V CC=3.3V) 2.4 2.4V V OL Output LOW Voltage0.40.4V V IH Input HIGH Voltage 2.0 2.0V V IL Input LOW Voltage0.80.8V I OZ Output Leakage Current–1010–1010µA I IX Input Leakage Current–1010–1010µAI CC Operating Current (V CC = Max., I OUT=0mA) Outputs Disabled Com’l.120175115165mA Ind.[15]135185mAI SB1Standby Current (Both Ports TTL Level)CE L & CE R≥ V IH, f = f MAX Com’l.35453040mA Ind.[15]4050mAI SB2Standby Current (One Port TTL Level) CE L| CE R≥ V IH, f = f MAX Com’l.751106595mA Ind.[15]75105mAI SB3Standby Current (Both Ports CMOS Level)CE L & CE R≥ V CC−0.2V, f = 0Com’l.1050010500µA Ind.[15]10500µAI SB4Standby Current (One Port CMOS Level)CE L | CE R≥ V IH, f = f MAX[16]Com’l.70956080mA Ind.[15]7090mACapacitance[17]Parameter Description Test Conditions Max.UnitC IN Input Capacitance T A = 25°C, f = 1 MHz,V CC = 3.3V 10pFC OUT Output Capacitance10pF Notes:13.The Voltage on any input or I/O pin can not exceed the power pin during power-up.14.Pulse width < 20 ns.15.Industrial parts are available in CY7C026AV and CY7C036AV only.16.f MAX = 1/t RC = All inputs cycling at f = 1/t RC (except output enable). f = 0 means no address or control lines change. This applies only to inputs at CMOS level standby I SB3.17.Tested initially and after any design or process changes that may affect these parameters.AC Test Loads and Waveforms3.0V GND90%90%10%3ns3ns10%ALL INPUT PULSES(a)Normal Load (Load 1)R1=590Ω3.3VOUTPUT R2=435ΩC =30pFV TH =1.4VOUTPUTC =30pF(b)Thévenin Equivalent (Load 1)(c)Three-State Delay (Load 2)R1=590ΩR2=435Ω3.3VOUTPUTC =5pFR TH =250Ω≤≤including scope and jig)(Used for t LZ , t HZ , t HZWE , and t LZWE Switching Characteristics Over the Operating Range [18]Parameter DescriptionCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV Unit-20-25Min.Max.Min.Max.Read Cycle t RC Read Cycle Time 2025ns t AA Address to Data Valid2025ns t OHA Output Hold From Address Change 33ns t ACE [19]CE LOW to Data Valid 2025ns t DOEOE LOW to Data Valid 1213ns t LZOE [20, 21, 22]OE Low to Low Z 33ns t HZOE [20, 21, 22]OE HIGH to High Z 1215ns t LZCE [20, 21, 22]CE LOW to Low Z 33ns t HZCE [20, 21, 22]CE HIGH to High Z 1215ns t PU [22]CE LOW to Power-Up 0ns t PD [22]CE HIGH to Power-Down 2025ns t ABE [19]Byte Enable Access Time2025nsWrite Cycle t WC Write Cycle Time 2025ns t SCE [19]CE LOW to Write End 1520ns t AW Address Valid to Write End 1520ns t HA Address Hold From Write End 00ns t SA [19]Address Set-up to Write Start 00ns t PWE Write Pulse Width 1520ns t SDData Set-up to Write End1515nsNotes:18.Test conditions assume signal transition time of 3 ns or less, timing reference levels of 1.5V, input pulse levels of 0 to 3.0V, and output loading of the specifiedI OI /I OH and 30-pF load capacitance.19.SCE time.20.At any given temperature and voltage condition for any given device, t HZCE is less than t LZCE and t HZOE is less than t LZOE .21.Test conditions used are Load 3.22.This parameter is guaranteed but not tested. For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timingwith Busy waveform.Data Retention ModeThe CY7C024AV/025AV/ 026AV and CY7C0241AV/ 0251AV/036AV are designed with battery backup in mind. Data retention voltage and supply current are guaranteed over temperature. The following rules ensure data retention:1.Chip Enable (CE) must be held HIGH during data retention, within V CC to V CC – 0.2V.2.CE must be kept between V CC – 0.2V and 70% of V CC during the power-up and power-down transitions.3.The RAM can begin operation >t RC after V CC reaches the minimum operating voltage (3.0V).Notes:23.For information on port-to-port delay through RAM cells from writing port to reading port, refer to Read Timing with Busy waveform.24.Test conditions used are Load 2.25.t BDD is a calculated parameter and is the greater of t WDD –t PWE (actual) or t DDD –t SD (actual).26.CE = V CC , V in = GND to V CC , T A = 25°C. This parameter is guaranteed but not tested.t HDData Hold From Write Endns t HZWE [21, 22]R/W LOW to High Z 1215ns t LZWE [21, 22]R/W HIGH to Low Z3ns t WDD [23]Write Pulse to Data Delay4550ns t DDD [23]Write Data Valid to Read Data Valid 3035ns Busy Timing [24]t BLA BUSY LOW from Address Match 2020ns t BHA BUSY HIGH from Address Mismatch 2020ns t BLC BUSY LOW from CE LOW 2020ns t BHC BUSY HIGH from CE HIGH 1717ns t PS Port Set-up for Priority 55ns t WB R/W HIGH after BUSY (Slave)00ns t WH R/W HIGH after BUSY HIGH (Slave)1517ns t BDD [25]BUSY HIGH to Data Valid 2025ns Interrupt Timing [24]t INS INT Set Time 2020ns t INR INT Reset Time2020ns Semaphore Timingt SOP SEM Flag Update Pulse (OE or SEM)1012ns t SWRD SEM Flag Write to Read Time 55ns t SPS SEM Flag Contention Window 55ns t SAASEM Address Access Time2025nsSwitching Characteristics Over the Operating Range (continued)[18]Parameter DescriptionCY7C024AV/025AV/026AV CY7C0241AV/0251AV/036AV Unit -20-25Min.Max.Min.Max.TimingParameter Test Conditions [26]Max.Unit ICC DR1@ VCC DR = 2V50µAData Retention Mode3.0V3.0VV CC > 2.0VV CC to V CC –0.2VV CCCEt RCV IHSwitching WaveformsNotes:27.R/W is HIGH for read cycles.28.Device is continuously selected CE = V IL and UB or LB = V IL . This waveform cannot be used for semaphore reads.29.OE = V IL .30.Address valid prior to or coincident with CE transition LOW.31.To access RAM, CE = V IL , UB or LB = V IL , SEM = V IH . T o access semaphore, CE = V IH , SEM = V IL .t RCt AAt OHADATA VALIDPREVIOUS DATA VALIDDATA OUTADDRESSt OHARead Cycle No.1 (Either Port Address Access)[27, 28, 29]t ACEt LZOEt DOEt HZOEt HZCEDATA VALIDt LZCEt PUt PDI SBI CCDATA OUTOECE and LB or UBCURRENTRead Cycle No.2 (Either Port CE/OE Access)[27, 30, 31]UB or LBDATA OUTt RCADDRESSt AAt OHACEt LZCEt ABEt HZCEt HZCEt ACE t LZCERead Cycle No. 3 (Either Port)[27, 29, 30, 31]Notes:32.R/W must be HIGH during all address transitions.33. A write occurs during the overlap (t SCE or t PWE ) of a LOW CE or SEM and a LOW UB or LB.34.t HA is measured from the earlier of CE or R/W or (SEM or R/W) going HIGH at the end of write cycle.35.If OE is LOW during a R/W controlled write cycle, the write pulse width must be the larger of t PWE or (t HZWE + t SD ) to allow the I/O drivers to turn off and data to be placed onthe bus for the required t SD . If OE is HIGH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified t PWE .36.To access RAM, CE = V IL , SEM = V IH .37.To access upper byte, CE = V IL , UB = V IL , SEM = V IH .T o access lower byte, CE = V IL , LB = V IL , SEM = V IH .38.Transition is measured ±500 mV from steady state with a 5-pF load (including scope and jig). This parameter is sampled and not 100% tested.39.During this period, the I/O pins are in the output state, and input signals must not be applied.40.If the CE or SEM LOW transition occurs simultaneously with or after the R/W LOW transition, the outputs remain in the high-impedance state.Switching Waveforms (continued)t AWt WCt PWE t HDt SDt HACER/WOEDATAOUTDATA INADDRESSt HZOE t SAt HZWE t LZWEWrite Cycle No.1: R/W Controlled Timing [32, 33, 34, 35][38][38][35][36, 37]NOTE 39NOTE 39t AWt WCt SCE t HDt SDt HACER/WDATA INADDRESSt SAWrite Cycle No. 2: CE Controlled Timing [32, 33, 34, 40][36, 37]Notes:41.CE = HIGH for the duration of the above timing (both write and read cycle).42.I/O 0R = I/O 0L = LOW (request semaphore); CE R = CE L = HIGH.43.Semaphores are reset (available to both ports) at cycle start.44.If t SPS is violated, the semaphore will definitely be obtained by one side or the other, but which side will get the semaphore is unpredictable.Switching Waveforms (continued)t SOPt SAAVALID ADRESS VALID ADRESSt HD DATA IN VALID DATA OUT VALIDt OHAt AWt HAt ACEt SOPt SCEt SDt SAt PWEt SWRDt DOEWRITE CYCLEREAD CYCLEOER/WI/O 0SEMA 0–A 2Semaphore Read After Write Timing, Either Side [41]MATCHt SPSA 0L –A 2LMATCHR/W L SEM LA 0R –A 2RR/W R SEM RTiming Diagram of Semaphore Contention [42, 43, 44]。

基于双口RAM的单片机通信

目录1.绪论 (2)1.1课题的提出 (2)1.2 双端口RAM概述 (2)1.3本论文主要研究的内容 (4)2. 基于双端口RAM的单片机间通信概述 (4)2.1双端口RAM的发展过程、存储原理 (4)2.1.1.双端口RAM的发展过程 (4)2.1.2.双端口RAM的基本存储原理 (5)2.1.3.双端口RAM的中断逻辑功能 (6)2.1.4.标识器逻辑及主/从模式 (6)2.2双端口RAM的应用 (7)2.3接口电路实现方案概述 (8)2.3.1. 基于CY7C133双口RAM (8)2.3.2. ISA总线与IDT7025的接口 (9)2.3.3. IDT7026实现高速并口缓存的接口电路 (10)2.4初期主要元器件的选择 (11)2.6双口RAMIDT7005S概述 (11)2.7其它主要器件概述 (17)3.系统硬件接口及实现 (18)3.1引言 (18)3.2 89C52单片机简介 (18)3.3 单片机与双口RAM的接口电路简介 (23)3.4硬件的调试 (26)4.系统软件及实现 (27)4.1引言 (27)4.2双口RAM的地址空间分配和旗语、中断逻辑 (28)4.3软件主要部分流程图 (30)4.4系统主要模块程序说明 (33)5.结论 (41)主要参考文献: (42)1.绪论1.1课题的提出在一些应用系统的通信设计中,PC机与单片机间常常采用串行异步通信方式。

因为这种通信方式,硬件电气连接简单在PC机上针对串口编程方便。

但是串行异步通信受传输速率的限制,通常最高波特率设定在9 600 b/s左右。

采用串行同步方式可提高传输率,但需在PC机上扩展设备。

如果所设计的数据采集系统,其数据传输速率要求达到60 kb/s以上,采用串行异步通信远远不能满足这个要求。

随着采集数据量的增大以及数据处理任务的增加,对数据传送的要求也越来越高,依靠单片机的自带串口实现数据的串行传输已经无法满足要求,在系统或模块间必须要能够进行高速的并行数据传输。

安全计算机双口RAM数据通信论文(全文)

安全计算机双口RM数据通信论文1安全数据交互方式为幸免MPU和HCU同时对双口RM的同一个内存单元进行访问,本设计没有采纳双口RM的中断或者信号量等机制,而是采纳一种基于角色的环形缓冲收发机制,将双口RM划分为两个独立环形缓冲区:发送环形缓冲区和接收环形缓冲区。

发送环形缓冲区负责将MPU数据传递给HCU,最终发送给外部设备;HCU从外部设备接收到数据,放到接收环形缓冲区,并传递给MPU。

1.1数据处理三取二安全计算机逻辑运算模块的运行周期为600ms,该模块按照周期进行数据接收、数据处理、数据输出。

在第n个周期,MPU上的操纵逻辑运算模块从双口RM接收到数据后,放到逻辑接收缓冲区;从逻辑接收缓冲区取出n-1个周期的数据并进行逻辑处理;将n-2个周期的逻辑处理结果,从逻辑发送缓冲区中取出,放到双口RM中。

MPU上的操纵逻辑运算模块对安全数据进行逻辑处理的时间不超过300ms,如果超过,就会影响MPU接收或者发送数据。

同样,MPU上的操纵逻辑运算模块接收、发送数据超过300ms,也会影响逻辑处理功能。

在接收发送处理阶段,300ms中的280ms被分为20个发送接收子周期,每一个子周期的时间为14ms。

在HCU中,也是按照同样的运行节拍从双口RM中写入或读出数据。

MPU与HCU之间交互的数据,按照预先定义的双口RM交换数据帧进行。

数据帧定义略———编者注。

1.2数据接收HCU通过XX络接口接收到数据后,对数据进行预处理,按照交换数据帧进行数据组包。

根据当前周期号设置“cycle”,同时确定该数据包需要被放到D、E、F三个区块中写入区块角色标志“role”,将“flg”设置为1(即为输入),并交换数据帧的其他字段,按照源XX络数据包中的信息进行设置。

HCU根据当前周期号确定在接收环形缓冲区中的写入区块后,将组包之后的交换数据帧放到写入区块中。

MPU根据当前周期号确定在接收环形缓冲区中的读出区块后,从读出区块中猎取交换数据帧,然后对数据帧进行解包,并通过“cycle”、“role”、“flg”、“sfety”、“crc”等信息来验证数据帧的唯一性和正确性,正常的数据帧被放到逻辑接收缓冲区,异常的数据帧被丢弃。

Xilinx IP core之RAM用法指南

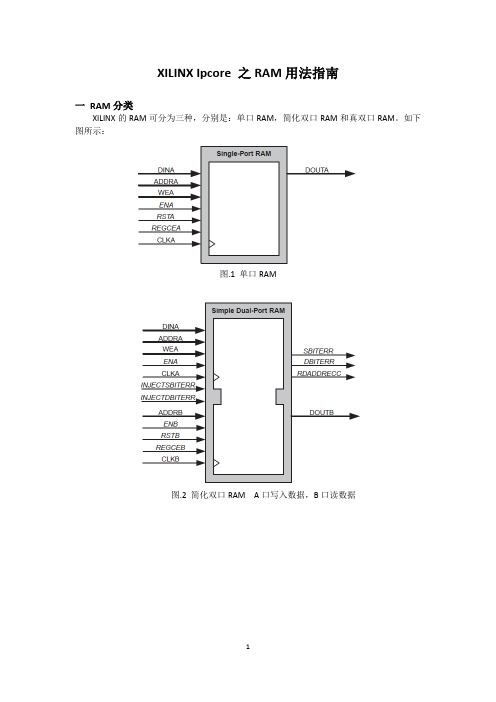

XILINX Ipcore 之RAM用法指南一RAM分类XILINX的RAM可分为三种,分别是:单口RAM,简化双口RAM和真双口RAM。

如下图所示:图.1 单口RAM图.2 简化双口RAM A口写入数据,B口读数据图.3 真双口RAM A,B任意一个口都可以读写数据,可从A写入,B读数据二选择数据位宽和深度Block RAM的数据位宽为1-1152bit,深度取决于所选择FPGA器件中block的数量。

超出地址范围之外的写操作,写进去的数据不会与存储器件中的数据冲突。

读超出地址范围之外数据将会返回无效数据。

注意,当对超出范围的地址进行操作的时候,不能置位set或reset 信号,因为这仍然会读出无效数据。

三操作模式每个端口的操作模式决定了此端口的读和写之间关系。

端口A和B可以独立配置为以下三种模式中任一模式:写优先模式,读优先模式,不改变模式。

这些模式详解见下面。

当A和B端口地址有冲突时,操作模式就会影响A和B口之间关系。

1.写优先模式(write first mode):在写优先模式中,输入数据被自动写入存储器件中,并且出现在数据输出端口。

时序见下图。

这种传输模式增强了在同一端口写操作时使用数据输出总线的灵活性。

图.4 写优先操作模式2.读优先模式(read first mode):在读优先模式中,预先存储在写地址中的数据会被输出,而输入数据被存入存储器件中。

这种模式见下图。

图.5 读优先模式3.不改变模式:在不改变模式中,输出锁存在写操作时候保持不变,见下图。

在同一端口的写操作不会对数据输出端口产生影响,输出仍然是以前的读数据。

图.6 不改变模式四数据位宽比例Block RAM产生器支持端口A和B的位宽不同。

即DINA,DINB,DOUA,DOUTB位宽可以互不相同。

支持1:32到32:1之间的比例,端口A的宽度最大可达端口B的32倍,反之亦然。

例如一个A口位宽32bit深度2048的真双口RAM,如果B端口宽度为8bit深度为8192。

基于FPGA的双口RAM在双CPU通信中的应用及设计本科毕业设计

毕业设计(论文)题目名称:基于FPGA的双口RAM在双CPU通信中的应用及设计学院:电气信息工程学院专业/班级:电子信息工程摘要基于现代通信系统的要求,本次设计详细研究了利用双端口RAM实现高速并行双CPU之间的数据通信,指出了设计中需要解决的几个关键性问题,并给出了相应的解决方案。

随着电子技术的迅速发展,大量的高速数据采集和现代工业测控系统和在线测试仪器的功能和性能提出了更高的要求,双CPU并行工作双单片机系统广泛应用。

为了使两个单片机可以快捷有效地交换信息,充分利用系统资源,共享内存实现通过使用双端口RAM现在更受欢迎的方法。

大容量高速FPGA器件具有较高的集成,体积小,灵活配置和实验风险小的优势。

在复杂数字系统越来越广泛的应用,数字电路设计采用1块FPGA设备存储设备和一些电气接口匹配电路解决方案已经成为一个主流的选择。

使用FPGA实现函数的双端口RAM是一个很好的方法来解决这个问题的并行性和速度,以及其灵活的可配置特性使基于FPGA双端口RAM容易修改测试和系统升级可以降低设计成本,缩短开发周期。

在嵌入式多CPU系统中,CPU之间的通信可以使用串行、并行和系统总线方式的双端口RAM,等等。

在三种沟通方式存在的共同传输速度慢的特点,在大量数据的情况下可能会导致数据处理时间的延长,实时性能,甚至出现数据拥堵现象。

所以与方法之间的双端口RAM数据交换系统是一个简单而有效的方法。

关键词: FPGA;双端口RAM;双CPU;并行数据通信AbstractBased on the demand of modern communication system, the design was studied by using dual port RAM to implement the parallel data communication between the double CPU, pointed out the need to be solved in the design of several key problems, and gives the corresponding solutions.With the rapid development of electronic technology, a large number of high-speed data acquisition and modern industry measurement and control system and the function of the online test instrument and performance put forward higher request, double CPU parallel work double single chip microcomputer system is widely used. Is becoming more and more widely used in complex number system, the digital circuit design of one piece of FPGA device storage equipment and some of the electrical interface matching circuit solution has become a mainstream choice. Using FPGA to realize function of dual port RAM is a very good method to solve the problem of parallelism and speed, and its flexible configurable properties based on FPGA dual port RAM is easier to modify test and system upgrade can reduce the design cost, shorten the development cycle.Key words: FPGA; Dual port RAM; Double CPU; The parallel data communication目录摘要 (I)Abstract (II)1绪论 (1)1.1研究发展趋势 (1)1.2研究现状 (1)1.3研究重点方向 (2)2 RAM与CPU之间通信的基本原理 (3)2.1 双口RAM 结构及工作原理 (3)2.1.1双口RAM的结构 (3)图2,1双口RAM存储结构图 (3)2.1.2双口RAM工作原理 (4)2.2 双CPU工作原理及应用 (5)2.2.1双CPU的结构 (5)2.2.2双CPU的工作原理 (6)2.2.3基于双CPU通信的设计及应用 (6)2.3 FPGA的基本结构及工作原理 (7)2.4本章小结 (8)3 双口RAM在双CPU通信中的设计及仿真 (9)3.1双端口RAM并行通信设计 (9)3.2系统关键性问题的解决 (10)3.2.1 系统故障冗余设计 (10)3.2.2 交叉事物处理设计 (10)3.3双CPU系统设计及关键技术问题 (11)3.3.1确保双CPU的协同可靠 (11)3.3.2合理设计交叉事物的实时处理软硬件 (11)3.3.3 双口RAM存储空间的组成及访问 (11)3.3.4可靠性的保障 (12)3.4仿真结果及性能分析 (13)3.5本章小结 (14)4总结及展望 (15)4.1课题研究所面临的问题 (15)4.2未来研究方向 (15)参考文献 (16)致谢 (17)附录 (18)1绪论1.1研究发展趋势随着现代智能系统的升级和更新,在双向通信和信息传输过程中,对信息量的增加和实时性的要求更加精准高效。

乒乓操作(两个双口RAM)

library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_unsigned.all;use IEEE.std_logic_arith.all;entity DPRAM_TEST isport(clk:in std_logic;data_out:out std_logic_vector(7 downto 0);scan:out std_logic_vector(7 downto 0));end DPRAM_TEST;architecture ONE of DPRAM_TEST issignal rdaddress1,wraddress1,q1: STD_LOGIC_VECTOR (3 DOWNTO 0); signal rden1,wren1:STD_LOGIC ;signal rdaddress2,wraddress2,q2: STD_LOGIC_VECTOR (3 DOWNTO 0); signal rden2,wren2:STD_LOGIC ;signal clk1hz,clk1khz,clk16_1s:std_logic;signal address:std_logic_vector(3 downto 0):="0000";signal address_en:integer range 0 to 20;signal data:std_logic_vector(3 downto 0):="0000";signal cnt1:integer range 0 to 3;signal scan1:std_logic_vector(7 downto 0);signal data_en:integer range 0 to 9;signal q1_en:integer range 0 to 9;signal q1_en2:integer range 0 to 9;signal q2_en:integer range 0 to 9;signal q2_en2:integer range 0 to 9;component RAM1PORT(clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);rdaddress : IN STD_LOGIC_VECTOR (3 DOWNTO 0);rden : IN STD_LOGIC := '1';wraddress : IN STD_LOGIC_VECTOR (3 DOWNTO 0);wren : IN STD_LOGIC := '1';q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );end component ;component RAM2PORT(clock : IN STD_LOGIC ;data : IN STD_LOGIC_VECTOR (3 DOWNTO 0);rdaddress : IN STD_LOGIC_VECTOR (3 DOWNTO 0);rden : IN STD_LOGIC := '1';wraddress : IN STD_LOGIC_VECTOR (3 DOWNTO 0);wren : IN STD_LOGIC := '1';q : OUT STD_LOGIC_VECTOR (3 DOWNTO 0) );end component;beginU1: RAM1 port map(clk1hz,data,rdaddress1,rden1,wraddress1,wren1,q1); U2: RAM2 port map(clk1hz,data,rdaddress2,rden2,wraddress2,wren2,q2);process(clk)variable cnt:integer range 0 to 24999999;beginif rising_edge(clk)thenif cnt=24999999 thenclk1hz<=not clk1hz;cnt:=0;elsecnt:=cnt+1;end if;end if;end process;process(clk1hz)variable cnt:integer range 0 to 15;beginif rising_edge(clk1hz)thenif cnt=15 thenclk16_1s<=not clk16_1s;cnt:=0;elsecnt:=cnt+1;end if;end if;end process;process(clk)variable cnt:integer range 0 to 24999; beginif rising_edge(clk)thenif cnt=24999 thenclk1khz<=not clk1khz ;cnt:=0;elsecnt:=cnt+1;end if ;end if ;end process;process(clk1hz)beginif rising_edge(clk1hz)thenif address="1111"thenaddress<="0000";elseaddress<=address+1;end if;end if;end process;process(clk1hz)beginif rising_edge(clk1hz)thencase clk16_1s iswhen '1'=>data<=data+1;when '0'=>data<=data-1;when others =>null;end case;end if;end process;process(clk1hz)beginif rising_edge(clk1hz)thenif wraddress1="1111"thenwraddress1<="0000";elsewraddress1<=wraddress1+1;end if;end if;end process;process(clk1hz)beginif rising_edge(clk1hz)thenif rdaddress1="1111"thenrdaddress1<="0000";elserdaddress1<=rdaddress1+1;end if;end if;end process;process(clk1hz)beginif rising_edge(clk1hz)thenif wraddress2="1111"thenwraddress2<="0000";elsewraddress2<=wraddress2+1;end if;end if;end process;process(clk1hz)beginif rising_edge(clk1hz)thenif rdaddress2="1111"thenrdaddress2<="0000";elserdaddress2<=rdaddress2+1;end if;end if;end process;process(clk16_1s)beginrden1<=clk16_1s;wren1<=not clk16_1s;rden2<=not clk16_1s;wren2<=clk16_1s;end process;process(clk1khz)beginif rising_edge(clk1khz) thenif cnt1=3 thencnt1<=0;elsecnt1<=cnt1+1;end if;end if;end process;process(clk)begincase q1 iswhen "0000"=>q1_en2<=0;q1_en<=0;when "0001"=>q1_en2<=0;q1_en<=1;when "0010"=>q1_en2<=0;q1_en<=2;when "0011"=>q1_en2<=0;q1_en<=3;when "0100"=>q1_en2<=0;q1_en<=4;when "0101"=>q1_en2<=0;q1_en<=5;when "0110"=>q1_en2<=0;q1_en<=6;when "0111"=>q1_en2<=0;q1_en<=7;when "1000"=>q1_en2<=0;q1_en<=8;when "1001"=>q1_en2<=0;q1_en<=9;when "1010"=>q1_en2<=1;q1_en<=0;when "1011"=>q1_en2<=1;q1_en<=1;when "1100"=>q1_en2<=1;q1_en<=2;when "1101"=>q1_en2<=1;q1_en<=3;when "1110"=>q1_en2<=1;q1_en<=4;when "1111"=>q1_en2<=1;q1_en<=5;when others=>null;end case;end process;process(clk)begincase q2 iswhen "0000"=>q2_en2<=0;q2_en<=0;when "0001"=>q2_en2<=0;q2_en<=1;when "0010"=>q2_en2<=0;q2_en<=2;when "0011"=>q2_en2<=0;q2_en<=3;when "0100"=>q2_en2<=0;q2_en<=4;when "0101"=>q2_en2<=0;q2_en<=5;when "0110"=>q2_en2<=0;q2_en<=6;when "0111"=>q2_en2<=0;q2_en<=7;when "1000"=>q2_en2<=0;q2_en<=8;when "1001"=>q2_en2<=0;q2_en<=9;when "1010"=>q2_en2<=1;q2_en<=0;when "1011"=>q2_en2<=1;q2_en<=1;when "1100"=>q2_en2<=1;q2_en<=2;when "1101"=>q2_en2<=1;q2_en<=3;when "1110"=>q2_en2<=1;q2_en<=4;when "1111"=>q2_en2<=1;q2_en<=5;when others=>null;end case;end process;process(cnt1)begincase cnt1 iswhen 0=>data_en<=q1_en;scan1<="11111110"; when 1=>data_en<=q1_en2;scan1<="11111101"; when 2=>data_en<=q2_en;scan1<="11111011"; when 3=>data_en<=q2_en2;scan1<="11110111";when others=>null;end case;scan<=scan1 ;end process;process(data_en)begincase(data_en) iswhen 0=>data_out<="11000000";when 1=>data_out<="11111001";when 2=>data_out<="10100100";when 3=>data_out<="10110000";when 4=>data_out<="10011001";when 5=>data_out<="10010010";when 6=>data_out<="10000010";when 7=>data_out<="11111000";when 8=>data_out<="10000000";when 9=>data_out<="10010000";when others=>data_out<="11111111";end case;end process;end ONE;。

基于双口RAM的多机数据通信技术

( . c o l f l ti l nier g N no gUnvri , no g26 1 , hn ; 1 Sh o e r a E g ei , a tn iesy Na tn 20 9 C ia o E c c n n t

260 ; 23 1 2 60 ) 2 3 1 ( . 通 大 学 电 气 工 程 学 院 , 苏 南通 1南 江 26 1 ;. 夏 太 阳 能 股 份 有 限 公 司 , 苏 南 通 2 0 92 桑 江

3 江 苏 省 太 阳能 光 热 组 件 及 控 制工 程 技 术 研 究 中心 , 苏 南 通 . 江

2 0在 01

仪 表 技 术 与 传 感 器

I sr me t T c n q e a d S n o n tu n e h i u n e s r

2 0 01 No 1 .1

第 1 期 1

基 于 双 口 RA 的 多 机 数 据 通 信 技 术 M

姜 平 , 周根 荣 , 肖红升 , 季 斌

题。

关键词 : 数据通信 ; 口 R M; 双 A 单片机

中 图 分 类 号 :P7 T24 文献标识码 : A 文 章 编 号 :0 2—14 ( 00 1 00 0 10 8 1 2 1 ) 1— 15— 3

ห้องสมุดไป่ตู้

M ulic m p e t m m u ia in c no o y Ba e n t・ o - utr Da a Co n c to Te h lg s d o Dua — r lpo tRAM

实验3双口RAM的仿真与综合

实验题目双口RAM的仿真与综合宏单元调用一、实验内容1、双口RAM的端口有写时钟控制端口wrclock、写始能端口wren、数据输入端口data、写地址端口wraddress、读时钟端口rdclock、读地址端口rdaddress以及输出端口q;2、在QuartusII软件环境下对双口ram进行宏单元调用,并对它进行综合;3、在modelsim软件环境下编写激励模块,并对宏调用的双口ram进行仿真;4、进一步熟悉QuartusII软件和modelsim软件的功能及环境。

二、详细设计设计步骤如下:1、在QuartusII软件环境下对双口ram进行宏单元调用,并对它进行综合;2、在modelsim软件环境下编写激励模块,并对宏调用的双口ram进行仿真,双口RAM的端口有写时钟控制端口wrclock、写始能端口wren、数据输入端口data、写地址端口wraddress、读时钟端口rdclock、读地址端口rdaddress以及输出端口q;3、在modelsim软件环境下进行后仿真。

4、根据仿真结果分析,最后得出结论。

三、仿真结果(1)在异步时钟脉冲下的结果如下:对应的地址有对应的输出,可以看出网表文件加上相应的延时文件仿真速度变慢同时得到的结果更接近实际。

可以看出地址1,输入的是58,则输出的是58.不连续地址变换仿真结果如上图。

连续地址变换所得仿真结果如上图。

总结:经过综合得出后仿真结果可以得出输出数据存在一定的时延,数据在输出时必须经过一定时间后才能有稳定的输出,可见前仿真比较稳定,后仿真有延时,更接近实际。

由以上RAM的端口有写时钟控制端口wrclock、写始能端口wren、数据输入端口data、写地址端口wraddress、读时钟端口rdclock、读地址端口rdaddress以及输出端口q;可以得出地址数共有8个,及3位二进制数。

数据共8位二进制。

(2)查看设计对应的寄存器传输级视图(3)布线情况(4)传真查看图四、调试情况,设计技巧及体会通过本次实验,我学会了宏调用双口ram,并学会对它设计激励并在modelsim软件环境下进行后仿真,通过本次实验,我更加熟悉了利用verilo语言来描述电路,同时熟悉了利用软件仿真电路的逻辑功能并进行验证和分析。

双口RAM(精)

1引言ARCNE 协议应用于高速动车组列车通信网络时,产生中央控制单元处理器PXA270与专用协议控制器件COM2002相连的时序不匹配问题,若用通用数字电 路模块进行时序转换,PXA270需占用PXA27(专门的资源(CPU 时间片)对 COM2002的寄存器、数据包缓冲区进行低速读写访问(对COM2002的相邻两次 读操作相隔至少300ns),这样将增加处理器的负担。

基于这种现状,提出一种 基于FPGA 勺PXA270外设时序转换接口设计方案,以FPGA 为桥梁进行时序转换, 并增加存储器直接访问DMA(Direct Memory Aeeess)功能,即FPGAl 动完成数 据包的收发工作,PXA270则只需高速读写访问FPGA 中的同步双口 RAIM2时序转换接口整体设计2. 1 FPGA 对外接白采用FPGA!接PXA270处理器与外设以解决PXA270处理器与外设直接连接 时的时序不匹配问题。

如图1所示,FPGA 从 PXA270处理器获得地址总线(ADDRBUS[17..14], ADDRBUS[9..0]),片选信号(SYSCS5)读允许(SYSOE)写 允许(SYSWE)并提供双向数据端口 DATABUS[7..0](可根据实际应用修改为32 位或16位等),中断(interrupt);同时,FPGA 向COM2002提供特定的总线接 口,包括COM20020_D,SCOM20020_CCOM20020_D ,COM20020_DATAB[US0],COM20020_ADDRBUS[2..等。

COMMONIFPGACOk2OG2 0,ADDiRBUS[2. , 0]图I FPGA 时序转换接口原理图2. 2内部功能实现PXA270和外设之间的连接是将FPGA 中的双口 RAM 作为数据中转站,以此间 接相连。

该设计由以下4个功能模块组成。

(1)PXA270对外设指定寄存器单次写操作 P XA27(先将所要写的数据送人双 口CLKIN ADDRBUS ADDRBUS SYSCSS SYSOE SYSWERAM然后PXA270向 FPGA勺命令寄存器写入对该外设指定寄存器的单次写指令,然后FP-GA 根据接收到的命令将RA 附的数据输出到外设数据总线,同时给 出对外设的写时序。

内部存储器RAM和ROM使用说明

内部存储器RAM和ROM用户指南

1、介绍内部存储器模块

本用户指南介绍了实现以下内存模式的宏功能:

■RAM:1-Port—Single-port RAM 单口RAM

■RAM:2-Port—Dual-port RAM 双口RAM

■ROM:1-Port—Single-port ROM 单口ROM

■ROM:2-Port—Dual-port ROM 双口ROM

Altera公司提供了两种宏功能来实现内存模式:ALTSYNCRAM和ALTDPRAM 宏功能。

QuartusII软件会自动选择其中一个宏功能来实现内存模式。

选择那种宏功能模式取决于目标器件,存储器模式和RAM和ROM的功能。

本用户指南会让您熟悉宏功能,以及如何创建它们。

如果您不熟悉的Altera 宏功能或“the MegaWizard™ Plug-In Manager”,请参阅介绍宏功能用户指南。

内部存储器具有如下功能:

■内存模式配置

■存储模块类型

■端口宽度设置

■存储器最大深度设置

■时钟模式和时钟使能

■地址时钟使能

■字使能

■异步清零

■读使能

■同时读写

■存储器初始化

■错误校正码

2、参数设置

Altera建议您使用参数编辑器来配置来构建您的RAM和ROM内存块,以确保您所选择的选项组合是有效的。

下表是双口RAM参数设置。

双口ram和多模块存储器

3.6 双口RAM和多模块存储器CPU和主存储器的速度不匹配问题一直以来都是计算机系统发展的障碍,到现在,这个问题变得越来越严重,以至于主存的存储速度成为了计算机系统的瓶颈。

为了解决这一瓶颈,尝试了多种办法,除通过寻找高速元件来提高访问速度外,还可以通过采用双口RAM和多模块存储器,使在一个存取周期内可以并行地读写多个字,从而提高存储器的访问速度。

1.双口RAM双口RAM是因同一个RAM具有两组相对独立的读写控制线路而得名,它可以进行并行的独立操作。

可以说双口RAM是具有两个独立端口的存储器,而每个端口又具有各自的地址线、数据线和控制线,可以对存储器中任何位置上的数据进行独立的存取操作。

双口RAM是常见的共享式多端口存储器,其最大的特点是存储数据共享。

它允许两个独立的CPU或控制器同时异步访问存储单元。

既然数据共享,就必须存在访问仲裁控制,否则就会出现错误或冲突。

两个端口对同一内存操作有4种情况:① 两个端口不同时对同一地址单元存取数据;② 两个端口同时对同一地址单元读出数据;③ 两个端口同时对同一地址单元写入数据;④ 两个端口同时对同一地址单元,一个写入数据,另一个读出数据。

在第①、第②种情况时,两个端口的存取不会出现错误,第③种情况会出现写入错误,第④种情况会出现读出错误。

为避免第③、第④种错误情况的出现,双口RAM设计有硬件“”功能输出,其工作原理如下。

当左、右端口不对同一地址单元存取时,可正常存取;当左、右端口对同一地址单元存取时,有一个端口的禁止数据的存取。

此时,两个端口中,哪个存取请求信号出现在前,则其对应的允许存取;哪个存取请求信号出现在后,则其对应的禁止其写入数据。

需要注意的是,两端口间的存取请求信号出现时间要相差在5ns以上,否则仲裁逻辑无法判定哪一个端口的存取请求信号在前;在无法判定哪个端口先出现存取请求信号时,控制线和只有一个为低电平,不会同时为低电平。

这样,就能保证对应于的端口能进行正常存取,对应于的端口不存取,从而避免双端口存取出现错误。

一种基于双口ram数据共享和422串口通信的数据交换器的制作方法

一种基于双口ram数据共享和422串口通信的数据交换器的制作方法专利名称:一种基于双口ram数据共享和422串口通信的数据交换器的制作方法技术领域:本实用新型涉及一种数据交换器,特别是涉及一种基于双口 RAM数据共享和422串口通信的数据交换器。

背景技术:双口RAM是在I个RAM存储器上具有两套完全独立的数据线、地址线和读写控制线,并允许两个独立的系统同时对其进行随机性访问的存储器,即共享多端口存储器。

双口RAM最大的特点是可实现存储数据共享。

随着电子技术的飞速发展,大量的高速数据采集和在线测试对现代工业测控系统和仪器仪表的功能和性能提更高要求,CPU并行工作(双单片机系统)方式得到广泛应用。

为了使两个单片机能够快速有效交换信息,充分利用系统资源,采用双口RAM实现存储器共享是目前较为流行的方法。

但这种方法仅仅只能实现两个系统之间的数据交换。

如果在两个以上的系统之间进行数据交换,由于所选CPU系统资源的局限性,则不能全部采用共享双口RAM的方式进行数据交换,否则就得增加CPU的使用数量,导致增大电路设计的难度,而需采用其它的方式来满足两个以上系统之间的数据交换的需求。

在本专利中,为了最大限度的利用CPU的系统资源,就针对它唯一的串口进行了扩展,因此采用了422串口通信与共享双口RAM的方式相结合的方式来完成了这一设计需求。

之所以采用422串口通信是因为422串口通信比起同类别的232串口通信具有接口芯片体积小,配置电路简单,通信可靠性更高的优点存在。

所以本专利是两种数据交换方式相结合的复合型的数据交换器。

这种设计能够减少电路设计的复杂性,增强设计的灵活性和资源的可配置性能,降低了设计成本,是一项实用的新型设计。

实用新型内容本实用新型的目的是提供一种基于双口 RAM数据共享和422串口通信的数据交换器,该交换器外部与双口RAM相连,采用422接口与多个受控单元相连,实现一个供多个受控单元的多方通信数据交换的平台。