针对IO的缓冲器版图设计

芯片IO缓冲及ESD设计

芯片I/O缓冲及ESD电路设计摘要:文章详细介绍了基于C MOS的芯片I/O缓冲电路分类,功能,电路及版图设计的一些考虑以及芯片引脚的静电保护问题。

广告插播信息维库最新热卖芯片:ST10043QC IRFR024N SMBJ5.0CA XC17S10PD8C ICL7612BCPA TC35302P2 4LC128T-I/SN TC551001BFL-85L PQ30RV21UPD485505G-35关键词:I/O;缓冲电路;静电保护;CMOS针对引脚的输入输出缓冲(I/O buffer)电路设计,也可以称为输入输出接口(I/O interface)电路设计,是一颗完整芯片设计中不可或缺的组成部分,但是详细论述其设计规则的文章或者著作在国内却比较鲜见,这对初学者或者没有这方面经验的工程师无疑会造成困惑。

本文以CMOS工艺为例,较全面的论述I/O缓冲电路设计中各种考虑,可以作为芯片引脚输入输出电路设计的一个参考。

根据I/O缓冲电路应用目标的不同,可将其分为输入、输出等几类,详见表1。

表1 I/O缓冲电路的分类输出缓冲(是个大驱动器,他将信号输出芯片)输出缓冲电路的功能要求能够驱动大的片外负载,通常为2~50pF,并且提供适当的上升/下降时间。

一组连续的大尺寸的缓冲器(buffer)对驱动能力的提高是有益的。

大尺寸的管子容易受闩锁效应(latch-up)的影响,在版图设计时建议采用保护环(Guardrings)保护以避免闩锁效应,如图1-1所示。

在图中,用P+作为内保护环,而N+作为外保护环(In n-well)。

图1-1缓冲器一种常见的输出电路如图1-2所示,En是输出电路的使能信号,Dout是输出数据,MOS管组合的功能如图中所示。

当En为低而Dout有效时,A、B均为高电平,输出Y为低,且由外向里看为高阻抗状态,如果Dout未定,则Y为高阻。

需要注意的是,最后输出级的管子尺寸要大到能够提供足够的电流源或电流沉并且减少延迟时间。

简单的单片机I-O口扩展实例

简单的单片机I/O口扩展实例扩展实例 简单的I/O口扩展通常是采用TTL或CMOS电路锁存器、三态门等作为扩展芯片,通过P0口来实现扩展的一种方案。

它具有电路简单、成本低、配置灵活的特点。

下图为采用74LS244作为扩展输入、74LS273作为扩展输出的简单I/O口扩展。

芯片及连线说明 图中电路中采用的芯片为TTL电路74LS244、74LS273。

其中,74LS244为8缓冲线驱动器(三态输出),、为低电平有效的使能端。

当二者之一为高电平时,输出为三态。

74LS273为8D触发器,为低电平有效的清除端。

当=0时,输出全为0且与其它输入端无关;CP端是时钟信号,当CP由低电平向高电平跳变时刻,D端输入数据传送到Q输出端。

P0口作为双向8位数据线,既能够从74LS244输入数据,又能够从74LS273输出数据。

输入控制信号由P2.0和相或后形成。

当二者都为0时,74LS244的控制端有效,选通74LS244,外部的信息输入到P0数据总线上。

当与74LS244相连的按键都没有按下时,输入全为1,若按下某键,则所在线输入为0。

输出控制信号由P2.0和相或后形成。

当二者都为0后,74LS273的控制端有效,选通74LS273,P0上的数据锁存到74LS273的 输出端,控制发光二极管LED,当某线输出为0时,相应的LED发光。

I/O口地址确定 因为74LS244和74LS273都是在P2.0为0时被选通的,所以二者的口地址都为FEFFH(这个地址不是惟一的,只要保证P2.0=0,其它地址位无关)。

但是由于分别由和控制,因而两个信号不可能同时为0(执行输入指令,如MOVX A,@DPTR或MOVX A,@Ri时,有效;执行输出指令,如MOVX @DPTR,A或MOVX @Ri,A时,有效),所以逻辑上二者不会发生冲突。

。

单片机IO口工作原理及结构框图

单片机IO口工作原理及结构框图8051单片机I/O引脚工作原理一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP 没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

IO扩展模块设计教程

4.3 I/O扩展模块4.3.1 设计目的及任务1、设计任务:设计一个基于单片机的I/O扩展模块以及相应的外围电路。

2、功能指标:扩展I/O数量大于16个,可以通过编程控制输入或者输出方向,电源为+5V供电3、设计要求:所设计的I/O扩展模块应满足EDP实验仪系统设计要求,并能与整个系统有效结合。

以下是一个以8155 I/O扩展芯片为例的设计范例及其相应电路的讲解,仅供参考。

4.3.2 8155 I/O扩展芯片的基本工作原理1 、8155内部结构Intel 8155芯片内包含有256个字节RAM,2个8位、1个6位的可编程并行I/O口和1个14位定时器/计数器。

8155可直接与MCS-51单片机连接不需要增加任何硬件逻辑。

由于8155既有RAM又具有I/O口,因而是MCS-51单片机系统中最常用的外围接口芯片之一,8155的引脚及内部结构如下图4-3-1:图4-3-1: 8155的引脚及内部结构8155共有40个引脚,采用双列直插式封装。

各引脚功能如下:AD7~AD0:地址数据总路线。

单片机和8155之间的地址、数据、命令、状态信息都是通过它传送的。

CE:片选信号线,低电平有效RD:存储器读信号线,低电平有效。

WR:存储器写信号线,低电平有效。

LE:地址及片选信号锁存线,高电平有效,其后沿将地址及片选信号锁存到器件中。

IO/M:I/O接口与存储器选择依赖线,高电平表示选择I/O接口,低电平选择存储器。

PA7~PA0:A口输入/输出线。

PB7~PB0:B口输入/输出线。

PC5~PC0:C口输入/输出或控制信号线。

用作控制信号线时,其功能如下:PC0:A INTR(A口中断信号线)。

PC1:A BF(A口缓冲器满信号线)。

PC2:ASTB(A口选通线)。

PC3:B INTR (B 口中断信号线)。

PC4:B BF (B 口缓冲器满信号线)。

PC5:BSTB (B 口选通线)。

TIMER IN :定时器/计时器输入端。

缓冲电路设计及仿真

1 缓冲电路作用缓冲电路一般并联在开关器件两端,重要有克制过电压、减少器件损耗、消除电磁干扰的作用。

1) 克制过电压逆变器高频工作时,开关器件快速开通、关断。

由于主电路存在杂散电感,器件在开关过程中,急剧变化的主电路电流会在杂散电感上感应出很高的电压,使器件在关断时承受很高的关断电压。

在器件关断时,主电路杂散电感上会产生与直流电压同向的感应电压pdiL dt,若无缓冲电路,则该电压会加在器件两端形成过电压,当该电压超过器件额定电压时,器件损坏。

此外,反并联二极管在反向恢复时产生的di/dt 也会导致较高的过电压。

2) 减少器件损耗已知器件的功耗由下式决定:01TP uidt T=⎰ (1.1)在电路中增长缓冲电路,可以改变器件的电压、电流波形,进而减少损耗。

从下图可知,在没有缓冲电路时,电压快速升至最大值,而此时电流仍然是最大值,此时的损耗最大。

加入缓冲电路后,避免了电压、电流出现同时最大值的情况,损耗得以减少。

U DS无缓冲电路U DS I DI D有缓冲电路3) 消除电磁干扰电路运营时,在没有缓冲电路的情况下,器件两端电压会发生高频振荡,产生电磁干扰。

采用缓冲电路,可克制器件两端电压的高频振荡,起到减小电磁干扰的作用。

因此,减少或消除器件电压、电流尖峰,限制dI/dt 或dV/dt ,减少开关过程中的振荡以及损耗,我们在逆变器中设计缓冲电路,以保证器件安全可靠工作。

2 杂散电感的测量与计算设计缓冲回路之前,一方面需要拟定杂散参数的量。

杂散电感是特定电路布局的结果,不容易计算出来,我们一般采用测量的方法来拟定杂散电感的大小。

在没有任何缓冲回路时,用示波器观测器件关断时的振荡周期T1;接着,在开关管两端并联一个值拟定的电容,即测试电容test C ,重新测量器件关断时的振荡周期T2。

则杂散电感可由下式得出:2221p 2()L 4testT T C π-=(2.1)杂散电容为:21(2)p p i C L f π=(2.2)其中i f 为无缓冲电路时的振荡频率。

单片机IO口结构及工作原理

、Po端口的结构及工作原理Po端口8位中的一位结构图见下图:地址∕ttiκI i O i XWwfr⅛⅛内部总线i⅛引脚PO 口工作康理图由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成下面,先分析组成P0 口的各个部分:先看输入缓冲器:在P0 口中,有两个三态的缓冲器,在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),上面一个是读锁存器的缓冲器,下面一个是读引脚的缓冲器,读取P0.X引脚上的数据,要使这个三态缓冲器有效,引脚上的数据才会传输到内部数据总线上。

D锁存器:在51单片机的32根I/O 口线中都是用一个D触发器来构成锁存器的。

D 端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

多路开关:在51单片机中,不需要外扩展存储器时,P0 口可以作为通用的输入输出端口(即I/O)使用,对于8031 (内部没有ROM )的单片机或者编写的程序超过了单片机内部的存储器容量,需要外扩存储器时,P0 口就作为,地址/数据? 总线使用。

这个多路选择开关就是用于选择是做为普通I/O 口使用还是作为,数据/地址?总线使用的选择开关了。

当多路开关与下面接通时,P0 口是作为普通的I/O 口使用的,当多路开关是与上面接通时,P0 口是作为,地址/数据?总线使用的。

输出驱动部份:P0 口的输出是由两个MOS管组成的推拉式结构,也就是说,这两个MOS管一次只能导通一个,当V1导通时,V2就截止,当V2导通时,V1截止。

Po 口作为I/O端口使用时,多路开关的控制信号为0 (低电平),V1管截止, 多路开关是与锁存器的Q非端相接的(即P0 口作为I/O 口线使用)。

作为地址/数据线使用时,多路开关的控制信号为1,V1管由地址/数据线决定,多路开关与地址/数据线连接。

输出过程:1、I/O输出工作过程:当写锁存器信号CP有效,数据总线的信号→锁存器的输入端D→锁存器的反向输出Q非端→多路开关→V2管的栅极→V2的漏极到输出端P0.X。

6.1输入输出缓冲器

转换电平

V

VDD K r VTN 1 Kr K r VDD VTP 1 K r

V

V V V , V V 噪声容限 NHM DD NLM

回滞电压

VH V V , V VH 2

11

史密特触发器做输 入缓冲器

利用回滞电压特性抑制输入噪声干扰

无缓冲器 (单级反相 器驱动)

S (CL / Cin)1/N tp NStp0

N CL / Cin

有缓冲器 缓冲器级数

1/ N

tp0

tp / tp0

tp / tp0

10 100 1000 10000

10 100 1000 10000

6.3 12.5 18.8 25.0

2 5 7 9

22

输出缓冲器

不同结构输出级MOS管对电路速度的影响

23

本节总结

输入缓冲器:电平转换/抑制噪声 输出缓冲器 :提高驱动能力

24

2

S CL / Cin

1/N

每级反相器的延迟时间 是:Stp 0

CL S N Cin .

tp NStp0 N CL / Cin

1/ N

tp0

17

输出缓冲器:反相器链

使tp最小的N与S的最优值

N ln(CL / Cin)

得到驱动大电容优化结果:根据CL和Cin,求出最 优反相器链级数N,每级尺寸增大S倍 一般情况下,每级尺寸增大2.72倍速度相对优化

一般用多级反相器构成的 反相器链做输出缓冲器

15

输出缓冲器

驱动不同负载电容时,输入/输出电压波形及 充放电电流

Xilinx可编程逻辑器件设计与开发(基础篇)连载9:Spartan

齐。

图 2-11 BUFIO_2FB 的原语

BUFIO_2FB 缓冲器为 CMT(PLL 或 DCM)参考输入 CLKIN 和反馈输入 CLKFB 的时钟布线延时提供了一个很好的解决方法。当使用 CMT 的反馈路 径时,ISE 会自动插入 BUFIO_2FB 和 BUFIO2 缓冲器,如图 2-12 所示。 图 2-12 BUFIO_2FB 缓冲器与时钟布线延时匹配 (4) BUFPLL。 图 2-13 所示为 BUFPLL 的原语,主要用来驱动高速 I/O,为 ISERDES2 和 OSERDES2 提供时钟。 它会将 PLL 的 LOCK 输出与 GCLK、SERDES 选通和 PLL 时钟对齐。其 中的 IOCLK 仅仅是将输入时钟通过了一级缓冲的版本。LOCK 输出信号其实 与 PLL 的 LOCKED 信号具有相同的功能,它们的区别在于,在 PLL 锁定、 BUFPLL 对齐 SERDES 选通信号之前,LOCK 不会变高。 图 2-13 BUFPLL 的原语 Spartan-6 器件每个 BANK 有两个 BUFPLL,专用于 PLL,不建议将其用 作逻辑时钟。

Xilinx 可编程逻辑器件设计与开发(基础篇)连载

9:Spartan

三、 I/O 时钟缓冲器 除了全局时钟缓冲器外,Spartan-6 还包含驱动高速 I/O 时钟区域的时钟缓 冲器。 I/O 时钟缓冲器的原语如表 2-9 所示。 表 2-9 I/O 时钟缓冲器的原语 (1) BUFIO2。 BUFIO2 接收来自 GCLK 时钟输入,产生两个时钟输出和一个驱动 IOSERDES2 的选通脉冲,如图 2-9 所示。 (2) BUFIO2_2CLK。 BUFIO2_2CLK 和 BUFIO2 功能几乎相同,不同的是 BUFIO2_2CLK 的输

针对IO的缓冲器版图设计

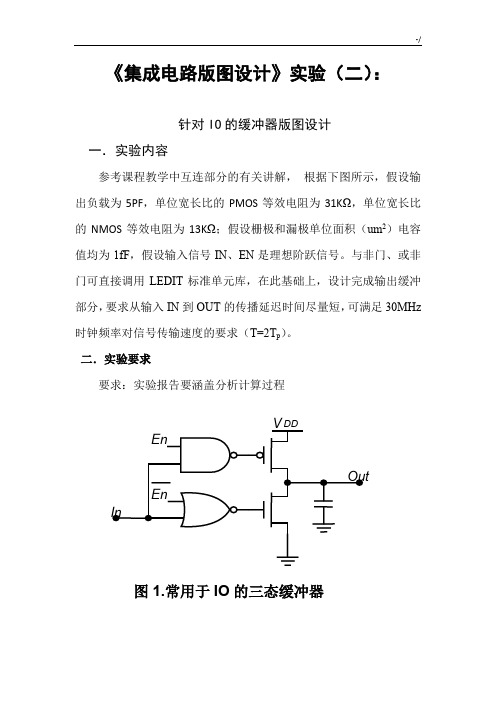

《集成电路版图设计》实验(二):针对IO的缓冲器版图设计一.实验内容参考课程教学中互连部分的有关讲解,根据下图所示,假设输出负载为5PF,单位宽长比的PMOS等效电阻为31KΩ,单位宽长比的NMOS等效电阻为13KΩ;假设栅极和漏极单位面积(um2)电容值均为1fF,假设输入信号IN、EN是理想阶跃信号。

与非门、或非门可直接调用LEDIT标准单元库,在此基础上,设计完成输出缓冲部分,要求从输入IN到OUT的传播延迟时间尽量短,可满足30MHz 时钟频率对信号传输速度的要求(T=2T p)。

二.实验要求要求:实验报告要涵盖分析计算过程V DDInEnEnOut 图1.常用于IO的三态缓冲器三、实验分析为了满足时钟频率对信号传输速度的要求,通过计算与非门和或非门的最坏延时,再用全局的时钟周期减去最坏的延时,就得到了反相器的应该满足的延时要求,可以得到反相器N管和P管宽度应该满足什么要求。

标准与非门和或非门的电容、电阻可以通过已知条件算出。

由于与非门、或非门可直接调用LEDIT标准单元库,所以本设计的关键在于后级反相器的设计上(通过调整反相器版图的宽长比等),以满足题目对电路延时的要求。

由于输入信号IN和是理想的阶跃信号,所以输入的延时影响不用考虑。

所以计算的重点在与非门和或非门的延时,以及输出级的延时。

对于与非门,或非门的延时,由于调用的是标准单元,所以它的延时通过提取标准单元的尺寸进行估算,输出级的尺寸则根据延时的要求进行设计。

四、分析计算计算过程:(1)全局延时要求为:30MHz的信号的周期为T=1/f=33ns;全局延时对Tp的取值要求,Tp<1/2*T=16.7ns;(2)标准单元延时的计算:所用到的标准单元如下图所示:图2.与非门和或非门标准单元版图通过在ledit软件中使用尺子测量与非门和或非门的晶体管的尺寸,得到了L=2um,W=28um,漏极的长度为LD=6um。

pmos和nmos采用的是等尺寸的。

MCS-51扩展IO接口的设计

此外,74LS系列的TTL电路也可以作为MCS-51的扩展 I/O口,如74LS244、 74LS273等。

最后介绍利用串行口来扩展并行I/O口。

9.2 MCS-51与可编程并行I/O芯片8255A的接口

9.2.1 8255A芯片介绍

8255A是Intel公司生产的可编程并行I/O接口芯片, 具有3个8位的并行I/O口,3种工作方式,可通过编 程改变其功能,因而使用灵活方便,通用性强。

3.CPU对8155H I/O端口的控制 (1) 8155H各端口地址分配

CE* IO/M* A7 A6 A5 A4 A3 A2 A1 A0

0 1 ××××× 0 0 0

0 1 ××××× 0 0 1

0

1 ××××× 0 1 0

0 1 ××××× 0 1 1

0 1 ××××× 1 0 0

0 1 ××××× 1 0 1

I/O寄存器与数据存储器单元同等对待,统一编址。 不需要专门的I/O指令,直接使用访问数据存储器的指 令进行I/O操作,简单、方便且功能强。

MCS-51使用统一编址的方式 每一接口芯片中的一个功能寄存器(端口)的地址

就相当于一个RAM单元。

9.1.3 I/O数据的几种传送方式 为实现和不同的外设的速度匹配,I/O接口必须

INTE A:中断允许,由PC6控制。

INTE B:中断允许,由PC2控制。

B口的方式1输出如图9-8所示:

3.方式2

只有A口才能设定为方式2。图9-9为方式2工作示意图。

在方式2下,PA7~PA0为双向I/O总线。

当输入时,PA7~PA0受STBA*和IBFA控制,其工作 过程和方式1输入时相同;

集成电路第8章I0.ppt

流Ih。

2024/9/30

18

第二节 输入保护电路

其中条件(2)的推导如下

设外界干扰引起的触发电流IAG 使Q1的EB结正偏电压大于≥0.7V。

此时Q1导通,若 IC1流过Rw产生的压降大于0.7V,就能使Q2也导

2024/9/30

12

第二节 输入保护电路

二、输入保护电路 2、上图所示可以很好保护NMOS管栅极,但是对PMOS管栅极保 护作用较差。若把二极管接在VDD和输入端之间,则对PMOS管 栅极保护作用好而对NMOS栅极保护差。 因此,CMOS IC中一般都采用双二极管保护电路,用两个二极管 和一个电阻构成的保护电路。

一旦发生闩锁效应,CMOS电路的电源和地之间就处于近似 短路的状态,这势必破坏电路的正常工作。此时只有将电源关 断,然后重新接通,电路才可能恢复正常工作。如果这种电流不 加限制,最终将使整个电路烧毁。

2024/9/30

17

第二节 输入保护电路

CMOS电路版图中的闩锁效应

产生闩锁效应的基本条件有三个: (1)外界因素使两个寄生三极管的EB结处于大于等于0.7的正向

2024/9/30

1

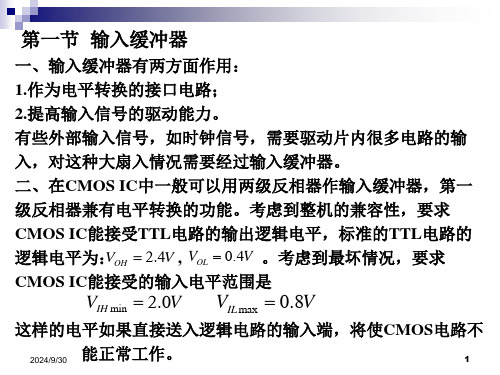

第一节 输入缓冲器

要通过输入缓冲器转换成合格的CMOS逻辑电平,再送到其他电

路的输入端。可以通过一个专门设计的CMOS反相器实现电平转

换,它的逻辑阈值设计在输入高、低电平范围之间,即

Vit

VIH min

VILmax 2

1.4V

若 VDD 5V VTN VTP 0.8V ,则要求输入级反相器的比例因子

2024/9/30

芯片IO缓冲及ESD电路设计

芯片I/O缓冲及ESD电路设计摘要:文章详细介绍了基于CMOS的芯片I/O缓冲电路分类,功能,电路及版图设计的一些考虑以及芯片引脚的静电保护问题。

关键词:I/O;缓冲电路;静电保护;CMOS针对引脚的输入输出缓冲(I/O buffer)电路设计,也可以称为输入输出接口(I/O interface)电路设计,是一颗完整芯片设计中不可或缺的组成部分,但是详细论述其设计规则的文章或者著作在国内却比较鲜见,这对初学者或者没有这方面经验的工程师无疑会造成困惑。

本文以CMOS工艺为例,较全面的论述I/O缓冲电路设计中各种考虑,可以作为芯片引脚输入输出电路设计的一个参考。

根据I/O缓冲电路应用目标的不同,可将其分为输入、输出等几类,详见表1。

表1 I/O缓冲电路的分类输出缓冲输出缓冲电路的功能要求能够驱动大的片外负载,通常为2~50pF,并且提供适当的上升/下降时间。

一组连续的大尺寸的缓冲器(buffer)对驱动能力的提高是有益的。

大尺寸的管子容易受闩锁效应(latch-up)的影响,在版图设计时建议采用保护环(Guardrings)保护以避免闩锁效应,如图1-1所示。

在图中,用P+作为内保护环,而N+作为外保护环(In n-well)。

图1-1缓冲器一种常见的输出电路如图1-2所示,En是输出电路的使能信号,Dout是输出数据,MOS管组合的功能如图中所示。

当En为低而Dout有效时,A、B均为高电平,输出Y为低,且由外向里看为高阻抗状态,如果Dout未定,则Y为高阻。

需要注意的是,最后输出级的管子尺寸要大到能够提供足够的电流源或电流沉并且减少延迟时间。

其负面影响是电流变化率(di/dt)变大而使穿过输出点到封装的压焊线上的L(di/dt)噪声增大,从而导致较大的片上噪声。

图1-2常用的输出缓冲电路在高性能的芯片中,如32位的微处理器,如果多个I/O输出驱动电路工作状态相似时,L(di/dt)噪声可能逐步增强,会影响芯片速度。

第6章_CMOS集成电路的IO设计

V VTN Vx

VDD R VTN 1 R

工作原理(2)

Vin=10:

VDD

MP1 4

当Vin=1时,输出为低电平;将 管N3关断,而P3导通;由于: VGSP1 Vin VDD VGSP 2 Vin Vy

VGSP 3 VOUT Vy

Y

MP3 6 MP2 3

2.5 2.0

Vx (V) 1.5

1.0

0.5 V VM2

此图为M3和M4分别为 0.5/0.25、1.5/0.25时的 模拟结果;

V+ VM1

0.0 0.0

0.5

1.0 1.5 Vin (V)

2.0

2.5

(a) Voltage-transfer characteristics with hysteresis.

R (VDD VTP ) 1 R

M5 N3

VDD

Notes2

' 选择合适的 ,即可得到所需的反向阈值电压;

R

用作TTL转换电路的输入级时,只要 VIH V , 输出就是合格的低电平;

V VTP Vy

R (VDD VTP ) 1 R

CMOS Schmitt Trigger的噪容

确定电平转换反相器中N、P管的宽长比:

W / L N

W / L P

P VDD VTP Vit N Vit VTN

2

电平转换电路的设计举例

VTN VTP 0.8V 且 N 2P 设 VDD 5V , 则:

W / L N

非反相施密特触发器及VTC曲线 (Schmitt Trigger)

微机原理实验-基本IO口扩展实验

微机原理与系统设计课程实验报告

实验名称基本IO扩展实验

实验三基本IO口扩展实验

一、实验目的

了解TTL芯片扩展简单I/O口的方法,掌握数据输入输出程序编制的方法。

二、实验内容说明

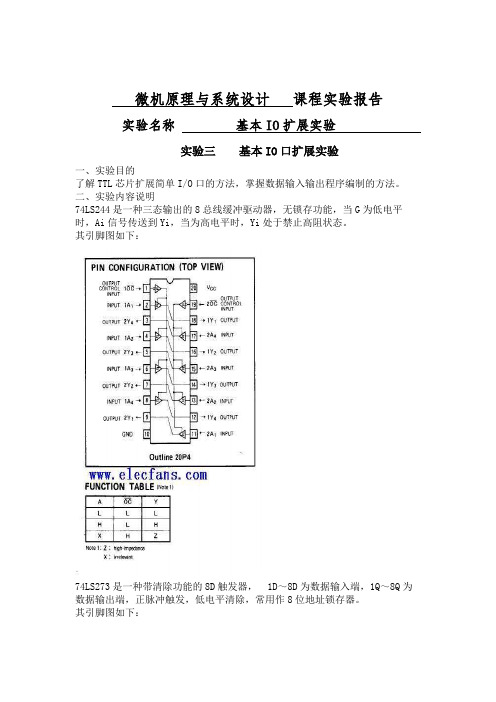

74LS244是一种三态输出的8总线缓冲驱动器,无锁存功能,当G为低电平时,Ai信号传送到Yi,当为高电平时,Yi处于禁止高阻状态。

其引脚图如下:

74LS273是一种带清除功能的8D触发器,1D~8D为数据输入端,1Q~8Q为数据输出端,正脉冲触发,低电平清除,常用作8位地址锁存器。

其引脚图如下:

本实验要求用74LS244作为输入口,读取开关状态,并将此状态通过74LS273连接到发光二极管显示。

具体实验内容如下:

(1)当开关Yi为低电平时对应的发光二极管点亮,Yi为高电平时对应的发光二极管灭。

(2)当开关Yi全为高电平时,发光二极管Qi从左至右轮流点亮。

(3)当开关Yi全为低电平时,发光二极管Qi从右至左轮流点亮。

(4)自主设计控制及显示模式,完成编程调试,演示实验结果。

三、实验原理图:

实验连线图:

四、实验步骤:

(1)实验连线:

①244的CS——ISA总线接口模块的0000H,Y7—Y0——开关K1—K8。

②273的CS——ISA总线接口模块的0020H,Q7—Q0——发光二极管L1—L8。

③该模块的WR、RD分别连到ISA总线接口模块的IOWR、IORD。

④该模块的数据(AD0~AD7)连到ISA总线接口模块的数据(LD0~LD7)。

(2)编写实验程序,编译链接,运行程序

(3)拨动开关,观察发光二极管的变化。

五、实验程序。

单片机IO口工作原理及结构框图

单片机IO口工作原理及结构框图8051单片机I/O引脚工作原理一、P0端口的结构及工作原理P0端口8位中的一位结构图见下图:由上图可见,P0端口由锁存器、输入缓冲器、切换开关、一个与非门、一个与门及场效应管驱动电路构成。

再看图的右边,标号为P0.X引脚的图标,也就是说P0.X引脚可以是P0.0到P0.7的任何一位,即在P0口有8个与上图相同的电路组成。

下面,我们先就组成P0口的每个单元部份跟大家介绍一下:先看输入缓冲器:在P0口中,有两个三态的缓冲器,在学数字电路时,我们已知道,三态门有三个状态,即在其的输出端可以是高电平、低电平,同时还有一种就是高阻状态(或称为禁止状态),大家看上图,上面一个是读锁存器的缓冲器,也就是说,要读取D锁存器输出端Q的数据,那就得使读锁存器的这个缓冲器的三态控制端(上图中标号为‘读锁存器’端)有效。

下面一个是读引脚的缓冲器,要读取P0.X引脚上的数据,也要使标号为‘读引脚’的这个三态缓冲器的控制端有效,引脚上的数据才会传输到我们单片机的内部数据总线上。

D锁存器:构成一个锁存器,通常要用一个时序电路,时序的单元电路在学数字电路时我们已知道,一个触发器可以保存一位的二进制数(即具有保持功能),在51单片机的32根I/O口线中都是用一个D触发器来构成锁存器的。

大家看上图中的D锁存器,D端是数据输入端,CP是控制端(也就是时序控制信号输入端),Q是输出端,Q非是反向输出端。

对于D触发器来讲,当D输入端有一个输入信号,如果这时控制端CP 没有信号(也就是时序脉冲没有到来),这时输入端D的数据是无法传输到输出端Q及反向输出端Q非的。

如果时序控制端CP的时序脉冲一旦到了,这时D端输入的数据就会传输到Q及Q非端。

数据传送过来后,当CP时序控制端的时序信号消失了,这时,输出端还会保持着上次输入端D的数据(即把上次的数据锁存起来了)。

如果下一个时序控制脉冲信号来了,这时D端的数据才再次传送到Q端,从而改变Q端的状态。

芯片IO缓冲和ESD设计

芯片I/O缓冲及ESD电路设计摘要:文章详细介绍了基于C MOS的芯片I/O缓冲电路分类,功能,电路及版图设计的一些考虑以及芯片引脚的静电保护问题。

关键词:I/O;缓冲电路;静电保护;CMOS针对引脚的输入输出缓冲(I/O buffer)电路设计,也可以称为输入输出接口(I/O interface)电路设计,是一颗完整芯片设计中不可或缺的组成部分,但是详细论述其设计规则的文章或者著作在国内却比较鲜见,这对初学者或者没有这方面经验的工程师无疑会造成困惑。

本文以CMOS工艺为例,较全面的论述I/O缓冲电路设计中各种考虑,可以作为芯片引脚输入输出电路设计的一个参考。

根据I/O缓冲电路应用目标的不同,可将其分为输入、输出等几类,详见表1。

表1 I/O缓冲电路的分类输出缓冲(是个大驱动器,他将信号输出芯片)输出缓冲电路的功能要求能够驱动大的片外负载,通常为2~50pF,并且提供适当的上升/下降时间。

一组连续的大尺寸的缓冲器(buffer)对驱动能力的提高是有益的。

大尺寸的管子容易受闩锁效应(latch-up)的影响,在版图设计时建议采用保护环(Guardrings)保护以避免闩锁效应,如图1-1所示。

在图中,用P+作为内保护环,而N+作为外保护环(In n-well)。

图1-1缓冲器一种常见的输出电路如图1-2所示,En是输出电路的使能信号,Dout是输出数据,MOS管组合的功能如图中所示。

当En为低而Dout有效时,A、B均为高电平,输出Y为低,且由外向里看为高阻抗状态,如果Dout未定,则Y为高阻。

需要注意的是,最后输出级的管子尺寸要大到能够提供足够的电流源或电流沉并且减少延迟时间。

其负面影响是电流变化率(di/dt)变大而使穿过输出点到封装的压焊线上的L(di/dt)噪声增大,从而导致较大的片上噪声。

图1-2常用的输出缓冲电路在高性能的芯片中,如32位的微处理器,如果多个I/O输出驱动电路工作状态相似时,L(di/dt)噪声可能逐步增强,会影响芯片速度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《集成电路版图设计》实验(二):

针对IO的缓冲器版图设计

一.实验容

参考课程教学中互连部分的有关讲解,根据下图所示,假设输出负载为5PF,单位宽长比的PMOS等效电阻为31KΩ,单位宽长比的NMOS等效电阻为13KΩ;假设栅极和漏极单位面积(um2)电容值均为1fF,假设输入信号IN、EN是理想阶跃信号。

与非门、或非门可直接调用LEDIT标准单元库,在此基础上,设计完成输出缓冲部分,要求从输入IN到OUT的传播延迟时间尽量短,可满足30MHz 时钟频率对信号传输速度的要求(T=2T p)。

二.实验要求

要求:实验报告要涵盖分析计算过程

图1.常用于IO的三态缓冲器

三、实验分析

为了满足时钟频率对信号传输速度的要求,通过计算与非门和或非门的最坏延时,再用全局的时钟周期减去最坏的延时,就得到了反相器的应该满足的延时要求,可以得到反相器N管和P管宽度应该满足什么要求。

标准与非门和或非门的电容、电阻可以通过已知条件算出。

由于与非门、或非门可直接调用LEDIT标准单元库,所以本设计的关键在于后级反相器的设计上(通过调整反相器版图的宽长比等),以满足题目对电路延时的要求。

由于输入信号IN和是理想的阶跃信号,所以输入的延时影响不用考虑。

所以计算的重点在与非门和或非门的延时,以及输出级的延时。

对于与非门,或非门的延时,由于调用的是标准单元,所以它的延时通过提取标准单元的尺寸进行估算,输出级的尺寸则根据延时的要求进行设计。

四、分析计算

计算过程:

(1)全局延时要求为:

30MHz的信号的周期为T=1/f=33ns;

全局延时对Tp的取值要求,Tp<1/2*T=16.7ns;

(2)标准单元延时的计算:

所用到的标准单元如下图所示:

图2.与非门和或非门标准单元版图

通过在ledit软件中使用尺子测量与非门和或非门的晶体管的尺寸,得到了L=2um,W=28um,漏极的长度为LD=6um。

pmos 和nmos采用的是等尺寸的。

NMOS的电阻为:R n=13 kΩ/(w/l)n=13 kΩ/14=0.93 kΩ

PMOS的电阻为:R p=31 kΩ/(w/l)p=31 kΩ/14=2.2 kΩ

栅极的寄生电容为C g=2⨯28⨯1fF=56fF

漏极的寄生电容为C d=6⨯28⨯1fF=168fF

分别计算与非门和或非门的上拉和下拉网络的延迟时间,以找到最坏路径的延时,将最坏延时确定这一级的延时。

CL为后级pmos 的栅极电容,由于栅极电容的量级一般在fF量级,从上面的结果知道,栅电容为56fF,对其延时影响有限,所以我们忽略栅电容的影响,只计算无负载延时。

(3)计算与非门的无负载延时

图三.与非门管级电路图

1、与非门下拉网络的无负载延时,即C1通过一个MOS管放电加上C2通过两个MOS管的放电时间:

T PHL=0.69*(0.93kΩ*168fF+(0.93kΩ+0.93kΩ)*168fF)=0.32ns

2、与非门上拉网络的最坏延迟时间即单管导通的延时:

T PLH =0.68⨯2.3kΩ⨯168fF=0.256ns;

所以比较可知与非门的最坏延时为下拉时间T PHL =0.32ns;(4)或非门的无负载延时

图4.或非门的管级电路图

1、或非门下拉网络的最大延迟即单管导通延迟:

T PHL =0.69*0.93kΩ*168fF=0.108ns;

2、或非门上拉网络的最大延迟:

T PLH =0.69*(2.3kΩ⨯168fF+(2.3kΩ+2.3kΩ)⨯168fF)=0.765ns;所以比较可知或非门的最大延时T PLH =0.765ns。

可见:与非门和或非门的最坏延时由或非门的上拉网络决定,其无负载的延时为0.765ns。

实际中或非门的下级负载是反相器NMOS 的栅极电容,从上面的结果知道,栅电容为56fF,可知栅极电容是比较小的,取一个适当的栅电容值100fF。

(5) 输出级的延时应该满足的数值

当负载电容为100 fF时的延时为:

T P栅=0.69*(2*R P*C g)

=0.69*2*2.2*10^3*100*10^(-15)=0.304ns

得到反相器前的最坏延迟为:

tp=T PLH+ T P栅=0.765ns+0.304ns=1.093ns

所以输出级的延时应该小于16.7ns-1.093ns=15.607ns。

(6)反相器尺寸的确定

由于漏极电容的量级在fF量级,所以,输出的电容负载近似的认为仅有CL=5pf提供。

1、设PMOS的栅宽为W p,栅长由工艺决定2um,所以上拉网络延时应该满足的关系为:

0.69*31 kΩ/(W P/2)*5*10^(-12)F<15.607ns

得到:W P>13.705 um。

2、设NMOS的栅宽为W n,栅长由工艺决定2um,所以上拉网络延时应该满足的关系为:

0.69*13 kΩ/(W n/2)*5*10^(-12)F<15.607ns

得到:W P>5.747 um。

五、版图绘制的过程概述

(1)计算后分析

我们通过计算得到了输出端NMOS和PMOS的最小尺寸,分别为5.747um和13.705um,其对应的栅电容比标准与非门和或非门小很多,前面计算得知标准与非门的栅电容仅仅为栅电容为56fF,可知栅极电容是比较小的,因此我们在前面取的或非门的后级负载电容量100fF是满足设计要求的。

通过上面计算可以知道,NMOS的尺寸只要大于5.747um,PMOS的尺寸只要大于13.705um就可以满足时钟频率对信号传输速度的要求。

由于布线,设计规则的限制,导致版图面积会变大,所以N管有源区的面积可以绘制大一些也并不会增大整体版图面积。

综合选定了反相器PMOS的的宽度为14 um,反相器NMOS的尺寸为12 um。

(2)绘制版图的过程

1、打开ledit软件,新建new layout,通过file中的replace setup选择lights.tdb文件,使用里面的参数设置来绘制版图。

2、调用标准与非门和或非门,将两个门放置在同一高度。

3、下面绘制反相器版图,根据前述的计算,在P衬底上绘制有源区,再画N select,将有源区包裹住,进行设计规则检查。

4、在有源区上绘制1条多晶硅,宽度为最小尺寸,。

需满足最小尺寸要求和伸展出有源区2um的距离。

进行设计规则检查无误后,这样就形成了MOS管的源漏。

4、绘制GND,反相器NMOS的源极通过metal1接地。

需要满足金属包裹接触孔、接触孔离有源区的边界、接触孔离多晶的距离,金属的最小尺寸等设计规则。

5、上述步骤将反相器的NMOS基本绘制完成。

下面绘制PMOS,根据前面计算的尺寸,首先绘制N well,再在N well中绘制P select,然后再绘制Active层,之后绘制多晶硅,伸展出有源区2 um的距离这样就形成了PMOS的源漏区,进行设计规则检查。

6、绘制VDD。

根据电路图知反向器PMOS的源极需要接电源,在有源区打接触孔,通过金属线连接至电源端。

需要满足金属包裹接触孔、接触孔离有源区的边界、接触孔离多晶的距离,金属的最小尺寸等设计规则。

7、上面的步骤基本完成了MOS管的绘制,之后就是连接和信号输入输出问题了。

根据电路图,将与非门和或非门的一个输入连接,引入IN信号,与非门的另一个输入引入En信号,或非门的另一个输入引入En的反向信号。

8、将或非门的输出通过Metal1→通孔→Metal2→通孔→Metal1→多晶硅接触→NMOS的栅极,最后进行设计规则检查。

9、将与非门的输出通过Metal1→通孔→Metal2→通孔→Metal1→多晶硅接触→PMOS的栅极,最后进行设计规则检查。

10、做NMOS和PMOS的衬底接触,进行设计规则检查。

11、将反相器的NMOS和PMOS的漏极通过Metal1连接,在Metal1上打通孔连接Metal2将最终的输出引出,进行设计规则检查。

综合布局布线,设计版图、输入输出如下图5所示。

通过DRC 检测没有错误。

图5. IO的缓冲器版图

(3)版图评价

1、将与非门、或非门、反相器的PMOS都绘制在了一个Nwell中,避免了不同Nwell之间间距的设计规则要求,节省了版图的面积。

2、版图的绘制都是一步一步按照设计规则卡出来的,使得有源区面积小,使用了最小尺寸的多晶硅和金属连线,减小寄生参数,降低RC延时。

3、在版图面积已经确定的情况下,尽可能的加大了有源区的面积,改善了电路性能。

4、在最小面积的有源区上,尽可能多的做了接触孔,减小接触电阻。

5、通过使用Metal2,减小了布线间距,节省了面积。

6、将nMOS管和pMOS管的多晶硅栅极对准,利于工艺上的加工,这样可以由最小长度的多晶硅线条组成栅极连线,这样做可以降低RC延时。

六、总结

这次版图设计我做的针对IO的缓冲器版图设计,明白了几成定阿鲁怎么对延时进行计算和分析,对所学的CMOS集成电路设计有一个更系统更全面的了解,通过两次L-edit软件的训练,进一步加深了L-edit软件的基本操作方法,进一步熟悉了版图的绘制步骤,并能够

. .. . 独立的运用该软件设计版图,灵活的根据要求绘制版图,我想这对我今后学习或者工作大有裨益,今后,我要更多的运用该软件,达到熟练掌握的目的,在我们锻炼动手能力的同时,学到更多的有关专业知识。

感师兄师姐上机时的悉心指导,使我能够进一步完善所绘制的版图,学习到更多知识。

.. ..范文. .。