AD9959数据手册部分内容中文翻译

Protel 99 元器件中英文对照表以及库对照表

CUSIICProtel 99各元器件名字中英文对照表以及各种库的对照电阻AXIAL无极性电容RAD电解电容RB-电位器VR二极管DIODE三极管TO电源稳压块78和79系列TO-126H和TO-126V场效应管和三极管一样整流桥D-44 D-37 D-46单排多针插座CON SIP双列直插元件DIP晶振XTAL1电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻:AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4瓷片电容:RAD0.1-RAD0.3。

其中0.1-0.3指电容大小,一般用RAD0.1电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小。

一般<100uF用B.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6二极管:DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4发光二极管:RB.1/.2集成块:DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5关于零件封装我们在前面说过,除了DEVICE。

Protel 99各元器件名字中英文对照表

Protel 99各元器件名字中英文对照表以及各种库的对照电阻AXIAL无极性电容RAD电解电容RB-电位器VR二极管DIODE三极管TO电源稳压块78和79系列TO-126H和TO-126V场效应管和三极管一样整流桥D-44 D-37 D-46单排多针插座CON SIP双列直插元件DIP晶振XTAL1电阻:RES1,RES2,RES3,RES4;封装属性为axial系列无极性电容:cap;封装属性为RAD-0.1到rad-0.4电解电容:electroi;封装属性为rb.2/.4到rb.5/1.0电位器:pot1,pot2;封装属性为vr-1到vr-5二极管:封装属性为diode-0.4(小功率)diode-0.7(大功率)三极管:常见的封装属性为to-18(普通三极管)to-22(大功率三极管)to-3(大功率达林顿管)电源稳压块有78和79系列;78系列如7805,7812,7820等79系列有7905,7912,7920等常见的封装属性有to126h和to126v整流桥:BRIDGE1,BRIDGE2: 封装属性为D系列(D-44,D-37,D-46)电阻:AXIAL0.3-AXIAL0.7 其中0.4-0.7指电阻的长度,一般用AXIAL0.4瓷片电容:RAD0.1-RAD0.3。

其中0.1-0.3指电容大小,一般用RAD0.1电解电容:RB.1/.2-RB.4/.8 其中.1/.2-.4/.8指电容大小。

一般<100uF用B.1/.2,100uF-470uF用RB.2/.4,>470uF用RB.3/.6二极管:DIODE0.4-DIODE0.7 其中0.4-0.7指二极管长短,一般用DIODE0.4 发光二极管:RB.1/.2集成块:DIP8-DIP40, 其中8-40指有多少脚,8脚的就是DIP8贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5关于零件封装我们在前面说过,除了DEVICE。

altium designer 必备:AD常用术语中英文对译 免费下载

原理图常用库文件:Miscellaneous Devices.ddbDallas Microprocessor.ddbIntel Databooks.ddbProtel DOS Schematic Libraries.ddb PCB元件常用库:Advpcb.ddbGeneral IC.ddbMiscellaneous.ddb部分 分立元件库元件名称及中英对照 AND 与门ANTENNA 天线BATTERY 直流电源BELL 铃,钟BVC 同轴电缆接插件BRIDEG 1 整流桥(二极管)BRIDEG 2 整流桥(集成块)BUFFER 缓冲器BUZZER 蜂鸣器CAP 电容CAPACITOR 电容CAPACITOR POL 有极性电容CAPVAR 可调电容CIRCUIT BREAKER 熔断丝COAX 同轴电缆CON 插口CRYSTAL 晶体整荡器DB 并行插口DIODE 二极管DIODE SCHOTTKY 稳压二极管 DIODE VARACTOR 变容二极管DPY_3-SEG 3段LEDDPY_7-SEG 7段LEDDPY_7-SEG_DP 7段LED(带小数点) ELECTRO 电解电容FUSE 熔断器INDUCTOR 电感INDUCTOR IRON 带铁芯电感 INDUCTOR3 可调电感JFET N N沟道场效应管JFET P P沟道场效应管LAMP 灯泡LAMP NEDN 起辉器LED 发光二极管METER 仪表MICROPHONE 麦克风MOSFET MOS管MOTOR AC 交流电机MOTOR SERVO 伺服电机NAND 与非门NOR 或非门NOT 非门NPN NPN三极管NPN-PHOTO 感光三极管OPAMP 运放OR 或门PHOTO 感光二极管PNP 三极管NPN DAR NPN三极管PNP DAR PNP三极管POT 滑线变阻器PELAY-DPDT 双刀双掷继电器 RES1.2 电阻RES3.4 可变电阻RESISTOR BRIDGE ? 桥式电阻 RESPACK ? 电阻SCR 晶闸管PLUG ? 插头PLUG AC FEMALE 三相交流插头 SOCKET ? 插座SOURCE CURRENT 电流源 SOURCE VOLTAGE 电压源 SPEAKER 扬声器SW ? 开关SW-DPDY ? 双刀双掷开关SW-SPST ? 单刀单掷开关SW-PB 按钮THERMISTOR 电热调节器 TRANS1 变压器TRANS2 可调变压器TRIAC ? 三端双向可控硅 TRIODE ? 三极真空管 VARISTOR 变阻器ZENER ? 齐纳二极管DPY_7-SEG_DP 数码管SW-PB 开关74系列:74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器 74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器 74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器 74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器 74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器 74LS253 TTL 三态输出双4选1数据选择器/复工器 74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器 74LS258 TTL 三态反码四2选1数据选择器/复工器 74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器 74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器 74LS365 TTL 门使能输入三态输出六同相线驱动器 74LS365 TTL 门使能输入三态输出六同相线驱动器 74LS366 TTL 门使能输入三态输出六反相线驱动器 74LS367 TTL 4/2线使能输入三态六同相线驱动器 74LS368 TTL 4/2线使能输入三态六反相线驱动器 74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器 74LS365 TTL 门使能输入三态输出六同相线驱动器 74LS366 TTL 门使能输入三态输出六反相线驱动器 74LS367 TTL 4/2线使能输入三态六同相线驱动器 74LS368 TTL 4/2线使能输入三态六反相线驱动器 74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器 74LS466 TTL 三态反相2与使能八总线缓冲器 74LS467 TTL 三态同相2使能端八总线缓冲器 74LS468 TTL 三态反相2使能端八总线缓冲器 74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动 74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器 74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器74LS645 TTL 三态输出八同相总线传送接收器 74LS670 TTL 三态输出4×4寄存器堆74LS73 TTL 带清除负触发双J-K触发器74LS74 TTL 带置位复位正触发双D触发器74LS76 TTL 带预置清除双J-K触发器74LS83 TTL 四位二进制快速进位全加器74LS85 TTL 四位数字比较器74LS86 TTL 2输入端四异或门74LS90 TTL 可二/五分频十进制计数器74LS93 TTL 可二/八分频二进制计数器74LS95 TTL 四位并行输入\输出移位寄存器 74LS97 TTL 6位同步二进制乘法器CD系列::CD4000 双3输入端或非门+单非门 TICD4001 四2输入端或非门 HIT/NSC/TI/GOLCD4002 双4输入端或非门 NSCCD4006 18位串入/串出移位寄存器 NSCCD4007 双互补对加反相器 NSCCD4008 4位超前进位全加器 NSCCD4009 六反相缓冲/变换器 NSCCD4010 六同相缓冲/变换器 NSCCD4011 四2输入端与非门 HIT/TICD4012 双4输入端与非门 NSCCD4013 双主-从D型触发器 FSC/NSC/TOSCD4014 8位串入/并入-串出移位寄存器 NSCCD4015 双4位串入/并出移位寄存器 TICD4016 四传输门 FSC/TICD4017 十进制计数/分配器 FSC/TI/MOTCD4018 可预制1/N计数器 NSC/MOTCD4019 四与或选择器 PHICD4020 14级串行二进制计数/分频器 FSCCD4021 08位串入/并入-串出移位寄存器 PHI/NSC CD4022 八进制计数/分配器 NSC/MOTCD4023 三3输入端与非门 NSC/MOT/TICD4024 7级二进制串行计数/分频器 NSC/MOT/TI CD4025 三3输入端或非门 NSC/MOT/TICD4026 十进制计数/7段译码器 NSC/MOT/TICD4027 双J-K触发器 NSC/MOT/TICD4028 BCD码十进制译码器 NSC/MOT/TICD4029 可预置可逆计数器 NSC/MOT/TICD4030 四异或门 NSC/MOT/TI/GOLCD4031 64位串入/串出移位存储器 NSC/MOT/TI CD4032 三串行加法器 NSC/TICD4033 十进制计数/7段译码器 NSC/TICD4034 8位通用总线寄存器 NSC/MOT/TICD4035 4位并入/串入-并出/串出移位寄存 NSC/MOT/TI CD4038 三串行加法器 NSC/TICD4040 12级二进制串行计数/分频器 NSC/MOT/TICD4041 四同相/反相缓冲器 NSC/MOT/TICD4042 四锁存D型触发器 NSC/MOT/TICD4043 4三态R-S锁存触发器("1"触发) NSC/MOT/TI CD4044 四三态R-S锁存触发器("0"触发) NSC/MOT/TI CD4046 锁相环 NSC/MOT/TI/PHICD4047 无稳态/单稳态多谐振荡器 NSC/MOT/TICD4048 4输入端可扩展多功能门 NSC/HIT/TICD4049 六反相缓冲/变换器 NSC/HIT/TICD4050 六同相缓冲/变换器 NSC/MOT/TICD4051 八选一模拟开关 NSC/MOT/TICD4052 双4选1模拟开关 NSC/MOT/TICD4053 三组二路模拟开关 NSC/MOT/TICD4054 液晶显示驱动器 NSC/HIT/TICD4055 BCD-7段译码/液晶驱动器 NSC/HIT/TICD4056 液晶显示驱动器 NSC/HIT/TICD4059 “N”分频计数器 NSC/TICD4060 14级二进制串行计数/分频器 NSC/TI/MOTCD4063 四位数字比较器 NSC/HIT/TICD4066 四传输门 NSC/TI/MOTCD4067 16选1模拟开关 NSC/TICD4068 八输入端与非门/与门 NSC/HIT/TICD4069 六反相器 NSC/HIT/TICD4070 四异或门 NSC/HIT/TICD4071 四2输入端或门 NSC/TICD4072 双4输入端或门 NSC/TICD4073 三3输入端与门 NSC/TICD4075 三3输入端或门 NSC/TICD4076 四D寄存器CD4077 四2输入端异或非门 HITCD4078 8输入端或非门/或门CD4081 四2输入端与门 NSC/HIT/TICD4082 双4输入端与门 NSC/HIT/TICD4085 双2路2输入端与或非门CD4086 四2输入端可扩展与或非门CD4089 二进制比例乘法器CD4093 四2输入端施密特触发器 NSC/MOT/STCD4094 8位移位存储总线寄存器 NSC/TI/PHICD4095 3输入端J-K触发器CD4096 3输入端J-K触发器CD4097 双路八选一模拟开关CD4098 双单稳态触发器 NSC/MOT/TICD4099 8位可寻址锁存器 NSC/MOT/STCD40100 32位左/右移位寄存器CD40101 9位奇偶较验器CD40102 8位可预置同步BCD减法计数器CD40103 8位可预置同步二进制减法计数器CD40104 4位双向移位寄存器CD40105 先入先出FI-FD寄存器CD40106 六施密特触发器 NSC\TICD40107 双2输入端与非缓冲/驱动器 HAR\TICD40108 4字×4位多通道寄存器CD40109 四低-高电平位移器CD4529 双四路/单八路模拟开关 CD4530 双5输入端优势逻辑门CD4531 12位奇偶校验器CD4532 8位优先编码器CD4536 可编程定时器CD4538 精密双单稳CD4539 双四路数据选择器CD4541 可编程序振荡/***CD4543 BCD七段锁存译码,驱动器CD4544 BCD七段锁存译码,驱动器CD4547 BCD七段译码/大电流驱动器CD4549 函数近似寄存器CD4551 四2通道模拟开关CD4553 三位BCD计数器CD4555 双二进制四选一译码器/分离器CD4556 双二进制四选一译码器/分离器CD4558 BCD八段译码器CD4560 "N"BCD加法器CD4561 "9"求补器CD4573 四可编程运算放大器CD4574 四可编程电压比较器CD4575 双可编程运放/比较器CD4583 双施密特触发器CD4584 六施密特触发器CD4585 4位数值比较器CD4599 8位可寻址锁存器CD40110 十进制加/减,计数,锁存,译码驱动 ST CD40147 10-4线编码器 NSC\MOTCD40160 可预置BCD加计数器 NSC\MOTCD40161 可预置4位二进制加计数器 NSC\MOT CD40162 BCD加法计数器 NSC\MOTCD40163 4位二进制同步计数器 NSC\MOTCD40174 六锁存D型触发器 NSC\TI\MOTCD40175 四D型触发器 NSC\TI\MOTCD40181 4位算术逻辑单元/函数发生器CD40182 超前位发生器CD40192 可预置BCD加/减计数器(双时钟) NSC\TI CD40193 可预置4位二进制加/减计数器 NSC\TICD40194 4位并入/串入-并出/串出移位寄存 NSC\MOT CD40195 4位并入/串入-并出/串出移位寄存 NSC\MOT CD40208 4×4多端口寄存器型号 器件名称 厂牌 备注CD4501 4输入端双与门及2输入端或非门CD4502 可选通三态输出六反相/缓冲器CD4503 六同相三态缓冲器CD4504 六电压转换器CD4506 双二组2输入可扩展或非门CD4508 双4位锁存D型触发器CD4510 可预置BCD码加/减计数器CD4511 BCD锁存,7段译码,驱动器CD4512 八路数据选择器CD4513 BCD锁存,7段译码,驱动器(消隐)CD4514 4位锁存,4线-16线译码器CD4515 4位锁存,4线-16线译码器CD4516 可预置4位二进制加/减计数器CD4517 双64位静态移位寄存器CD4518 双BCD同步加计数器CD4519 四位与或选择器CD4520 双4位二进制同步加计数器CD4521 24级分频器CD4522 可预置BCD同步1/N计数器CD4526 可预置4位二进制同步1/N计数器 CD4527 BCD比例乘法器CD4528 双单稳态触发器。

高性能DDS芯片AD9959及其应用

(4) 可以有一个通道工作在16电平调制模式, 余下的通道工作在单频模式;

(5) 单频模式下, 可以控制每个通道的 输 出 幅度斜率;

(6) P2和P3引 脚 用 于 控 制 输 出 幅 度 斜 率 时 , 任意两个通道可同时工作在2电平调制模式, 也 可同时工作在线性调频或调相模式;

图2 单bit两线模式的串口写时序

图3 双bit模式的串口写时序

6 电子元器件应用 2007.6 www.ecda.cn

第9卷 第6期 2007年6月

电子元器件应用 Electronic Component & Device Applications

Vol.9 No.6 June. 2007

CLR CE

0 引言

◇ 内置时钟倍频锁相环 ( 4 ̄20倍倍频) 。

AD9959是 美 国ADI 公 司 最 新 推 出 的 一 款 四 通 道高速直接数字频率合成器。该芯片内部集成了 四个DDS核, 因此可对四个内部同步输出通道独 立进行编程。通过一个公用系统时钟在芯片内部 同 步 其 独 立 的 通 道 , AD9959可 以 对 由 于 模 拟 处 理 (例 如 滤 波 、 放 大) 或 者PCB布 线 失 配 而 产 生 的外部信号通道的不均衡进行有效的校正, 从而 使系统工程师用相当少的时间和精力去处理这个 通常很复杂的系统设计问题。

AD9959 的 四 个 通 道 可 共 享 一 组 寄 存 器 地 址 , 这种地址共享机制其得可以同时向四个通道的配 置寄存器写入相同的数据。当需要对四个通道进 行不同设置时, 可以通过设置通道使能位来各自 独立地写入每个通道设置的数据。

一个串口通信周期分为指令周期和数据读写 周期两个阶段。首先传送指令阶段的8位指令字, 对应于SCLK的8个上升沿, 然后执行由指令设定 的1~4 个字节的数据读写, 完成后再等待下一个 指令周期的到来。

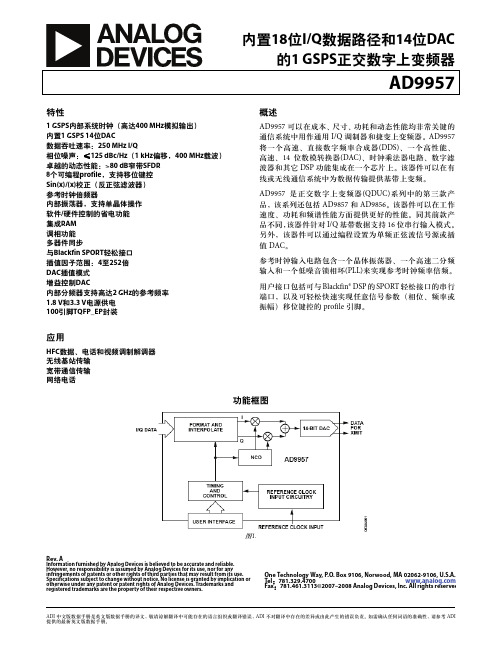

AD9957_cn

内置18位I/Q 数据路径和14位DAC的1 GSPS 正交数字上变频器AD9957Rev. AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P .O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel :781.329.4700 Fax :781.461.3113©2007–2008 Analog Devices, Inc. All rights reserved特性1 GSPS 内部系统时钟(高达400 MHz 模拟输出) 内置1 GSPS 14位DAC数据吞吐速率:250 MHz I/Q相位噪声:≤125 dBc/Hz (1 kHz 偏移,400 MHz 载波) 卓越的动态性能:>80 dB 窄带SFDR 8个可编程profile ,支持移位键控 Sin(x)/(x)校正(反正弦滤波器) 参考时钟倍频器内部振荡器,支持单晶体操作 软件/硬件控制的省电功能 集成RAM 调相功能 多器件同步与Blackfin SPORT 轻松接口 插值因子范围:4至252倍 DAC 插值模式 增益控制DAC内部分频器支持高达2 GHz 的参考频率 1.8 V 和3.3 V 电源供电 100引脚TQFP_EP 封装应用HFC 数据、电话和视频调制解调器 无线基站传输 宽带通信传输 网络电话概述AD9957可以在成本、尺寸、功耗和动态性能均非常关键的通信系统中用作通用I/Q 调制器和捷变上变频器。

DDSAD9959应用电路和配置源程序

DDS AD9959应用电路和配置源程序AD9959是一款有四个DDS通道,最高达500M SPS的数字频率合成芯片。

常用电路接法:主要程序:#include "config.h"void delay(void){unsigned int i;for(i=0;i<10;i++);}/***************************************************************************** 功能描述: 加载寄存器,上升延有效*****************************************************************************/ void run(void){CLR_IOUPDATE;CLR_IOUPDATE;CLR_IOUPDATE;CLR_IOUPDATE;CLR_IOUPDATE;CLR_IOUPDATE;CLR_IOUPDATE;SET_IOUPDATE;SET_IOUPDATE;}/***************************************************************************** 函数名: write_a_byte功能描述: 通过串口写一个字节,MSB first,上升延有效*****************************************************************************/ void write_a_byte(uint8 w_data){uint8 i;for(i=0;i<8;i++){if(w_data & 0x80){SET_SDIO0;}else{CLR_SDIO0;}w_data <<= 1;SET_DDSSCLK;CLR_DDSSCLK;}}/***************************************************************************** 函数名: write_CSR功能描述: 写CSR寄存器:*****************************************************************************/ void write_CSR(uint8 w_data){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x00); //write address 0. CSR's address is 0.write_a_byte(w_data);SET_DDSCS;SET_SDIO3;}void write_FR1(uint8 w_data1,uint8 w_data2,uint8 w_data3){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x01); //write address 1. FR1's address is 0x01write_a_byte(w_data1);write_a_byte(w_data2);write_a_byte(w_data3);SET_DDSCS;SET_SDIO3;}void write_FR2(uint8 w_data1,uint8 w_data2){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x02); //write address 2write_a_byte(w_data1);write_a_byte(w_data2);SET_DDSCS;SET_SDIO3;}void write_CFR(uint8 w_data1,uint8 w_data2,uint8 w_data3){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x03);write_a_byte(w_data1);write_a_byte(w_data2);write_a_byte(w_data3);SET_DDSCS;SET_SDIO3;}void write_CTW0(uint32 F_word) //Channel Frequency Tuning Word (CTW0){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x04);write_a_byte(((unsigned char *)(&F_word))[3]);write_a_byte(((unsigned char *)(&F_word))[2]);write_a_byte(((unsigned char *)(&F_word))[1]);write_a_byte(((unsigned char *)(&F_word))[0]);SET_DDSCS;SET_SDIO3;}void write_CPW0(uint16 P_word) //Channel Phase1 Offset Word (CPW0) (0x05) {CLR_SDIO3;CLR_DDSCS;write_a_byte(0x05);write_a_byte(((unsigned char *)(&P_word))[1]&0x3F);write_a_byte((((unsigned char *)(&P_word))[0]));SET_DDSCS;SET_SDIO3;}void write_ACR(uint32 A_word){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x06);write_a_byte(((unsigned char *)(&A_word))[3]);write_a_byte(((unsigned char *)(&A_word))[2]);write_a_byte(((unsigned char *)(&A_word))[1]);SET_DDSCS;SET_SDIO3;}void write_LSR(uint8 rising,uint8 falling){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x07);write_a_byte(rising);write_a_byte(falling);SET_DDSCS;SET_SDIO3;}void write_RDW(uint32 rising){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x08);write_a_byte(((unsigned char *)(&rising))[3]);write_a_byte(((unsigned char *)(&rising))[2]);write_a_byte(((unsigned char *)(&rising))[1]);write_a_byte(((unsigned char *)(&rising))[0]);SET_DDSCS;SET_SDIO3;}void write_FDW(uint32 falling){CLR_SDIO3;CLR_DDSCS;write_a_byte(0x09);write_a_byte(((unsigned char *)(&falling))[3]);write_a_byte(((unsigned char *)(&falling))[2]);write_a_byte(((unsigned char *)(&falling))[1]);write_a_byte(((unsigned char *)(&falling))[0]);SET_DDSCS;SET_SDIO3;}void write_CTWn(uint8 n,uint32 w_data){CLR_SDIO3;CLR_DDSCS;write_a_byte(n+0x09); //CTWn's address is n+0x09.n>=1 and n<=15.write_a_byte(((unsigned char *)(&w_data))[3]);write_a_byte(((unsigned char *)(&w_data))[2]);write_a_byte(((unsigned char *)(&w_data))[1]);write_a_byte(((unsigned char *)(&w_data))[0]);SET_DDSCS;SET_SDIO3;}#define PLL_DIV 5#define systemp_frequency (22.1184*1000000*PLL_DIV)void set_frequency(uint32 f){unsigned long int temp;temp=(unsigned long int)f*(0xFFFFFFFF/(float)systemp_frequency+1.0/systemp_frequency);write_CTW0(temp);}uint32 change(uint32 f){unsigned long int temp;temp=(unsigned long int)f*(0xFFFFFFFF/(float)systemp_frequency+1.0/systemp_frequency);return temp;}void AD9959_init(void){uint16 i;DDS_DDR = 0xff;CLR_DDSRESET;for(i=0;i<10000;i++);SET_DDSCS;CLR_DDSSCLK;SET_SDIO3;SET_DDSRESET;for(i=0;i<10000;i++);CLR_DDSRESET;for(i=0;i<100;i++);}0 引言AD9959可以对由于模拟处理(例如滤波、放大)或者PCB布线失配而产生的外部信号通道的不均衡进行有效的校正,从而使系统工程师用相当少的时间和精力去处理这个通常很复杂的系统设计问题。

AD9953资料

AD9953

tuning word). The frequency tuning and control words are loaded into the AD9953 via a serial I/O port. The AD9953 includes an integrated 1024x32 Static RAM to support flexible frequency sweep capability in several modes. The AD9953 is specified to operate over the extended industrial temperature range of -40° to +85°C.

RAM Control

32

System Clock

RAM Data

RAM Addr

DDS Clock

3 10

Phase Accumulator RESET

14

32

z-1

32

DDS Clock

M U X

14 RAM Data <31:18>

θ OSK PwrDwn

Sync

I/O Update Sync Out

M U X 0

SYNC

Timing & Control Logic

4

Control Registers

Oscillator/Buffer

RefClk RefClk

ENABLE

4x-20x Clock Multipler

M U X

System Clock

Crystal Out

PS<1:0> IO Port

AD9859数据手册中文翻译

AD9859数据手册特征400 msps内部时钟速度集成10位DAC32位调谐字相位噪声≤–120 dBc/Hz@1 kHz偏移量(DAC输出)卓越的动态性能160兆赫(±100千赫偏移)输出时>75分贝SFDR串行I/O控制1.8V电源软硬件控制电源关闭48铅TQFP/EP包支持大多数输入电平为5 V的数字输入PLL REFCLK乘法器(4×到20×)内部振荡器;可由单晶体驱动相位调制能力多芯片同步简介AD9859是一种直接数字合成器(DDS),具有一个10位DAC,工作速度高达400 msps。

AD9859采用先进的DDS技术,结合内部高速、高性能的DAC,形成一个数字可编程、完整的高频合成器,能够在高达200兆赫的频率灵活模拟输出正弦波形。

AD9859提供快速跳频和微调解决方案(32位频率调谐字)。

频率调节控制字通过串行I/O端口加载到AD9859中。

AD9859规定在-40°C至+105°C的延伸工业温度范围内运行。

AD9859-电气规范除非另有说明,否则,AVDD、DVDD=1.8 V±5%、DVDDU I/O=3.3 V±5%、RSET=3.92 kΩ、外部参考时钟频率=20 MHz,且在启用了20×参考时钟乘法器情况下。

DAC输出必须引用到AVDD,而不是AGND。

引脚功能描述40 SCLK I 该引脚用作I/O操作的串行数据时钟。

41 SDIO I/O 当将I/O端口作为3线串行端口操作时,此引脚仅用作串行数据输入。

当作为2线串行端口操作时,此插脚是双向串行数据插脚。

43 DVDD_I/O I 数字电源(仅适用于I/O单元,3.3 V)。

44 SYNC_IN I 用于同步多个AD9859S的输入信号。

此输入连接到主AD9859的同步时钟输出。

45 SYNC_CLK O 时钟输出引脚用作外部硬件的同步器。

AD9952 Evaluation Board Datasheet说明书

功能框图图1.DC/PHASE CORRECTION DC/PHASE CORRECTIONC SS C L KS D I OSERIAL PORT INTERFACE15141323892325262838VPOS_3P3DECL1TO DECL4211119303136273340101VPOS_5VLDO VCOLDO 2.5VRFIN0RFIN12922POLYPHASE FILTERLOIN–REFINLOIN+I+I–Q–Q+QUAD DIVIDERPLL343935547611990-001Rev. ADocument FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013–2014 Analog Devices, Inc. All rights reserved. Technical Support 695 MHz 至2700 MHz 正交解调器,集成小数N 分频PLL 和VCOADRF6820产品特性集成小数N 分频PLL 的I/Q 解调器RF 输入频率范围:695 MHz 至2700 MHz 内部LO 频率范围:356.25 MHz 至2850 MHz 输入P1dB :14.5 dBm (1900 MHz RF) 输入IP3:35 dBm (1900 MHz RF) 可编程HD3/IP3调整单刀双掷(SPDT) RF 输入开关RF 数字步进衰减范围:0 dB 至15 dB集成式RF 可调谐巴伦,支持单端50 Ω输入 多核集成式VCO解调1 dB 带宽:600 MHz 4个可选基带增益和带宽模式数字可编程LO 相位失调和直流零点可通过三线式串行端口接口(SPI)进行编程 40引脚、6 mm x 6 mm LFCSP 封装应用蜂窝W-CDMA/GSM/LTE 数字预失真(DPD)接收器 微波点对点无线电概述ADRF6820是一款高度集成的解调器和频率合成器,非常适合用于下一代通信系统中。

2017全国大学生电子设计竞赛H题

2017全国大学生电子设计竞赛H 题作者:日期:2017年全国大学生电子设计竞赛远程幅频特性测试仪(H题)2017年08月12日本幅频特性测试装置采用STM32F407为主控芯片,通过集成DDS芯片AD9959作为信号源,实现了幅度和频率的动态可调;通过级联两块AD8367作为放大器,实现了增益0-40dB连续可调,具有较好的噪声抑制效果;通过AD8310 对数检波模块,实现了不同频率信号幅度的测量,并且能够定性的绘制出幅频特性曲线.关键词:幅频特性测试装置;DDS; VGA ;低噪;对数检波AbstractThe amp litude freque ncy characteristic test device uses STM32F407 as the main control chip, through the integrated DDS chip AD9959 as the signal source, to achieve the amp litude and freque ncy of the dyn amic adjustable; through the cascade of two AD8367 as an amp lifier, to achieve a gain of 0-40dB con ti nu ously adjustable , With good noise suppression effect; through the AD8310 logarithmic detection module, to achieve a different frequency signal amplitude measurement, and can qualitatively draw the amp litude and freque ncy characteristics of the curve.Keyword: amplitude frequency characteristic test device; DDS;VGA;lownoise ;目录1.1方案比较与选择1.2方案描述 ......二.理论分析与计算2.1 DDS模块……2.2 放大器模块…2.3 幅值测量模块2. 4 n型衰减网络.电路与程序设计.3.1电路设计.......3. 2 程序设计 .....四.测试方案与测试结果五.结论远程幅频特性测试装置(H题).系统方案1.方案比较与选择1)信号源模块:方案一:采用直接数字频率合成(DDS)方案。

AD9957中文资料

内置18位I/Q 数据路径和14位DAC的1 GSPS 正交数字上变频器AD9957Rev. AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P .O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel :781.329.4700 Fax :781.461.3113©2007–2008 Analog Devices, Inc. All rights reserved特性1 GSPS 内部系统时钟(高达400 MHz 模拟输出) 内置1 GSPS 14位DAC数据吞吐速率:250 MHz I/Q相位噪声:≤125 dBc/Hz (1 kHz 偏移,400 MHz 载波) 卓越的动态性能:>80 dB 窄带SFDR 8个可编程profile ,支持移位键控 Sin(x)/(x)校正(反正弦滤波器) 参考时钟倍频器内部振荡器,支持单晶体操作 软件/硬件控制的省电功能集成RAM 调相功能 多器件同步与Blackfin SPORT 轻松接口 插值因子范围:4至252倍 DAC 插值模式 增益控制DAC内部分频器支持高达2 GHz 的参考频率 1.8 V 和3.3 V 电源供电 100引脚TQFP_EP 封装应用HFC 数据、电话和视频调制解调器 无线基站传输 宽带通信传输 网络电话概述AD9957可以在成本、尺寸、功耗和动态性能均非常关键的通信系统中用作通用I/Q 调制器和捷变上变频器。

AD9954芯片中文数据表(部分)

AD9954芯片中文数据表(部分)操作模式单音信号模式在单音信号模式下,DDS核使用了一个单独的调谐字(tuningword)。

存储在FTW0中的任何值可被用来做相位累加。

这个值仅能手动改变,通过向FTW0写一个新值并更新I/O来实现。

相位调整可通过相位偏置寄存器实现。

RAM可控制操作模式直接转换模式直接转换模式使能FSK调制或PSK调制。

AD9954在直接转换模式可以编程,其通过写RAM使能位为真并将每个期望的profile的RAM片段模式控制位编程成逻辑000(b)实现。

对于当前profile,该模式仅读取了RAM片段起始地址的内容。

直接转换模式下,没有地址ramping可用。

为了执行4-toneFSK,对于直接转换模式及一个唯一的起始地址值,使用者对每一个RAM片段控制字编程。

另外,RAM使能位被写为真,这使得RAM、RAM目的文件位被写成fale,设置RAM输出为频率调谐字。

Profile〈1:0〉输入为4-toneFSK数据输入。

当profile被改变时,存储在新的profile中的频率调谐字被加载到相位累加器中并且被用做相位连续型式中的当前存储值的增量。

相位-偏置字驱使相位偏置加法器。

对于数据而言,2-toneFSK可通过仅使用一个profilepin来完成。

对于为了PSK调制将AD9954编程和FSK是相似的,除了RAM目的文件位设置为逻辑“1”外,使RAM输出驱动相位偏置加法器。

FTW0驱动输入至相位累加器。

Togglingtheprofilepin改变(调制)当前相位值。

RAM的upper14位驱动相位加法器(〈31:18〉)。

当RAM目的文件位被设置时,RAM输出的Bit〈17:0〉未被使用。

直接转换模式下,无停留位(no-dwell)是一项禁忌注意事项。

Ramp-Up模式Ramp-Up模式,结合分割的RAM容量,允许多达4种不同的“weepprofile”在AD9954中编程。

AD9中的英文词汇对照翻译

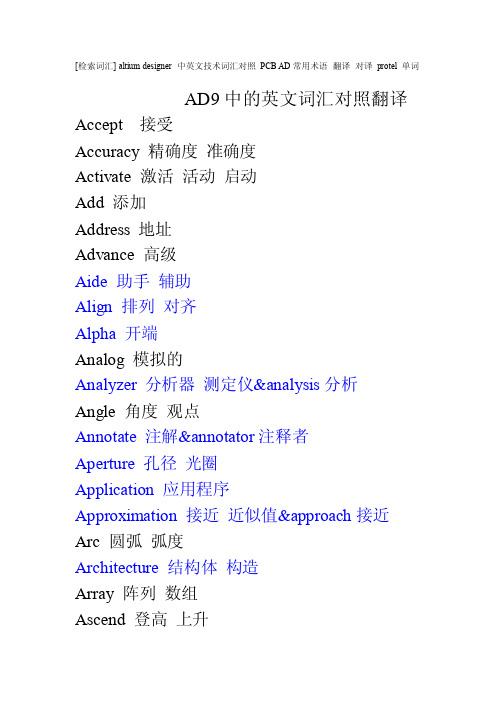

[检索词汇] altium designer 中英文技术词汇对照PCB AD常用术语翻译对译protel 单词AD9中的英文词汇对照翻译Accept 接受Accuracy 精确度准确度Activate 激活活动启动Add 添加Address 地址Advance 高级Aide 助手辅助Align 排列对齐Alpha 开端Analog 模拟的Analyzer 分析器测定仪&analysis分析Angle 角度观点Annotate 注解&annotator注释者Aperture 孔径光圈Application 应用程序Approximation 接近近似值&approach接近Arc 圆弧弧度Architecture 结构体构造Array 阵列数组Ascend 登高上升Assembly 集合装配Associate 关联的辅助的Asynchronous 异步的&chronous同步的Automatical 自动的Access 存取通道接近Action 行动作用Active 积极的活泼的Adder 加法器Administration 管理员管理器Aggressor 干扰源入侵者&Aggress攻击侵略Alias 别名化名混淆Allow 允许Always 总是永远Analysis 分析研究Animation 动画Any 任意的Applicable 可应用的适用的Apply 应用Arbiter 仲裁器bus arbiter总线仲裁器Architect 设计者制造者Area 面积范围Arrange 安排排列调整Arrow 箭形箭头Assembler 装配器汇编Assign 分配分派指定assign a value分配一个值赋值Astable 非稳态的多谐振荡的Attempt 尝试Available 有效的有用的Backup 备用Bar 标签Base 基极基础基地Batch 批处理批量Begin 开始创建Behavior 行为举止态度Bell 铃钟Between 两者之间Bidir 允许双向unidir单向Bidirectional 双向性Bill 清单Binary 二进制二元的Bistable 双稳bistable unit 双稳态部件Bit 位Bitmap 位图&button bitmap键盘键位图Black 黑色黑色的Blind 盲孔Blip 标志信号&collision blip碰撞标志Block 框栏隔阻&title block标题栏Board 板子牌子委员会Body 物体主干主体Boolean 布尔值Border 边线border set边缘集Bottom 底部Bounce 反弹抖动Breakpoint 中断点断点Broken 破裂的损坏的Browse 浏览browse through浏览Buffer 缓冲器&screen buffer屏幕缓冲Build 构建Bullet 锥形体子弹Bury 埋藏Bus 总线Butterfly 蝶形Button 按钮Bypass 省略Byte 字节Cable 电缆Calculation 计算估计CAM(computer aided manufacturing)计算机辅助制造Cancel 作废删除Capacitor 电容Caption 标题Capture 捕获收集记录Case 实情案例Category 类目范畴部属Cathode 阴极Center 中心Centimeter 厘米Chain 链Change 改变Channel 通道Charge 充电指责指示Check 检测Chart 制成图表Child 子女Chip 集成芯片Circuit 电路Circular 圆环弧形Class 阶层等级Cleanup 清扫工作Clear 清除清零Clearance 清除余地间隙Click 单击点击Clipboard 剪切板Clock 时钟Close 关闭结束Closure 关闭闭幕Code 编码代码Collector 集电极Color 彩色着色Colour 颜色Column 圆柱纵列栏目Combination 组合Comma 逗号Command 命令Comparator 比较器Community 社区群落Compilation 编辑物Compatible 兼容的和谐的Component 元器件组成成分Compile 编辑收集汇编Computer 计算机Composite 合成的复合的综合的Condition 条件Concurrent 并发事件同行Configure 配置Confidence 置信度自信信赖Conflict 冲突Confirm 确认证实Connector 连接端Connectivity 连线Constraint 约束限制因素Console 主控台表盘托架Consumer 用户使用者Construction 构造Continue 继续延伸Contract 缩短Control 控制Convert 转化转变Coordinate 坐标Copper 铜Copy 拷贝复制Core 核Cord 绳线索Corner 角落拐角Corporation 公司企业法人Counter 计数器Courtyard 天井庭院Create 创建Cross 十字符号混合Crosspoint 插入测试点Crosstalk 串扰CRTCrystal 晶体Current 电流当前的流行的Cursor 光标游标指示器Custom 惯例Customer 用户客户Cutout 切出划出挖空Cycle 周期Comment 注释发表评论说明书Dashed 下划线Data 数字数据Databse 数据库资料库Date 日期Daughtrer 子系子插件派生Debug 排错调试Dead 死的Decimal 十进制小数Decade 十进制十年Default 默认值缺省值弃权Decoder 译码器Definition 定义式限定分辨率Define 定义下定义Delay 延时Degree 度等级Demo 演绎演示版Delete 删除Demote 降级降低Deny 否认Description 描述Designator 标识指示者Designer 设计师Destination 目标目的Detail 细节零件Device 装置设备图样器件Diagram 示意图Dialog 对话Diagonal 对角线Difference 差异查分差额Diamond 菱形钻石Digital 数字的Different 不同的Dimension 尺度Dim 朦胧暗淡Direct 指示指令Diode 二极管Disable 无能无效无用Director 指南指导咨询Disk 圆盘Discharge 放点排出释放Distribution 分配分布分发Display 显示Dock 停放连接接驳Divider 分配分割Dot 小点虚线点缀Donut 环形Download 下载Down 下降Draw 绘制描写冲压成型Drag 拖拽Drop 下拉滴落遗漏Drill 钻Duplicate 复制副本Dual 双数的两倍Duty 占空比Edge 边缘Edit 编辑Efficient 高效的有能力的Electrical 电气的电学的电力的Ellipse 椭圆Embed 潜入插入Emitter 射极Emulate 效法Enable 使能激活有效Encoder 编码器End 结束Engineer 设计建造工程师Enter 进入参加Entity 实体Entry 入口Enum 列举型别Error 错误Evaluation 评价评估鉴定Example 例子Excel 胜过优秀突出Execute 执行实施签署Exist 存在的现有的Expand 扩大推广展开Expansion 扩大扩展扩张Expiry 终止期满Explode 爆炸分解Exponent 指数Export 输出出品Explore 探究查询Extra 额外的附加的External 外部的外面的外形Extrude 压制突出Extract 提取摘录Fabrication 制造Frequency 频率Failure 无效毁坏的Function 函数功能False 虚假的伪造的Fail 失败不足Fanout 扇出Fall 下降降落落差Favorite 最爱的(sth sb)Famale 凹的阴的Figure 图形Fatal 致命的Fill 填充Field 现场域范围Filter 过滤器File 文件Find 建立发现Film 胶片First 第一首先Finally 最终的Flash 闪光闪烁曝光Finish 完成结束Flatten 弄平弄直Fit 适合相配Flip-flop 触发器Flat 平的平坦的Floorplan 层平面图Flip 倒转Focus 集中聚焦Float 发行Footprint 封装Flow 流动源自Format 格式Folder 文件夹折叠Formula 公式Force 强制FPGAForum 讨论论坛会Frame 框图塑造Free 自由Framework 架构结构Form 从····起由于Gate 门Generate 产生导致造成Graphic 图形green 绿色Grid 栅格Ground 地面基础Group 组类集聚Guide 引导指南手册Hard 坚硬的困难的Hardware 硬件设备五金Harmonic 谐波谐振Harness 束Hatch 策划画影线舱口Hazard 冒险Hazy 模糊的混浊的Height 高度Help 帮助Hexadecimal 十六进制Hide 隐藏Hierarchy 体系分层系列High 高的高级的高尚的Hint 暗示History 历史记录Horizontal 水平横向Hug 拥抱紧靠Ideal 理想的Identical 相同的相等的恒等的Identifier 识别符Identify 识别标记IDF(integrated data file) 综合资料文件IEEE 电气电子工程师协会Impedance 阻抗Ignore 忽略Import 输入导入Imperial 英制的Include 包含Incident 事变入射Index 索引Increment 增量Inductor 电感Indication 指示表示Information 信息Industry 工业企业产业行业Innovation 创新Initial 最初的开始的Insert 插入嵌入添Input 输入Insight 洞察顿悟Inside 内部的里面的Install 安装Inspector 检查视察Instrument 仪器Instance 实例Integrate 积分的集成使完成使结合Integer 整数Interactive 互动的交互的Integrity 完整的Interface 接口界面Interconnect 互联器Internet 因特网Internal 内部的IPC(industry process control)工业过程控制Interrupt 打断中断Isolate 隔离Island 孤岛岛屿Item 项目条款ISP(In-system programmable)在线编程JTAG(joint test action group) 联合测试行为组Job 工作职业Joint 联合的Jump 跳跃Junctions 结点接点Keep 保持Key 关键钥匙Kind 种类Knowledge 知识Label 标签商标Lattice 晶格点阵Landscape 横向Layer 层Latch 锁存器锁扣LCD(liquid crystal display) 液晶显示器Launch 发射投掷出版LED(light emitting diode) 发光二级管Layout 布置布局Legacy 老化遗留下Learn 学习学会认知Length 长度Left 左边向左Less 较少的Legend 图例图注Library 库图书馆Lens 镜Line 线条线路Level 水平Link 链接连接License 注册Linear 线性的直线的一次的Liquid 液体流体不稳的Live 激活Localize 本地局部本地化定位Locate 把···设置在位置场所Lock 锁定Log 记录Logarithmic 对数的Logic 逻辑逻辑学Logical 逻辑的合理的Login 登录Lookup 查找查阅Loop 循环环状物Low 低的矮的Lot 地段许多Laboratory 实验室LPM(library of parameter modules) 参数化模块库Language 语言用语术语Machine 机器机械Multivibrator 多谐振荡器Maker 制造者Magnitude 幅值强度量值Manage 管理操纵Male 阳的Manual 手册手动的Manager 管理者经理主任Map 图Manufacture 制造制作加工Match 匹配比赛Mask 表面掩膜屏蔽Matrix 矩阵混合物Material 材料物质Maximum 最大值最大量Maximize 增加扩大Measure 测量Meal 粉状物膳食Medium 中间的媒介Mechanical 机械的Membership 会员资格Mega 许多非常强大Memory 存储器内存Menu 菜单Merge 合并Message 信息Meter 米(长度单位)Metric 公制的Microsoft 微软Millimeter 毫米Minimum 最小值Miscellaneous 混合杂项多样Miser 钻探机Miss 损失差错遗漏Miter 斜接斜角Mix 混合结合杂交Mode 形状方式风格Model 模型模特型号Modify 更改修饰Module 模块组件单元Moire 网纹纹波龟纹Mold 模块模型Monitor 监控Monostable 单稳状态Moor 固定系住Mount 安装Move 移动Mult 多种多元多路Magnify 放大Name 名称Nano 十亿分之一纳Navigator 领航导航Neck 领口瓶颈Negative 负的Net 网络Netlable 网络标号Netlist 网络表New 新的Next 下一步再Nexus 关系Node 结点波峰Noise 噪音None 忽略一个也没Normal 正常的常规的Number 数字号码数量Object 物体目标Octagon 八边形Octal 八进制Octave 八行八度八位ODBC(ovject database connectivity) 开放数据库互联Ohm 欧姆(电阻单位)OLE DB(object lin king and embedding databse) 目标链接及嵌入式数据库Online 在线Opcode 运算码Openbus 开放总线公共总线Open 开放的公开的Operate 工作运转营业Operand 操作数运算域Optimizer 优化程序优化器Operator 运算符Orange 橙子桔子Option 选择选项Orientation 取向Order 顺序Original 原本的最初的Origin 起源原点Outline 外形略述概括Orthogonal 直角的正交的Outside 外部的外观Output 输出Overlay 覆盖层Overall 全部的Owner 物主所有者Overshoot 过冲Package 封装包装Pad 焊盘基座垫料Page 页码翻阅Pair 成对成双Palette 调色盘选盘控制板Panel 面板画板嵌镶板Parallel 并行并联Parameter 参数系数因数Parent 父系Parsing 部析Part 部件Passive 无源的被动的Paste 助焊贴敷铜Path 路径轨迹PCBPeak 峰值Peripheral 周边的外围的Permission 同意Persistent 坚持不懈固执的Physical 物理的Pickbox 点选框取景框Pickup 拾取收集Pin 引脚管脚Place 放置Placement 布局Plane 平板平面飞机Plugin 插件栓Point 点Plus 十字记号加号Polygon 多边形多角形Pole 极极地Popup 弹出Polyline 折线Portable 可移植的移动的Port 端口Position 位置Portrait 竖向纵向Postpone 延时搁置Positive 正的Power 电源功率Pour 倾泻倒灌Preference 偏好优先Predefined 预先定义Preliminary 预备的初步语言的Prefix 前缀字首Preserve 保护保藏维护Prepreg 预浸料半固化品Preview 预览预习排练Preset 置数Primary 主要的Previous 以前的早先的Print 打印Primitive 原始的纯朴的Priority 优先级优先权Printout 打印输出Process 进程步骤Probe 探测调查Profile 外形轮廓部面Processor 处理器加工者Program 程序设计Programmable 可编程的Project 工程项目Proper 适当的恰当的Promote 促进创办Provider 提供者供应商Property 性质特性Pull 拉牵拖PSD(programmable system device) 可编程的系统部件Pulse 脉冲跳动Pullback 障碍阻扰拉回Push 推挤推进拓展Quality 质量特性Query 疑问质问问号Quiet 静态的安静的Radix 根基数RAMRange 级别排行类别Raster 光栅屏面Ray 射线光线闪现Rebuild 重建重构Recent 最近的Record 记录经历Rectangle 矩形长方形Rectangular 矩形的成直角的Red 红色的Reference 参考基准Reflect 反射Region 区域地带Register 寄存器Remove 删除移除Repeat 重复Report 报告Require 需要需求Reserve 储备保存Reset 复位置零Reshape 改造矫形变形Resistance 电阻值Resistor 店主Resource 资源Restore 恢复还原返回Restrict 限制约束Result 结果导致Retrieve 取回恢复Revision 修订本校正版Right 右的右方Ring 铃声环形物Rise 上升起立增强ROMRoom 房间空间位置Root 根根源本质Rotation 旋转自转Round圆的Routing 走线布线Row 成形排列Rule 规则Run 运转流行的趋势Server 服务服务器Same 相同的同样的Sans 没有无Save 保存Scalar 标量数量Scale 刻度调节Schematic 图表示意图Scope 范围域Score 成绩计分Script 脚本Scroll 卷动Search 搜索Secondary 次要的从属的Section 部分片断Seed 原因种子Select 挑选选拔Separate 分离区别标识Sequential 有顺序的相继的Serial 串行的系列的序列的Serif 细体字Series 串联连贯成套Session 学期期间Service 服务检修劳务Shader 材质Set 设置置位Shadow 阴影着色Shape 造型形状Share 共享Sheet 图纸方块Shelve 搁置暂缓考虑Shift 移动变换Shortcut 快捷方式Show 显示展示Signal 信号Sign 签署有符号的征兆标志Silent 沉默的Silkscreen 丝印层Similar 相似的类似的Simple 简单的朴实的Simulation 仿真Sitemap 网站地图网站导航Situs 地点位置Silce 切片薄片Slider 滑块滑动Slot 槽Small 小的细的微的Smart 智慧灵气Snap 跳转突然折断Snippet 片断摘录Software 软件Solder 焊接Solid 实心的固体的坚固的Sort 分类Source 电源根源Space 间隔间隙Speaker 扬声器Special 特殊的Specification 说明书明细表Specify 具体指定详细指明列入清单Speed 速度Split 分离Spreadsheet 电子表格试算表Square 方形正直的Stack 堆积层叠Standalone 单板机Standard 标准规范Standoff 支架平淡Start 起始Starve 不足饥饿State 状态形势州Static 静止的Station 平台地位Status 地位资格身份Step 步进踏步步骤Stimulus 激励促进刺激Stop 停止Storage 储存器Strategy 策略方案战略String 字符串串条弦Structure 构成结构组织Style 风格文体作风Subversion 颠覆Summary 摘要概括总结Support 支持Suppress 压制抑制阻止Surface 表面Suspend 暂停挂起终止Swap 交换Sweep 扫描环视Switch 开关Symbol 符号Synchronous 同步的Syntax 语法Synthesis 综合合成System 系统Table 表格True 真实Target 目标对象指标Tail 末尾尾部Technology 技术工艺Teardrop 泪滴Template 样板Temperature 温度气温Terminal 极限的末端的端子Tenting 掩盖遮掩Terminator 终端负载Terminate 终结终止Text 文本正本Test 测试Themselves 他们自己TFT 触摸屏显示器Thruhole 通孔Thermal 热的热量的Time 时间Tile 铺排Timer 定时器Timebase 时基Toggle 切换开关双稳Timing 时序定时Tool 工具Tolerance 公差容限容差Top 顶部Toolbar 工具栏工具条Total 总体的合计为Topic 题目Track 轨迹Touchscreen 触摸屏Train 培训Trail 拖Transfer 传递Trance 恍惚Transistor 三极管晶体管Transient 暂态瞬态Transparency 透明度Translate 转变翻译Triangle 三角Transport 传输Trigonometry 三角法Trigger 触发器启动引起Tube 真空管电子管试管Tune 调谐曲调协调Tutorial 指导导师Type 类型Unassign 未定义Uncouple 解耦松开Undershoot 下冲负尖峰Undo 取消还原Uniform 相同的一致的单调的Unique 独特的唯一的Unit 单位Universal 普遍的全体的宇宙的Unspecified 不规定不确定Up 向上Update 更新Usage 用法习惯处理Utility 实用的通用的Use 实用V alid 有效的确实的合法的V alidate 使生效V alidation 确认验证V alue 数值价值价格评价V ariant 变化派生V ector 矢量向量V endor 供应商卖主V ersion 版本翻译V ertical 垂直纵向V ertex 顶点制高点极点V ery 很非常甚至VHDLVia 经由过孔Victim 被干扰受害者Video 视频录像View 查看Violation 违犯冲突Virtual 实质上的虚拟的Visible 可视的V oltage 电压Wait 等待延缓Walkaround 环绕步行栈桥Warn 警告提醒预告Wave 波动起伏挥动Waveform 波形图Where 地点在哪里Wide 宽的广泛的Window 窗口Width 宽度幅度带宽Wizard 向导精灵Wire 导线Workspace 工作区工作空间Worksheet 工作表单WOSA(windows open services architecture) 开放服务结构Worst 最差的最坏的Zero 零Zone 地段区域Zoom 缩放陡升。

DSP控制AD9959实现快速跳频的接口设计

DSP控制AD9959实现快速跳频的接口设计【摘要】本文介绍了直接数字合成(Direct Digital Synthesic缩写DDS)技术的工作原理及特点,并给出了DSP控制DDS芯片AD9959实现快速跳频的接口设计方案。

【关键词】跳频;DDS;AD9959;SPI串行通信1.引言跳频通信是扩频通信的一种主要形式。

由于其具有抗干扰、抗截获的能力,并能做到频谱资源共享,在当前军事抗干扰通信系统中被广泛应用。

跳频通信系统的一项重要参数是频率的跳变速度。

它在很多程度上决定了跳频通信系统抗跟踪式干扰的能力,这一点在电子对抗中尤为重要。

因此,快速跳频频率合成器的设计就成为跳频通信的关键之一。

直接数字合成(DDS)是近年来迅速发展起来的一种新的频率合成方法。

这种方法简单可靠、控制方便,且具有很高的频率分辨率和转换速度,非常适合快速跳频通信的要求。

本文将介绍DDS的工作原理,并给出基于DDS的跳频频率合成器的设计。

2.DDS的结构及工作原理直接数字频率合成是采用数字化技术,通过控制和位的变化速度,直接产生各种不同频率信号的一种频率合成方法。

DDS的结构原理框图如图1所示,它由相位累加器、波型存储器、数模转换器、低通滤波器和参考时钟五部分组成。

参考时钟fc由一个稳定的晶体振荡器产生,用它来同步整个合成器的各个组成部分。

在参考时钟的控制下,相位累加器对频率控制字K进行线性累加,得到的相位码对波型存储器寻址,使之输出相应的幅度码,经过数模转换器得到相应的阶梯波,最后经低通滤波器对阶梯波进行平滑处理,得到所需频率的波形。

3.DDS的特点及跳频能力新一代的直接数字频率合成器采用全数字的方式实现频率合成,与传统的频率合成技术相比,具有以下特点:(1)频率转换快。

直接数字频率合成是一个开环系统,无任何反馈环节,其频率转换时间主要由频率控制字状态改变所需的时间及各电路的延时时间所决定,转换时间很短;(2)频率分辨率高、频点数多。

AD9959中文资料

AD9959中⽂资料4 Channel 500MSPS DDS with 10-bit DACsPreliminary Technical DataAD9959Rev. PrBInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700/doc/5164787af242336c1eb95e50.html Fax: 781.326.8703? 2004 Analog Devices, Inc. All rights reserved.FEATURESFour synchronized DDS channels @500 MSPS Independent frequency / phase / amplitude control between all channels Matched latencies for Freq, Phase, and Amplitude changes Excellent channel to channel isolation Frequency sweeping capabilityUp to 16 levels of modulation (pin selectable)Individually programmable DAC full scale currents Four integrated 10-bit D/A converters(DACs) 32-bit frequency tuning resolution 14-bit phase offset resolution10-bit output amplitude scaling resolutionSerial I/O Port(SPI) with enhanced data throughputSoftware/Hardware controlled power-downDual supply operation (1.8 V DDS core / 3.3 V serial I/O) Built-in synchronization for multiple devicesSelectable REF_CLK multipier(PLL) 4x to 20x (bypassable) Selectable REF_CLK crystal operation 56 pin LFCSP package APPLICATIONSAgile L.O. frequency synthesis Phased array radar / sonar InstrumentationSynchronized clocking RF source for AOTFFUNCTIONAL BLOCK DIAGRAMCLK_MODE_SELSYNC_IN S 0S 3S 2S 1Figure 1 AD9959 Block DiagramAD9959Preliminary Technical DataRev. PrB | Page 2 of 9AD9959—SPECIFICATIONSTable 1. Unless otherwise noted, AVDD, DVDD = 1.8 V ± 5%, DVDD_I/O = 3.3 V ± 5%, R SET = 1.96 k?, External ReferenceClock Frequency = 500 MSPS (REF_CLK multiplier bypassed)ParameterMin TypMaxUnitsTest Conditions/Comments REF CLOCK INPUT CHARACTERISTICSREF_CLK inputs must be ACcoupled due to internal biasingFrequency RangeREF_CLK Multiplier bypassed0 500 MHzREF_CLK Multiplier enabled at 4x(min) 25 125 MHzREF_CLK Multiplier enabled at 20x(max)5 25 MHz Internal VCO range w/ REF_CLK multiplier enabled 100 500 MHz Crystal REF_CLK source mode 20 30 MHz Input Power Sensitivity -15 3 dBm External 50 ohm terminationInput voltage level 400 mV Input Capacitance 3 pF Input Impedance1500 ohms Duty Cycle w/ REF_CLK Multiplier bypassed 50 %Duty Cycle w/ REF_CLK Multiplier enabled 35 65 %CLK Mode Select logic 1 Voltage 1.25 V Not a 3.3V digital input CLK Mode Select logic 0 Voltage0.6VNot a 3.3V digital input DAC OUTPUT CHARACTERISTICSMust be referenced to AVDDResolution10 Bits Full Scale Ouput Current 10 mA Gain Error -10 10 %FS Output Offset0.6 uA Differential Nonlinearity -0.5 0.5 LSB Integral Nonlinearity -1 1 LSB Output Capactiance 5 pF Voltage Compliance RangeAVDD– 0.50 AVDD+ 0.50 VChannel to Channel Isolation60 dB Channel to Channel amplitude matching error2 %WIDEBAND SFDRWideband SFDR defined as DC toNyquist1-20 MHz Analog Out-65 dBc 20-60 MHz Analog Out -62 dBc 60-100 MHz Analog Out -59 dBc 100-150 MHz Analog Out -56 dBc 150-200 MHz Analog Out-54dBcNARROWBAND SFDR1.1 MHz Analog Out (+/- 10kHz) -90 dBc 1.1 MHz Analog Out (+/- 50kHz) -88 dBc 1.1 MHz Analog Out (+/- 250kHz) -86 dBc 1.1 MHz Analog Out (+/- 1MHz) -85 dBc15.1 MHz Analog Out (+/- 10kHz) -90 dBc 15.1 MHz Analog Out (+/- 50kHz) -87 dBc 15.1 MHz Analog Out (+/- 250kHz) -85 dBc 15.1 MHz Analog Out (+/- 1MHz) -83 dBc40.1 MHz Analog Out (+/- 10kHz) -90 dBc 40.1 MHz Analog Out (+/- 50kHz) -87 dBc 40.1 MHz Analog Out (+/- 250kHz) -84 dBc 40.1 MHz Analog Out (+/- 1MHz)-82dBcPreliminary Technical DataAD9959Rev. PrB | Page 3 of 9ParameterMinTypMax Units Test Conditions/Comments75.1 MHz Analog Out (+/- 10kHz) -87 dBc 75.1 MHz Analog Out (+/- 50kHz) -85 dBc 75.1 MHz Analog Out (+/- 250kHz) -83 dBc 75.1 MHz Analog Out (+/- 1MHz) -82 dBc100.1 MHz Analog Out (+/- 10kHz) -87 dBc 100.1 MHz Analog Out (+/- 50kHz) -85 dBc 100.1 MHz Analog Out (+/- 250kHz) -83 dBc 100.1 MHz Analog Out (+/- 1MHz) -81 dBc200.1 MHz Analog Out (+/- 10kHz) -87 dBc 200.1 MHz Analog Out (+/- 50kHz) -85 dBc 200.1 MHz Analog Out (+/- 250kHz) -83 dBc 200.1 MHz Analog Out (+/- 1MHz)-81dBcPHASE NOISE CHARACTERISTICS**************************(Aout)@1kHzoffsetTBDdBc/Hz@10kHzoffsetTBDdBc/Hz@100kHzoffsetTBD dBc/ Hz @1MHz offset TBD dBc/ Hz**************************(Aout)@1kHzoffsetTBDdBc/Hz@10kHzoffsetTBDdBc/Hz@100kHzoffsetTBD dBc/ Hz @1MHz offsetTBD dBc/ Hz***************************(Aout)@1kHzoffsetTBDdBc/Hz@10kHzoffsetTBDdBc/Hz@100kHzoffsetTBD dBc/ Hz @1MHz offset TBD dBc/ Hz**************************(Aout)w/REFCLKmultiplierenabled4x@1kHzoffsetTBDdBc/Hz@10kHzoffset TBD dBc/ Hz @100kHz offset TBD dBc/ Hz @1MHz offsetTBD dBc/ Hz**************************(Aout)w/REFCLKmultiplierenabled4x@1kHz offset TBD dBc/ Hz @10kHz offset TBD dBc/ Hz @100kHz offset TBD dBc/ Hz @1MHz offsetTBDdBc/*****************************(Aout)w/REFCLKmultiplierenabled4x@1kHz offset TBD dBc/ Hz @10kHz offset TBD dBc/ Hz @100kHz offset TBD dBc/ Hz @1MHz offset TBD dBc/ Hz SERIAL PORT TIMING CHARACTERISTICSMaximum Frequency200MHzMinimum Clock Pulsewidth Low (t PWL ) TBD ns Minimum Clock Pulsewidth High (t PWH ) TBD nsAD9959Preliminary Technical DataRev. PrB | Page 4 of 9Maximum Clock Rise/Fall TimeTBDnsMinimum Data Setup Time (t DS ) TBD nsMinimum Data Hold TimeTBDnsMISC TIMING CHARACTERISTICSMaster_Reset minimum Pulsewidth TBD Sync CLKI/O_Update minimum Pulsewidth1 Sync CLKMinimum setup time (IO_Update to Sync_CLK) TBD ns Rising edge to rising edge Minimum hold time (IO_Update to Sync_CLK)ns Rising edge to rising edgeMinimum setup time (Profile inputs to Sync_CLK)TBD ns Minimum hold time (Profile inputs to Sync_CLK)nsDATA LATENCY (PIPE LINE DELAY)Pipeline delays for Freq, Phase,Amp changes are programmable to match one another.Matched pipe line of Freq, Phase, Amplitude TBD Sys Clks matched Frequency word to DAC output TBD Sys Clks unmatched Phase Offset word to DAC output TBD Sys Clks unmatched Amplitude word to DAC outputTBDSys ClksunmatchedCMOS LOGIC INPUTSV IH 2.2 V V IL0.6 V Logic 1 Current 3 12 uA Logic 0 Current -12 uA Input Capacitance2pFCMOS LOGIC OUTPUTS (1 mA Load)V OH 2.8 VV OL0.4 VPOWER SUPPLYTotal Power Dissipation- all channels ON, single-tone modeTBDmWMaximum Power Dissipation- all channels, freq accumulatoroutput multiplier ONTBDIavdd – All Channels ON, Single tone modeTBD mA Iavdd – All Ch(s) ON, Freq accum, and output multiplier ON TBD mA Idvdd – All Ch(s) ON, Single tone mode TBD mAIdvdd – All Ch(s) ON, Freq accum, and output multiplier ONTBDmAdvdd_/O TBD mAPower down Mode TBD mAPreliminary Technical DataAD9959Rev. PrB | Page 5 of 9ABSOLUTE MAXIMUM RATINGSTable 2.Parameter Rating Maximum Junction Temperature 150°C DVDD_I/O (Pin 49) 4 V AVDD, DVDD 2 V Digital Input Voltage (DVDD_I/O = 3.3 V) –0.7 V to +4V Digital Output Current 5 mA Storage Temperature –65°C to +150°C Operating Temperature –40°C to +105°C Lead Temperature (10 sec Soldering) 300°C θJA 21°C/W θJCStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.TERMINATE OUTPUTS INTO AVDD. DO NOT EXCEED OUTPUT VOLTAGE COMPLIANCE.AVOID OVERDRIVING DIGITAL INPUTS.FORWARD BIASING DIODES MAY COUPLE DIGITAL NOISE ON POWER PINS.REF_CLK INPUTS ARE INTERNALLY BIASED AND NEED TO BE AC-COUPLED.OSC INPUTS ARE DCCOUPLEDCMOS DIGITAL INPUTSDAC OUPUTSOSC / REF_CLKINPUTSFigure 1 Equivalent input and output circuitsAD9959Preliminary Technical DataRev. PrB | Page 6 of 9PRODUCT OVERVIEWThe AD9959 consists of four independently programmable DDS channels. The AD9959 features independent frequency, phase, and amplitude control of each channel; this allows for the correction of imbalances due to analog processing such as filtering, amplification, or PCB layout related mismatches. The AD9959 supports frequency sweeping for radar andinstrumentation applications. Since all four channels share a common system clock, they are inherently synchronized. If more than four channels are required, synchronizing multiple AD9959s is a simple task.The AD9959 uses advanced DDS technology which provides low power dissipation with high performance. The device incorporates four integrated high speed 10-bit DACs withexcellent wideband and narrowband SFDR. Each DDS has a 32-bit frequency tuning word, 14-bits of phase offset, and a 10-bit output scale multiplier.Each DAC has it own programmable reference to enable a different full scale current for each channel.Each DDS acts as a high resolution frequency divider with the REF_ CLK as the input and the DAC providing the output. The REF_CLK input source is common to all DDS channels, and can be driven directly, or used in combination with an integrated REF_CLKmultiplier (using a PLL) up to a maximum of 500 MSPS. The REF_ CLK multiplication factor is programmable from 4 to 20, in integer steps. The REF_CLK input features an oscillator which supports either a crystal as a source, or may be bypassed. The crystal frequency must be between 20MHz and 30MHz. The crystal can be used with or without the REF_CLK multiplier. The DAC outputs are supply referenced and must be terminated into AVDD by a resistor, or an AVDD center-tapped transformer. The AD9959 comes in a space-saving 56-lead LFCSP package. The DDS core (AVDD and DVDD pins) must be powered by a 1.8V supply. The digital I/O interface (SPI) operates at 3.3V and requires that the pin labeled “DVDD_I/O”(pin 49) be connected to 3.3V .The AD9959 operates over the industrial temperature range of -40C to +85Preliminary Technical DataRev. PrB | Page 7 of 9PIN CONFIGURATIOND V D DD G N D S D I O _1S D I O _2S D I O _3D G N DD V D DI /O _U P D A T ES Y N C _C L KP 3D V D D _ I /OC SS C L KS D I O _0Notes :1) The exposed EPAD on bottom side of package is an electrical connection and must be soldered to ground.2) Pin 49 is DVDD_IO and is tied to 3.3V.AD9959 Preliminary Technical DataRev. PrB | Page 8 of 9Preliminary Technical DataAD9959Rev. PrB | Page 9 of 9ESD CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performancedegradation or loss of functionality.。

AD9954芯片资料中文版

AD9954- Direct Digital Synthesizer400 MSPS 14-Bit, 1.8 V CMOS功能: (2)应用 (2)概述 (2)AD9954电气特性 (3)最大操作范围 (4)Table 2. (4)管脚定义 (4)管脚功能描述 (4)典型的性能特性 (6)原理 (7)器件块 (7)控制寄存器位描述 (10)Other Register Descriptions 其他寄存器描述 (14)Programming AD9954 Features-- AD9954编程特性 (18)SERIAL PORT OPERATION串口操作 (19)INSTRUCTION BYTE指令字节 (20)SERIAL INTERFACE PORT PIN DESCRIPTION串行接口管脚描述 (20)MSB/LSB TRANSFERS (20)RAM I/O VIA SERIAL PORT (21)Power-Down Functions of the AD9954 AD9954省电功能 (21)功能:400MSPS 内部时钟 集成14位DAC可编程相位/幅度抖动 32位控制字相位噪声小于等于-120dbc/Hz@1kHz(DAC 输出)出色的动态性能>80db SFDR@160MHz (偏离100KHz ) 串行I/O 口控制 超高速模拟比较器 自动线性和非线性扫频能力 4种频率/相位偏移坡面 1.8v 电压供电软件或者硬件控制休眠内部集成1024字节*32位RAM 大多数输入口支持5v 电平PLL REFCLK 乘法器(4倍-20倍) 单晶振驱动内部时钟 相位调制能力 多芯片同步 应用敏捷LO 频率输出 可编程的时钟发生器雷达和扫频系统中的FM 啁啾源自动雷达测试和测量设备 声光设备驱动概述AD9954具有一个14位DAC 最高达400 MSPS 的DDS 。

AD9954使用了先进的DDS 技术,内部集成高速,高性能的DAC 形成数字可编程,完整的高频合成器,能产生高达200MHz 模拟正弦波的能力。

AD9959数据手册部分内容中文翻译

精心整理AD9959数据手册(部分)GENERALDESCRIPTION概述TheAD9959consistsoffourdirectdigitalsynthesizer(DDS)coresthatprovideindependentfrequency ,phase,andamplitudecontroloneachchannel.Thisflexibilitycanbeusedtocorrectimbalancesbetweensig nalsduetoanalogprocessing,suchasfiltering,amplification,orPCBlayout-relatedmismatches.Becauseal lchannelsshareacommonsystemclock,theyareinherentlysynchronized.Synchronizationofmultipledevi cesissupported.TheAD9959canperformuptoa16-levelmodulationoffrequency,phase,oramplitude(FS或PCB 同步。

SPI 脚(DAC具10VDDce lyorusedincombinationwithanintegratedREFCLKmultiplier(PLL)uptoamaximumof500MSPS.The PLLmultiplicationfactorisprogrammablefrom4to20,inintegersteps.TheREFCLKinputalsofeaturesa noscillatorcircuittosupportanexternalcrystalastheREFCLKsource.Thecrystalmustbebetween20MH zand30MHz.ThecrystalcanbeusedincombinationwiththeREFCLKmultiplier.DAC的输出供给参考必须通过电阻接到A VDD或接到A VDD中心抽头变压器。

AD9 中文教程

2.1 3D 显示......................................................................................................................... 18 2.1.1 设计时的 3D 显示状态 ..................................................................................... 18 2.1.2 3D 显示设置 .................................................................................................... 18

3. 设计规则检查及报告信息 ....................................................................................................... 27

3.1 设计规则检查设置 ........................................................................................................ 27 3.1.1 如何检查设计规则 ........................................................................................... 27 3.1.2 规则应用.......................................................................................................... 28 布线规则....................................................................................................................... 28 制造规则....................................................................................................................... 28 High Speed rules 高速布线规则................................................................................... 28 布局规则....................................................................................................................... 29

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD9959数据手册(部分)GENERAL DESCRIPTION概述The AD9959 consists of four direct digital synthesizer (DDS) cores that provide independent frequency, phase, and amplitude control on each channel. This flexibility can be used to correct imbalances between signals due to analog processing, such as filtering, amplification, or PCB layout-related mismatches. Because all channels share a common system clock, they are inherently synchronized. Synchronization of multiple devices is supported. The AD9959 can perform up to a 16-level modulation of frequency, phase, or amplitude (FSK, PSK, ASK). Modulation is performed by applying data to the profile pins. In addition, the AD9959 also supports linear sweep of frequency, phase, or amplitude for applications such as radar and instrumentation.AD9959含有四个直接数字频率合成器(DDS),提供各通道独立的频率、相位和振幅控制。

这种灵活性可以用来纠正信号之间的不平衡,这种不平衡是由于模拟处理,如滤波,放大,或PCB布局相关的不匹配导致。

因为所有通道共用一个系统时钟,因此固有的同步。

也支持多个设备的同步。

AD9959可以执行16级频率、相位、振幅(FSK,PSK,ASK)调制,通过将数据传到配置引脚执行。

此外,AD9959还支持频率、线性扫频、相位或振幅的应用,如雷达和仪表。

The AD9959 serial I/O port offers multiple configurations to provide significant flexibility. The serial I/O port offers an SPI- compatible mode of operation that is virtually identical to the SPI operation found in earlier Analog Devices, Inc., DDS products. Flexibility is provided by four data pins (SDIO_0/SDIO_1/ SDIO_2/SDIO_3) that allow four programmable modes of serial I/O operation.AD9959的串行I/O端口提供了多种配置,提供显著的灵活性。

串行I / O端口提供了一个SPI兼容的操作模式,SPI操作与较早的模拟设备公司DDS产品几乎相同。

灵活性是通过四个数据引脚(sdio_0 / sdio_1 /sdio_2 / sdio_3)允许四可编程串行I/O操作模式来实现的。

The AD9959 uses advanced DDS technology that provides low power dissipation with high performance. The device incorporates four integrated, high speed 10-bit DACs with excellent wideband and narrow-band SFDR. Each channel has a dedicated 32-bit frequency tuning word, 14 bits of phase offset, and a 10-bit output scale multiplier.AD9959采用先进的DDS技术,提供低高性能低功耗。

该器件集成了四个高速10位DAC 具有优良的宽带和窄带SFDR。

每个通道有一个专门的32位频率调谐字,14位相位偏移,和一个10位幅度调节输出。

The DAC outputs are supply referenced and must be terminated into AVDD by a resistor or an AVDD center-tapped transformer. Each DAC has its own programmable reference to enable different full-scale currents for each channel. The DDS acts as a high resolution frequency divider with the REFCLK as the input and the DAC providing the output. The REFCLK input source is common to all channels and can be driven directly or used in combination with an integrated REFCLK multiplier (PLL) up to a maximum of 500 MSPS. The PLL multiplication factor is programmable from 4 to 20, in integer steps. The REFCLK input also features an oscillator circuit to support an external crystal as the REFCLK source. The crystal must be between 20 MHz and 30 MHz. The crystal can be used in combination with the REFCLK multiplier.DAC的输出供给参考必须通过电阻接到AVDD或接到AVDD中心抽头变压器。

每个DAC 有自己的可编程参考,能提供各通道的不同满量程电流。

REFCLK作为输入时,DDS核心作为一个高分辨率分频器,以DAC提供输出。

REFCLK输入源对所有通道是一样的,可直接驱动或用于与一个集成的REFCLK乘法器组合(PLL),最高500 MSPS。

PLL倍增因子可编程,从4到20的整数。

REFCLK输入还可作为一个振荡器电路,支持外部晶振作为参考源。

该晶振必须介于20兆赫和30兆赫。

晶振可用于与REFCLK倍频组合。

The AD9959 comes in a space-saving 56-lead LFCSP package. The DDS core (AVDD and DVDD pins) is powered by a 1.8 V supply. The digital I/O interface (SPI) operates at 3.3 V and requires DVDD_I/O (Pin 49) be connected to 3.3 V. The AD9959 operates over the industrial temperature range of −40°C to +85°C.AD9959使用节省空间的56引脚LFCSP封装。

DDS的核心(AVDD和DVDD引脚)由1.8 V 供电。

数字I / O接口(SPI)的工作在3.3 V,要求dvdd_I/O(引脚49)连接到3.3 V。

AD9959可运行在超过工业温度范围的-40°C到85°C。

ABSOLUTE MAXIMUM RATINGS 绝对最大额定值Table 2. 表2Parameter参数Rating 额定值Maximum Junction Temperature 最大结温150°CDVDD_I/O (Pin 49) 4 VAVDD, DVDD 2 VDigital Input Voltage (DVDD_I/O = 3.3 V)数字输入电压−0.7 V to +4 VDigital Output Current数字输出电流 5 mAStorage Temperature Range 存储温度–65°C to +150°COperating Temperature Range操作温度–40°C to +85°CLead Temperature (10 sec Soldering) 焊接温度300°CθJA 21°C/WθJC 2°C/WTHEORY OF OPERATION 操作原理DDS CORE DDS核心The AD9959 has four DDS cores, each consisting of a 32-bit phase accumulator and phase-to-amplitude converter. Together, these digital blocks generate a digital sine wave when the phase accumulator is clocked and the phase increment value (frequency tuning word) is greater than 0. The phase-to-amplitude converter simultaneously translates phase information to amplitude information by a cos(θ) operation. The output frequency (fOUT) of each DDS channel is a function of the rollover rate of each phase accumulator. The exact relationship is given in the following equation:AD9959有四个DDS内核,每个含32相位累加器和相位-幅度转换器。