半导体物理基础 第六章 MOS

半导体器件之MOS

P型衬底

栅电压=阈值电压 表面空间电荷区 厚度达到最大值

12

MOS电容 空间电荷区厚度:n型衬底情形

阈值反型点条件: 表面势=费米势的2倍,表面处的空穴浓度=体内的电子浓度,栅电压=阈值电压

表面势

表面空间电荷 区厚度

n型衬底

13

MOS电容 空间电荷区厚度:与掺杂浓度的关系

实际器件 参数区间

14

MOS电容 表面反型层电子浓度与表面势的关系

零栅压下半导体的 表面势

接触之后能带图的变化:

1)MOS成为统一系统, 0栅压下热平衡状态有统一的EF。

2)SiO2的能带倾斜:

3)半导体一侧能带弯曲:

18

11.1 MOS电容

功函数差:计算公式

内建电势差:

功函数差

Vbi Vox0 S 0 ms

ms

m

' (

'

Eg 2e

加负栅压,堆积层电荷能够跟得上栅 压的变化,相当于栅介质平板电容

C' (acc)

Cox

ox

tox

平带

本征

36

11.2 C-V特性

平带状态

所加负栅压正好等于平带电压VFB,使 半导体表面能带无弯曲

C'FB

tox

ox ox kT

tox e

s

eN a

平带 本征

37

11.2 C-V特性

表面势 s 半导体表面电势与 体内电势之差

费米势

半导体体内费米能 级与禁带中心能级 之差的电势表示

P型衬底

表面空间电 荷区厚度

采用单边突变结的 耗尽层近似

耗尽层形成:正栅压,P衬表面多子空穴耗尽,留下固定不动的Na-,由半导体浓度

MOS概述及应用PPT课件

*

(5)、控制器中的MOS经常“坏掉”,到底是什么原因? 1. 控制器温度过高,将功率管“烧”坏,打开控制器可以看到功率管上面的塑封体被烧化了.这主要是控制器长期在大电流下运行造成的,可能是MOS与散热片上的螺丝未拧紧导致散热不良。连接MOS的螺丝和塑料粒子也容易变形烧坏,可以在塑料粒子和螺丝之间再垫上金属平垫片和弹簧垫片,保证塑料粒子被压紧,同时散热性能也会好点。 2.另外,控制器软件和硬件保护做的又不到位,还有驱动电路与功率管不匹配都会导致这种问题。建议客户将样品寄给我们,以便匹配; 3. 电机本身设计的不好。这点从相对地波形容易看出。如果相对地波形不是梯形波,而是有明显的电压突变现象,就会使dV/dt过大,也会导致MOS管易坏,这点建议电机厂修改电机。

*

垂直导电MOSFET

根据栅氧槽形状,可分成VMOS、UMOS、TMOS、DMOS等

*

1001M导电结构

1001纵向剖面图

*

MOS主要应用范围

高压MOS: 1、 PC电源:2N60、4N60、10N60 2、节能灯:830(5A500V)、840(8A500V)、 3、 电子镇流器:830、840、5N50; 4、 充电器、笔记本适配器:1N60、2N60、4N60、5N60、6N60、7N60、8N60、10N60; 低压MOS: 5、 电动工具:60N06、; 6、 电动车: 1001、1808 ; 7、 锂电池保护:8205; 8、 UPS:1001、1707;

MOS动态参数

*

MOS参数中英文对照表

*

MOS动态参数

gfs---正向跨导 。表示栅源电压UGS — 对漏极电流ID的控制能力,即漏极电流ID变化量与栅源电压UGS变化量的比值. dv/dt---电压上升率(控制器电路参数) 由于MOSFET的封装电感和线路的杂散电感的存在,在MOSFET反向恢复电流Irr突然关断时,MOSFET上的电压Vds会出现振铃,导致Vds超过MOSFET的BVDSS从而发生雪崩现象。 若MOSFET的米勒电容Cgd 偏大的同时且VTH又偏小,则MOSFET在关闭的瞬间,将在GS端感应出电压(与dv/dt、Cgd、Cgs、RG相关),若该电压大于VTH,则将导致Cdv/dt感应导通。

mos原理

mos原理

MOS原理:现代电子技术的基础

MOS(Metal-Oxide-Semiconductor)是一种半导体器件,是现代电子技术的基础之一。

MOS原理是指利用金属-氧化物-半导体结构来实现电子器件的工作原理。

MOS器件具有低功耗、高速度、高可靠性等优点,被广泛应用于集成电路、微处理器、存储器等领域。

MOS原理的基本结构是由金属、氧化物和半导体三部分组成。

金属是电极,氧化物是绝缘层,半导体是导电层。

当金属电极施加电压时,电子会在半导体中形成电子云,这个电子云会在氧化物中形成电场,从而控制半导体中的电子流动。

这种控制电子流动的方式被称为场效应,因此MOS器件也被称为场效应晶体管。

MOS器件的优点之一是低功耗。

由于MOS器件的绝缘层是氧化物,所以电流只能通过金属电极和半导体之间的电场控制,而不能通过氧化物。

这种结构使得MOS器件的电流非常小,因此功耗也很低。

MOS器件的另一个优点是高速度。

由于MOS器件的电流非常小,所以响应速度也非常快。

此外,MOS器件的结构非常简单,制造工艺也比较成熟,因此可以实现高密度集成,从而提高器件的速度。

MOS器件的可靠性也非常高。

由于MOS器件的绝缘层是氧化物,所以不容易受到外界的干扰。

此外,MOS器件的结构非常简单,没有机械部件,因此也不容易出现故障。

MOS原理是现代电子技术的基础之一,MOS器件具有低功耗、高速度、高可靠性等优点,被广泛应用于集成电路、微处理器、存储器等领域。

随着科技的不断发展,MOS器件的性能也在不断提高,未来MOS器件将会更加智能化、高效化、可靠化。

半导体基础知识mos管的结构和工作原理

uGS uDS iD

s

gd

uGS uDS iD

s

gd

N

N

N

N

P

P

B

B

•uGS对iD的影响:uGS↑→沟道宽度↑→iD↑

23

(2)特性曲线与电流方程

iD IDO

★

iD 预夹断轨迹uDS=uGS-UGS(th)

IDO 可变

UGS3=2UGS(th)

电阻区 恒流区 UGS2

O

UGS(th) 2UGS(th) uGS O

+4

+5

+4

多余电子

5

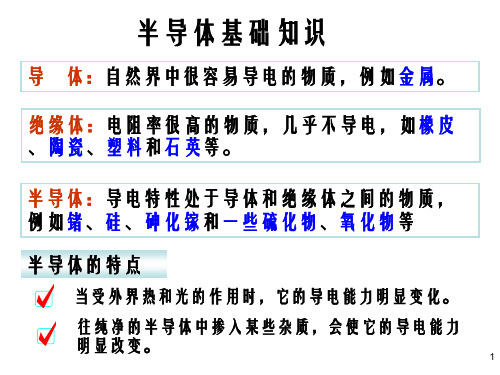

2)P型半导体

在硅或锗晶体(四价)中掺入少量的三价元素硼, 使空穴浓度大大增加。 多数载流子(多子):空穴。取决于掺杂浓度; 少数载流子(少子):电子。取决于温度。

+4

+4

空穴

硼原子

+3

+4

6

归纳

◆

1、杂质半导体中两种载流子浓度不同,分为多 数载流子和少数载流子(简称多子、少子)。

s N沟道

d

B g

s P沟道

B 20

(1)工作原理 通常源极和衬底是连在一起的 ①GS间开路时 此时,漏源间有两个背靠背的PN结, 因此DS间接什么电压,都不会有电 流产生。即此时不存在导电沟道。

②uGS>0,DS短接 此时,栅极接正,衬底接负,衬底中的 多子空穴被排斥到下方,上面形成耗尽 层。且uGS越大,耗尽层越宽。

20℃ 数值后,才有明显的正向电流。

硅:Uon=0.5V;锗:Uon=0.1V

U(BR) IS

0 Uon

正向导通电压U范围:

硅:0.6~0.8V(计算时取0.7V),U=0.7

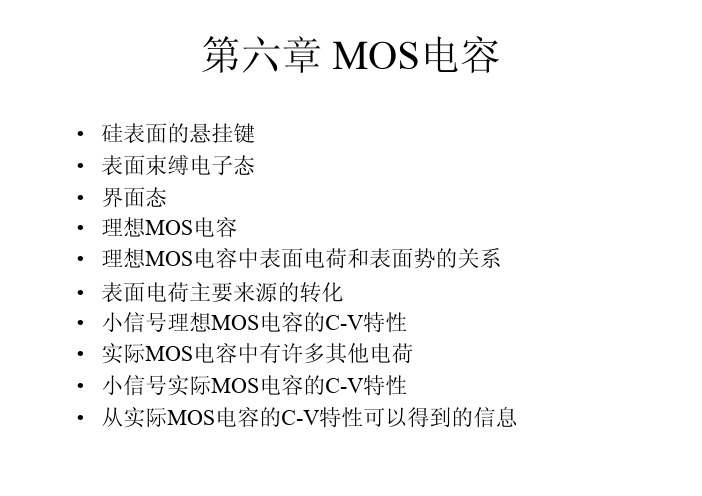

复旦大学(微电子)半导体器件第六章MOSC-V

第六章MOS电容•硅表面的悬挂键•表面束缚电子态•界面态•理想MOS电容•理想MOS电容中表面电荷和表面势的关系•表面电荷主要来源的转化•小信号理想MOS电容的C-V特性•实际MOS电容中有许多其他电荷•小信号实际MOS电容的C-V特性•从实际MOS电容的C-V特性可以得到的信息半导体器件的基本结构-金属/氧化层/半导体结构的电容~电压关系硅片表面的悬挂键•硅单晶体内部一个原子是以共价键形式和周围四个原子结合起来的。

•在表面,硅原子的排列中断,表面的原子就有一部分未成键的电子。

•这种未成键的电子的面密度约1015/cm2。

•这些未成键的电子和体内成键的电子所处的状态不同,是局域束缚电子。

氧化层和硅的界面没有界面态;=?sc1/2exp 1s s q q kT kT ψψ⎫⎤⎪⎛⎞−−⎬⎜⎟⎥⎝⎠⎦⎪⎭小信号理想MOS的C-V特性取决于:测试信号和偏置电压的选择:•低频、稳态;•高频、稳态;•高频、瞬态。

实际MOS电容中有许多其他电荷畸变平移AC B从MOS电容测试可以获得的信息一般可以测试:•可动离子浓度(加偏压、温度测试C-V曲线漂移);•界面态密度(低频稳态和高频稳态C-V曲线);•产生寿命(高频深耗尽到高频稳态的过渡过程);•氧化层厚度(氧化层电容);•衬底的导电类型和掺杂浓度(耗尽区稳态高频C-V);其他影响因素;•二氧化硅中的陷阱、外表面吸附离子、含磷二氧化硅极化、界面杂质、辐射效应…重点内容•表面电荷和表面势的关系。

•小信号MOS电容的三种特性曲线是在什么情况下得到的。

•从MOS电容测试可以得到哪些信息。

•电荷在二氧化硅和金属的界面附近对测试结果没有影响而在半导体表面一侧则影响最大(为什么?)。

半导体物理学第六章解读

ND X D ND NA

1

Q=eND

Xn

2

0e

(

NDNA ND NA

)(VD

V

2 )

♦单边突变结:

XD

2

e

0

1

(VD V NB

)

2

♦势垒区主要在轻掺杂 一边

• 对p+-n结, NB代表ND • 对p-n+结, NB代表NA

xn X D

xp XD

P+-n结

3. 突变结的势垒电容

电势

图6-8

电子势能(能带)

6.1.5p-n载流子的分布 ♦ 当电势零点取x=-xp处,则有: EC (x) EC qV (x)

EV (x) EV qV ( x)

x x p , EC ( x) EC x xn , EC (x) EC qVD

♦势垒区的载流子浓度为:

EC qV ( x ) EF

• 反向偏压下的突变结势垒电容(单位面积):

1

CT A

dQ dV

2(

0eND NA

ND NA )(VD

V

)

2

CT 0

A XD

CT

(VD

1 V )1/ 2

• 几点说明:

① p-n结的势垒电容可以等效为一个平行

板电容器,势垒宽度即两平行极板的距离

② 这里求得的势垒电容, 主要适用于反向 偏置情况

xn

NAXD ND NA

, xp

ND X D ND NA

• 代入上式

VD

q

2 0

( NAND ND NA

)

X

2 D

♦则,平衡p-n结

1

XD

半导体物理学第六章

6.3.2 突变结的势垒电容

1.突变结的电场电势分布

①耗尽层近似下的空间电荷: 突变结+杂质完全电离+耗尽近似的条件下,势垒 区中电离杂质组成空间电荷 • 势垒宽度: XD= Xp +Xn • 势垒区中单位面积的正负电荷总量相等: |Q|=eNAXp =eNDXn

( x) qN A ( x p x 0) ( x) qN D (0 x xn )

势垒区 能带

空间电荷分布

矩形近似

d 2V ( x) , 2 dx 0

②电场: ♦泊松方程: d 2V

dx

♦ 积分一次

d 2V1 qN A ( x p x 0) 2 dx 0

2 2

qN D ( x)

0

(0 x xn )

dV1 qN A ( ) x C1 ( x p x 0) dx 0 dV2 qN D ( x) ( ) x C2 (0 x xn ) dx 0

大注入效应 空间电荷区的复合

单向导电性应用

• 整流二极管 • 检波二极管 • 开关二极管

第6章 pn 结

• 6.1 pn结及其能带图 6.2 pn结电流电压特性 6.3 pn结电容 6.4 pn结击穿 6.5 pn结隧道效应

电容

6.3.1 PN结电容的来源

PN结的两端有等效电容,此电容由两部分组成: 势垒电容CB和扩散电容CD。

突变结

Step Junction

能带

内建电势

电场

电荷

第6章 pn 结

• 6.1 pn结及其能带图 6.2 pn结电流电压特性 6.3 pn结电容 6.4 pn结击穿 6.5 pn结隧道效应

半导体物理第六章PPT课件课件

电子和空穴的扩散方程可进一步变换为下式:

上述两式就是在掺杂和组分均匀的条件下,半导体材 料中过剩载流子浓度随着时间和空间变化规律的方程。

《半导体物理第六章》PPT课件

扩散方程的物理意义: 与时间相关的扩散方程描述过剩载流子浓度随着时间和 空间位置的变化规律。

《半导体物理第六章》PPT课件来自这一节将详细讨论过剩载流子运动的分析方法。

《半导体物理第六章》PPT课件

6.2.1 连续性方程 如下图所示的一个微分体积元,一束一维空穴流在

x处进入微分体积元,又在x+dx处离开微分体积元。 空穴的流量:Fpx+,单位:个/cm2-s,则有下式成立:

《半导体物理第六章》PPT课件

《半导体物理第六章》PPT课件

6.3.1 双极输运方程的推导

利用方程: 扩散方程; 泊松方程;

(泊松方程能建立过剩电子浓度及过剩空穴浓度与内 建电场之间的关系),其表达式为:

其中εS是半导体材料的介电常数。 《半导体物理第六章》PPT课件

扩散方程中的

项不能忽略。

《半导体物理第六章》PPT课件

双级输运方程的推导: 半导体中的电子和空穴是成对产生的,因此电子和空 穴的产生率相等,即:

Eapp:外加电场; Eint:内建电场。

《半导体物理第六章》PPT课件

内建电场倾向于将过剩电子和过剩空穴保 持在同一空间位置,因此这些带负电的过剩电 子和带正电的过剩空穴就会以同一个等效的迁 移率或扩散系数共同进行漂移或扩散运动。 这种现象称为双极扩散或双极输运过程。

《半导体物理第六章》PPT课件

§6.3 双极输运

在第5章中,导出的电子电流密度方程和空穴电流密 度方程中,引起漂移电流的电场指的是外加的电场。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

QS QB qNa xd

2 qNa xd S 2k s 0

(6-5)

和

(6-6)

6.2 理想MOS电容器

代入(6-44)式解出 x

d

Xd

kS 0 kS 0 2VG 1 C0 2 C0 C0 qkS 0 N a

2 0 12

(6-45)

C 2C 1 qN k VG C0 a S 0

6.2 理想MOS电容器

积累区( VG <0)

MOS系统的电容C基本上等于绝缘体电容 C0。当负偏压的数值逐渐减少时,空间电 荷区积累的空穴数随之减少,并且 QS 随 C也就变小。 平带情况( VG =0)

S

的变化也逐渐减慢, C S 变小。总电容

C FB C0

1 k 0 LD 1 k s x0

(6-1)

掌握载流子积累、耗尽和反型和强反型的概念。 正确画出流子积累、耗尽和反型和强反型四种情况的能带图。 导出反型和强反型条件

6.2 理想MOS电容器

6.2 理想MOS电容器

系统单位面积的微分电容

微分电容C与外加偏压 VG 的关系称为MOS系统的电容—电压特性。

dQM C dVG

(6-1)

S =半导体表面的电场

k0 =氧化物的相对介电常数

k S =半导体相对介电常数

xd =空间电荷区在半导体内部的边界亦即空间电荷区宽度。

外加电压 VG 为跨越氧化层的电压

V0和表面势 S 所分摊:

(6-2)

VG V0 S

6.1 理想MOS结构的表面空S结构内的电位分布

(6-22)

dV0 d s 1 dVG C dQM dQM dQM

若令

(6-23)

C0

dQM dV0

(6-24)

dQS dQM CS d S d S

(6-25)

6.2 理想MOS电容器

则

1 1 1 C C0 C S

(6-26)

C0 =绝缘层单位面积上的电容,

6.1 理想MOS结构的表面空间电 荷区

6.1 理想MOS结构的表面空间电荷区

理想MOS结构基于以下假设: (1)在氧化物中或在氧化物和半导体之间的界面上不存在电荷。 (2)金属和半导体之间的功函数差为零,如绘于图6-2b中的情形。 〔由于假设(1)、(2),在无偏压时半导体能带是平直的。〕

(3) SiO 层是良好的绝缘体,能阻挡直流电流流过。因此,即使有外加电压,表面空

(6-46)

归一化MOS电容 C C0 随着外加偏压

VG 的增加而减小

画出了理想系统的电容—电压特性(图6.7)。

6.2 理想MOS电容器

教学要求

掌握理想系统的电容—电压特性,对图6.7作出正确分析。 导出公式(6-45)、(6-46)。

6.3沟道电导与阈值电压

6.3沟道电导与阈值电压

x dm 2k S 0 si qNa 4 k S 0 f qNa

(6-19)

QB qNa xdm

总表面空间电荷

(6-20)

QS QI QB QI qNa xdm

(6-21)

QI为反型层中单位面积下的可动电荷即沟道电荷:

QI qnI x dx

2

间电荷区也处于热平衡状态,这使得整个表面空间电荷区中费米能级为常数。这些 假设在以后将被取消而接近实际的MOS结构。

6.1 理想MOS结构的表面空间电荷区

半导体表面空间电荷区 :

每个极板上的感应电荷与电场之间满足如下关系

QM QS k0 0 0 k S 0 S

式中0=自由空间的电容率

kS 0 kS 0 2VG Xd 1 C0 2 C0 C0 qkS 0 N a

C 2C 1 qN k VG C0 a S 0

2 0 12

(6-28)

在耗尽区

(6-45)

2 12

2 0 k 0 1 V 2 G qNa k S x0

6.1 理想MOS结构的表面空间电荷区

载流子耗尽 单位面积下的总电荷为

QS QB qNa xd

式中 xd 为耗尽层宽度。

2 qNa xd S 2k s 0 x x S 1 x d

(6-5)

(6-6)

2

(6-7)

载流子反型:载流子类型发生变化的现象或者说半导体的导电类型发生变化的现象。

偏压 V 使半导体表面具有表面势,出现表面空间电荷区。 G

空间电荷与电场具有以下关系

QM QS k0 0 0 k S 0 S

(6-1)

6.1 理想MOS结构的表面空间电荷区

小结

载流子积累、耗尽和反型的概念。

载流子积累、耗尽和反型和强反型四种情况的能带图。 体费米势的概念:

MOS电容定义为

C

dQM dVG

(6-22)

绝缘层单位面积电容

导体表面空间电荷区单位面积电容

dQM 0 k 0 C0 dV0 x0

(6-29)

dQS dQM CS d S d S

(6-25)

6.2 理想MOS电容器

小结

归一化电容

C 1 C0 1 C0 C S

C S =半导体表面空间电荷区单位面积电容。

C 1 C0 1 C0 C S

(6-28)

C C0 称为系统的归一化电容。

dQM 0 k 0 C0 dV0 x0

(6-29)

6.2 理想MOS电容器

将电容随偏压的变化分成几个区域,变化大致情况如图6-7所示。

图6-7 P型半导体MOS的C-V特性

G

控制,这正是MOSFET工作的基础。

VTH

QB Si C0

(6-55)

第一项表示在形成强反型时,要用一部分电压去支撑空间电荷 QB ; 第二项表示要用一部分电压为半导体表面提供达到强反型时所需要的表面势 Si 。

6.3沟道电导与阈值电压

小结

二个概念:沟道电导、阈值电压

沟道电导公式

6.1 理想MOS结构的表面空间电荷区

载流子积累、耗尽和反型

载流子积累 紧靠硅表面的多数载流子浓度大于体内热平衡多数载流子浓度时,称为载流子积 累现象。 单位面积下的空间电荷

Qs q [ p ( x) p0 ]dx

0

xd

6.1 理想MOS结构的表面空间电荷区

图6-4 几种偏压情况的能带和电荷分布 (a) VG , (b)小的 VG , (c)大的 VG

xI 0

(6-52)

6.1 理想MOS结构的表面空间电荷区

小结

理想MOS结构基于以下假设: (1)在氧化物中或在氧化物和半导体之间的界面上不存在电荷。 (2)金属和半导体之间的功函数差为零,如绘于图6-2b中的情形。

〔由于假设(1)、(2),在无偏压时半导体能带是平直的。〕

(3) SiO2层是良好的绝缘体,能阻挡直流电流流过。因此,即使有外加电压,表面空 间电荷区也处于热平衡状态,这使得整个表面空间电荷区中费米能级为常数。

一 沟道电导

Z xI g I q n nI x dx L 0

式中n I

(6-51)

x 为沟道中的电子浓度。 xI 为沟道宽度。

xI 0

qnI x dx QI

(6-52)

即为反型层中单位面积下的总的电子电荷 沟道电导为

Z g I n QI L

(6-53)

6.3沟道电导与阈值电压

二 阈值电压 VTH :定义为形成强反型所需要的最小栅电压。

当出现强反型时

QI QB VG Si C0 C0

Q QI C0 VG B Si C0 VG VTH C 0

(6-51) (6-54)

沟道电荷受到偏压 V 阈值电压:

2 0 k 0 1 V 2 G qNa k S x0

2

12

(6-46)

归一化电容 C C0 随着外加偏压 VG 的增加而减小. 反型区( VG >0)

dQI dQB dQS Cs d S d S d S

(6-47)

6.2 理想MOS电容器

小结

gI

Z n QI L

(6-53)

阈值电压公式

QB QI C0 VG C Si C0 VG VTH 0

(6-54)

6.3沟道电导与阈值电压

教学要求

掌握概念:沟道电导、阈值电压

导出沟道电导公式(6-53) 导出阈值电压公式(6-54) 说明阈值电压的物理意义。

SiO2

+

+

+

界面陷阱电荷 Qit

Si

图 6-13 热氧化硅形成的 Si SiO 2 系统中 的各类电荷

6.4 实际MOS的电容—电压特性

界面陷阱电荷(interface trapped charge)

Qit

硅(100)面, Qit 约 1010 cm 2 , 硅(111)面, Qit 约 1011 cm 2 。

(6-57) 的函数,与

VG VG1 起着有效电压的作用。实际系统的电容C作为 G VG1 V

理想MOS系统C的作为 VG 的函数,在形式上应该是一样的。

6.4 实际MOS的电容—电压特性

界面陷阱和氧化物电荷的影响

N

a