sop封装引脚标准

元件封装及基本脚位定义说明

元件封裝及基本腳位定義說明PS:以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装.普通的元件封装有针脚式封装(DIP)与表面贴片式封装(SMD)两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。

)元件按电气性能分类为:电阻,电容(有极性,无极性),电感,晶体管(二极管,三极管),集成电路IC,端口(输入输出端口,连接器,插槽),开关系列,晶振,OTHER(显示器件,蜂鸣器,传感器,扬声器,受话器)1.电阻: I.直插式[1/20W 1/16W 1/10W 1/8W 1/4W]II.贴片式[0201 0402 0603 0805 1206]III.整合式[0402 0603 4合一或8合一排阻]IIII.可调式[VR1~VR5]2.电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II.有极性电容分两种:电解电容[一般为铝电解电容,分为DIP与SMD两种]钽电容[为SMD型: A TYPE (3216 10V) B TYPE (3528 16V) C TYPE (6032 25V) D TYPE (7343 35V)]3.电感: I.DIP型电感II.SMD型电感4.晶体管: I.二极管[1N4148 (小功率) 1N4007(大功率) 发光二极管(都分为SMD DIP两大类)]II.三极管[SOT23 SOT223 SOT252 SOT263]5.端口: I.输入输出端口[AUDIO KB/MS(组合与分立) LAN COM(DB-9) RGB(DB-15) LPT DVI USB(常规,微型) TUNER(高频头) GAME 1394 SATA POWER_JACK等] II.排针[单排双排(分不同间距,不同针脚类型,不同角度)过IDE FDD,与其它各类连接排线.III.插槽[DDR (DDR分为SMD与DIP两类) CPU座PCIE PCI CNR SD MD CF AGP PCMCIA]6.开关:I.按键式II.点按式III.拔动式IIII.其它类型7.晶振: I.有源晶振(分为DIP与SMD两种包装,一個電源PIN,一個GND PIN,一個訊號PIN)II.无源晶振(分为四种包装,只有接兩個訊號PIN,另有外売接GND)8.集成电路IC:I.DIP(Dual In-line Package):双列直插封装。

元件封装类型

常用元件封装类型1.DIP(dual in-line package)双列直插式封装封装材料有塑料和陶瓷两种。

引脚中心距2.54mm,引脚数从6 到64。

封装宽度通常为15.2mm。

图1 DIP封装(1)SDIP (shrink dual in-linepackage)窄节距双列直插式封装收缩型DIP。

插装型封装之一,形状与DIP 相同,但引脚中心距(1.778mm)小于DIP(2.54mm),引脚数从14 到90。

材料有陶瓷和塑料两种。

DIP 类封装尺寸DIP8图2 DIP8DIP16DIP18DIP20DIP24S(SKDIP24)DIP28(DIP28W)SDIP28SDIP30图9 SDIP302.SOP/SOIC(mall Outline Package)小外形封装派生类型有SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP (甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT (小外形晶体管)、SOIC(小外形集成电路)等。

(1)SO:宽度7.62mm(300mil),引脚间距1.27mm图10 SO封装(2)SOJ:宽度8.89mm(350mil),引脚间距1.27mm,引脚数从20 至40图11 SOJ封装(3)SOP窄体SOP20封装实为SOP-20,宽度9.652mm(380mil),引脚间距1.27mm 宽体SOP20封装实为SOL-20或SOW-20或SO20W,宽度11.684mm (460mil),引脚间距1.27mm图12 SOP封装(4)SSOP:引脚间距0.635mm(25mil)图13 SSOP封装(5)TSOP:厚度低于1.27mm ,引脚间距1.27mm(50mil)图14 TSOP封装(6)TSSOP:厚度低于1.27mm,引脚间距0.65mm(26mil)SOP类封装尺寸SOP8图15 SOP8 SOP16图16 SOP16 SOP20SOP28SOP30图19 SOP30 SSOP 类SSOP20SSOP24图21 SSOP24 TSSOP 类TSSOP16TSSOP20图23 TSSOP3、BGA (ball grid array)球栅阵列封装表面贴装型封装之一。

常用元器件封装标准尺寸

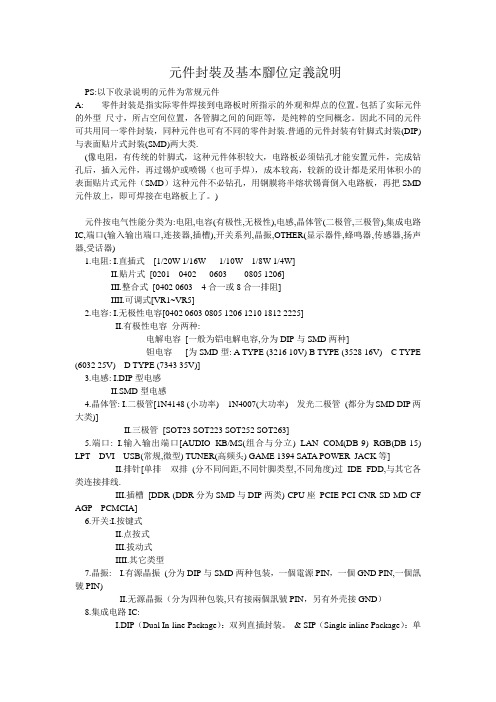

常用元器件封装标准尺寸王永建整理尺寸中的计量单位 mil / 40 = mmDIP 双列封装QFP 四方扁平封装引脚数宽度 mil 引脚数宽度8,14,16,18,20 300 44,48 10*10mm22 400 5214*14mm 24,28,32,40,42,48600 64,80,100,12814*20mm 28,32,40(陶瓷)600 144,160,20828*28mm SKDIP 小双列封装SOP 小外形封装引脚数宽度 mil 引脚数宽度 mil22,24,28,32 300 8,14 15016,14,16,18,20 30028 33032 45044 500SDIP 缩短双列封装SSOP 缩短小型封装引脚数宽度 mil 引脚数宽度 mil40,42,64 600 16,24,28 150 TSSOP 缩短细小型封装20,28 209 引脚数: 8, 20, 48引脚数: 8 MSOP, 48 BQSOP48,56 300NSOP 窄小形双列封装TSOP 细小封装引脚数宽度 mil 引脚数宽度16 150 28,328*13.4mm SOJ 细小封装32 8*14mm 引脚数32 8*20mm28,32QFP 四方扁平封装LQFP 矮四方扁平封装引脚数宽度引脚数宽度44,48 10*10mm 32,44,48 7*7mm52 14*14mm 44,64,80 10*10mm64,80,100,128 14*20mm 80 12*12mm,14*14mm144,160,208 28*28mm 100,128 14*14mm,14*20mm144 20*20mm 208 28*28mmTQFP 细四方扁平封装 其他引脚数宽度类型引脚数 80,100 14*14mmPLCC 塑封大空间封装 SOT-23, SOT-223, SOT-89SOT-25SOT-26 TO-92TO-220, TO-252, TO-26328, 32, 44, 52, 68, 84 3 5 6 3,4 3塑封 DIP/SKDIP/SDIP 尺寸 (单位: mil)SOP/NSOP 封装尺寸(单位: mil)TSSOP 封装尺寸(单位: mil)SOJ 封装尺寸(单位: mil)QFP/LQFP/TQFP 封装尺寸(单位: mil)PLCC 封装尺寸(单位: mil)SOT 23 封装尺寸(单位: mil)SOT 223SOT 89SOT 25SOT 26TO 92TO 220TO 252TO 263 (DD2 PAK)。

SO、SOP、SOIC封装详解

精心整理SO、SOP、SOIC封装详解2015-12-15一、简介SOP(Small Outline Package)小外形封装,指鸥翼形(L形)引线从封装的两个侧面引出的一种表面贴装型封装。

1968~1969年飞利浦公司就开发出小外形封装(SOP)。

以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT (小外形晶体管)、SOIC(小外形集成电路)等。

在引脚数量不超过40的领域,SOP是普及最广的表面贴装封装,典型引脚中心距 1.27mm(50mil),其它有0.65mm、0.5mm;引脚数多为8~32;装配高度不到1.27mm的SOP也称为TSOP。

表1、常用缩写代码含义代码英文全称中文全称SOP Small Outline Package 小外形封装。

在EIAJ标准中,针脚间距为 1.27mm (50mil)的此类封装被称为“SOP”。

请注意,JEDEC 标准中所称的“SOP”具有不同的宽度。

SOIC Small Outline Integrated Circuit 小外形集成电路。

有时也称为“SO”或“SOL”,在JEDEC标准中,针脚间距为 1.27mm (50mil)的此类封装被称为“SOIC”。

请注意,EIAJ标准中所称的“SOIC”封装具有不同的宽度。

SO Small Outline (SOP的别称)DSO Dual Small Out-lint 双侧引脚小外形封装(SOP 的别称)SOL Small?Out-Line?L-leaded?package 按照JEDEC标准对SOP?所采用的名称SOW Small Outline Package(Wide-Type) 宽体SOP。

部分半导体厂家采用的名称SSOP Shrink Small Outline Package 缩小外形封装VSOP Very Small Outline Package 甚小外形封装VSSOP Very Shrink Small Outline Package 甚缩小外形封装TSOP Small Outline Package 薄小外形封装TSSOP Thin Shrink Small Outline Package 薄的缩小外形封装MSOP Mini Small Outline Package 迷你小外形封装。

SO、SOP、SOIC封装详解

SO、SOP、SOIC封装详解2015-12-15一、简介SOP(Small Outline Package)小外形封装,指鸥翼形(L形)引线从封装的两个侧面引出的TSSOP Thin Shrink Small Outline Package薄的缩小外形封装MSOP Mini Small Outline Package迷你小外形封装。

Analog Devices公司将其称为“micro SOIC”,Maxim公司称其为“SO/uMAX”,而国家半导体(NationalSemiconductor)公司则称之为“Mini SO”SOJ Small Out-Line J-Leaded Package J 形引脚小外型封装SOT Small Outline Transistor小外形晶体管二、宽体、中体、窄体以及SO、SOP、SOIC之争。

在事实上,针对SOIC封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准JEDEC (美国联合电子设备工程委员会)和EIAJ(日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及SO、SOP、SOIC”几个概念之间争得死去活来。

还有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC和EIAJ这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:1、单从字面上理解,其实SO=SOP=SOIC。

2、混乱现象主要出现在管脚间距的封装上,多为74系列的数字逻辑芯片。

3、两个标准对代码缩写各有自己的习惯:EIAJ习惯上使用SOP(体宽);JEDEC习惯上使用SOIC(与两种体宽);也有些公司并不遵守这个习惯,如UTC,使用SOP(与两种体宽);另有很多制造商使用SO、DSO、SOL等。

SSOPSOPDIPQFNBGAFPGA等包封类型有什么区别要点

LZ好,1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚 BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA(butt joint pin grid array) 表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

元件封装及基本脚位定义说明

元件封裝及基本腳位定義說明PS:以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装.普通的元件封装有针脚式封装(DIP)与表面贴片式封装(SMD)两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD)这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。

)元件按电气性能分类为:电阻,电容(有极性,无极性),电感,晶体管(二极管,三极管),集成电路IC,端口(输入输出端口,连接器,插槽),开关系列,晶振,OTHER(显示器件,蜂鸣器,传感器,扬声器,受话器)1.电阻: I.直插式[1/20W 1/16W 1/10W 1/8W 1/4W]II.贴片式[0201 0402 0603 0805 1206]III.整合式[0402 0603 4合一或8合一排阻]IIII.可调式[VR1~VR5]2.电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II.有极性电容分两种:电解电容[一般为铝电解电容,分为DIP与SMD两种]钽电容[为SMD型: A TYPE (3216 10V) B TYPE (3528 16V) C TYPE (6032 25V) D TYPE (7343 35V)]3.电感: I.DIP型电感II.SMD型电感4.晶体管: I.二极管[1N4148 (小功率) 1N4007(大功率) 发光二极管(都分为SMD DIP两大类)]II.三极管[SOT23 SOT223 SOT252 SOT263]5.端口: I.输入输出端口[AUDIO KB/MS(组合与分立) LAN COM(DB-9) RGB(DB-15) LPT DVI USB(常规,微型) TUNER(高频头) GAME 1394 SA TA POWER_JACK等] II.排针[单排双排(分不同间距,不同针脚类型,不同角度)过IDE FDD,与其它各类连接排线.III.插槽[DDR (DDR分为SMD与DIP两类) CPU座PCIE PCI CNR SD MD CF AGP PCMCIA]6.开关:I.按键式II.点按式III.拔动式IIII.其它类型7.晶振: I.有源晶振(分为DIP与SMD两种包装,一個電源PIN,一個GND PIN,一個訊號PIN)II.无源晶振(分为四种包装,只有接兩個訊號PIN,另有外売接GND)8.集成电路IC:I.DIP(Dual In-line Package):双列直插封装。

元器件封装及基本管脚定义说明(精)

元器件封装及基本管脚定义说明以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装. 普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD )这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。

元件按电气性能分类为:电阻, 电容(有极性, 无极性, 电感, 晶体管(二极管, 三极管, 集成电路IC, 端口(输入输出端口, 连接器, 插槽, 开关系列, 晶振,OTHER(显示器件, 蜂鸣器, 传感器, 扬声器, 受话器1. 电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4II. 贴片式 [0201 0402 0603 0805 1206]贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5III. 整合式 [0402 0603 4合一或8合一排阻]IIII. 可调式[VR1~VR5]2. 电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II. 有极性电容分两种:电解电容 [一般为铝电解电容, 分为DIP 与SMD 两种]钽电容 [为SMD 型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25VD TYPE (7343 35V]3. 电感: I.DIP型电感II.SMD 型电感4. 晶体管: I.二极管[1N4148 (小功率 1N4007(大功率发光二极管 (都分为SMD DIP两大类]II. 三极管 [SOT23 SOT223 SOT252 SOT263]常见的to-18(普通三极管)to-22 (大功率三极管to-3 (大功率达林顿管5. 端口: I.输入输出端口[AUDIO KB/MS(组合与分立 LAN COM(DB-9RGB(DB-15 LPT DVI USB(常规, 微型 TUNER(高频头 GAME 1394 SATA POWER_JACK等]II. 排针[单排双排 (分不同间距, 不同针脚类型, 不同角度过 IDE FDD, 与其它各类连接排线.III. 插槽 [DDR (DDR分为SMD 与DIP 两类 CPU座 PCIE PCI CNR SD MD CF AGP PCMCIA]6. 开关:I.按键式II. 点按式III. 拔动式IIII. 其它类型7. 晶振: I. 有源晶振 (分为DIP 与SMD 两种包装,一個電源PIN ,一個GND PIN,一個訊號PINII.无源晶振(分为四种包装, 只有接兩個訊號PIN ,另有外売接GND )8. 集成电路IC:I.DIP (Dual In-line Package):双列直插封装。

sop8引脚定义

sop8引脚定义SOP8引脚定义引脚定义是指芯片封装的引脚在电路设计中的功能及连接方式的规定。

SOP8是一种常见的封装形式,其中SOP代表了Small Outline Package,即小外形封装。

SOP8封装具有8个引脚,下面将详细介绍这些引脚的定义和功能。

1. 引脚1(VCC):这是芯片的电源引脚,用于提供正常工作所需的电压。

在设计中,应该将此引脚连接到电源正极。

2. 引脚2(GND):这是芯片的地引脚,用于提供电路的参考电平。

在设计中,应该将此引脚连接到电源的负极或地。

3. 引脚3(IN1):这是输入引脚1,用于接收外部输入信号。

在设计中,应该根据具体需求将该引脚连接到输入信号源。

4. 引脚4(IN2):这是输入引脚2,与引脚3类似,也用于接收外部输入信号。

在设计中,应根据需要将该引脚连接到另一个输入信号源。

5. 引脚5(OUT1):这是输出引脚1,用于输出芯片内部处理后的信号。

在设计中,应该将此引脚连接到需要接收输出信号的电路或器件。

6. 引脚6(OUT2):这是输出引脚2,与引脚5类似,也用于输出芯片内部处理后的信号。

在设计中,应根据需要将该引脚连接到另一个需要接收输出信号的电路或器件。

7. 引脚7(NC):这是未连接引脚(No Connection),表示该引脚在芯片内部未连接到任何功能电路。

在设计中,应该将此引脚悬空,不进行连接。

8. 引脚8(NC):与引脚7相同,也是未连接引脚,不进行连接。

总结:SOP8封装的芯片具有8个引脚,其中包括VCC和GND用于供电和地引脚。

IN1和IN2是输入引脚,用于接收外部输入信号。

OUT1和OUT2是输出引脚,用于输出芯片内部处理后的信号。

NC引脚是未连接引脚,不进行连接。

在设计中,应根据具体需求正确连接这些引脚,以确保芯片正常工作。

PCB元件封装库命名规则简介

PCB元件封装库命名规则简介1、集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N和W两种,用来表示器件的体宽N为体窄的封装,体宽300mil,引脚间距2.54mmW为体宽的封装, 体宽600mil,引脚间距2.54mm如:DIP-16N表示的是体宽300mil,引脚间距2.54mm的16引脚窄体双列直插封装2 、集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M和W三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距1.27mmM为介于N和W之间的封装,体宽208mil,引脚间距1.27mmW为体宽的封装, 体宽300mil,引脚间距1.27mm如:SO-16N表示的是体宽150mil,引脚间距1.27mm的16引脚的小外形贴片封装若SO前面跟M则表示为微形封装,体宽118mil,引脚间距0.65mm3、电阻SMD贴片电阻命名方法为:封装+R如:1812R表示封装大小为1812的电阻封装碳膜电阻命名方法为:R-封装如:表示焊盘间距为英寸的电阻封装水泥电阻命名方法为:R-型号如:R-SQP5W表示功率为5W的水泥电阻封装4、电容无极性电容和钽电容命名方法为:封装+C如:6032C表示封装为6032的电容封装SMT独石电容命名方法为:RAD+引脚间距如:表示的是引脚间距为200mil的SMT独石电容封装电解电容命名方法为:RB+引脚间距/外径如:.4表示引脚间距为200mil, 外径为400mil的电解电容封装5、二极管整流器件命名方法按照元件实际封装,其中BAT54和1N4148封装为1N41486 、晶体管命名方法按照元件实际封装,其中SOT-23Q封装的加了Q以区别集成电路的SOT-23封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名7、晶振HC-49S,HC-49U为表贴封装,AT26,AT38为圆柱封装,数字表规格尺寸如:AT26表示外径为2mm,长度为8mm的圆柱封装8、电感、变压器件电感封封装采用TDK公司封装9、光电器件贴片发光二极管命名方法为封装+D来表示如:0805D表示封装为0805的发光二极管直插发光二极管表示为LED-外径如LED-5表示外径为5mm的直插发光二极管数码管使用器件自有名称命名10、接插SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm如:表示针脚间距为2.54mm的7针脚单排插针DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm如:表示针脚间距为2.54mm的10针脚双排插针其他接插件均按E3命名封装库元件命名一、多引脚集成电路芯片封装SOIC、SOP、TSOP在元器件封装库中的命名含义。

sop焊盘设计标准

sop焊盘设计标准

SOP焊盘设计的标准如下:

1.焊盘中心距等于引脚中心距。

2.单个引脚焊盘设计的一般原则是:Y=T+b1+b2=1.5~2mm

(b1=0.3~1.0mm,b2=0.3~0.7mm),X=1~1.2W。

3.相对两排焊盘内侧距离按下式计算(单位:mm):G=F-K,其中G

为两排焊盘之间距离,F为元器件壳体封装尺寸,K为系数,一般取

0.25mm。

4.良好的焊点应该包含前端的“脚趾”和后端的“脚跟”,而且焊点的强度

主要由这两个部分保证。

5.焊盘的长度比焊盘宽度更为重要,焊盘的可靠性主要取决于焊盘的长

度。

在焊盘长度的选择中,需要考虑引脚的长度以及引脚内侧和外侧的延伸长度。

6.对于0805以上的电阻、电容元件,或引脚间距在1.27mm以上的SO、

SOJ封装的IC芯片,宽度一般在元件实际引脚的基础上再加一个数量值,这个数据范围为0.1~0.25mm;而对于0.64(包括0.64mm)引脚间距以下的芯片,焊盘宽度等于引脚宽度。

7.对于细间距的QFP封装的器件,有时焊盘的宽度相对引脚来说还要

适当减小(如果两引脚间需要有引线出来的话)。

以上标准仅供参考,实际应用中可能还需要根据具体的产品和工艺进行调整。

SOSOPSOIC封装详解

S O、S O P、S O I C封装详解2015-12-15一、简介SOP(SmallOutlinePackage)小外形封装,指鸥翼形(L形)引线从封装的两个侧二、宽体、中体、窄体以及SO、SOP、SOIC之争。

在事实上,针对SOIC封装的尺寸标准,不同的厂家分别或同时遵循了两种不同的标准JEDEC(美国联合电子设备工程委员会)和EIAJ(日本电子机械工业协会),结果就导致了“宽体、中体和窄体”三个分支概念的出现,把很多人搞得晕头转向,也激起很多砖家在“宽体、中体、窄体以及SO、SOP、SOIC”几个概念之间争得死去活来。

还有许多来自不同半导体制造商的封装不属于上述标准。

另外,JEDEC和EIAJ这两种标准的名称也并非总是被用于制造商的产品目录和数据表中,除此以外,不同制造商之间的描述系统也不统一。

其实,静下心来,仔细看一下两个封装标准,再对比几种常见的元件尺寸,不难发现,规律其实并不复杂:1、单从字面上理解,其实SO=SOP=SOIC。

2、混乱现象主要出现在管脚间距1.27mm的封装上,多为74系列的数字逻辑芯片。

3、两个标准对代码缩写各有自己的习惯:EIAJ习惯上使用SOP(5.3mm体宽);JEDEC习惯上使用SOIC(3.9mm与7.5mm两种体宽);也有些公司并不遵守这个习惯,如UTC,使用SOP(3.9mm与7.5mm两种体宽);另有很多制造商使用SO、DSO、SOL等。

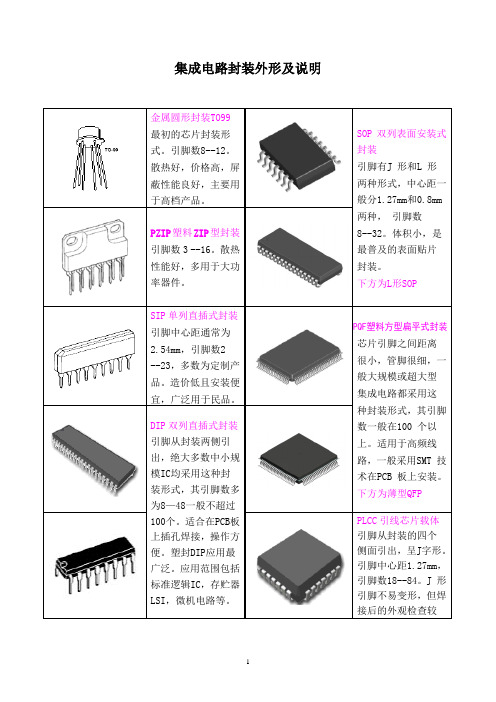

4、两个标准规定的尺寸不同,互不兼容,其差异主要体现在宽度WB和WL上,下表给出了常用SOP封装在两个标准下的WB与WL值:表2、SOP封装在JEDEC和EIAJ标准下的尺寸差异引脚数WB(体宽)WL(总宽)JEDEC EIAJ JEDEC EIAJmil mm mil mm mil mm mil mm 8150 3.8208 5.3236 6.03107.914150 3.8208 5.3236 6.03107.916150/3003.8/7.5208 5.3236/4006.0/10.23107.9183007.5208 5.340010.23107.9203007.5208 5.340010.23107.9243007.5208 5.340010.23107.9注:更详细的尺寸信息请参见文件MS-012(JEDEC)、MS-013(JEDEC)和TYPE-II 其中WB与WL的含义如下:三、举例1、74HC573,仙童公司可同时提供两种封装:SOIC-20---JEDECMS-013,0.300"=7.5mmWideSOP-20---EIAJTYPEII,5.3mmWide2、LM2904,TI公司可同时提供两种封装:SOIC-8(D)---JEDECMS-012variationAA,0.150"=3.8mmWideSO-8(PS)---5.3mmWide3、74HC595,TI公司可同时提供三种封装:SOIC-16(D)---JEDECMS-012variationAC,0.150"=3.8mmWideSOIC-16(DW)---JEDECMS-013variationAA,0.150"=3.8mmWideSO-16(NS)---5.3mmWide四、推荐的标注方法为避免误解,在设计选型时,尽可能将同一型号的不同制造商的datasheet收集齐全,按制造商的datasheet给出符合通用习惯的代号,对于多种封装尺寸共存的型号(如74HC595),在后面注明尺寸:宽*长,如SOIC-16(3.9*9.9)、SOIC-16(7.5*10.3)、SOP-16(5.3*10.2)。

sop封装引脚标准

SOP封装引脚标准一、引言在集成电路设计过程中,往往需要将设计好的芯片进行封装,以便与其他电子元件连接。

在封装过程中,一个非常重要的环节就是设定引脚标准。

本文将详细讨论SOP封装引脚标准的相关内容。

二、理解SOP封装引脚标准2.1 SOP封装简介SOP(Small Outline Package)是一种常用的封装形式,其尺寸相对较小,适合于高密度电路板设计。

SOP封装的引脚位置和设计是按照一定的标准进行布置的。

2.2 引脚标准的重要性引脚标准在封装设计中起到关键作用。

合理的引脚标准可以保证芯片和电路板之间的连接可靠,减少电路板布线难度,提高生产效率。

因此,制定合理的引脚标准至关重要。

三、制定SOP封装引脚标准的步骤3.1 确定芯片功能在制定SOP封装引脚标准之前,首先需要对芯片的功能进行分析和确定。

不同的功能需要有不同的引脚连接方式和分布规则。

3.2 布置引脚位置根据芯片的功能和布局要求,确定引脚的位置。

通常情况下,需要考虑引脚的对称性,相邻引脚之间的间距,以及引脚与芯片边缘的距离等因素。

3.3 划分引脚类型根据芯片的功能,将引脚分为不同的类型,如电源引脚、输入引脚、输出引脚、时钟引脚等。

根据引脚的类型,可以确定引脚的位置和数量。

3.4 定义引脚标号对于每个引脚,需要定义其唯一的引脚标号。

引脚标号可以通过数字、字母或者其组合来表示,在设计中起到引脚识别的作用。

3.5 确定引脚电气特性针对不同的引脚类型,需要确定其电气特性,如输入电阻、输出电压等。

这些特性将直接影响到引脚的设计和连接。

四、SOP封装引脚标准的设计规范4.1 引脚编号规范1.引脚编号应按照逆时针方向进行,从左上角开始编号。

2.引脚编号应采用字母和数字的组合表示,避免使用特殊字符。

3.引脚编号应清晰可见,避免重叠或者模糊不清。

4.2 引脚布局规范1.引脚布局应具有对称性,以便于焊接和连接。

2.相邻引脚之间的间距应保持一致,并预留一定的空间用于扩展焊盘。

集成电路封装外形及说明

集成电路封装外形及说明

说明:

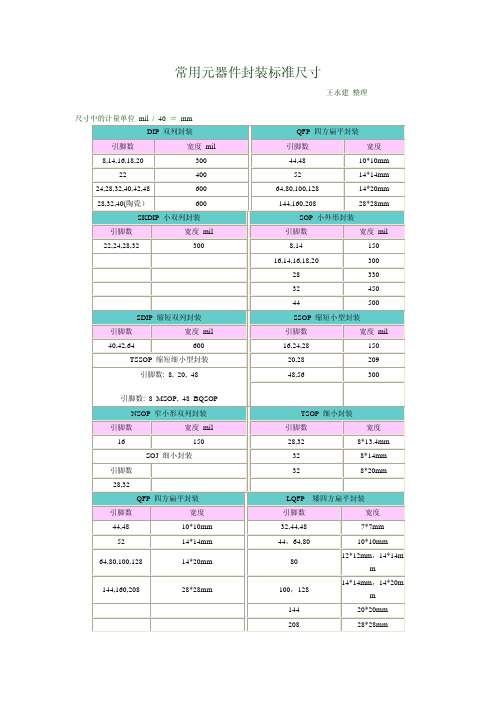

常见的封装材料有:塑料、陶瓷、玻璃、金属等,现在基本采用塑料封装。

按封装形式分:普通双列直插式,普通单列直插式,小型双列扁平,小型四列扁平,圆形金属,体积较大的厚膜电路等。

按封装体积大小排列分:最大为厚膜电路,其次分别为双列直插式,单列直插式,金属封装、双列扁平、四列扁平为最小。

两引脚之间的间距分:普通标准型塑料封装,双列、单列直插式一般多为2.54±0.25 mm,其次有2mm(多见于单列直插式)、1.778±0.25mm(多见于缩型双列直插式)、1.5±0.25mm,或1.27±0.25mm(多见于单列附散热片或单列V 型)、1.27±0.25mm(多见于双列扁平封装)、1±0.15mm(多见于双列或四列扁平封装)、0.8±0.05~0.15mm(多见于四列扁平封装)、0.65

±0.03mm(多见于四列扁平封装)。

双列直插式两列引脚之间的宽度分:一般有7.4~7.62mm、10.16mm、12.7mm、15.24mm等数种。

双列扁平封装两列之间的宽度分(包括引线长度:一般有6~6.5±mm、7.6mm、10.5~10.65mm 等。

四列扁平封装40 引脚以上的长×宽一般有:10×10mm(不计引线长度)、13.6

×13.6±0.4mm(包括引线长度)、20.6×20.6±0.4mm(包括引线长度)、8.45×8.45±0.5mm(不计引线长度)、14×14±0.15mm(不计引线长度)等。

标准贴片封装尺寸参数

标准贴片封装尺寸参数标准贴片封装尺寸参数是电子元器件制造中的关键指标,对封装技术的发展和应用有重要意义。

本文将对标准贴片封装尺寸参数进行详细介绍。

标准贴片封装尺寸参数包含了封装的几何形状、外观面积、连接脚的结构形式、尺寸和位置等多个参数。

其中,最基本的参数有以下几个:1.芯片尺寸:指芯片的长、宽和厚度。

常用的芯片尺寸有0603、0805、1206等。

2.外形尺寸:指封装的边长、厚度和高度等。

常用的外形尺寸有SOT23、SOP8、QFP64等。

3.引脚间距:指相邻引脚的距离。

常用的引脚间距有0.5mm、0.65mm、0.8mm、1.0mm等。

4.引脚数目:指封装的引脚数目。

常用的引脚数目有2、4、6、8、14、16、20、24、28、32、40、48、64、80、100等。

5.引脚形式:指引脚的形状。

常用的引脚形式有直脚、弯脚、SMD、BGA等。

6.引脚排列方式:指引脚的排列方式。

常用的引脚排列方式有单列、双列、四列等。

7.引脚位置:指引脚在封装中的位置。

常用的引脚位置有中心位置、四周位置等。

以上是标准贴片封装尺寸参数的基本内容,还有一些其他的参数也是需要注意的,如引脚长度、引脚形态等。

对于不同的封装,其尺寸参数会有不同的要求。

例如,对于耐高温封装,需要更高的尺寸精度和更严格的实现标准,而对于低成本的贴片封装,尺寸精度要求相对较低。

总之,标准贴片封装尺寸参数是电子元器件生产过程中必须重视的重要指标,其精度和准确性不仅关系到产品的品质和稳定性,也关系到整个生产过程的流畅程度和成本效益。

因此,在生产过程中,要严格执行相关的标准,确保封装尺寸参数的精度和稳定性。

IC器件引脚和封装-叶华山老师

面具有型号丝印、方向指示缺口、

方向指示缺口

第一脚指示标记。国际上采用IC

脚位的统一标准:将IC的方向指

示缺口朝左边,靠近自己一边的

引脚从左至右为第一脚至第N脚,

远离自己的一边从右至左为第N

第一脚指示

+1脚至最后一脚。

注:有部分厂家生产的IC不是用方向指示缺口来标识,而是用一条丝

印来表示方向辨认脚位的方法和上述方法一样。

6

为IC的第一脚,按逆时针方向依

次为第二脚至第N脚。

5

IC器件封装形式

正面

底面

方向指示标记

4、BGA( 底部锡球贴片);随着技术的更新集成电路的集成度不断提 高,功能强大的IC不断被设计出来,引脚不断增多QFP方式已不能解决 需求,因此BGA封装方式被设计出来,它充分利用IC与PCB接触面积, 大幅的利用IC 的底面和垂直焊接方式,从而解决了引脚的问题。

3

IC器件封装形式

第一脚指示

2)SOT IC(双排直列),IC的丝印

面具有型号丝印、方向指示缺口

(有部分厂家的产品没有指示缺

口)、第一脚指示标记。国际上

采用IC脚位的统一标准:将IC的

第一脚指示标记朝左边并靠近自

己,靠近自己一边的引脚从左至

右为第一脚至第N脚,远离自己

的一边从右至左为第N+1脚至最

后一脚。

4

IC器件封装形式

方向指示标记

3、QFP IC(四方形贴片):在

集成电路的集成量和功能的增加

的同时,IC的引脚不断的增多,

而IC的体积确不能增大太多,因

此,IC为解决这个矛盾设计出四

边都有引脚的四方形IC封装形式。

正四方IC引脚脚位辨认方法:

sop8封装湿敏等级

sop8封装湿敏等级

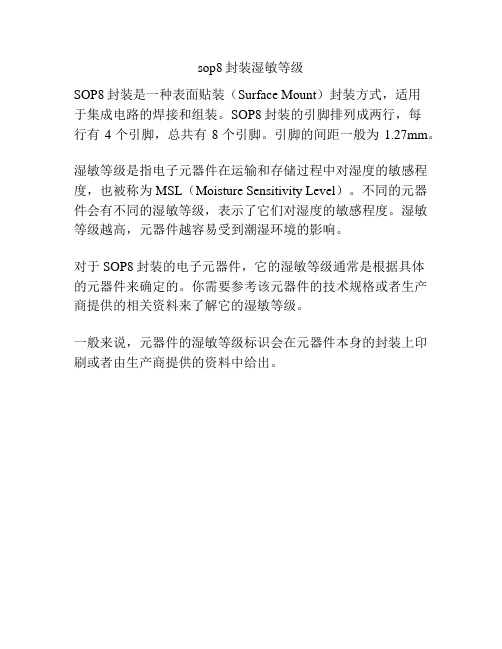

SOP8封装是一种表面贴装(Surface Mount)封装方式,适用

于集成电路的焊接和组装。

SOP8封装的引脚排列成两行,每

行有4个引脚,总共有8个引脚。

引脚的间距一般为1.27mm。

湿敏等级是指电子元器件在运输和存储过程中对湿度的敏感程度,也被称为MSL(Moisture Sensitivity Level)。

不同的元器件会有不同的湿敏等级,表示了它们对湿度的敏感程度。

湿敏等级越高,元器件越容易受到潮湿环境的影响。

对于SOP8封装的电子元器件,它的湿敏等级通常是根据具体

的元器件来确定的。

你需要参考该元器件的技术规格或者生产商提供的相关资料来了解它的湿敏等级。

一般来说,元器件的湿敏等级标识会在元器件本身的封装上印刷或者由生产商提供的资料中给出。

sop封装尺寸

双侧引脚扁平封装,是SOP的别称。

此前曾用此称法现在已基本不用。

SOP(small Out-Line Package)小外形封装。

表面帖装型封装之一,引脚从封装两侧引出呈海鸥翼状(L字形)。

材料有塑料和陶瓷两种。

另外也叫SOL和DFP。

SOP除了用于存储器LSI外,也广泛用于规模不太大的ASSP等电路。

在输入输出端子不超过10~40的领域,SOP是普及最广泛的表面帖装封装。

引脚中心距1.27mm,引脚数从8~44。

另外,引脚中心距小于1.27mm的SOP也称为SOOP;装配高度不到1.27mm的SOP也称为TSOP。

还有一种带散热片的SOP。

SOP EIAJ TYPE II 14L

SSOP 16L

SSOP

集成电路封装标准芯片封装图:

SOP-8 DIMENSION

SOP-14 DIMENSION

SOP-16 DIMENSION

SOP-20 DIMENSIPON

SOP-24 DIMENSION

SOP-28 DIMENSION

T SSOP-8 DIMENSION。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

sop封装引脚标准

SOP封装引脚标准是一种常用的电子元器件封装方式,它的完全名称是小外形塑封封装(Small Outline Package)。

SOP封装被广泛应用于各种电子设备中,尤其是在移动设备如手机、平板电脑等中得到了广泛应用。

SOP封装引脚标准的特点是引脚密集且封装尺寸小,因此可以在较小的空间内集成更多的功能,同时也更容易进行自动化焊接和处理,提高了生产效率和质量。

SOP封装可以分为SOP8、SOP16、SOP24、SOP28等不同规格尺寸,用户可以根据实际需求选择不同类型的SOP 封装引脚标准。

另外,SOP封装引脚标准还具有遮光性好、不易老化、高可靠性等特点。

由于其封装方式紧凑,可以有效地减小电路板的面积,降低产品成本,提高产品性能和生产效率,因此广受欢迎。

在实际应用中,用户还需要注意些诸如底面是否供电、引脚间距、引脚排列等细节问题。

在进行SOP封装引脚标准选择时,应根据实际需求、器件功耗等综合因素进行选择,以获得最佳的高效和稳定性能。

总之,SOP封装引脚标准是一种常用的电子元器件封装方式,具有体

积小、性能稳定、效率高等多项优点,被广泛应用于电子产品生产中。

在实际应用中,用户还需注意细节问题,以充分发挥其优势。