2.1_引脚式封装

常用PCB封装图解

常用集成电路芯片封装图doc文档可能在WAP端浏览体验不佳。

建议您优先选择TXT,或下载源文件到本机查看。

PCB 元件库命名规则2.1 集成电路(直插)用DIP-引脚数量+尾缀来表示双列直插封装尾缀有N 和W 两种,用来表示器件的体宽N 为体窄的封装,体宽300mil,引脚间距2.54mm W 为体宽的封装, 体宽600mil,引脚间距 2.54mm 如:DIP-16N 表示的是体宽300mil,引脚间距2.54mm 的16 引脚窄体双列直插封装 2.2 集成电路(贴片)用SO-引脚数量+尾缀表示小外形贴片封装尾缀有N、M 和W 三种,用来表示器件的体宽N为体窄的封装,体宽150mil,引脚间距 1.27mm M 为介于N 和W 之间的封装,体宽208mil,引脚间距1.27mm W 为体宽的封装, 体宽300mil,引脚间距 1.27mm 如:SO-16N 表示的是体宽150mil,引脚间距1.27mm 的16 引脚的小外形贴片封装若SO 前面跟M 则表示为微形封装,体宽118mil,引脚间距0.65mm 2.3 电阻 2.3.1 SMD 贴片电阻命名方法为:封装+R 如:1812R 表示封装大小为1812 的电阻封装2.3.2 碳膜电阻命名方法为:R-封装如:R-AXIAL0.6 表示焊盘间距为0.6 英寸的电阻封装 2.3.3 水泥电阻命名方法为:R-型号如:R-SQP5W 表示功率为5W 的水泥电阻封装 2.4 电容 2.4.1 无极性电容和钽电容命名方法为:封装+C 如:6032C 表示封装为6032 的电容封装 2.4.2 SMT 独石电容命名方法为:RAD+引脚间距如:RAD0.2 表示的是引脚间距为200mil 的SMT 独石电容封装 2.4.3 电解电容命名方法为:RB+引脚间距/外径如:RB.2/.4 表示引脚间距为200mil, 外径为400mil 的电解电容封装 2.5 二极管整流器件命名方法按照元件实际封装,其中BAT54 和1N4148 封装为1N4148 2.6 晶体管命名方法按照元件实际封装,其中SOT-23Q 封装的加了Q 以区别集成电路的SOT-23 封装,另外几个场效应管为了调用元件不致出错用元件名作为封装名 2.7 晶振HC-49S,HC-49U 为表贴封装,AT26,AT38 为圆柱封装,数字表规格尺寸如:AT26 表示外径为2mm,长度为8mm 的圆柱封装 2.8 电感、变压器件电感封封装采用TDK 公司封装 2.9 光电器件 2.9.1 贴片发光二极管命名方法为封装+D 来表示如:0805D 表示封装为0805 的发光二极管 2.9.2 直插发光二极管表示为LED-外径如LED-5 表示外径为5mm 的直插发光二极管2.9.3 数码管使用器件自有名称命名 2.10 接插件 2.10.1 SIP+针脚数目+针脚间距来表示单排插针,引脚间距为两种:2mm,2.54mm 如:SIP7-2.54 表示针脚间距为 2.54mm 的7 针脚单排插针 2.10.2 DIP+针脚数目+针脚间距来表示双排插针,引脚间距为两种:2mm,2.54mm 如:DIP10-2.54 表示针脚间距为2.54mm 的10 针脚双排插针 2.10.3 其他接插件均按E3 命名 2.11 其他元器件详见《Protel99se 元件库清单》3 SCH 元件库命名规则3.1 单片机、集成电路、二极管、晶体管、光电器件按照器件自有名称命名 3.2 TTL74 系列和COMS 系列是从网上找的元件库,封装和编码需要在画原理图时重新设定 3.3 电阻 3.3.1 SMD 电阻用阻值命名,后缀加-F 表示1%精度,如果一种阻值有不同的封装,则在名称后面加上封装如:3.3-F-1812 表示的是精度为1%,封装为1812,阻值为 3.3 欧的电阻 3.3.2 碳膜电阻命名方法为:CR+功率-阻值如:CR2W-150 表示的是功率为2W,阻值为150 欧的碳膜电阻 3.3.3 水泥电阻命名方法为:R+型号-阻值如:R-SQP5W-100 表示的是功率为5W,阻值为100 欧的水泥电阻 3.3.4 保险丝命名方法为:FUSE-规格型号,规格型号后面加G 则表示保险管如:FUSE-60V/0.5A 表示的是60V,0.5A 的保险丝 3.4 电容3.4.1 无极性电容用容值来命名,如果一种容值有不同的封装,则在容值后面加上封装。

ADA01AL-B升级版_led调光开关,pwm调光开关规格书V2.1

OUT1

VDD

C S1

GND TOUCH0

ADA01 AL_B

D1 R3

LED

8

7

R2 1K

6

5

R4 1

10 K touch p ad

Q1 NPN

VCC

73 50

1

Vin

Vout

C3 C5

10 4 10 uF/16 V

2 GND

模式五

1

C1 10 3 2

3

3

+ C4

C2

4

10 4

10 uF/16 V

VCI

OUT1

VDD

C S1

GND TOUCH0

ADA01 AL_B

D1 R3

LED

8

7 VDD

6

R2 1K

5

R4 1

10 K touch p ad

Q1 NPN

模式一 第 6 页 共 10 页

VCC

73 50

1

Vin

Vout

C3 C5

10 4 10 uF/16 V

2 GND

1

C1 10 3 2

3

3

第 3 页 共 10 页

3:分段调光的 PWM 频率大约在 4KHz 左右

以下为详细功能说明:

模式一、不带亮度记忆不带亮度缓冲的触摸无级调光功能如下: 1) TOUCH0 触控输入对应 OUT1 一路输出。初始上电时,灯为关灭状态。 2) 点击触摸(触摸持续时间小于 550ms)时,可实现灯光的亮灭控制。一次点击触摸,灯亮;再一次点击触

2、特性简介

为方便用户灵活定义不同的产品特点,ADA01AL(升级版)共设置了 6 种不同的输出模式。TOUCH0 触 摸输入对应 OUT1 以及 OUT2 灯光控制输出。CS2/OUT2 为输入输出功能复用管脚,既可以用作调光输出 OUT2, 也可以用作选项输入 CS2。共有六种功能可选,由 CS1/CS2/CS3 管脚上电前的输入状态来决定。具体如下:

晶圆电阻封装尺寸表

晶圆电阻封装尺寸表1. 引言晶圆电阻是一种用于电子元器件中的被动元件,主要用于电阻调节、电流限制和电压分压等功能。

晶圆电阻的封装尺寸表是制造商为方便用户选择和使用晶圆电阻而提供的重要参考资料。

本文将详细介绍晶圆电阻封装尺寸表的内容和使用方法。

2. 晶圆电阻封装尺寸表的组成部分晶圆电阻封装尺寸表通常包含以下几个主要部分:2.1 产品基本信息•产品型号:标识晶圆电阻的型号,用于唯一标识不同规格的晶圆电阻。

•封装类型:标识晶圆电阻的封装形式,例如贴片封装、插件封装等。

•封装尺寸:描述晶圆电阻的封装尺寸,包括长度、宽度和高度等参数。

2.2 封装图示封装图示通常以二维或三维形式展示晶圆电阻的封装结构,帮助用户直观了解晶圆电阻的外观和尺寸。

2.3 封装尺寸表格封装尺寸表格是晶圆电阻封装尺寸表的核心内容,列出了不同型号晶圆电阻的封装尺寸参数。

通常包括以下列: - 型号:晶圆电阻的型号。

- 长度:晶圆电阻的长度尺寸。

- 宽度:晶圆电阻的宽度尺寸。

- 高度:晶圆电阻的高度尺寸。

- 引脚数:晶圆电阻的引脚数量。

- 引脚间距:晶圆电阻的引脚间距尺寸。

2.4 其他信息封装尺寸表还可以包含其他相关信息,如封装材料、焊盘形状、包装方式等,以满足用户对晶圆电阻的更多需求。

3. 晶圆电阻封装尺寸表的使用方法晶圆电阻封装尺寸表是用户选择和使用晶圆电阻的重要参考资料,以下是一些常见的使用方法:3.1 查找型号用户可根据需要的晶圆电阻型号,在封装尺寸表中查找对应型号的封装尺寸参数,以确保选择的晶圆电阻与应用需求相匹配。

3.2 比较尺寸用户可通过封装尺寸表中的尺寸参数,对不同型号的晶圆电阻进行比较,以选择最适合自己应用的封装尺寸。

3.3 设计封装对于需要自行设计电路板的用户,封装尺寸表中的尺寸参数可以作为设计参考,帮助用户合理布局电路,确保晶圆电阻的封装尺寸与其他元件相协调。

4. 总结晶圆电阻封装尺寸表是制造商为方便用户选择和使用晶圆电阻而提供的重要参考资料。

fcbga参数

FCBGA参数引言1. 了解FCBGA在现代集成电路封装技术中,FCBGA(FlipChip Ball Grid Array)是一种常见的封装形式。

它采用翻转封装技术,通过在芯片表面引出一系列小球连接芯片与基板,实现了高密度、高性能的集成电路封装。

在使用FCBGA封装时,了解其参数对于设计和应用具有重要的意义。

2. 参数的重要性FCBGA的性能和应用特性与其参数直接相关。

掌握这些参数可以帮助工程师更好地进行电路设计、布局和热管理,确保芯片在不同应用场景下能够稳定可靠地工作。

3. 本文结构本文将深入介绍FCBGA的相关参数,包括封装形式、引脚数量、球网阵列结构等。

通过对这些参数的详细解析,读者可以更全面地了解FCBGA的特性,为其在电子设计中的应用提供指导。

正文1. FCBGA封装形式1.1 封装外形尺寸FCBGA的封装外形尺寸直接影响其在电路板上的布局和安装。

这包括了整个封装的高度、宽度和长度等方面的尺寸,工程师需要根据具体的应用场景选择适合的封装尺寸。

1.2 封装材料封装材料是影响FCBGA散热性能和机械强度的关键因素。

不同的材料会对封装的热导率和机械稳定性产生影响,工程师需根据具体需求权衡各种材料的特性。

2. 引脚数量与布局2.1 引脚数量FCBGA的引脚数量直接关系到其可连接的信号数量和种类。

高引脚数量可以提供更多的输入输出接口,但也需要更为复杂的布线设计。

2.2 引脚布局引脚的布局对于电路板的设计至关重要。

良好的引脚布局可以降低信号干扰、提高电路板布局密度和简化布线,因此工程师需要仔细考虑引脚的位置和排列方式。

3. 球网阵列结构3.1 小球直径和间距球网阵列结构中小球的直径和间距影响着焊接工艺和可靠性。

小球直径较小可以提供更高的连接密度,但也增加了焊接难度。

3.2 焊球材料焊球的材料直接关系到焊点的可靠性和封装的耐用性。

通常使用的焊球材料有铅锡合金、锡铜合金等,选择适合应用场景的焊球材料至关重要。

封装标准介绍(简化版)

芯片的封装技术已经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

下面将对具体的封装形式作详细说明。

封装形式塑封体尺寸mm*mm*mm引线间距mm/mil跨度mm/milDIP8L9.25*6.35*3.32.54/1007.62/300DIP14L19.1*6.35*3.32.54/1007.62/300DIP16L19.1*6.35*3.32.54/1007.62/300DIP18L22.9*6.5*3.32.54/1007.62/300DIP20L26.23*6.55*3.32.54/1007.62/300DIP24L31.76*13.8*3.852.54/10015.24/600DIP28L37.05*13.8*3.8515.24/600DIP40L52.25*13.8*3.85 2.54/10015.24/600DIP42L52.25*13.8*3.85 2.54/10015.24/600HDIP12L19.1*6.35*3.3 2.54/1007.62/300SDIP24L22.9*6.55*3.3 1.778/707.62/300SDIP28L25.6*8.8*3.3 1.778/7010.16/400SIP8L19.2*6.5*2.8 2.54/100___SIP9L22.3*5.6*3.2 2.54/100___SIP10L24.2*6.7*3.25 2.54/100___HSIP12L2.54/100___ZIP16L24.2*6.7*3.25 1.50/59___SOP8L4.9*3.9*1.38 1.27/505.72/225SOP14L8.65*3.9*1.38 1.27/505.72/225SOP16L9.9*3.9*1.38 1.27/505.72/225SOP16L(W) 10.3*7.5*2.3 1.27/509.53/375SOP20L12.8*7.5*2.3 1.27/509.53/375SOP24L15.4*7.5*2.3 1.27/509.53/375SOP28L18.09*7.5*2.3 1.27/509.53/37519*7.6*2.3 1.27/509.53/375HSOP28L 18.9*7.5*2.3 0.8/31.59.53/375SSOP10L(1) 4.9*3.9*1.38 1/39.33.9/153.5SSOP16L6.2*5.3*1.5 0.62/25.65.3/209SSOP20L7.2*5.3*1.5 0.62/25.65.3/209SSOP24L8.2*5.3*1.5 0.62/25.65.3/209SSOP24L(1) 13*6*1.81/39.36/236SSOP28L 10.2*5.3*1.75 0.62/25.65.3/209TSOP44L 18.44*10.16*1 0.8/31.510.16/400TSOP54L22.2*10.16*10.8/31.510.16/400QFP44L10*10*2.10.8/31.5_____LQFP64L14*14*1.40.8/31.5_____TO251(5L)6.5*5.5*2.31.27/50_____TO252(5L)6.5*5.5*2.31.27/50_____SOT89(3L)4.5*2.5*1.51.5/59_____SOT223(3L)6.5*3.5*1.652.3/91_____一、DIP PGA封装DIP,引脚少于等于24,一般主体宽度为300mil(窄体).多于24脚,多为600mil(宽体)。

2.1_引脚式封装

封装的必要性

LED芯片只是一块很小的固体,它的两个 电极要在显微镜下才能看见,加入电流之后他

才会发光。

在制作工艺上,除了要对LED芯片的两

个电极进行焊接,从而引出正极、负极之外,

同时还需要对LED芯片和两个电极进行保护。

LED封装解决的问题

电学:电极连接保护

光学:光束整形

热学:散热

LEHale Waihona Puke 封装的电学问题

一、二次光学设计的概念 一次光学设计概念:将LED芯片封装成LED器 件,必须进行光学设计,这种设计在业内称为 一次光学设计。 决定出光角度、光通量大小(光强大小)光强 分布、色温范围(色温分布)。 二次光学设计概念:使用LED器件时,整个系 统的出光效果、光强、色温的分布等光学参数 也需要设计,称为二次光绪设计

测试LED的光电参数、检验外形尺寸,同时根据客户 要求对LED产品进行分选。 11.包装 将成品进行计数包装。超高亮LED需要防静电包装。

管理机制和生产环境

做好LED的四大重要因素 人、物、设备、生产环境 说明:

只是从生产的角度 公司企业:物料采购、生产、销售、人事、财务、 信息——企业六管

第二章led封装led的封装led的封装属led的中游产业靠设备封装的必要性封装的必要性ledled芯片只是一块很小的固体它的两个芯片只是一块很小的固体它的两个电极要在显微镜下才能看见加入电流之后他电极要在显微镜下才能看见加入电流之后他才会发光

第二章 LED封装

LED的封装 属LED的中游产业 靠设备

LED封装的方式的选择

LED pn结区发出的光子是非定向的,即向各个方向 发射有相同的几率,因此并不是芯片产生的所有光都可以 发射出来。 能发射多少光,取决于半导体材料的质量、芯片结构、 几何形状、封装内部材料与包装材料。 因此,对LED封装,要根据LED芯片的大小、功率大 小来选择合适的封装方式。

半导体封装简介

EOL– Molding(注塑)

L/F L/F

Cavity

Molding Tool(模具)

➢EMC(塑封料)为黑色块状,低温存储,使用前需先回温。其特 性为:在高温下先处于熔融状态,然后会逐渐硬化,最终成型。

➢Molding参数:

Molding Temp:175~185°C;Clamp Pressure:3000~4000N; Transfer Pressure:1000~1500Psi;Transfer Time:5~15s; Cure Time:60~120s;

半导体封装简介

一、半导体封装介绍 二、封装主要原材料 三、封装工艺流程—IC芯片 四、封装工艺流程—功率模块

一、半导体封装介绍

1.1 半导体工艺流程

目前半导体材料已经发展到第三代,第一代以硅(Si)为代表材料;第二代以砷化镓(GaAs)为代表材料; 第三代以碳化硅(SiC)和氮化镓(GaN)为主流材料。目前Si仍然是半导体行业使用最多的材料。

二、封装原材料简介 2.1 wafer(晶圆)

【Wafer】晶圆

2.2 【Lead Frame】引线框架

➢提供电路连接和Die的固定作用; ➢主要材料为铜,会在上面进行镀银、NiPdAu等材料; ➢L/F的制程有Etch和Stamp两种; ➢易氧化,存放于氮气柜中,湿度小 于40%RH; ➢除了BGA和CSP外,其他Package都会采用Lead Frame,BGA采用的是Substrate;

➢磨片时,需要在正面(Active Area)贴胶带保护电路区域, 同时 研磨背面。研磨之后,去除胶带,测量厚度;

FOL– Wafer Saw晶圆切割

Wafer Mount 晶圆安装

Wafer Saw 晶圆切割

微电子封装技术-课后习题答案

3.1简述包封技术的特点。

答:

包封通过将有源器件和环境隔离来实现保护元器件的功能,同时芯片和封装材料形成一体,以达到机械保护的目的。包封一般采用有机材料,成本相对较低,在民用集成电路封装中占主导地位。但其耐湿性不佳,影响了产品可靠性。

3.2简述包封技术常用的材料。

答:

从基质材料的综合特性来看,最常用的包封材料分为四种类型:环氧类、氰酸酯类、聚硅酮类和氨基甲酸乙酯类,目前IC封装使用邻甲酚甲醛型环氧树脂体系的较多。具有耐湿、耐燃、易保存、流动充填性好、电绝缘性高、应力低、强度大和可靠性好等特点。

硅片的背面减薄技术主要有磨削、研磨、干式抛光(Dry Polishing)、化学机械平坦工艺(CMP)、电化学腐蚀(Electrochemical Etching)、湿法腐蚀(Wet Etching)、等离子增强化学腐蚀Plasma Enhanced Chemical Etching,PECE)、常压等离子腐蚀(Atmosphere Downstream Plasma Etching,ADPE)等。

3.5简述模注成形技术的常见问题。

答:

有塑封产品无论是采用先进的传递模注封装还是采用传统的单注塑模封装,塑封成形缺陷总是普遍存在的,而且无法完全消除。1.未填充;2.冲丝;3.气泡或气孔;4.麻点;5.开裂;6.溢料;7.其他缺陷,在塑封中还有粘污、偏芯等缺陷。

3.6简述模注成形技术常见问题的解决对策。

2.4简述芯片贴装的常用工艺技术。

答:

贴装的方式主要共晶粘贴法、焊接粘贴法、导电胶粘贴法和玻璃胶粘贴法。共晶粘贴法是利用金-硅合金(一般是69%的金和31%的Si),在363℃时的共晶熔合反应使IC芯片粘贴固定。焊接粘贴法是将芯片背面淀积一定厚度的Au或Ni,同时在焊盘上淀积Au-Pd-Ag和Cu的金属层。这样就可以使用Pb-Sn合金制作的合金焊料将芯片焊接在焊盘上。导电胶进行芯片贴装的工艺用针筒或注射器将黏着剂涂布在芯片焊盘上,然后将芯片精确地放置到焊盘的黏着剂上面。玻璃胶粘贴芯片先以盖印、网印、点胶等技术将玻璃胶原料涂布在基板的芯片座上,将IC芯片放置在玻璃胶上后,再将封装基板加热至玻璃熔融温度以上即可完成粘贴。

FE2.1中文资料

FE2.1高速七端口USB2.0集线器控制芯片一引言FE2.1芯片是高度集成,高品质,高性能,低能耗,总体花费低的高速七端口USB2.0集线器解决方案。

FE2.1适应多样任务译码器(MMT)风格,借此达到最大的数据输出。

六个(而不是两个)非周期数据处理缓冲器被用来将潜在的传输干扰降至最低。

整个设计基于状态机控制原理,降低了相应延迟时间。

该芯片中没有使用微控制器。

为了保证高品质,整个芯片覆盖测试扫描链—包括高速模块(频率480MHz),所以在运行前可以检测所有逻辑组件。

芯片拥有特殊的自检建立模式,可以在封装和测试阶段测试高速、全速和低速模拟前端结束(AFE)元件。

通过使用0.18微米制造工艺和全面电源/时钟控制机制实现低功耗。

若无必要,芯片的大部分不会被锁住。

特点:■低功耗:□七个下行端口全部在高速模式工作时电流为155mA,□一个下行端口工作在高速模式下电流为66mA,■完全符合通用串行总线规范修订版2.0(USB2.0):□上传端口支持高速度(480MHz信)和全速(12MHZ)模式;□7下行端口支持高速(480MHz信),全速(12MHz)和低速(1.5MHz)模式;。

■集成USB2.0收发器;■集成上传1.5KΩ上拉电阻、下行1.5KΩ下拉电阻和串行电阻;■集成5V转3.3V和1.8V的电压调节器;■集成上电复位电路■集成12MHz的振荡器与反馈电阻和晶体负载电容;■集成12MHz转480MHz锁相回路;■多种任务译码器□一个任务译码器负责一个下行端口;□单任务译码器采用备用接口0,多任务译码器用备用接口1;□每个任务译码器可以处理64个开始分散任务、32个完全分散任务和6个无周期任务;■只支持自供电模式■主板配置选项——□成组或单独的电源控制模式选项;□全局、多模块或单模块过流保护选项;□配置可拆卸或不可拆卸下行设备;□选择下行端口数目;■电可擦可编程只读存储器配置选项——□供应商ID、产品ID和设备发行数量;□可拆卸或不可拆卸下行设备配置;□编号;□下行端口数目:■综合状态指标支持□标准下行端口状态指示灯(每个下行端口有绿色和琥珀色LED控制指示灯);□集线器工作/暂停状态LED指示灯;■支持微软Windows98SE/ME,2000,XP和Vista操作系统;■支持Mac OS 8.6及以上操作系统;■支持Linux 内核2.4.20及以上系统;封装:■64针脚LQFP(大小:10×10mm)■48针脚LQFP (大小: 7×7mm )框图(面积大小:10×10mm)64针脚封装引脚分配图48针脚封装引脚分配图引脚说明表格备注:1.OVCJ[7:2]针脚配有可选择的内部上拉电阻。

电容封装类型

电容封装类型1. 引言电容是一种电子元件,用于储存电荷和能量。

电容封装类型是指电容器的外观和尺寸规格,不同的封装类型适用于不同的应用场景。

本文将对常见的电容封装类型进行详细探讨。

2. 电容封装类型的分类根据封装形式和尺寸,电容封装类型可以分为以下几种:2.1 直插式封装(Through-Hole Mounting)直插式封装是最早使用的电容封装类型之一。

它的引脚以直径较大的圆柱形状向下延伸,以便于焊接固定在电路板上。

直插式封装的优点是结构稳定,耐高温和更易于手工焊接。

然而,由于直插式封装占用的空间较大,适用于较宽的间距和较大的尺寸要求。

2.2 表面贴装封装(Surface Mounting)表面贴装封装是现代电子产品中最常见的电容封装类型。

它的引脚位于封装底部,可以直接粘贴在印刷电路板(PCB)的表面,通过焊接固定。

表面贴装封装具有体积小、重量轻、适应高密度布局的优点,使得其适用于大部分电子产品,例如移动设备、计算机和通信设备。

2.2.1 BGA封装(Ball Grid Array)BGA封装是表面贴装封装中的一种。

它的引脚位于底部,以小球形状排列成网格,与PCB连接。

BGA封装的优点是引脚密度高,可提供更好的电气性能和导热性能。

它在高速处理器和芯片组等集成电路的封装中得到广泛应用。

2.2.2 QFN封装(Quad Flat No-leads Package)QFN封装是另一种常见的表面贴装封装类型。

它的引脚位于底部,并采用四边平面排列。

QFN封装的优点是占用空间小、封装厚度薄,适应高密度集成电路布局的要求。

它广泛应用于消费类电子设备和汽车电子等领域。

2.3 焊接贴片封装(Chip Soldering)焊接贴片封装是一种将电容直接焊接在PCB上的封装方式。

它的尺寸较小,通常为方形,便于高速贴片设备进行快速和自动化的焊接。

焊接贴片封装常用于高密度的电路板应用,例如移动设备、耳机和嵌入式系统。

2.4 简单封装(Leadless Package)简单封装是一种无引脚的电容封装类型。

浅析电子实习之电烙铁使用方法

浅析电子实习之电烙铁使用方法毕兴会(江苏省徐州技师学院,江苏徐州221151)舀商要]本文对最基本焊接工具电烙铁的使用方法避行了论述.从最常用的引线元件到贴片元件,从细节到具体操作。

[芙蝴]电烙铁;引脚型元件;贴片型元件随着电子元器件的封装更新换代越来越快,电路板E的元件越来越少,越来越密,管脚越来越细,电路板越来越小。

而且电路板上大量使用表面贴装元件,倒装芯片等元件,这无—例外的说明了电子工业已期向小型化、微型化方面发展,手工焊接难度也随之增加,在焊接当中稍有不慎就会损伤元器件,或引起焊接不良,所以工作人员必须对焊接原理,焊接过程,焊接方法,焊接质量的评定,及电子基础有一定的了解。

1焊接工具电烙铁是焊接中最常用的工具,焊接是否成功很大一部分是看对它的操控怎么样。

—般来说,电烙铁的功率越大,热量越大,烙铁头的温度也越高。

像我1门对硬件改造选用20W的内热式(30—40W外热式)电烙铁足够了,使用功率过大容易烧坏元件,一般二极管、三极管结点温度超过200℃就会损坏。

现在常用的电烙铁有外热式和内热式两种,内热式电烙铁热效率高,加热速度快。

外热式电烙铁功率较高,使用方法相同,但在市场上内热式电烙铁的配件较多,所以建议使用内热式电烙铁。

普通电烙铁在使用前必须先给烙铁头镀上一层焊锡。

具体方法是:首先把烙铁头锉成需要的形状,然后接上电源,当烙铁头温度升至能融化锡时,将松香涂在烙铁头上,再涂上—层焊锡,直至烙铁头的刃面部挂上一层锡,便可使用。

r2焊接方法现在的电路阪上主要有两大类元器件,一类是直插式引脚式元't t-,另一类是贴片类元件。

以下就按这两大类元件来具体的说一说每类元件的焊接方法。

2.1直播引脚式元件焊接方法22-1烙铁头与两个被焊件的接触方式烙铁头应同时接触到相互连接的2个被焊接件(如焊脚与焊盘),烙铁一般倾斜30,45度,应避免只与其中一个被焊接件接触。

当两个被焊接元件受热面积相差悬殊时,应适当调整烙铁倾斜角度,使烙铁与焊接面积大的被焊接元件倾斜角减小,使焊接面积较大的被焊件与烙铁的接触面积增大,热传导能力加强。

SMT常见贴片元器件封装类型和尺寸

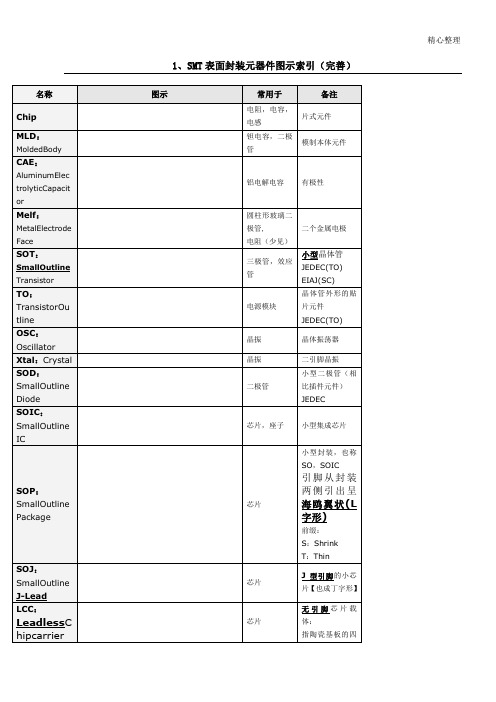

1、SMT 表面封装元器件图示索引(完善)名称 图示 常用于备注Chip电阻,电容,电感 片式元件MLD :Molded Body钽电容,二极管模制本体元件CAE :Aluminum Electrolytic Capacitor铝电解电容有极性Melf :MetalElectrode Face圆柱形玻璃二极管,电阻(少见)二个金属电极SOT :Small Outline Transistor三极管,效应管小型晶体管JEDEC(TO) EIAJ(SC)TO :Transistor Outline电源模块晶体管外形的贴片元件 JEDEC(TO)OSC : Oscillator晶振 晶体振荡器Xtal :Crystal晶振 二引脚晶振SOD:SmallOutlineDiode二极管小型二极管(相比插件元件)JEDEC SOIC:SmallOutline IC芯片,座子小型集成芯片SOP:SmallOutlinePackage芯片小型封装,也称SO,SOIC引脚从封装两侧引出呈海鸥翼状(L字形)前缀:S:ShrinkT:Thin SOJ:SmallOutlineJ-Lead芯片J型引脚的小芯片【也成丁字形】LCC:LeadlessChipcarrier芯片无引脚芯片载体:指陶瓷基板的四个侧面只有电极接触而无引脚的表面贴装型封装。

也称为陶瓷QFN 或QFN-C PLCC:plasticleadedChipcarrier芯片引脚从封装的四个侧面引出,呈丁字形或J型,是塑料制品。

DIP:Dual In-linePackage变压器,开关,芯片双列直插式封装:引脚从封装两侧引出QFP:QuadFlat Package芯片四方扁平封装:引脚从四个侧面引出呈海鸥翼(L)型。

基材有陶瓷、金属和塑料三种。

BGA:BallGrid Array 芯片塑料:P陶瓷:C球形栅格阵列:在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚QFN:Quad FlatNo-lead 芯片四方扁平无引脚器件SON:Small Outline No-Lead芯片小型无引脚器件2、SMT物料基础知识一. 常用电阻、电容换算:1.电阻(R):电阻:定义:导体对电流的阻碍作用就叫导体的电阻。

贴片电阻常见封装有9种,用两种尺寸代码来表示

1.0mrn>:0.5mm 尺寸贴片电咀缪1 005(0402)贴片电阻常见封装有9种,用两种尺寸代码来表示。

一种尺寸代码是由4位数字表示的EIA(美国电子工业协会)代码,前两位与后两位分别表示电阻的长与宽,以英寸为单位。

我们常说的0603封装就是指英制代码。

另一种是米制代码,也由4位数字表示,其单位为毫米。

下表列出贴片电阻封装英制和公制的关系及详细的尺寸:贴片元件的封装一、零件规格:(a)、零件规格即零件的外形尺寸,SMT发展至今,业界为方便作业,已经形成了一个标准零件系列,各家零件供货商皆是按这一标准制造。

标准零件之尺寸规格有英制与公制两种表示方法,如下表英制表示法1206 0805 0603 0402公制表示法3216 2125 1608 1005含义L:1.2inch(3.2mm)W:0.6inch(1.6mm)L:0.8inch(2.0mm)W:0.5inch(1.25mm)L:0.6inch(1.6mm)W:0.3inch(0.8mm)L:0.4inch(1.0mm)W:0.2inch(0.5mm)注:a、L (Length):长度;W (Width):宽度;inch:英寸b、1inch=25.4mm(b)、在(1)中未提及零件的厚度,在这一点上因零件不同而有所差异,在生产时应以实际量测为准。

(c)、以上所讲的主要是针对电子产品中用量最大的电阻(排阻)和电容(排容),其它如电感、二极管、晶体管等等因用量较小,且形状也多种多样,在此不作讨论。

(d)、SMT发展至今,随着电子产品集成度的不断提高,标准零件逐步向微型化发展,如今最小的标准零件已经到了0201。

二、常用元件封装1)电阻:最为常见的有0805、0603两类,不同的是,它可以以排阻的身份出现,四位、八位都有,具体封装样式可参照MD16仿真版,也可以到设计所内部PCB库查询。

注:ABCD四类型的封装形式则为其具体尺寸,标注形式为L X S X H1210具体尺寸与电解电容B类3528类型相同0805具体尺寸:2.0 X 1.25 X 0.5 (公制表示法)1206具体尺寸:3.0 X 1.5 0X 0.5 (公制表示法)2)电阻的命名方法1、5%精度的命名:RS - 05 K 102 JT2、1 % 精度的命名:RS - 05 K 1002 FTR 一表示电阻S 一表示功率0402 是1/16W、0603 是1/10W、0805 是1/8W、1206 是1/4W、1210 是1/3W、1812 是1/2W、2010 是3/4W、2512 是1W。

领芯微LCM08F003G内核微控制器 产品手册

杭州领芯微电子有限公司LCM08F003GT20 LCM08F003GS20 LCM08F003GQ20内置高精度振荡、12位ADC 、4个定时器、2路UART、1路I2C、1路SPI、16K Flash存储器、低失调OPA和256B可编程E2PROM的8位MCU主要特点⚫8位单周期8051内核CPU- 兼容MCS51指令集。

- 双DPTR,增加软件陷阱指令。

⚫片上存储器- 16K+64字节FLASH,数据保持时间大于10年,写周期>1000次。

- 256字节EEPROM,数据保持时间大于10年,写周期>10000次。

- 1024字节SRAM:256字节SRAM,768字节XRAM。

- 支持在系统编程(ISP),仅需4个管脚(包括VDD和VSS在内)。

- 支持FLASH/EEPROM的单字节写操作。

- 支持FLASH分页加密,每512字节单独读写可控。

⚫电源和复位- 工作电压:VDD=1.8V~5.5V。

- 内置上电复位电路(POR)。

- 内置低压复位电路(LVR),8个复位点可选:1.8V、2.0V、2.5V、2.6V、2.8V、3.0V、3.5V、4.0V。

- 内置低压检测电路(LVD),8个检测点可选:2.2V、2.4V、2.5V、2.7V、2.9V、3.1V、3.65V、4.5V。

- 内置低功耗低压复位/检测电路(LPLVD),8个检测点可选:2V、2.2V、2.5V、2.8V、3V、3.5V、4V、4.5V。

停机模式(Stop)下可用。

⚫时钟系统- 内置32KHz低频RCL。

- 内置16MHz高精度RCH,精度±1.5%,T A= -40°C~+105°C。

- 支持外部输入外部高频振荡4~16MHz,或者外部低频振荡32.768KHz,两者复用同一组管脚,由信息区配置,默认为32.768KHz振荡。

- 系统时钟分频:16/8/4/2/1/0.5/0.25MHz。

sop封装引脚标准

SOP封装引脚标准一、引言在集成电路设计过程中,往往需要将设计好的芯片进行封装,以便与其他电子元件连接。

在封装过程中,一个非常重要的环节就是设定引脚标准。

本文将详细讨论SOP封装引脚标准的相关内容。

二、理解SOP封装引脚标准2.1 SOP封装简介SOP(Small Outline Package)是一种常用的封装形式,其尺寸相对较小,适合于高密度电路板设计。

SOP封装的引脚位置和设计是按照一定的标准进行布置的。

2.2 引脚标准的重要性引脚标准在封装设计中起到关键作用。

合理的引脚标准可以保证芯片和电路板之间的连接可靠,减少电路板布线难度,提高生产效率。

因此,制定合理的引脚标准至关重要。

三、制定SOP封装引脚标准的步骤3.1 确定芯片功能在制定SOP封装引脚标准之前,首先需要对芯片的功能进行分析和确定。

不同的功能需要有不同的引脚连接方式和分布规则。

3.2 布置引脚位置根据芯片的功能和布局要求,确定引脚的位置。

通常情况下,需要考虑引脚的对称性,相邻引脚之间的间距,以及引脚与芯片边缘的距离等因素。

3.3 划分引脚类型根据芯片的功能,将引脚分为不同的类型,如电源引脚、输入引脚、输出引脚、时钟引脚等。

根据引脚的类型,可以确定引脚的位置和数量。

3.4 定义引脚标号对于每个引脚,需要定义其唯一的引脚标号。

引脚标号可以通过数字、字母或者其组合来表示,在设计中起到引脚识别的作用。

3.5 确定引脚电气特性针对不同的引脚类型,需要确定其电气特性,如输入电阻、输出电压等。

这些特性将直接影响到引脚的设计和连接。

四、SOP封装引脚标准的设计规范4.1 引脚编号规范1.引脚编号应按照逆时针方向进行,从左上角开始编号。

2.引脚编号应采用字母和数字的组合表示,避免使用特殊字符。

3.引脚编号应清晰可见,避免重叠或者模糊不清。

4.2 引脚布局规范1.引脚布局应具有对称性,以便于焊接和连接。

2.相邻引脚之间的间距应保持一致,并预留一定的空间用于扩展焊盘。

场效应管封装类型和标识_解释说明以及概述

场效应管封装类型和标识解释说明以及概述1. 引言1.1 概述场效应管(MOSFET)是一种常用的电子元件,广泛应用于电路设计和功率控制系统中。

在实际应用中,不同的场效应管需要使用不同的封装类型和标识来满足特定的需求。

1.2 文章结构本文将重点介绍场效应管封装类型和标识的相关知识。

首先,我们将解释说明什么是场效应管封装类型,包括其定义、特点和主要分类。

然后,我们将详细讨论场效应管封装标识,介绍其作用、使用方法以及常见的标识符号含义。

最后,我们将对场效应管封装进行概述,总结各种封装的主要特点和适用范围。

1.3 目的通过本文对场效应管封装类型和标识进行详细说明和概述,旨在帮助读者更好地理解场效应管及其相关标识信息,并为正确选择合适的封装类型提供参考依据。

此外,本文还将为读者提供一个全面了解场效应管封装领域发展动态的基础,在电子领域中有关设计、测试和选型方面提供实用指导。

2. 场效应管封装类型和标识2.1 场效应管封装类型解释说明场效应管(MOSFET)是一种常用的电子器件,广泛应用于各种电路中。

场效应管的封装类型决定了其外观形状、引脚布局以及安装方式等特征。

常见的场效应管封装类型有TO-92、TO-220、SOT-23等。

TO-92是一种较小型的封装,通常具有三个引脚。

其中一个引脚是栅极(Gate),另外两个引脚分别是漏极(Drain)和源极(Source)。

这种封装适用于低功率的电路应用,如小型信号放大器和开关等。

TO-220是一种较大型的封装,通常具有三个或四个引脚。

其中一个引脚是栅极,其他引脚则用于漏极和源极之间的电流传输以及导热至散热器。

这种封装适用于中高功率的电路应用,如交流驱动器、开关稳压器和电机控制等。

SOT-23是一种更小型的表面贴片封装,通常具有三个引脚。

与TO-92相比,SOT-23封装更适用于小型空间集成电路和低功耗应用,如便携式设备和手机等。

2.2 场效应管封装标识解释说明场效应管的封装标识通常是指封装型号或代号,其目的是方便对不同类型的场效应管进行识别和选择。

肖特基二极管的几中封装-概述说明以及解释

肖特基二极管的几中封装-概述说明以及解释1.引言1.1 概述肖特基二极管广泛应用于电子电路中,其性能优越且具有多种封装类型。

本文将重点探讨肖特基二极管的几种封装类型及其特点。

在开始介绍各种封装类型之前,我们先对肖特基二极管进行简要概述。

肖特基二极管是一种特殊结构的二极管,它由金属与半导体形成的异质结构组成。

相较于普通的二极管,肖特基二极管具有更快的开关速度、较低的开启电压和较小的开启电流等优点。

这些特性使得肖特基二极管在嵌入式系统、功率管理、高频电路以及模拟电路等领域得到广泛应用。

对于肖特基二极管的封装类型,本文将着重介绍TO-92和SOT-23两种常见的封装形式。

这两种封装形式具有各自的特点和适用场景,并在实际应用中得到广泛使用。

除了封装类型外,本文还将讨论封装材料的选择和封装形式的设计对于肖特基二极管性能的影响。

这些因素直接影响着器件的散热性能、电气特性以及机械可靠性等方面。

最后,我们将总结肖特基二极管的各种封装类型,并强调封装对器件性能的重要影响。

深入了解肖特基二极管封装类型的优缺点,对于正确选择合适的封装类型,提升电路性能,具有重要意义。

通过本文的阐述,我们希望读者能够全面了解肖特基二极管的封装类型及其特点,从而在实际应用中能够做出明智的选择。

1.2 文章结构本文将围绕肖特基二极管的封装类型展开论述。

首先在引言部分概述肖特基二极管的基本知识,并介绍本文的目的。

接下来在正文部分,将详细介绍肖特基二极管的封装类型,包括TO-92封装和SOT-23封装。

对于每种封装类型,将讨论其特点,包括封装材料选择和封装形式设计。

在结论部分,将总结肖特基二极管的封装类型,并强调封装对器件性能的影响。

通过本文,读者将能够全面了解肖特基二极管的几种封装类型及其特点,从而对肖特基二极管的应用和选择有更深入的认识。

希望本文能为读者提供有价值的信息,并在实际应用中起到指导作用。

1.3 目的目的部分的内容可以按照以下方式编写:目的:肖特基二极管是一种重要的电子器件,具有快速开关、低功耗和高工作频率等特点,被广泛应用于各个领域。

SMT常见贴片元器件封装类型和尺寸

精心整理1、SMT表面封装元器件图示索引(完善)一.????常用电阻、电容换算:1.电阻(R):电阻:定义:导体对电流的阻碍作用就叫导体的电阻。

无方向,用字母R表示,单位是欧姆(Ω),分:欧(Ω)、千欧(KΩ)、兆欧(MΩ)1MΩ=1000KΩ=1000000Ω1).换算方法:①.前面两位为有效数字(照写),第三位表示倍数10n次方(即“0”的个数)103=10*103=10000Ω=10KΩ471=47*101=470Ω100=10*100=10Ω101=10×101=100Ω120=12×100=12Ω②.前面三位为有效数字(照写),第四位表示倍数倍数10n次方(即“0”的个数).??1001=100*101=1000Ω=1KΩ??1632=163*102=16300Ω=16.3KΩ1470=147×100=147Ω1203=120×103Ω=120KΩ4702=470×102Ω=47KΩ?330=33×10=33pF2.3钽电容:它用金属钽或者铌做正极,用稀流酸等配液做负极,用钽或铌表面生成的氧化膜做成介质制成,其特点是体积小、容量大、性能稳定、寿命长、绝缘电阻大、温度特性好,用在要求较高的设备中。

钽电容表面有字迹表明其方向、容值,通常有一条横线的那边标志钽电容的正极。

钽电容规格通常有:A型、B型、C型、P型。

2.4电容的误差表示2.4.1常用钽电容代换参照表.1UF:105、A6、CA62.2UF:2253.3UF:335、AN6、CN6、JN6、CN694.7UF:475、JS610UF:106、JA7、AA7、GA722UF:226、GJ7、AJ7、JJ747UF:4763.电感(L)电感的单位:亨(H)、毫享(MH)、微享(μH)、纳享(NH),其中:1H=103MH=106μH=109NH 片状电感????电感量:10NH~1MH????材料:铁氧体绕线型陶瓷叠层????精度:J=±5%K=±10%M=±20%????尺寸:04020603080510081206121018121008=2.5mm*2.0mm1210=3.2mm*2.5mm ????个别示意图:贴片绕线电感??????????贴片叠层电感??1H=1000MH??1MH=1000UH??1UH=1000NH电感量4.CHIP元件规格英制?公制。

stm32f103cbt6使用手册

STM32F103CBT6是STMicroelectronics公司推出的一款32位微控制器,具有丰富的外设和强大的性能。

本使用手册将全面介绍STM32F103CBT6的性能特点、引脚定义、外设功能、编程方法等内容,帮助用户深入了解和正确使用这款微控制器。

一、STM32F103CBT6性能特点1.1 高性能STM32F103CBT6采用基于ARM Cortex-M3内核的32位RISC处理器,工作频率可达到72MHz,具有较高的计算能力和运行速度,适合对处理器性能要求较高的应用场合。

1.2 丰富的外设STM32F103CBT6集成了多种通用和专用外设,包括多个通用定时器、串行通信接口、并行接口、通用并行接口、模拟数字转换器、通用IO口等,满足了不同应用场景下的外设需求。

1.3 丰富的存储器STM32F103CBT6内置了128KB的Flash存储器和20KB的SRAM,可满足程序和数据存储的需求,同时支持在不同存储器之间进行数据传输。

1.4 低功耗设计STM32F103CBT6在设计上考虑了低功耗需求,具有多种低功耗模式和唤醒机制,可在功耗和性能之间进行灵活的平衡。

二、STM32F103CBT6引脚定义2.1 封装形式STM32F103CBT6采用LQFP48封装,包括了48个引脚,具体引脚定义如下:1)PA0-PA15:通用IO口2)PB0-PB15:通用IO口3)PC0-PC15:通用IO口4)PD0-PD2:通用IO口5)PD13-PD15:通用IO口6)PE0-PE5:通用IO口7)PF0-PF2:通用IO口8)PG0-PG2:通用IO口9)PH0-PH1:通用IO口2.2 引脚功能STM32F103CBT6的每个引脚都具有特定的功能,包括通用IO口、定时器输入输出、串行通信接口、模拟数字转换器输入等,用户在使用时需根据具体需求配置引脚功能。

三、STM32F103CBT6外设功能3.1 定时器STM32F103CBT6集成了多个通用定时器和高级定时器,可用于精确的定时和脉冲宽度调制等应用场景,具有较高的灵活性和精度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

温度、湿度可控。

相对湿度:可以表示为在相同温度下样品空气的水 蒸气压和饱和的蒸气压的比率(百分率)。

有效防静电:电脑里面的显卡(第五章详细介 绍)

LED点亮时的热量导出

引脚封装的LED中,90%的热量是由负极引 脚散发到印制电路板上的。 封装角度:引脚有铜支架和铁支架(我们平时 使用的一般是铁支架) 使用角度:印制电路板上的薄铜板面积留大, 以便于散热。较大功率加风扇,再大功率,如 大屏幕显示加空调。

5.烧结

烧结的目的是使银胶固化,烧结要求对温度进行监控, 防止批次性不良。 银胶烧结的温度一般控制在150℃,烧结时间2小时。 根据实际情况可以调整到170℃,1小时。

绝缘胶一般150℃,1小时。

6.压焊

压焊的目的将电极引到LED芯片上,完成产品内外引 线的连接工作。 LED的压焊工艺有两种:

小结

封装解决的是光学、电学、热学方面的问题。 对于引脚式封装,一次光学设计可以获得大于 80%的聚光效率,pn电极得到保护,但散热仅 靠支架导出,散热性能不理想。 尽管如此,这种LED的寿命有的可以达到数万 小时以上。

引脚式封装工艺

五大物料 五大制程

晶片 支架 银胶 固晶

金线

焊线

环氧树脂

封胶

切脚

测试

引脚式封装工艺

主要工艺

LED封装工艺

主要工艺

1.芯片检验 用显微镜检查材料表面

是否有机械损伤及麻点; 芯片尺寸及电极大小是否符合工艺要求; 电极图案是否完整。

2.扩片 由于LED芯片在划片后依然排列

电学:电极连接保护

光学:光束整形

热学:散热

LED封装的电学问题

封装的对象是芯片,芯片的尺寸小从 200×200µ m到1.666×1.666mm,其上的电极 更小,要将内部电极引到外部电极,同时要对 电极进行保护。

LED封装的光学问题

LED的pn结电子和空穴的复合产生可见、紫 外、红外光。 pn结发出的光向各个方向的几率相同。 为了使光尽可能发射到感兴趣的方向上,LED 封装要考虑封装结构对光的变换作用,即一次 光学设计。

第二章 LED封装

LED的封装 属LED的中游产业 靠设备

封装的必要性

LED芯片只是一块很小的固体,它的两个 电极要在显微镜下才能看见,加入电流之后他

才会发光。

在制作工艺上,除了要对LED芯片的两

个电极进行焊接,从而引出正极、负极之外,

同时还需要对LED芯片和两个电极进行保护。

LED封装解决的问题

对于蓝宝石绝缘衬底的蓝光、绿光LED芯片,采用绝缘胶

来固定芯片。

备胶:和点胶相反,备胶是用备胶机先把银胶涂在 LED背面电极上,然后把背部带银胶的LED安装在LED支 架上。 备胶的效率远高于点胶,但不是所有产品均适用备胶 工艺。

4.手工刺片/自动装架 将扩张后LED芯片(备胶或未备胶)安置在刺片台的 夹具上,LED支架放在夹具底下,在显微镜下用针将LED 芯片一个一个刺到相应的位置上。 手工刺片和自动装架相比有一个好处,便于随时更换 不同的芯片,适用于需要安装多种芯片的产品。 自动装架:先在LED支架上点上银胶(绝缘胶), 然后用真空吸嘴将LED芯片吸起移动位置, 再安置在相应的支架位置上。

管理机制

物料:

现场物料一定要标识清楚。 存放位置固定,不能随意乱放。 防止物料混杂。 严禁物料取错、配错、过期、受潮。 任何的小错误都会使整批产品报废。

设备:定期检修、核对。 工艺:制定工艺合理,不能随意改变工艺。

LED封装环境

净化厂房:整体10万级,局部1万级。

10万级的洁净度是指(按照美国联邦标准209E)在一 立方英尺的空间内颗粒尺寸大于等于0.5微米的粒 子数为10万个。 1英尺(ft)=0.3048米(m) 1英寸(in)=25.4毫 米(mm) 1英尺=12英寸

金丝球焊 铝丝压焊

7.点胶封装 /灌胶封装/模压封装 点胶封装基本上工艺控制的难点是气泡、多缺料、黑点。 灌胶封装:先在LED成型模腔内注入液态环氧,然后插入压焊 好的LED支架,放入烘箱让环氧固化后,将LED从模腔中脱出 即成型。

模压封装:将压焊好的LED支架放入模具中, 将上下两副模

具用液压机合模并抽真空,将固态环氧放入注胶道的入口加

常用的LED芯片封装方式包括:

引脚式封装

平面式封装 表贴封装 食人鱼封装 功率型封装

引脚式封装

引脚式封装

引脚式LED封装方式是最普通、最常用的一种 封装形式。

引脚式封装结构

LED引脚式封装采用引线架作为各种封装外型的引脚,

常见的是直径为5mm的圆柱型(简称Φ 5mm)封装。

紧密间距很小(约 0.1mm ),不利

于后工序的操作。 采用扩片机对黏结芯片的膜进 行扩张,使 LED 芯片的间距拉伸到 约0.6mm。

也可以采用手工扩张,但很容易

造成芯片掉落浪费等不良问题。

3.点胶/背胶 点胶:在LED支架的相应位置点上银胶或绝缘胶。

对于GaAs、SiC导电衬底,具有背面电极的红光、黄光、 黄绿芯片,采用银胶。

热,用液压顶杆压入模具胶道中,环氧顺着胶道进入各个LED

成型槽中并固化。

8.固化与后固化 固化是指封装环氧的固化,一般环氧固化条件在135℃, 1小时。 模压封装一般在150℃,4分钟。

9.切筋和划片 由于LED在生产中是连在一起的(不是单个),LED 采用切筋切断LED支架的连筋。

1光学设计概念:将LED芯片封装成LED器 件,必须进行光学设计,这种设计在业内称为 一次光学设计。 决定出光角度、光通量大小(光强大小)光强 分布、色温范围(色温分布)。 二次光学设计概念:使用LED器件时,整个系 统的出光效果、光强、色温的分布等光学参数 也需要设计,称为二次光绪设计

LED封装的方式的选择

LED pn结区发出的光子是非定向的,即向各个方向 发射有相同的几率,因此并不是芯片产生的所有光都可以 发射出来。 能发射多少光,取决于半导体材料的质量、芯片结构、 几何形状、封装内部材料与包装材料。 因此,对LED封装,要根据LED芯片的大小、功率大 小来选择合适的封装方式。

测试LED的光电参数、检验外形尺寸,同时根据客户 要求对LED产品进行分选。 11.包装 将成品进行计数包装。超高亮LED需要防静电包装。

管理机制和生产环境

做好LED的四大重要因素 人、物、设备、生产环境 说明:

只是从生产的角度 公司企业:物料采购、生产、销售、人事、财务、 信息——企业六管