飞思卡尔运用JMP提升半导体良率

半导体良率

半导体良率

半导体良率是指在半导体制造过程中,合格产品的数量与总生产数量之比。

良率是衡量半导体制造质量的重要指标,直接影响到产品的成本和市场竞争力。

半导体制造过程中,良率的提高是一个长期的过程。

首先,需要对生产过程进行全面的分析和优化,找出可能存在的问题和缺陷,并采取相应的措施进行改进。

其次,需要加强对生产设备的维护和保养,确保设备的正常运行和稳定性。

此外,还需要加强对员工的培训和管理,提高员工的技能和素质,减少人为因素对产品质量的影响。

在半导体制造过程中,常见的影响良率的因素包括材料质量、工艺参数、设备状态、环境条件等。

其中,材料质量是影响良率的关键因素之一。

半导体材料的质量直接影响到产品的性能和可靠性,因此需要选择优质的材料,并对材料进行严格的检测和筛选。

此外,工艺参数的控制也是提高良率的重要手段之一。

通过对工艺参数的优化和调整,可以减少产品的缺陷和不良率,提高产品的可靠性和稳定性。

在半导体制造过程中,良率的提高不仅可以降低成本,提高市场竞争力,还可以提高产品的品质和可靠性,增强用户的信任和满意度。

因此,半导体制造企业应该重视良率的提高,加强对生产过程的管理和控制,不断优化生产工艺和技术,提高产品的质量和性能,为

用户提供更加优质的产品和服务。

如何快速提高产品良率

如何快速提高产品良率现在的半导体制造要求比过去任何时候都要高。

为了满足市场的需要,半导体公司必须能够更及时和以更低的成本大批量生产更复杂的产品。

为此,客户要求制造商能够采用全新的良率管理方法,达到比以前更高的良率水平,而且能够更快地实现稳定生产。

反过来,新的良率管理方法取决于更广泛和更深入的工程分析方法,这些分析方法可以帮助半导体公司作出更加准确的判断,更快地达到稳定的良率。

通过持续的良率“学习”,自动制造技术则可以更加有效地利用这些分析结果,它不仅可以将各种条件变化反馈给生产线而且还能及时判断工艺条件发生变化时是否仍然可以达到预期结果,及时找到问题原因和解决问题。

这些新方法并不是遥远的概念,有些先进的制造商已经在使用这些方法了。

本文将简单介绍AMD公司先进的工程分析方法和自动精确制造(Automated Precision Manufacturing, APM)技术,及其与客户共同取得的成果。

快速提高良率的基本要素良率的快速提高是不断发现和解决生产过程中各种影响良率的因素,从而实现和发挥产品与工艺过程良率潜能的过程。

实现批量生产、降低平均成本、最大程度提高利润率的需求推动了良率的不断提高。

尽管通常良率学习曲线粗看起来非常平滑,实际上它是由工艺改善过程和一系列噪音以及良率异常情况叠加形成的(图1)。

图中良率上升的每个小台阶代表了工艺不断改善的趋势,而向下的摆动则代表了设备或工艺不正常引起的异常情况。

良率提高的总体速度取决于异常情况的响应和解决速度以及工艺改善的效率。

每个阶段的快速进步都需要经验丰富的工程师以及各种数据和分析结果的支持。

良率学习和提高有两种情况:根据现有工艺引进新产品;全新产品和工艺,例如新技术和新工艺的引进。

新产品旧工艺良率提高的主要内容是找到设计方面的问题并加以解决,因为其工艺通常已通过其它产品验证并固定下来。

全新产品和工艺的情况则比较复杂,因为它涉及设计和工艺、工艺目标、设备极限能力等因素的综合效应。

改善Fab良率的最佳方案

改善F a b良率的最佳方案作者:BruceWhitefield,ManuRehani和NathanStrader,LSILogicCorp2005-12-28点击:1302很久以来,定期检测每个工艺步骤增加的缺陷来验收用于生产的设备,已经成为半导体业的惯例。

对设备的缺陷状况做出的判断,对于器件的有非常重要的影响。

不论这种检测的频率和影响如何,就采用的方法而言,是相对粗糙的,而且这种数据支持系统主要是针对工程缺陷分析和传统的()技术而设计的。

本文介绍LSILogic采用最佳的设备控制方法,采用新的数据系统来改进其晶圆厂的设备颗粒。

这种方法调研了设备缺陷验收的整个企业过程,建立了一个新的数据系统构造来支持所有人在这方面的努力。

这种新的数据系统叫作YieldDRIVER,它意味着通过设备的明显改进而实现缺陷的降低。

良率和IC制造工厂利润率中最高的两个杠杆因素是芯片的良率和设备的生产率。

对以上两者都非常关键的是如图1所示的简单的设备颗粒验收检测。

检测颗粒是为了保证产品在交付之前工艺设备不会产生降低良率的缺陷检测当步工艺前后点检片上颗粒的数量,来计算增加的缺陷数量。

像半导体制造中的许多其他动向一样,器件几何尺寸和运转晶圆厂费用的无情压缩,都在推动设备颗粒特性的改善和更紧的控制。

结果之一便是如何进行缺陷检测的确切细节已经变得非常关键,同时这个过程还要足够简单,使操作人员能够每天来进行。

2002年,在LSI的Gresham晶圆厂里,出于新技术导入和良率经济效益的考量,要求设备的颗粒水平降低50%。

并且这种改善要在现有设备的基础上实现,要避免基建投资,改善总体的设备利用率而不增加成本。

更换旧的工艺设备、购买更先进的颗粒检测设备不作为选项。

授权一个工厂范围内的缺陷控制职能交叉小组来完成这个任务。

降低缺陷的途径这个缺陷控制小组决定首先来分析整个工厂范围内现存的设备缺陷控制方法,以发现改进的机会。

分析的主要发现是:●许多非常好的颗粒管理实例已经在使用之中。

基于DOE与RSM提升半导体测试良品率的方法

数理统计理论为基础处理多变量问题的一套有效方 法, 最初应用在物理实验领域[ 3 J , 近年来 , 以响应 曲面 方法和实验设计相结合 的方法被认为是一种有效的

统 计设 计方 法 ,在 电子器 件 的优化 设计 领 域取 得 了

广泛应 用 。

分布如图 1 所示。高端驱动限制 电流的数值 明显偏

本研究使用统计分析软件 M i n i t a b , 应用 实验设

计( D O E) 和 响应 曲 面方 法 ( R S M) , 以某 F芯 片 的

高端驱动限制电流为例 ,对限制 电流微调参数进行

ห้องสมุดไป่ตู้

L S L分 别 为 规 格 上 限 和规 格 下 限 , 和 仃 分 别 为

h t t p: I l www. c i c ma g. c o m

L — 一测 试

C hi na I nt egr at ed Ci r cui t

巾 国 集 成 电 路

基于 D o E与 R S M 提升半导体测试良品率的方法

刁维 虎

( 飞思卡 尔半导体有 限公 司 )

摘要: 通过 D O E与 R S M的 方法 , 利用 M i n i t a b软件 , 对 I c测试 参数 进行 优化 。 本 文 以 F芯 片的 高端驱 动

为降低工艺波动和失调对电路的影响 , 微调技术 已

经应 用 到各种 模拟 电路 设计 中[ 1 _ 。 业 界常 用到 的微 调

1 改善前 F芯片高端驱动

限 制 电流 在 最 终 测 试 中 的 状 况

高端驱 动 限制 电流测 试项 是 F芯片测 试 中最 严

方法包括激光微调 ,熔丝微调 ,齐纳二极管微调 ,

赋能半导体良率管理

赋能半导体良率管理

首先,赋能半导体良率管理可以通过引入先进的数据分析和人

工智能技木来实现。

通过对生产过程中的大量数据进行分析,可以

及时发现潜在的质量问题和生产异常,从而采取措施加以解决,提

高良率。

人工智能技术可以帮助建立预测模型,预测潜在的生产问题,并提出相应的改进方案,从而减少不良品率。

其次,赋能半导体良率管理还可以通过优化生产工艺和设备来

实现。

采用先进的工艺技术和设备可以提高生产的稳定性和一致性,从而降低不良品率。

例如,采用先进的光刻技术和化学机械抛光工

艺可以提高芯片的制造精度和表面质量,从而提高良率。

此外,赋能半导体良率管理还需要加强对供应链的管理和控制。

半导体制造涉及到大量的原材料和零部件,供应链的稳定性和质量

直接影响到最终产品的良率。

因此,加强对供应链的管理和控制,

确保原材料和零部件的质量和供应稳定性,对于提高半导体产品的

良率至关重要。

总的来说,赋能半导体良率管理需要综合运用先进的技术和方法,包括数据分析、人工智能、工艺优化和供应链管理等方面的手

段,以提高半导体制造过程中的良率,从而提高产品质量和生产效率。

这对于半导体行业的发展和竞争力具有重要意义。

飞思卡尔运用JMP提升半导体良率

飞思卡尔运用JMP提升半导体良率LUTION▲嵌入式技术飞思卡尔运用耶江P提升半导体良率SASlnstituteItic飞思卡尔(Freescale)是全球著名的微控制器、射频半导体、模块与混合信号电路、软件技术及相关管理解决方案的供应商,其前身是拥有50多年历史的摩托罗拉半导体部门,其主要客户来自于汽车、消费电子、工业品、网络和无线应用市场的10,000多家企业。

公司拥有专利5,900多项,2007年的营业收入达N57亿美元,在全球30多个国家拥有24,000多名员工,其中包括中国天津的组装测试厂和北京、上海、苏州的三个设计、研发和支持中心。

六西格玛统计分析软件JMP是SAS公司的卓越绩效统计发现引擎,应用范围包括业务可视化、数据发现、六西格玛和持续改进(可视化六西格玛、质量管理、流程优化)、研发及创新、试验设计DOE等,客户遍及半导体、机械、化工、制药、金融、汽车、钢铁、航空航天等各个行业。

半导体产品的典型宏观流程图飞思卡尔所在的半导体设计和制造行业是一个非常特殊的高科技行业,工艺流程十分复杂。

其间,来白化学、光学、机械、电子和空间等多方面的因素交织在一起,共同影响着最终产品的质量和流程的效率(参见下图)。

而且,半导体对加工精度的要求也非常苛刻,这里点,从我们常见的电路板的复杂连线上就可以体会到,半导体产品的测量尺度不是以毫米为单位的,而是以纳米为单位的(1毫米=1000000纳米)!所幸的是,在半导体的生产过程中,成千上万的测量数据被同步记录下来,为我们的分析和工艺改进工作奠定了基础。

对每一家半导体企业而言,要想在这个竞争日趋白热化的市场上生存并发展,必须提高并控制产品的良率Yield,而且要“用最快的速度做出最准确的改善反应”。

因为半导体产品的价值很大程度上取决于研发生产过程中所采用的技术,而这些技术的价值往往随着时间的推移而迅速贬值。

因此,一旦出现良率下降的质量问题,谁能够最快地发现关键因素并加以纠正,谁就能最快地转危为安,最早地向市场大规模供应成熟产品,获得最大的利润。

通吃整个半导体产业链的良率问题

通吃整个半导体产业链的良率问题“半导体产业园”—半导体知识科普每周末发布半导体产业周报平时发表半导体系列文章拒绝做新闻搬运工上两期我们聊了芯片的封装和测试问题,包括CP测试,FT测试和系统级测试(没看过的朋友可以点击这里你不知道的那些芯片测试和测试黑幕和你了解芯片封装技术吗?)。

这一次我们聊一下半导体中良率的问题。

良率是个啥?有什么用?良率是什么?准确的说,就是总共的芯片(可以是一片wafer,可以是一个批次,可以是一个产品,或者是一段时间内有多少芯片等等)。

在这些芯片测试完成后,有哪些芯片是通过测试的,两者相除就是良率,为了聊起来方便,我们就拿晶圆级测试(CP)来做例子。

下面是一片foundry寄给测试厂的wafer,现在要进行CP测试了。

现在我们假设这片wafer总共有100颗芯片,在完成CP1,CP2,CP3之后,只有92颗芯片是通过的。

所以说,我们把这一片的良率称作是92%(92/100)。

那你可能会问,那又怎么了,有92颗芯片能用,我就用92颗呗,可不是这样哦。

因为foundry是按照wafer的价格卖给fabless的,可不是按照芯片的价格卖的。

举个例子,假设一片wafer是按照1000美元的价格卖给fabless,那么如果测试的良率是98%,fabless有98颗芯片是能用的,但是如果测试的良率是68%,那只有68颗芯片能用,但是这个时候的价格仍然是1000美元。

fabless是不是赔了?所以任何一家fabless都希望拿到的wafer良率是100%(虽然这是不可能的)。

这里你也可能会问?难道foundry生产的wafer良率是0的话,难道fabless也要吃下?当然不是,每个foundry都有赔付标准,当一片wafer的良率如果低于某个值或者某条规则规定的值,而且是认定foundry的原因导致低良的话,fabless是可以找foundry索赔的。

至于具体是多少,有哪些rule,这些涉及到商业机密,我们这里就不聊了。

JMP在半导体行业的应用

JMP在半导体行业的应用(1)--用较少的硅片解决筛选实验中的混杂问题发表时间:2008-1-3 上海先进半导体股份有限公司6Sigma经理闵亚能来源:e-works关键字:6Sigma3/4部分析因设计筛选实验JMP信息化应用调查在线投稿加入收藏发表评论好文推荐打印文本当我们设计一个工艺特性实验遇到因子交互作用混杂时会怎样考虑呢?通常,解决混杂的方法是增加实验处理序列。

在这个案例中,我们展示了一个比平常更少实验处理序列的技术(3/4部分析因设计),这个技术用于刻蚀均匀性实验,从而使得它的均匀性达到目标。

实验概要问题的由来由于工艺的精度要求,实验设计在半导体工业中应用越来越广。

因为半导体生产设备正变得越来越复杂,多个工艺因子必须在同一描述中被研究。

因为有多个工艺因子,首先要考虑的往往是筛选实验。

筛选实验对于筛选主要因子及甄别交互作用效率是最高的。

因为筛选实验研究多因子而实验处理序列较少,但是,它们的结果会导致混杂。

所以它经常不能辨别因子的交互作用,而要解决之,往往是增加实验处理序列。

一个案例是气相刻蚀设备在150mm硅片转移加工200mm硅片中通过增加少量实验处理来解决混杂的问题。

为了精确描述新刻蚀工艺的气相刻蚀设备,实施了一个6因子16个处理,加上2个中心点的实验处理,分辨率为IV的筛选实验(共18个处理)。

实验分析了6个因子9个交互作用的混杂情况来达到改善均匀性的目的。

要分清哪些交互作用只有这16个处理是根本不可能的。

通常的方法是根据折叠原则增加16个处理,这些处理是增加另一个6因子完全析因实验26的1/4部分析因设计。

但这种通常的方法将要34个实验处理,几乎扩大了一倍的实验处理,这些对于时间与资源都是不允许的,所以提出了一个现实的问题:是否可能用更少的实验处理来解决此类混杂问题。

解决策略学术论文上曾发表过仅用8个实验次数来代替增加的16个处理的文章,即用26个处理来代替34个处理。

这增加的8个处理与原来的16个处理一起组成3/4部分析因实验,由于增加的8个处理,9个交互作用中的7个将被估算出来。

半导体外延工艺的良率提升

半导体外延工艺的良率提升在半导体产业中,良率分析一直是个热门话题。

投资方几十亿的资金投在晶圆制造的设备上,谁都希望能够快速收回投资成本。

而对于技术部门来说,加速良率学习并提高良率是一项重要的工作。

如果要维持一定的竞争力,就至少要求不能增加浪费在寻找和改正制造问题的时间。

谁能把良率提高10%,就可以替企业省下一年数亿的资金。

由于半导体工艺的高度复杂性,往往需要依托统计分析技术,才能突破良率提升的瓶颈,这一点在很多国内外先进的高科技企业中已经达成了共识。

例如,某全球知名的半导体公司上海厂在外延沉积的工艺处理中,OOC Rate (失控率)极高,平均水平仅为30%左右,导致生产周期拖长,严重影响了该厂的生产能力,对月产3000片的要求造成极大威胁;而且增加了额外的生产成本,严重影响公司的既定利润目标的实现。

因此,该厂领导下决心建立专案小组来解决多年来一直没有解决的顽症,改进这方面的工作。

图一 外延的工艺流程图晶圆制备中的外延基本工艺流程如图一所示,根据对OOC Rate 的初步分析发现,缺陷主要来源于RS (表面电阻阻值)、RS UNIF (表面电阻均匀性)、THK (厚度)和THK UNIF (厚度均匀性)四大类型。

再深入研究下去,发现影响这四大缺陷类型的潜在原因有很多,诸如Big etch 、Wrong Wafer 、MFC usage 、Slit purge 等等,通过在工业界内常用的鱼骨形式得到如图二所示的定性分析结果。

图二Low OCC Rate的鱼骨图分析虽然我们可以根据工程技术中的已有经验排除一些次要的原因,明确一些重要因子的设置。

但是实在无法对H2 main(即Main Flow)、H2 split(即Slit Purge)和MDOP3(即Dope Gas Flow)这三个关键因子做出明确的设定。

怎么办?还是得借助统计建模与预测来实现。

图三JMP刻画器的优化结果由图三可知,无论这些工程数据是来源于Big Data(比如日积月累的历史生产记录),还是精心设计的DOE(实验设计)结果,只要它们具有有代表性,就不仅可以精确地量化这三个关键因子对RS、RS UNIF、THK和THK UNIF的影响程度,而且可以根据其内在的模型公式,确认当H2 main=22.84、H2 split=6.21、MDOP3=95.68时,总体不良率是最低的。

如何快速提高产品良率

如何快速提高产品良率现在的半导体制造要求比过去任何时候都要高。

为了满足市场的需要,半导体公司必须能够更及时和以更低的成本大批量生产更复杂的产品。

为此,客户要求制造商能够采用全新的良率管理方法,达到比以前更高的良率水平,而且能够更快地实现稳定生产。

反过来,新的良率管理方法取决于更广泛和更深入的工程分析方法,这些分析方法可以帮助半导体公司作出更加准确的判断,更快地达到稳定的良率。

通过持续的良率“学习”,自动制造技术则可以更加有效地利用这些分析结果,它不仅可以将各种条件变化反馈给生产线而且还能及时判断工艺条件发生变化时是否仍然可以达到预期结果,及时找到问题原因和解决问题。

这些新方法并不是遥远的概念,有些先进的制造商已经在使用这些方法了。

本文将简单介绍AMD公司先进的工程分析方法和自动精确制造(Automated Precision Manufacturing, APM)技术,及其与客户共同取得的成果。

快速提高良率的基本要素良率的快速提高是不断发现和解决生产过程中各种影响良率的因素,从而实现和发挥产品与工艺过程良率潜能的过程。

实现批量生产、降低平均成本、最大程度提高利润率的需求推动了良率的不断提高。

尽管通常良率学习曲线粗看起来非常平滑,实际上它是由工艺改善过程和一系列噪音以及良率异常情况叠加形成的(图1)。

图中良率上升的每个小台阶代表了工艺不断改善的趋势,而向下的摆动则代表了设备或工艺不正常引起的异常情况。

良率提高的总体速度取决于异常情况的响应和解决速度以及工艺改善的效率。

每个阶段的快速进步都需要经验丰富的工程师以及各种数据和分析结果的支持。

良率学习和提高有两种情况:根据现有工艺引进新产品;全新产品和工艺,例如新技术和新工艺的引进。

新产品旧工艺良率提高的主要内容是找到设计方面的问题并加以解决,因为其工艺通常已通过其它产品验证并固定下来。

全新产品和工艺的情况则比较复杂,因为它涉及设计和工艺、工艺目标、设备极限能力等因素的综合效应。

JMP软件中的晶圆图( Wafer Map)分析

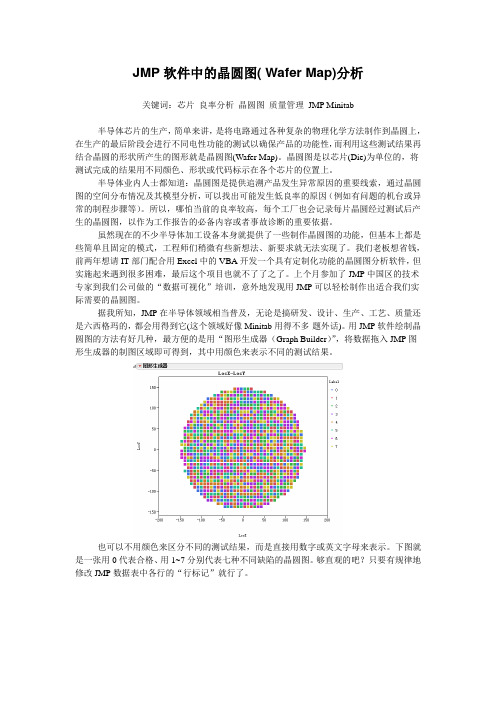

JMP软件中的晶圆图( Wafer Map)分析关键词:芯片良率分析晶圆图质量管理JMP Minitab半导体芯片的生产,简单来讲,是将电路通过各种复杂的物理化学方法制作到晶圆上,在生产的最后阶段会进行不同电性功能的测试以确保产品的功能性,而利用这些测试结果再结合晶圆的形状所产生的图形就是晶圆图(Wafer Map)。

晶圆图是以芯片(Die)为单位的,将测试完成的结果用不同颜色、形状或代码标示在各个芯片的位置上。

半导体业内人士都知道:晶圆图是提供追溯产品发生异常原因的重要线索,通过晶圆图的空间分布情况及其模型分析,可以找出可能发生低良率的原因(例如有问题的机台或异常的制程步骤等)。

所以,哪怕当前的良率较高,每个工厂也会记录每片晶圆经过测试后产生的晶圆图,以作为工作报告的必备内容或者事故诊断的重要依据。

虽然现在的不少半导体加工设备本身就提供了一些制作晶圆图的功能,但基本上都是些简单且固定的模式,工程师们稍微有些新想法、新要求就无法实现了。

我们老板想省钱,前两年想请IT部门配合用Excel中的VBA开发一个具有定制化功能的晶圆图分析软件,但实施起来遇到很多困难,最后这个项目也就不了了之了。

上个月参加了JMP中国区的技术专家到我们公司做的“数据可视化”培训,意外地发现用JMP可以轻松制作出适合我们实际需要的晶圆图。

据我所知,JMP在半导体领域相当普及,无论是搞研发、设计、生产、工艺、质量还是六西格玛的,都会用得到它(这个领域好像Minitab用得不多-题外话)。

用JMP软件绘制晶圆图的方法有好几种,最方便的是用“图形生成器(Graph Builder)”,将数据拖入JMP图形生成器的制图区域即可得到,其中用颜色来表示不同的测试结果。

也可以不用颜色来区分不同的测试结果,而是直接用数字或英文字母来表示。

下图就是一张用0代表合格、用1~7分别代表七种不同缺陷的晶圆图。

够直观的吧?只要有规律地修改JMP数据表中各行的“行标记”就行了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LUTION▲嵌入式技术

飞思卡尔运用耶江P提升半导体良率SASlnstituteItic

飞思卡尔(Freescale)是全球著名的微控制器、射频半导体、模块与混合信号电路、软件技术及相关管理解决方案的供应商,其前身是拥有50多年历史的摩托罗拉半导体部门,其主要客户来自于汽车、消费电子、工业品、网络和无线应用市场的10,000多家企业。

公司拥有专利5,900多项,2007年的营业收入达N57亿美元,在全球30多个国家拥有24,000多名员工,其中包括中国天津的组装测试厂和北京、上海、苏州的三个设计、研发和支持中心。

六西格玛统计分析软件JMP是SAS公司的卓越绩效统计发现引擎,应用范围包括业务可视化、数据发现、六西格玛和持续改进(可视化六西格玛、质量管理、流程优化)、研发及创新、试验设计DOE等,客户遍及半导体、机械、化工、制药、金融、汽车、钢铁、航空航天等各个行业。

半导体产品的典型宏观流程图

飞思卡尔所在的半导体设计和制造

行业是一个非常特殊的高科技行业,工

艺流程十分复杂。

其间,来白化学、光

学、机械、电子和空间等多方面的因素

交织在一起,共同影响着最终产品的质

量和流程的效率(参见下图)。

而且,

半导体对加工精度的要求也非常苛刻,

这里点,从我们常见的电路板的复杂连

线上就可以体会到,半导体产品的测量

尺度不是以毫米为单位的,而是以纳米

为单位的(1毫米=1000000纳米)!所

幸的是,在半导体的生产过程中,成千

上万的测量数据被同步记录下来,为我

们的分析和工艺改进工作奠定了基础。

对每一家半导体企业而言,要想在

这个竞争日趋白热化的市场上生存并发

展,必须提高并控制产品的良率Yield,

而且要“用最快的速度做出最准确的改

善反应”。

因为半导体产品的价值很大

程度上取决于研发生产过程中所采用的

技术,而这些技术的价值往往随着时间

的推移而迅速贬值。

因此,一旦出现良

率下降的质量问题,谁能够最快地发现

关键因素并加以纠正,谁就能最快地转

危为安,最早地向市场大规模供应成熟

产品,获得最大的利润。

飞思卡尔在“良率提升Yield

Enhancement”领域拥有丰富的成功经

验,主要工作可以概括为三步曲:

1获取数据

2分析数据

3展示数据

“获取数据”的概念不难理解,

很多半导体企业在早期的信息化建设、

ERP项目、MES项目中都已初获成功,

为获取数据创建了良好的条件。

难就难

在后面的“分析数据”和“展示数据”

上,国内的一些半导体企业在这方面明

显缺乏经验。

飞思卡尔在这方面使用的工具是专

业统计分析软件JMP。

半导体行业的工

程师整天要和数据打交道,飞思卡尔内

部的几位既懂专业又懂统计的资深专家

发挥JMP使用简单、功能强大、可视化

效果好的优势,让JMP成为了飞思卡尔

良率提升的关键武器之一。

例如,飞思卡尔的工程十分用半导

体行业中常见的晶圆图WaferPlot来初步

分析晶圆的缺陷,以下两个图形就是运

用JMP软件绘制而成的。

第一张图显示

的是单个晶圆的质量特征,并配有帕累

托图Pareto

PlotJ畏示芯片的良率状况和各万方数据

嵌入式技术

基于JMP软件的单个晶圆图分析

种缺陷出现的频次。

第二张图则是从整体层面显示一个批次Lot产品的质量特征(一般来说,飞思卡尔规定25个晶圆组成1个批次)。

在当前的经济形势和行业条件下,企业不允许工程师们花费大量的时间来进行数据分析和展示,而是要求工程师们将更多的精力放在实际的业务改进中。

飞思卡尔巧妙地利用JMP提供的自动编程语言JSL(JMPScriptLaIlguage)为大规模重复性分析、绘图

基于JMP软件的5X5晶圆图

工作以及成熟的

建模工作开发出

各种JMP脚本程

序,从很大程度

上实现了“分析

自动化”,使得

良率改善人员只

需要要点击一两

个按钮,就可以完

成通过菜单操作

需要几个小时才

能完成的分析工

作,大大节省了

数据分析、问题发现以及解决方案形

成的时间。

而且,飞思卡尔还将这些JMP脚本

文件当成企业知识管理的重要内容,将

其统一整合到内部网络上供全球的相关

人员分享使用(如下图所示),并为每

一个文件编写了使用说明,以方便大家

的使用并帮助进一步提高了企业的工作

效率。

JMP4半随着飞思卡尔走过了风风雨

雨的近20年,一起走出失败的阴影,

共同分享成功的喜

悦。

飞思卡尔良率

管理部的负责人这

样认为:JMP软件现

在已经推出的新版

JMP8中,数据可视

化的功能又有了长

足的发展。

这正好

和半导体良率提升

中简单、直观、快

速的原则相吻合,

新型泡泡图、图形

生成器等JMP特色平

台已逐渐成为具有

飞思卡尔特色的良

率提升方法论中的

重要工具。

Ea凼

解决方案

创新科技在2009籽亿高科

峰会上与中国的高科技公

司建立战略伙伴关系

新加坡一2009年12月1日一数码娱乐

产品的全球领导厂商创新科技(Creative

TechnologyLid)和业界领先的媒体处理

器和平台制造商、创新科技全属子公

司ZiiLABS于12月1日一2日在中国深圳福

田区香格里拉酒店举行2009籽亿高科峰

会,他们将与中国高科技公司进行合

作,建立战略伙伴关系。

参加2009籽亿高科峰会的合作伙伴

将有机会看到一系列为OEM量身打造、

以Zii技术为核心的产品,这些产品均采

用ziiLABSI均ZM¥一05和ZMS-08富媒体应

用处理器。

每种芯片均能满足独特的市

场需求-ZM8—05是为大众消费市场开发

的节能型芯片,而ZMS-08贝4为掌上型富

媒体设备而设计。

届时参展的以zii为核心的产品包

括支持Pl&szm&和Android的双操作系统概

念手机、触摸式视频会议桌面设备、网

盒、560。

多视角摄像系统、PCIExpress

加置卡(为笔记本电脑增加高清视频通

讯编码功能,实现高品质视频会议)、

能媲美一些世界顶级钢琴音质的袖珍式

音乐合成器,和世界最小,只有信用卡

大小的的蓝光品质媒体播放机(基于

ZMS-08芯片)。

双操作系统ziiTRINITY概念手机是

众多以zii为核心的产品的一个亮点,这

是一款经zij优化的Android和Plaszma智慧

手机。

该概念手机允许开发者使用熟悉

的Android操作系统,但具备更优异的效

能。

利用ZMS一05和ZMS一08富媒体处理器

上的干细胞计算技术,提供高速流畅的

3D图形与高清视频播放能力。

届时也演示ZiiLife整套内容和网络

内增值服务的高端内容服务功能。

ZiiLife是内容提供商和OEM合作伙伴的理

想之选,使他们有潜力开创未来的娱乐

和教育方案。

因幽万方数据。