FTU硬件详细设计说明书

FTU说明书v1.3

A TFTU低压监测保护装置ATFTU微机低压监测保护装置技术说明书使用说明书武汉奥特科技有限公司Wuhan Auto Technology Co.,Ltd.目录ATFTU数字式保护测控装置 (3)一、概述 (3)1.1装置主要特点 (3)1.2保护功能的主要配置: (3)二、技术参数 (4)2.1 额定参数 (4)2.2 主要技术性能 (5)2.3 绝缘性能 (5)2.4 电磁兼容性能 (6)2.5 机械性能 (6)2.6 环境条件 (7)三、工作原理说明 (7)3.1 机箱结构 (7)3.2 交流插件 (7)3.3 CPU插件 (7)3.4 电源插件 (9)3.5 逻辑及跳闸插件 (9)四、保护原理说明 (11)4.1过电流元件 (11)4.2 过电压元件 (11)4.3欠压保护元件 (12)4.4失压保护元件 (13)五、装置的整定及事件信息 (14)5.1 整定值清单及说明 (14)5.2 事件信息一览表 (15)附录1:面板图 (20)附录2: 背板端子图 (21)ATFTU数字式保护测控装置一、概述ATFTU数字式电容器保护装置是以电流电压保护及不平衡电压保护为基本配置的成套电容器保护装置,适用于110kV及以下电压等级的电容器组,可在开关柜就地安装,也可组屏安装于控制室。

应用范围覆盖电力、水利、交通、石油、化工、煤炭、冶金、铁路等行业。

1.1装置主要特点☆装置采用双CPU结构,保护模块选用高性能32位CPU,人机对话模块选用专用CPU,使产品的稳定性和运算速度得到充分保证☆保护模块采用14位的A/D转换器,测量模块采用专用的A/D转换器、精度高达24位,各项测量计算指标轻松达到要求☆配置大容量的RAM和Flash Memory,可记录8至50个录波报告,记录的事件数不少于1000条,具有掉电保持功能☆保护功能由图形化的逻辑编程实现,功能的变化不用修改系统程序,使保护实现原理透明、可靠,装置的灵活性、稳定性、可靠性大大加强☆配置专用的调试软件,可以进行逻辑灌装也可联接至计算机进行调试和分析☆可独立整定32套保护定值,定值切换安全方便☆高精度的时钟芯片,并配置有GPS硬件对时电路,便于全系统时钟同步☆配备高速以太网络通信接口,并集成了IEC870-5-103标准通信规约☆精心的电气设计,整机无可调节器件,实现了免调试概念设计☆高等级、高品质保证的元器件选用☆强弱电前后布置、独立模块设计,使装置具有优异的抗干扰性能,组屏或安装于开关柜时不需其它抗干扰模件☆完善的自诊断功能☆防潮、防尘、抗振动的机箱设计1.2保护功能的主要配置:●二段式相间过流保护●二段式过压保护●二段式欠压保护● 失压保护 测控功能配置● 11路遥信开入采集● 装置失电告警,装置事故信号,装置告警信号 ● 断路器遥控分合,接地选跳● 模拟量遥测:Ia 1、Ib 1、Ic 1、Ua 1、Ub 1、Uc 1、Ia 2、Ib 2、Ic 2、Ua 2、Ub 2、Uc 2、P 1、Q 1、COS θ1、P 2、Q 2、COS θ2、U AB1、U BC1、U CA1、U AB2、U BC2、U CA2 ● 2路脉冲输入 ● 1路GPS 对时二、技术参数2.1 额定参数2.1.1额定直流电压: 220V 或110V (订货注明) 2.1.2 额定交流数据:a) 相电压 3/380 Vb) 交流电流 75A (如需更改订货注明) c) 额定频率50Hz2.1.3 功率消耗:a) 直流回路正常工作时:不大于15W 动作时: 不大于25W b) 交流电压回路 每相不大于0.5VAc) 交流电流回路 额定电流为75A 时:每相不大于1VA 2.1.4 状态量电平:CPU 及通信接口模件的输入状态量电平 24V (18 V ~30V ) GPS 对时脉冲输入电平 24V (18 V ~30V ) CPU 输出状态量(光耦输出)允许电平 24V (18 V ~30V )2.2 主要技术性能2.2.1采样回路精确工作范围(10%误差)电压:0.4 V~120V电流:0.08In-20In2.2.2接点容量信号回路接点载流容量400VA信号回路接点断弧容量60VA2.2.3跳合闸电流本装置跳合闸电流采用自适应模式,无需选择。

FTU模块技术方案设计

FTU模块技术方案1技术方案1.1FTU模块总体方案FTU模块采集三相电流、线电压、频率、有功功率、无功功率、零序电流和零序电压,采用配电线损采集模块实现计量功能。

1.2FTU模块基本组成一二次融合FTU模块采用罩式装置,其重要组成部分为线损采集模块和航空插头接口,且航空插头接口包括:供电电源及线电压输入接口( 6芯,1个)、电流输入接口( 6芯防开路,1个)、控制信号、零序电压接口(14芯,1个)、以太网接口( 1个,备用)。

开关侧采用2根电缆、1个26 芯航空插头从开关本体引出零序电压、电流及控制信号,接入到FTU的航空插头;采用 2根电缆提供供电电源、线电压信号(采用电磁式 PT取电)。

1.3技术方案优缺点优点:罩式FTU模块体积小,防护等级高,能适应更为严酷的户外运行环境,使用寿命高;缺点:罩式FTU模块的小体积对内部线损模块、电源模块等重要组成部件要求更高,增大了生产工艺难度。

1.4与相关技术方案对比无对比技术方案。

2功能要求2.1计量功能要求(配套用户末端分界开关除外)FTU采用配电线损采集模块实现计量功能,包括:a)正反向有功电量计算和四象限无功电量计算及功率因数计算;b)计量数据冻结功能:包括日冻结数据,功率方向改变时的冻结数据;c)有功电量计算为0.5S级精度,无功电量计算为 2级,功率因数分辨率0.01 o2.2测量功能要求采集三相电流、线电压、频率、有功功率、无功功率、零序电流和零序电压。

(1)保护功能要求a)应满足Q/GDW-51《配电自动化终端子站功能规范》及《配电自动化终端技术规范》相关要求。

b)分段/联络断路器、分界断路器具备相间故障检测及跳闸功能、相间故障信息上传功能。

c)分段/联络断路器、分界断路器、分界负荷开关具备进出线接地故障的检测及跳闸功能;具备故障录波与通信上传功能,接地故障录波每周波80点以上。

(2)测量/计量/保护精度要求a)保护、测量、计量电压:外置PT线电压额定输入为100V,测量精度0.5 %;b)保护、测量、计量电流:三相额定电流输入为1A;保护W 3%测量精度为0.5级;计量精度为0.5S级;c)零序电流:20A/1A;测量精度< 0.5 % ;d)零序电压:(10kV/ V3)/(6.5V/3);测量精度 3P。

配电自动化远方控制终端(FTU)安装使用说明书浙江华仪电力

图 3 FTU 硬件结构 FTU 的硬件是以功能强大的 DSP 为核心,配备丰富的外围接口电路构成。原理结构框图 见图 3。 FTU 采用的 DSP 为 IT 公司 2004 年正式推出的 32 位高集成性能数字信号处理器。其工作 主频 150M,工作温度-40℃~125℃,内置看门狗及丰富的资源,极其适合工业控制领域的应用。 交流量变换隔离电路使用互感器对 11 路外接交流电流或电压进行隔离,并将隔离后的信 号转换为滤波放大电路及测频电路的输入驱动信号。共有 14 路通道的二阶低通滤波及放大电 路,其中 3 路用于实现对 3 路保护电流的低端值的精准测量。 10 路 DI、7 路 DO 电路(其中 DO1-DO4 为重载继电器,主要用于断路器跳合闸等重要出 口,DO5-DO7 为信号继电器, 用于报警等出口)用来实现对开入量的采集和监视,以及对开出 继电器的驱动和管理。开入开出由 CPLD 和 DSP 协调管理,DSP 直接管理启动继电器,用于控

3

一、 概述 配电自动化系统主要由主站系统、数据通讯系统和配电自动化终端三部分组成,配电自

动化终端是自动化系统与一次设备的接口。 配电自动化远方控制终端(FTU)是浙江华仪电力自动化有限公司研发的新一代数字继电

保护测控终端。 配电自动化远方终端在系统中主要实现的功能是采集就地的交流测量量(如电压、电流、

1) 采用高速工业级 DSP 的硬件平台技术,提高系统的高效性、快速性、高精度。

®

ZHEJIANG HUAYI ELECTRIC POWER AUTOMATION CO.,LTD

配电自动化远方控制终端(FTU)安装使用说明书

4

2)核心单元为 HYP400 微机可编程保护测控装置,采用大容量、资源冗余设计,可用于 不同主接线方式。保护功能也支持多种故障隔离运行模式。如:电流-时间型、电压-时间型、 电流电压-时间型、用户分界开关运行模式。

FTU的硬件结构设计和软件设计

摘要随着对配电网自动化的要求的提高,作为其重要设备的FTU的性能也应提高。

针对当今市面上的终端设备的不足,本文尝试给出一种功能强大、性价比高、可推广性强的FTU装置。

本设计采用当前流行的嵌入式技术和数字信号处理技术来完成核心处理器,采用以ARM9与TMS320LF2407A有机结合的双CPU构架,这种设计稳定、高效、节能,优于以往FTU的核心处理器的设计。

本设计采用当前非常先进以太网通信方式,较以往FTU的通信方式网络化更强,信息传输能力更为强大。

本设计除了在核心处理器和通信方式上有明显优势外,在其他部分亦有改进。

希望这种装置在相当长的时间内都保持优越性。

本文讲述了笔者对馈线自动化的理解,介绍了设计过程,给出了FTU的硬件结构设计和软件设计。

关键词:双CPU,嵌入式,AT91RM9200,TMS320LF2407A,以太网AbstrastAs requirements of the distribution network automation increasing, the major equipment , FTU performance, should also be improved. To the old terminal equipments’deficiencies, this paper tries to give a powerful, cost-effective, strong promotion of FTU device. This kind of FTU uses ARM9 and TMS320LF2407A organic combination of double CPU structure. It is high efficiency, energy saving, stability, better than the previous FTU core processor design. The current design using highly advanced Ethernet communication mode, compared to the previous FTU communication mode of network information transmission ability stronger, more powerful. This design in addition to the core processor and communication mode has obvious advantages,in the other part are improved.Hoping this FTU will be advanced for a long time in the future. This paper mainly introduces the FTU hardware structure and the main algorithm, and gives the hardware circuit.Key words:Double CPU,embedded,AT91RM9200,TMS320LF2407A,Ethernet目录1 绪论 (1)1.1 本课题的研究目的和意义 (1)1.2 本课题的主要研究内容(提纲) (2)1.3 文献综述(国内外研究情况及其发展) (3)1.4 拟解决的关键问题 (4)1.5 研究思路和方法 (5)1.6 本课题的进度安排 (5)2 系统设计及原理 (6)2.1 双CPU构架 (6)2.2 系统结构设计 (6)3 硬件设计 (8)3.1 处理器的设计 (8)3.2 模拟量输入电路的设计 (13)3.3 开关量输入/输出回路的设计 (16)3.4 频率测量电路的设计 (17)3.5 通信单元设计 (18)3.6 电源设计 (21)4 算法设计 (23)4.1 电网参数的计算 (23)4.2 故障判断算法 (24)4.3 FIR滤波算法 (27)5 软件设计 (30)5.1 主程序 (30)5.2 通信中断程序 (32)6 总结与展望 (34)6.1 总结 (34)6.2 展望 (35)参考文献 (36)致谢 (39)附录 (40)附录1 (40)附录2 (63)1 绪论1.1 本课题的研究目的和意义长期以来,我国配电网的建设未得到应有的重视,建设资金短缺,设备技术性能落后,事故频繁发生,严重影响了人民生活和经济建设的发展,随着电力的发展和电力市场的建立,配电网的薄弱环节显得越来越突出,形成了与电网建设不协调的局面。

带液晶显示的FTU 实验装置设计

透视Hot-Point PerspectiveDI G I T C W 热点项目编号:TB201904016作者简介: 吴 航,男,汉族,1994年生,江苏宿迁人,研究方向为智能电网信息工程。

韩 俊,男,汉族,1998年生,江苏南京人,研究方向为智能电网信息工程。

何 帅,男,汉族,1996年生,河南洛阳人,研究方向为智能电网信息工程。

王娅楠,女,汉族,1999年生,女,汉族,江苏泰州人,研究方向为智能电网信息工程。

程 亮,男,汉族,1998年生,安徽宣城人,研究方向为智能电网信息工程。

1 引言近些年随着我国配网自动化系统的建设,针对配网自动化系统的仿真培训及实验系统也得到了探索。

如文献[1]介绍了一种配网自动化仿真系统,该系统有模拟柜(三部分构成:配网一次设备模拟部分,模拟控制器部分及负荷模拟部分)、控制中心(控制中心由计算机、通讯控制器及其它计算机辅助设备构成。

软件由四部分构成:控制中心界面设计软件、系统运行情况演示软件、远程操作控制软件,线路仿真及计算软件)及显示部分构成。

该仿真系统为配电网自动化系统搭建了一个应用研究平台,目前,该系统能实现配电网自动化系统多种方案的仿真。

系统能演示配电网的正常运行方式和故障运行方式及故障隔离过程。

文献[2]介绍了一种采用分层式体系结构实现对实际城区 10kV 配电网自动化的计算机模拟。

根据现实的配网系统,整个模拟系统分为配电网主站层、终端层和一次设备层 3个层次。

通过通信系统将 3个图3 配电模拟培训系统配置层次统一起来,可以实现配电网自动化系统各种工况和故障的模拟实验,让学习者充分了解现代化的配网自动化系统,了解配电网运行规律和电网调度运行技术,充分掌握电力系统远动技术。

目前配网自动化系统的仿真培训系统有纯软件仿真和数字物理混合仿真系统两种,本文介绍一个配网自动化实验系统,也是兼具软件设计和硬件设计的结构。

2 配网自动化实验系统简介本文设计的配网自动化试验系统以0.4kV 电压等级模拟10kV 配网,结构上分为主站层和终端层2层设计。

配电自动化馈线终端(FTU)技术规范

配电自动化馈线终端(FTU)技术规范目录1 规范性引用文件 (1)2 技术要求 (1)3 标准技术参数 (10)4 环境条件表 (12)5 试验 (13)附录A馈线终端无线通信安装位置、航插尺寸定义(参考性附录) (14)附录B 馈线终端接口定义(规范性附录) (28)配电自动化馈线终端(FTU)技术规范1 规范性引用文件下列文件对于本文件的应用是必不可少的。

凡是注日期的引用文件,仅注日期的版本适用于本文件。

凡是不注日期的引用文件,其最新版本适用于本文件。

GB/T 17626.1 电磁兼容试验和测量技术抗扰度试验总论GB/T 17626.2 静电放电抗扰度试验GB/T 17626.3 射频电磁场辐射抗扰度试验GB/T 17626.4 浪涌(冲击)抗扰度试验GB/T 17626.5 电快速瞬变脉冲群抗扰度试验GB/T 17626.8 工频磁场的抗扰度试验GB/T 17626.10 阻尼振荡磁场的抗扰度试验GB/T 17626.11 电压暂降、短时中断和电压变化抗扰度试验GB/T 15153.1 远动设备及系统第2部分:工作条件第1篇:电源和电磁兼容兼容性GB/T 11022 高压开关设备和控制设备标准的共用技术要求GB/T 14285 继电保护和安全自动装置技术规程GB/T 4208 外壳防护等级(IP)GB/T 13729 远动终端设备GB/T 5096 电子设备用机电件基本试验规程及测量方法GB/T 19520 电子设备机械结构GB 7251.5 低压成套开关设备和控制设备第五部分:对户外公共场所的成套设备—动力配电网用电缆分线箱(CDCs)的特殊要求DL/T 637-1997 阀控式密封铅酸蓄电池订货技术条件DL/T 721 配电网自动化系统远方终端DL/T 634.5101 远动设备及系统第5-101部分:传输规约基本远动任务配套标准DL/T 634.5104 远动设备及系统第5-104部分:传输规约采用标准传输协议子集的IEC60870-5-101网络访问DL/T 814 配电自动化系统功能规范Q/GDW 382 配电自动化技术导则Q/GDW 513 配电自动化主站系统功能规范Q/GDW 514 配电自动化终端/子站功能规范Q/GDW 625 配电自动化建设与改造标准化设计技术规定2技术要求2.1概述馈线终端的结构形式可分为箱式馈线终端和罩式馈线终端。

FTU模块技术设计方案

FTU模块技术设计方案FTU(Fault Terminal Unit)是一种用于电力系统中的终端设备,用于监测、控制和保护电力设备。

本文将介绍FTU模块的技术设计方案。

1.引言2.硬件设计2.1 主控芯片:选择一款性能稳定、功耗低的ARM Cortex-M系列芯片作为主控芯片。

该芯片具有较高的计算能力和丰富的外设接口,可以满足FTU模块的数据处理和通信需求。

2.2输入输出模块:设计多路输入输出信号的输入输出模块,可以接入各种类型的传感器和执行器。

同时,为了提高FTU模块的稳定性和可靠性,该模块应支持冗余设计,以防单个输入输出模块出现故障。

2.3通信模块:选择高可靠性的通信模块,如以太网和4G通信模块。

以太网用于与电力系统SCADA系统进行数据传输,而4G通信模块用于远程监控和控制。

2.4电源模块:设计高效稳定的电源模块,以满足FTU模块的供电需求。

这包括使用高质量的电源稳压芯片和电源滤波器,以提供稳定和清洁的供电。

3.软件设计3.1实时操作系统(RTOS):选择适合嵌入式系统的实时操作系统,以管理FTU模块的多任务和中断处理。

RTOS可以提供任务调度、内存管理和设备驱动等功能。

3.2驱动程序:编写驱动程序来管理FTU模块的不同硬件组件,包括输入输出模块、通信模块和电源模块。

驱动程序应提供接口和API供上层应用程序调用。

3.3数据处理程序:编写数据处理程序来处理从传感器到FTU模块的各种数据。

这些程序应实现数据解析、转换和校验功能,确保数据的可靠性和完整性。

3.5故障保护算法:设计故障保护算法来监测电力设备的状态并触发相应的保护动作。

这些算法应根据实际需求进行设计,并能及时响应和处理系统故障。

4.总结本文介绍了FTU模块的技术设计方案。

通过选择适当的硬件和软件组件,可以设计出稳定可靠的FTU模块,用于监测、控制和保护电力设备。

在实际应用中,还需考虑FTU模块的可扩展性、可靠性和安全性等方面的需求。

配电网设备一二次融合FTU说明书(适用于断路器负荷开关分段联络分界)

DAF-810一二次融合FTU(箱式/断路器/负荷开关/分段联络分界)技术使用说明书V2.8s特别提示尊敬的客户:衷心感谢您选用本产品!我们承诺在保证产品性能及品质的同时,将竭诚为您提供完善的技术服务。

为了让您更好地使用本产品,请在设备到货后仔细阅读以下提示内容,并在安装前阅读说明书全文。

工程供货配电终端,现场接线时,请查看随机的《外部接线图》和《航插电缆定义图》图纸,具体配置以随机图纸为准。

在装置通电运行之前,应仔细检查接线是否正确。

装置接地线柱应可靠地经多股铜导线接到接地网上去,以避免装置外壳带电对人身造成伤害,并使装置的抗浪涌干扰电路正常的发挥作用。

智昊不断地对其产品进行改进完善,由于技术的不断进步及国网产品标准的不断更新,说明书与实际产品可能存在差异。

欢迎您对本公司的产品提出宝贵意见。

◆包装箱有无损坏;◆设备外表有无明显的破裂或损坏;◆产品铭牌上的设备名称、型号是否与订货相符;◆装箱清单所列物品、随机文件是否齐全及与实物相符。

目录1 产品概述 (1)1.1产品特点 (1)1.2技术参数 (3)1.3环境条件 (4)2主要功能 (5)3 DAF-810主控单元 (7)3.1功能板概述 (7)3.2主控单元外形尺寸 (8)3.3主控单元前面板布局 (8)3.4主控单元接线端子 (9)4 终端操作面板 (12)5 终端操作使用说明 (13)5.1人机界面 (13)5.1.1 工况显示 (13)5.1.2 LCD主菜单界面 (14)5.1.3 保护投退 (15)5.1.4 保护定值 (16)5.1.5 时间设置 (17)5.1.6设备参数 (17)5.1.7通信参数 (20)5.1.8密码设置 (21)5.1.9 定值浏览 (21)5.1.10 信息记录 (21)5.1.11 遥信信息 (21)5.1.12 其它操作 (21)5.2终端的分、合闸操作 (21)5.2.1就地分合闸 (21)5.2.2手持遥控器分合闸 (22)5.3终端的保护指示与复归 (22)5.4电源模块概述 (22)5.4.1电源模块端子 (23)5.4.2 使用说明 (23)5.5配电线损采集模块 (24)6 终端航插接口定义 (24)7终端外形结构 (26)8 安装接线 (27)9 终端调试 (28)9.1调试所需设备 (28)9.2终端与开关柜本地联调 (28)9.2.1通电前后检查 (28)9.2.2参数设置 (28)9.2.3三遥功能调试 (29)9.3终端与主站联调 (31)9.3.1确认终端相关通信参数设置 (31)9.3.2主站联调 (31)10 投运说明及注意事项 (31)1 产品概述DAF-810配电自动化系统馈线远方终端是针对柱上开关研制的配网自动化产品,是根据配电设备一二次融合的最新发展需求,汲取计算机技术、数字信号处理技术、电网故障检测技术研究的新成果研制的新型馈线远方终端设备(FTU)。

ZX8650馈线自动化终端装置(FTU)使用说明书

在所规定的标称值范围内,线性误差不超过±0.2%;

3.2.3

故障电流的输入范围为10IN(IN为额定输入电流)线性范围;

故障电流的总误差应不大于±3%。

3.2.4

输入回路采用光电隔离

接点电压:+24V

SOE分辨率小于2毫秒

事故时遥性变位传送时间:小于1秒

软件防抖动时间0-60000毫秒可设

接口方式:无源/有源

6.装置运行时不可随意按动装置的任何按钮.

7.系统的配置参数不能随意更改或变换,必须由厂家指定的专业人员进行更换,更换后应进行严格的登记.

8.装置安装之前应检查机箱内的所有部件的紧固程度.

9.装置安装完毕后应认真检查接口连接是否正确, 遥控继电器接点与一次设备的对应关系是否正确,尤其是电压回路不能短路,电流回路不能开路.

提供远程和本地维护接口,使得运行人员可在本地或主站等远方完成对其维护。

采用了单片机的DSP高速采样技术,实现了对馈线故障识别、三遥监控功能。

支持电话拨号、无线、光纤、以太网、RS232/485等多种通信方式。

可接入其他站端设备(如TTU),并将数据转发。

具有设备自诊断和自恢复功能。

谐波分析功能。

具备双电源自动无缝切换供电功能。

交流电压电流采样精度:0.2级/0.5级

直流电压、频率采样精度:0.2级

有功功率、无功功率、功率因数采样精度:0.5级/1.0级

在所规定的标称值范围内,交流工频电量每一电流输入回路的功率消耗应不大于0.25VA,每一电压输入回路的功率消耗应不大于0.25VA;

在所规定的标称值范围内,线性误差不超过±0.5%

3.4.6

在正常工作状态下,将终端置于与系统电源电压相同频率的随时间正弦变化的、强度为100A/m的均匀磁场的线圈中心,工作正常。

配电网设备一二次融合FTU说明书(适用于断路器负荷开关分段联络分界)

DAF-810一二次融合FTU(箱式/断路器/负荷开关/分段联络分界)技术使用说明书V2.8s特别提示尊敬的客户:衷心感谢您选用本产品!我们承诺在保证产品性能及品质的同时,将竭诚为您提供完善的技术服务。

为了让您更好地使用本产品,请在设备到货后仔细阅读以下提示内容,并在安装前阅读说明书全文。

工程供货配电终端,现场接线时,请查看随机的《外部接线图》和《航插电缆定义图》图纸,具体配置以随机图纸为准。

在装置通电运行之前,应仔细检查接线是否正确。

装置接地线柱应可靠地经多股铜导线接到接地网上去,以避免装置外壳带电对人身造成伤害,并使装置的抗浪涌干扰电路正常的发挥作用。

智昊不断地对其产品进行改进完善,由于技术的不断进步及国网产品标准的不断更新,说明书与实际产品可能存在差异。

欢迎您对本公司的产品提出宝贵意见。

◆包装箱有无损坏;◆设备外表有无明显的破裂或损坏;◆产品铭牌上的设备名称、型号是否与订货相符;◆装箱清单所列物品、随机文件是否齐全及与实物相符。

目录1 产品概述 (1)1.1产品特点 (1)1.2技术参数 (3)1.3环境条件 (4)2主要功能 (5)3 DAF-810主控单元 (7)3.1功能板概述 (7)3.2主控单元外形尺寸 (8)3.3主控单元前面板布局 (8)3.4主控单元接线端子 (9)4 终端操作面板 (12)5 终端操作使用说明 (13)5.1人机界面 (13)5.1.1 工况显示 (13)5.1.2 LCD主菜单界面 (14)5.1.3 保护投退 (15)5.1.4 保护定值 (16)5.1.5 时间设置 (17)5.1.6设备参数 (17)5.1.7通信参数 (20)5.1.8密码设置 (21)5.1.9 定值浏览 (21)5.1.10 信息记录 (21)5.1.11 遥信信息 (21)5.1.12 其它操作 (21)5.2终端的分、合闸操作 (21)5.2.1就地分合闸 (21)5.2.2手持遥控器分合闸 (22)5.3终端的保护指示与复归 (22)5.4电源模块概述 (22)5.4.1电源模块端子 (23)5.4.2 使用说明 (23)5.5配电线损采集模块 (24)6 终端航插接口定义 (24)7终端外形结构 (26)8 安装接线 (27)9 终端调试 (28)9.1调试所需设备 (28)9.2终端与开关柜本地联调 (28)9.2.1通电前后检查 (28)9.2.2参数设置 (28)9.2.3三遥功能调试 (29)9.3终端与主站联调 (31)9.3.1确认终端相关通信参数设置 (31)9.3.2主站联调 (31)10 投运说明及注意事项 (31)1 产品概述DAF-810配电自动化系统馈线远方终端是针对柱上开关研制的配网自动化产品,是根据配电设备一二次融合的最新发展需求,汲取计算机技术、数字信号处理技术、电网故障检测技术研究的新成果研制的新型馈线远方终端设备(FTU)。

(完整版)fTU使用说明书

一、概述GEA-PFT2C2W型FTU是专门为配电系统设计的馈线自动化产品,,又名柱上开关智能监控单元.它是一种集测量。

、保护、监控为一体的综合型自动监控装置。

该产品设计时吸收微机保护装置及其他类似产品的优点,综合考虑了配网的现状,需求以及将来扩充的发展要求, 是新一带实现配网自动化的重要设备。

二、系统功能及构成(1)功能特点1)交流采样:能够测量三相电压、三相电流及零序电流,计算出有功功率、无功功率.2)故障状态检测:测量记录故障电流及方向、故障发生时间,能够满足故障分析、故障定位及隔离的需要。

3)直流采样:能够测量两路直流量。

4)具有速断、时限过流保护功能.5)遥控返校与闭锁功能,保证不误动.6)通信规约:支持IEC870—5—101、SC1801,向DNP3.0、MODBUS等通信规约扩展.7)通讯接口:RS232/485.8)通信信道:可支持载波、无线扩频、无线数传电台、光纤、电话线等多种通讯形式,由用户任选.9)设有手动控制分/合开关,便于设备的检查与调试.10)具有双电源供电回路,并装有备用电池,即使在开关两侧均失电的情况下,系统仍可运行不少于8个小时,并可进行开关的控制。

.11)硬件系统采用工业级芯片,个别芯片采用军品级,并对元件进行了老化筛选,保证系统具有宽广的工作温度范围及抗恶劣环境的能力。

(12)输入回路、通讯线以及整机的抗干扰、抗雷电设计,保证装置能够在恶劣环境下稳定正常的运行。

(13)简洁模块化的接线与结构,大大方便了运行人员的巡视和检修。

(14)系统高可靠性①智能单元可靠性智能单元是FTU系统的核心,从硬件和软件两个方面确保了其高可靠性指标的实现。

在硬件方面,元器件全部选用工业级以上产品(工作温度—40℃~85℃),部分关键元器件选用了军级产品(工作温度—55℃~125℃),且充分考虑了元器件的电参数使用裕度;电源、输入/输出通道以及通信接口使用DC/DC电源模块和光电耦合器件实现了与中央处理单元的电磁/光电隔离;在PCB板布线方面也充分考虑了提高系统抗干扰能力.从设计角度采取的以上措施辅之以严格的装配、调试工艺,确保了智能单元具有较高的综合质量指标。

fTU使用说明书

fTU使用说明书fTU使用说明书1.简介fTU是一款功能强大的软件工具,适用于各种场景和需求。

本文档将详细介绍fTU的安装、配置和使用方法,以帮助用户充分发挥其潜力。

2.安装2.1 系统要求- 操作系统:Windows 10或更高版本- 内存:至少8GB- 存储空间:至少100MB的可用空间2.2 和安装fTU- 登录fTU官方网站()。

- 在主页上找到页面,在其中选择适合您操作系统的版本。

- 完成后,运行安装程序,并按照提示完成安装过程。

3.配置3.1 账户设置- 打开fTU软件,“设置”。

- 在设置选项卡中,选择“账户”。

- 输入您的用户名和密码,并“保存”以应用更改。

3.2 数据存储设置- 在fTU软件中,选择“设置”。

- 选择“数据存储”选项卡。

- 选择您要存储数据的文件夹路径,并“保存”。

4.主要功能4.1 数据导入与导出- “导入”按钮,选择要导入的数据文件,并按照提示完成导入过程。

- “导出”按钮,选择导出的数据类型和文件保存路径,并按照提示完成导出过程。

4.2 数据分析与统计- 在fTU软件中,选择“分析”选项卡。

- 选择要分析的数据类型和分析方法,并按照提示完成分析过程。

- 在分析结果中查看统计数据和图表。

4.3 报告- 在fTU软件中,选择“报告”选项卡。

- 选择报告的数据类型和报告样式,并按照提示完成报告过程。

- 在报告预览中查看的报告,并保存为PDF或其他格式。

5.附件本文档没有涉及到具体的附件。

6.法律名词及注释6.1 用户协议- 用户协议是用户和软件提供方之间达成的法律协议,规定了双方的权利和义务。

用户在使用fTU软件前需要同意并遵守用户协议。

6.2 数据隐私- 数据隐私是指用户的个人数据和机密信息在使用fTU软件过程中的保护。

fTU软件承诺对用户数据进行隐私保护,不向第三方泄露用户信息。

6.3 著作权- 著作权是指作者对其创作作品的独占权利。

fTU软件及其相关文档受版权保护,用户在使用fTU软件时需遵守相关著作权法律法规。

GKEC-600F配电自动化系统馈线远方终端(FTU)说明书新

青岛高科电子通信有限公司

1

目录

一、概述...............................................................................................................................4 二、主要性能特点:...........................................................................................................4 三、引用标准.......................................................................................................................5 四、主要技术指标...............................................................................................................6 五、主要功能.......................................................................................................................7 六、硬件结构.......................................................................................................................9 七、显示操作.....................................................................................................................12 八、端子图.........................................................................................................................17

ftu说明书

POWERTHUNDER-FTU-1控制器使用说明书北京中电迅雷通讯技术有限公司1. 概述POWERTHUNDER-FTU-1型配电控制器是配合我国配电领域的实际需求的新一代配电控制器。

能够与各种负荷开关、断路器、重合器、电动刀闸配合使用,完成配电网的保护、通信、故障检测隔离、测量等功能。

装置采用统一整体设计理念,各功能的选择可以灵活设置,操作简单实用,产品功能集成度高,整一化强。

POWERTHUNDER-FTU-1配电线路开关控制器可以实时监测配电系统的运行,通过GPRS/GSM通信,可以将整个配电进行数据采集并将其线路状态数据在后台调度中心实时显示,为配电网监控和调度提供技术手段,并实现遥控功能。

同时,主站系统为故障定位、供电恢复提供技术支持。

并具有前后控制器配合实用,实现馈线自动化功能。

馈线自动化功能主要是完成故障定位、隔离和非故障区域恢复供电。

有以下几种方式实现:以GPRS或其它高速通讯网络支持,集中采集现场开关控制器的数据,在后台电子地图进行网络拓扑,根据开关控制范围进行故障区域定位,发送遥控命令使离故障最近的开关分闸,从而隔离故障,最后将联络开关合闸,实现非故障区域恢复供电,这种方法避免了多次分合闸操作而导致的对系统多次冲击,一次即可隔离成功,但对通信的依赖较大,需要比较坚强的通信网络支撑。

第二种是完全依赖高速通讯网络在各个开关控制器之间完成双向通讯,构成“纵联差动”保护方式,这种方式只对故障区域开关进行“试合”来隔离故障区域;但是这种方式通讯成本较高。

另外一种是不依赖通讯,通过设置开关控制器的保护参数,根据“电流-电压”或“电流-时间”保护方式,各个开关通过1-3次重合闸,完成隔离故障区域,最后联络开关合闸,恢复非故障区域供电,这种方式不依赖通讯,完全自主完成故障隔离和网络重构,所做工作只是事先按需要配置好开关控制器的参数即可。

因为大部分线路故障发生在用户侧或线路分支侧,所以另外一种简单方式是分支线路或用户线路出现故障,分支开关优先于出线开关分闸,直接隔离故障段,同时上报故障信息。

(完整word版)配电自动化馈线终端(FTU)技术规范

223.2“三遥”FTU功能要求

a)满足2.4.1基本功能要求。

b)具备为开关动作提供配套电源的能力,满足控制开关分合闸,数据远传及远方控制功能。

c)具备就地/远方切换开关和控制出口硬压板,支持控制出口软压板功能;

d)具备双路供电电源输入和自动无缝切换功能。

d)抗浪涌干扰的要求

按GB/T 15153.1中的有关规定执行。

在施加如表5规定的浪涌干扰电压和1.2/50卩s波形的情况下,设备应能正常工作,其性能指 标符合基本性能的要求。

表5高频干扰、快速瞬变和浪涌试验的主要参数

试验项目

级别

共模试验值(*)

试验回路

高频干扰

3

2.5kVP

信号、控制回路和电源回路

凡是不注日期的引用文件,其最新版本适用于本文件。

GB/T 17626.1

电磁兼容试验和测量技术抗扰度试验总论

GB/T 17626.2

静电放电抗扰度试验

GB/T 17626.3

射频电磁场辐射抗扰度试验

GB/T 17626.4

浪涌(冲击)抗扰度试验

GB/T 17626Leabharlann 5电快速瞬变脉冲群抗扰度试验

GB/T 17626.8

d)无线通信模块与SIM卡的接口应符合GSM11.11的要求,与SIM卡交互数据应符合GSM11.14要 求。

e)无线通信模块支持端口数据监视功能,具备网络中断自动重连功能。

f)无线通信模块应支持SMS管理功能,可通过SMS支持关键参数设置、状态查询、故障诊断功能。

g)无线通信模块应支持本地维护功能,可通过本地维护接口支持调试、参数设置、状态查询和软 件升级。

智能馈线终端(FTU)说明书

1.4.技术参数

序号

项目

单位

参数

序号

项目

单位

参数

输 入 工 作 电 压 V A C 2 2 0 V/单路

4 遥 信 量 ≥3路 , 包 括 开 关 分 位 、 合 位 、 未 储能位

1 工作电源 频率

HZ 50~60

≥2路 , 包 括 分 闸 、 合 闸 输 出

二段过流保护(限时速断保护) A、B、C任 意 一 相 保 护 电 流 大 于1段 过 流 保 护

定 值 并 达到1段过流保护延时时间保护跳闸动作并 点亮一段过流保护指示灯和告警指示灯。

二段过流保护(限时速断保护) A、B、C任 意 一 相 保 护 电 流 大 于1段 过 流 保 护

定 值 并 达到1段过流保护延时时间保护跳闸动作并 点亮一段过流保护指示灯和告警指示灯。

博远智能科技

博远智能科技

设置前请输入密码 :000000

BY 08/14/15 20:35

确认变比

CT

8/100

修改

确认

博远智能科技

BY 08/14/15 20:35

三段过流 一次定值 2400.0A 二次定值 000.00A 延时时间 000.00S 功能状态 投入

博远智能科技

BY 08/14/15 20:35

BY 08/14/15 20:35

确认变比 零 序C T 8 /1 0 0

修改

确认

博远智能科技

一段过流 一次定值 2400.0A 二次定值 000.00A 延时时间 000.00S 功能状态 投入

博远智能科技

设置前请输入密码 :000000

FTU的整体设计与实现

FTU的整体设计与实现1F30主要用途及适用范围iES-F30馈线监控系统,是根据配电网自动化的最新发展需求,汲取计算机技术、数字信号处理技术、电网故障检测技术研究的新成果研制的新型馈线远方终端设备。

它的设计、制造和检验全面采用国际IEC标准和国家有关标准,适用于10KV馈线的监测和控制。

其主要功能包括:信息采集和处理、接受并执行遥控命令、时间纪录及上报、电源失压保护、通信、自诊断自恢复、当地调试、故障识别、隔离和恢复非故障段供电等。

结合一次开关,并与配电小区主站(或配电主站)组网配合,可以完成10KV馈线的故障诊断、故障区段隔离、网络重构和非故障区段的正常供电。

2F30组成iES-F30馈线监控系统采用综合单元通过CANBUS网络互连的分层、分布式网络结构,包括馈线终端单元、多功能电源模块、当地操作模块、通信管理模块、PC机维护软件等。

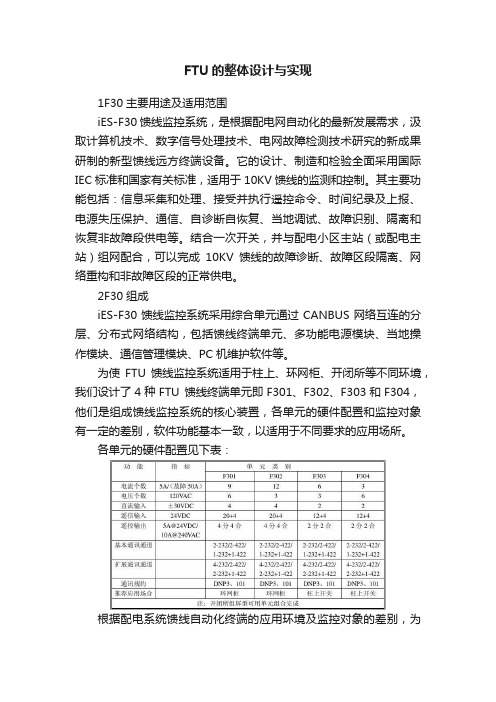

为使FTU馈线监控系统适用于柱上、环网柜、开闭所等不同环境,我们设计了4种FTU 馈线终端单元即F301、F302、F303和F304,他们是组成馈线监控系统的核心装置,各单元的硬件配置和监控对象有一定的差别,软件功能基本一致,以适用于不同要求的应用场所。

各单元的硬件配置见下表:根据配电系统馈线自动化终端的应用环境及监控对象的差别,为方便用户选配,我们针对不同应用场所推出了以下三种馈线监控系统:●iES-F30A开闭所馈线监控系统●iES-F30B环网柜馈线监控系统●iES-F30C柱上终端馈线监控系统各系统的组成如下表所示:如用户要求与推荐系统有一定差别,可使用馈线终端单元灵活组态,构成新的馈线监控系统,以满足实际要求。

3系统设计3.1 需求分析分析目前FTU的应用场合,主要有开闭所、环网柜、柱上馈线,其中柱上情况一般采集进线侧和出线侧的电压和电流,控制一路负荷开关的通断,采集开关的位置信号和气体压力,及储能闭锁信号等,其特点是工作在户外,风吹日晒,环境恶劣,且断电时要能够对开关进行分合操作。

ftu硬件方案

ftu硬件方案一、引言FTU(Fault Tolerant Unit)是电力系统中的一种重要保护设备,旨在提高电力系统的可靠性和稳定性。

本文将介绍一个全新的FTU硬件方案,以满足以下要求:可靠性高、灵活性强、成本低廉、易于维护。

二、硬件方案概述该FTU硬件方案由以下几个主要组成部分构成:1. 控制器控制器是FTU硬件方案的核心,采用高性能的嵌入式处理器,具有强大的计算和处理能力。

控制器通过与其他硬件模块的通信,实现对电力系统的监测和保护功能。

2. 传感器传感器用于感知电力系统中的状态和参数,包括电流、电压、频率等。

本方案中采用了高精度的传感器,能够实时准确地采集电力系统的运行数据,并将数据传输给控制器进行处理。

3. 物理接口物理接口是控制器与电力系统之间的连接桥梁,主要包括信号采集模块、通信模块等。

信号采集模块负责将传感器采集到的数据转换成数字信号,并传输给控制器;通信模块则负责与其他FTU设备进行通信,实现数据的共享和同步。

4. 电源模块电源模块为整个FTU硬件方案提供稳定可靠的电力供应。

采用高效率的开关电源设计,具有过压、过流、过载等保护功能,能够在电力系统异常情况下保障FTU的正常运行。

5. 外壳和散热设计外壳和散热设计在保证FTU硬件方案正常工作的同时,也具备一定的防护和散热功能。

外壳采用高强度的金属材料制作,能够有效防护FTU硬件免受外界的干扰;散热设计采用高效的散热器和风扇,能够在高温环境下保持FTU硬件的正常工作。

三、主要特点和优势本FTU硬件方案具有以下主要特点和优势:1. 高可靠性:采用先进的硬件设计和工艺,拥有强大的抗干扰和抗冲击能力,能够在恶劣的环境条件下稳定运行。

2. 灵活性强:硬件方案支持多种不同类型的电力系统,具备灵活的配置能力,能够满足不同用户的需求。

3. 成本低廉:采用成熟的集成电路和组件,有效降低了硬件方案的制造成本,使其更加经济实用。

4. 易于维护:硬件方案采用模块化设计,易于维修和升级,降低了维护成本和工作量。

FTU模块技术方案

FTU模块技术方案1 技术方案1.1 FTU模块总体方案FTU模块采集三相电流、线电压、频率、有功功率、无功功率、零序电流和零序电压,采用配电线损采集模块实现计量功能。

1.2 FTU模块基本组成一二次融合FTU模块采用罩式装置,其重要组成部分为线损采集模块和航空插头接口,且航空插头接口包括:供电电源及线电压输入接口(6芯,1个)、电流输入接口(6芯防开路,1个)、控制信号、零序电压接口(14芯,1个)、以太网接口(1个,备用)。

开关侧采用2根电缆、1个26芯航空插头从开关本体引出零序电压、电流及控制信号,接入到FTU的航空插头;采用2根电缆提供供电电源、线电压信号(采用电磁式PT取电)。

1。

3 技术方案优缺点优点:罩式FTU模块体积小,防护等级高,能适应更为严酷的户外运行环境,使用寿命高;缺点:罩式FTU模块的小体积对内部线损模块、电源模块等重要组成部件要求更高,增大了生产工艺难度。

1.4 与相关技术方案对比无对比技术方案。

2 功能要求2。

1 计量功能要求(配套用户末端分界开关除外)FTU采用配电线损采集模块实现计量功能,包括:a)正反向有功电量计算和四象限无功电量计算及功率因数计算;b)计量数据冻结功能:包括日冻结数据,功率方向改变时的冻结数据;c)有功电量计算为0.5S级精度,无功电量计算为2级,功率因数分辨率0。

01。

2.2测量功能要求采集三相电流、线电压、频率、有功功率、无功功率、零序电流和零序电压。

(1)保护功能要求a)应满足Q/GDW-514《配电自动化终端子站功能规范》及《配电自动化终端技术规范》相关要求。

b)分段/联络断路器、分界断路器具备相间故障检测及跳闸功能、相间故障信息上传功能。

c)分段/联络断路器、分界断路器、分界负荷开关具备进出线接地故障的检测及跳闸功能;具备故障录波与通信上传功能,接地故障录波每周波80点以上.(2)测量/计量/保护精度要求a)保护、测量、计量电压:外置PT线电压额定输入为100V,测量精度≤0.5%;b)保护、测量、计量电流:三相额定电流输入为1A;保护≤3%;测量精度为0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FTU硬件详细设计说明书产品线:配电终端产品类别:产品型号:产品版本:批准:审核:初审:编写:1.引言 (4)1.1.前言 (4)1.2.文档术语 (4)1.3.参考文档 (4)2.开发环境 (4)3.硬件详细设计 (5)3.1.系统架构 (5)3.2.主板 (5)3.2.1.主板硬件框图 (6)3.2.2.模块1:CPU核心板 (6)3.2.3.模块2:时钟模块 (18)3.2.4.模块3:无线通讯 (19)3.2.5.模块6 以太网接口 (24)3.2.6.RS232/RS485电路 (26)3.2.7.SD卡模块电路 (27)3.2.8.直流量采集模块 (28)B HOST接口 (30)3.3.遥控遥信板 (31)3.3.1.硬件框图 (31)3.3.2.遥信电路模块 (31)3.3.3.遥控电路模块 (33)3.4.遥测板 (34)3.4.1.遥测板框图 (34)3.4.2.遥测电路模块 (34)3.4.3.电源模块 (38)3.4.4. (40)3.4.5.元器件总成本: (40)3.5.硬件测试方法 (40)4.FPGA逻辑设计 (41)4.1.子板逻辑 (41)4.1.1.架构概述 (42)4.2.主板逻辑 (44)5.结构工艺设计 (45)5.1.外观设计................................................................................... 错误!未定义书签。

5.1.1.外形结构........................................................................... 错误!未定义书签。

5.1.2.铭牌................................................................................... 错误!未定义书签。

5.1.3.终端内部结构................................................................... 错误!未定义书签。

5.2.组屏方案................................................................................... 错误!未定义书签。

5.3.其他........................................................................................... 错误!未定义书签。

5.4 (45)1.引言1.1. 前言1.2. 文档术语1.3. 参考文档2.开发环境硬件设施:普通个人PC软件:protel99 seCadence 16.33. 硬件详细设计3.1. 系统架构AD 采集板X4遥信遥控板X4主板 X1电源板 X13.2. 主板3.2.1.主板硬件框图3.2.2.CPU核心板3.2.2.1. 功能:保存各种数据,参数设置等其他需要保存的数据及给各功能模块提供逻辑接口。

3.2.2.2. 接口描述:32位RISC嵌入式ARM9+DSP内核CPU:OMAPL138ZWT,通过内置DDR2/mDDR控制器接口外扩1片32M/16位或64M/16 位DDR2 SDRAM:MT47H32M16HR/MT47H64M16HR;通过内置外部存储器接口(EMIFA)外扩1片128MBytes NandFLASH:MT29F1G08ABAEAWP-IT和一片FPGA: ALTERA EP3C25F256;通过内部集成的网络接口控制一片网络芯片:LAN8720A;CPU通过一个PWM口作为看门狗的定时喂狗信号来控制CPU的复位脚;此外,CPU核心板把CPU内部集成的外设接口(例如USB、UART、IIC、SPI、MMC/SD 等)和GPIO口及FPGA的LVDS口引出到核心板接口上供其他功能模块接口使用。

3.2.2.3. 设计原理:1)DDR2因OMAPL138ZWT内部集成的RAM 较小,需外扩一片RAM,可利用芯片内置的DDR2/mDDR控制器接口外扩一片32M或64 M容量的DDR2 SDRAM:MT47H32M16HR 或MT47H64M16HR接口如Figure 15-19所示,引脚定义如Table 15-1所示;为满足信号完整性要求,需要在信号线进行端接处理。

因只接了一片DDR芯片所以采用串行端接,原理图如下:CPU_DDR_DQ6CPU_DDR_DQ7CPU_DDR_DQ8CPU_DDR_DQ9CPU_DDR_DQ10CPU_DDR_DQ11CPU_DDR_DQ12CPU_DDR_DQ13CPU_DDR_DQ0CPU_DDR_DQ14CPU_DDR_DQ1CPU_DDR_DQ2CPU_DDR_DQ3CPU_DDR_DQ4CPU_DDR_DQ15CPU_DDR_DQ5CPU_DDR_A12CPU_DDR_A0CPU_DDR_A1CPU_DDR_A2CPU_DDR_A3CPU_DDR_A4CPU_DDR_A5CPU_DDR_A6CPU_DDR_A7CPU_DDR_A8CPU_DDR_A9CPU_DDR_A10CPU_DDR_A11R510402-27R±1%R270402-27R±1%R530402-27R±1%R520402-27R±1%R540402-27R±1%R550402-27R±1%R560402-27R±1%R570402-27R±1%R580402-27R±1%R590402-27R±1%R600402-27R±1%R610402-27R±1%R650402-27R±1%CPU_DDR_CSn5CPU_DDR_CLKP 5CPU_DDR_CLKN5CPU_DDR_WEn 5CPU_DDR_DQS15CPU_DDR_RASn 5CPU_DDR_CASn 5CPU_DDR_DQM15CPU_DDR_DQS05CPU_DDR_CKE 5CPU_DDR_DQM05CPU_DDR_A[0:13]5CPU_DDR_BA[0:2]5R690402-27R±1%R700402-27R±1%R710402-27R±1%CPU_DDR_BA0CPU_DDR_BA2CPU_DDR_BA1R10402-27R±1%MT47H32M16HR MT47H64M16HR DDR2 SDRAM U2A0M8A1M3A2M7A3N2A4N8A5N3A6N7A7P2A8P8A9P3A10M2BA0L2ODTK9DQ0G8DQ1G2DQ2H7DQ3H3DQ4H1DQ5H9DQ6F1DQ7F9UDQS B7UDQS A8LDMF3VDD J9VDD M9VDDL J1VREF J2VDDQ E9VSS A3VSS E3VDDQ A9VDD E1RFU1A2RFU2E2CKE K2CK J8CK K8CAS L7RAS K7WE K3CS L8VDDQ C3VDDQ C7VDDQ C9VSSQ D8VSSQ E7VSSQ F2VSSQ F8VDD A1VSS J3A11P7BA1L3A12R2BA2L1VSS N1VSSDLJ7VSSQ B2RFU3R3DQ8C8DQ9C2DQ10D7DQ11D3DQ12D1DQ13D9DQ14B1DQ15B9VDD R1VDDQ G1VDDQ G7VDDQ G9VSS P9VSSQ D2VSSQ A7VSSQ B8VSSQ H2VSSQ H8VDDQ G3VDDQ C1UDM B3LDQS E8LDQS F7RFU4R7RFU5R8R30402-27R±1%R20402-27R±1%R50402-27R±1%R40402-27R±1%R70402-27R±1%R60402-27R±1%R90402-27R±1%R80402-27R±1%R100402-27R±1%R110402-27R±1%VCC_3V3D1,2,3,5,6GND 1,2,3,5,6R120402-27R±1%R130402-27R±1%1V8_LDO 1,3R140402-27R±1%R150402-27R±1%R160402-27R±1%DDR2_D0DDR2_D3DDR2_D2DDR2_D1DDR2_D4DDR2_D7DDR2_D6DDR2_D5DDR2_D8DDR2_D11DDR2_D10DDR2_D9DDR2_D12DDR2_D15DDR2_D14DDR2_D13DDR2_D1DDR2_D0DDR2_D3DDR2_D2DDR2_D5DDR2_D4DDR2_D7DDR2_D6DDR2_D9DDR2_D8DDR2_D11DDR2_D10DDR2_D13DDR2_D12DDR2_D15DDR2_D14DDR2_A1DDR2_A0DDR2_A3DDR2_A2DDR2_A5DDR2_A4DDR2_A7DDR2_A6DDR2_A9DDR2_A8DDR2_A11DDR2_A10R170402-27R±1%R180402-27R±1%R190402-27R±1%R200402-27R±1%R210402-27R±1%R220402-27R±1%R230402-27R±1%R240402-27R±1%R250402-27R±1%DDR2_DQM1DDR2_DQM0DDR2_CAS DDR2_RAS DDR2_DQS1DDR2_DQS0DDR2_SDCK DDR2_SDCKE DDR2_SDWE DDR2_NSDCKR280402-27R±1%R260402-27R±1%DDR2_NCS1DDR2_A12DDR2_BA2DDR2_BA1DDR2_BA0DDR2_SDCKE DDR2_CASDDR2_NCS1DDR2_NSDCK DDR2_SDCK DDR2_DQS1DDR2_SDWE DDR2_RASDDR2_DQS0DDR2_DQM0DDR2_DQM1EBI_A15C1C2C3C4C5C6C7C8C9C10C11C12C13C14C15C16DDR_VREFVCC_1V8DC170402-100nF±10%R1231K /1% 1/10WVCC_1V8DDDR_VREF1R1241K /1% 1/10WC1190402-100nF±10%C1360402-100nF±10%R800402-27R±1%CPU_DDR_A13CPU_DDR_A[0:13]5CPU_DDR_D[0:15]2)NANDFLASH因OMAPL138ZWT 内部集成的ROM 较小,需外扩一片NANDFLASH ,可利用芯片内置的EMIFA 接口外扩一片1Gb 或2Gb 容量的 NANDFLASH : MT29F1G08ABAEAWP-IT 或MT29F2G08ABAEAWP-IT 。