saber仿真模拟前序讲解

Saber电源仿真--基础篇[

Saber电源仿真——基础篇电路仿真作为电路计算的必要补充和论证手段,在工程应用中起着越来越重要的作用。

熟练地使用仿真工具,在设计的起始阶段就能够发现方案设计和参数计算的重大错误,在产品开发过程中,辅之以精确的建模和仿真,可以替代大量的实际调试工作,节约可观的人力和物力投入,极大的提高开发效率。

Saber仿真软件是一个功能非常强大的电路仿真软件,尤其适合应用在开关电源领域的时域和频域仿真。

但由于国内的学术机构和公司不太重视仿真应用,所以相关的研究较少,没有形成系统化的文档体系,这给想学习仿真软件应用的工程师造成了许多的困扰,始终在门外徘徊而不得入。

本人从事4年多的开关电源研发工作,对仿真软件从一开始的茫然无知,到一个人的苦苦探索,几年下来也不过是了解皮毛而已,深感个人力量的渺小,希望以这篇文章为引子,能够激发大家的兴趣,积聚众人的智慧,使得我们能够对saber仿真软件有全新的认识和理解,能够在开发工作中更加熟练的使用它,提高我们的开发效率。

下面仅以简单的实例,介绍一下saber的基本应用,供初学者参考。

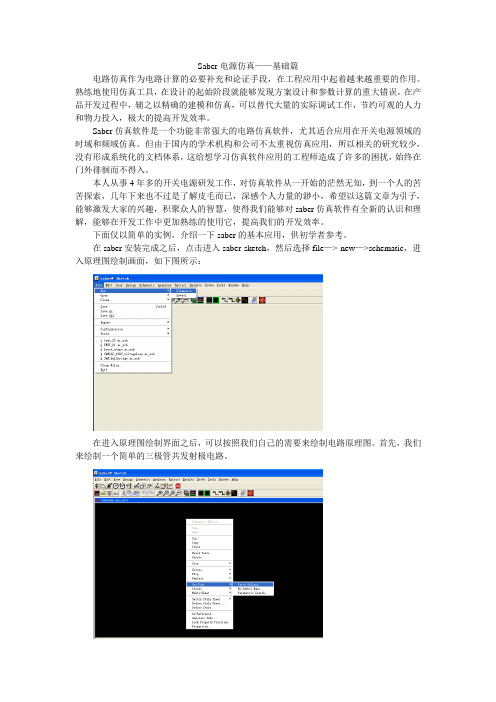

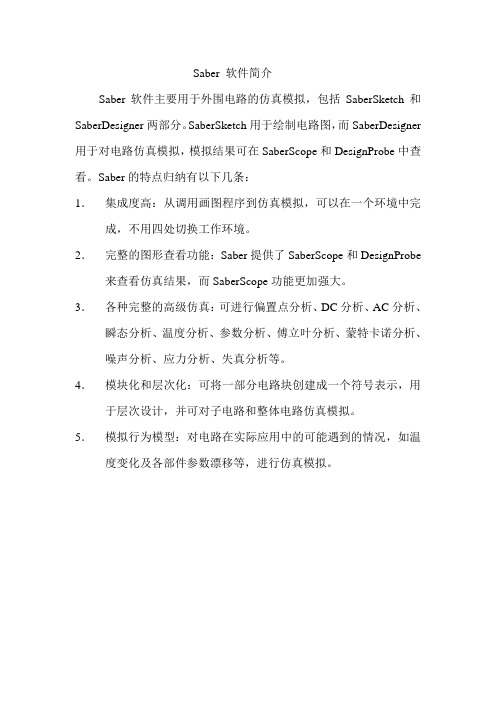

在saber安装完成之后,点击进入saber sketch,然后选择file—> new—>schematic,进入原理图绘制画面,如下图所示:在进入原理图绘制界面之后,可以按照我们自己的需要来绘制电路原理图。

首先,我们来绘制一个简单的三极管共发射极电路。

第一步,添加元器件,在空白处点击鼠标右键菜单get part—>part gallery有两个选择器件的方法,上面的左图是search画面,可以在搜索框中键入关键字来检索,右图是borwse画面,可以在相关的文件目录下查找自己需要的器件。

通常情况下,选择search方式更为快捷,根据关键字可以快速定位到自己想要的器件。

如下图所示,输入双极型晶体管的缩写bjt,回车确定,列表中显示所有含有关键字bjt的器件,我们选择第三个选择项,这是一个理想的NPN型三极管,双击之后,在原理图中就添加了该器件。

saber-2004基础教程

Saber 软件简介Saber软件主要用于外围电路的仿真模拟,包括SaberSketch和SaberDesigner两部分。

SaberSketch用于绘制电路图,而SaberDesigner用于对电路仿真模拟,模拟结果可在SaberScope和DesignProbe中查看。

而SaberScope功能更加强大。

3.各种完整的高级仿真:可进行偏置点分析、DC分析、AC分析、瞬态分析、温度分析、参数分析、傅立叶分析、蒙特卡诺分析、噪声分析、应力分析、失真分析等。

4.模块化和层次化:可将一部分电路块创建成一个符号表示,用于层次设计,并可对子电路和整体电路仿真模拟。

5.模拟行为模型:对电路在实际应用中的可能遇到的情况,如温度变化及各部件参数漂移等,进行仿真模拟。

第一章用SaberSketch画电路图在Parts Gallery中,通过对库的描述、符号名称、MAST模板名称等,进行搜索。

画完电路图后,在SaberSketch界面可以直接调用SaberGuide对电路进行模拟,SaberGuide的所有功能在SaberSketch中都可以直接调用。

启动SaberSketchSaberSketch包含电路图和符号编辑器,在电路图编辑器中,可以创建电路图。

如果要把电路图作为一个更大系统的一部分,可以用SaberSketch将该电路图用一个符号表示,作为一个块电路使用。

启动SaberSketch:▲UNIX:在UNIX窗口中键入Sketch▲Windows NT:在SaberDesigner程序组中双击SaberSketch图标下面是SaberSketch的用户界面及主要部分名称,见图1-1:退出SaberSketch用File>Exit。

打开电路图编辑窗口在启动SaberSketch后,要打开电路图编辑窗口,操作如下:▲要创建一个新的设计,选择File>New>Design,或者点击快捷图标,会打开一个空白窗口。

(完整版)Saber仿真软件介绍

Saber 软件简介Saber软件主要用于外围电路的仿真模拟,包括SaberSketch和SaberDesigner两部分。

SaberSketch用于绘制电路图,而SaberDesigner 用于对电路仿真模拟,模拟结果可在SaberScope和DesignProbe中查看。

Saber的特点归纳有以下几条:1.集成度高:从调用画图程序到仿真模拟,可以在一个环境中完成,不用四处切换工作环境。

2.完整的图形查看功能:Saber提供了SaberScope和DesignProbe 来查看仿真结果,而SaberScope功能更加强大。

3.各种完整的高级仿真:可进行偏置点分析、DC分析、AC分析、瞬态分析、温度分析、参数分析、傅立叶分析、蒙特卡诺分析、噪声分析、应力分析、失真分析等。

4.模块化和层次化:可将一部分电路块创建成一个符号表示,用于层次设计,并可对子电路和整体电路仿真模拟。

5.模拟行为模型:对电路在实际应用中的可能遇到的情况,如温度变化及各部件参数漂移等,进行仿真模拟。

第一章用SaberSketch画电路图在SaberSketch的画图工具中包括了模拟电路、数字电路、机械等模拟技术库,也可以大致分成原有库和自定义库。

要调用库,在Parts Gallery中,通过对库的描述、符号名称、MAST模板名称等,进行搜索。

画完电路图后,在SaberSketch界面可以直接调用SaberGuide对电路进行模拟,SaberGuide的所有功能在SaberSketch中都可以直接调用。

➢启动SaberSketchSaberSketch包含电路图和符号编辑器,在电路图编辑器中,可以创建电路图。

如果要把电路图作为一个更大系统的一部分,可以用SaberSketch将该电路图用一个符号表示,作为一个块电路使用。

启动SaberSketch:▲UNIX:在UNIX窗口中键入Sketch▲Windows NT:在SaberDesigner程序组中双击SaberSketch图标下面是SaberSketch的用户界面及主要部分名称,见图1-1:退出SaberSketch用File>Exit。

Saber 仿真讲座

一、SABER 软件概述

• Saber是美国Analogy(Synopsys)公司开发的系统 仿真软件,被誉为全球最先进的系统仿真软件, 也是唯一的多技术、多领域的系统仿真产品,现 已成为混合信号、混合技术设计和验证工具的业 界标准,可用于电子、电力电子、机电一体化、 机械、光电、光学、控制等不同类型系统构成的 混合系统仿真,这也是Saber的最大特点。 SABER作为混合仿真系统,可以兼容模拟、数字、 控制量的混合仿真,便于在不同层面上分析和解 决问题,其他仿真软件不具备这样的功能。

二、 SABER 的操作界面及仿真

Saber的波形测量

三、 SABER 的应用

指定顶级电路图 要用Saber对设计进行模拟,必须让SaberSketch知道设 计中哪个电路图是最上层的,因为Saber在打开时只能有一 个网表,所以在SaberSketch中只能指定一个顶级电路图。 如果电路图不包含层次设计,SaberSketch会默认打开的电 SaberSketch 路图为顶级电路图。

3.1 DC Operating Point Analysis (直流工作点分析)

Select File > Open > Design… 打开文件 ex_rlc 如下:

三、 SABER 的应用

3.1 DC Operating Point Analysis (直流工作点分析)

1. Click on the Operating Point button 2. Click OK to accept the defaults. 3. When the analysis is complete, select Results > Operating Point Report… from the SaberSketch Pulldown Menu Bar to display the results of the analysis. 4. Click OK to accept the operating point report defaults. The Report Tool comes up, and displays the results of the analysis. Note that all of the displayed values are zero. To find out if this is correct, look at the initial value of the voltage source that drives the filter. The schematic shows that the voltage source has an initial value of 0, and a pulse value of 1. This means that the source will supply zero volts at time = 0. So the results are correct.

Saber仿真软件入门教程解析

SABER讲义第一章使用Saber Designer创建设计本教材的第一部分介绍怎样用Saber Design创建一个包含负载电阻和电容的单级晶体管放大器。

有以下任务:*怎样使用Part Gallery来查找和放置符号*怎样使用Property Editor来修改属性值*怎样为设计连线*怎样查找一些常用模板在运行此教材前,要确认已正确装载Saber Designer并且准备好在你的系统上运行(找系统管理员)。

注:对于NT鼠标用户:两键鼠标上的左、右键应分别对应于本教材所述的左、右键鼠标功能。

如果教材定义了中键鼠标功能,还介绍了完成该任务的替代方法。

一、创建教材目录你需要创建两个目录来为你所建立的单级放大器电路编组数据。

1. 创建(如有必要的话)一个名为analogy_tutorial的目录,以创建教材实例。

2. 进入analogy_tutorial目录。

3. 创建一个名为amp的目录。

4. 进入amp目录。

二、使用Saber Sketch创建设计在这一部分中,你将使用Saber Sketch设计一个单级晶体管放大器。

1. 调用Saber Sketch(Sketch),将出现一个空白的原理图窗口。

2. 按以下方法为设计提供名称3) 通过选择File>Save As …菜单项,存储目前空白的设计。

此时将出现一个Save Schematic As对话框,如图1所示。

图 12) 在File Name字段输入名称Single_amp。

3) 单击OK。

3. 检查Saber Sketch工作面1)将光标置于某一图符上并保持在那里。

会显示一个文字窗口来识别该图符。

在工作面底部的Help字段也可查看有关图符的信息2)注意有一个名为Single_amp的Schematic窗口出现在工作面上。

三、放置部件在教材的这一部分你将按图2所示在原理框图上放置符号。

图中增加了如r1、r2等部件标号以便参照。

图 2 单级晶体管放大器部件布局1.按以下方式查找和放置npn晶体管符号:1) 单击Parts Gallery图符出现Parts Gallery对话框,如图3所示。

Saber_仿真讲座资料

Trig: 完成一些三角运算 (sin cos tag等)

Stack: 管理堆栈寄存器

二、 SABER 的操作界面及仿真

Saber的波形测量

三、 SABER 的应用

➢ 指定顶级电路图 要用Saber对设计进行模拟,必须让SaberSketch知道设

计中哪个电路图是最上层的,因为Saber在打开时只能有一 个网表,所以在SaberSketch中只能指定一个顶级电路图。 如果电路图不包含层次设计,SaberSketch会默认打开的电 路图为顶级电路图。

1.5 可制造性和稳健的设计 Saber的InSpecs工具包能够帮助用户进行复杂的分析,包括统计、

参数和应力分析。统计分析确定参数公差对系统性能的影响,参数分 析显示设计中的关键参数,应力分析评估系统中各组件的应力程度。

一、SABER 软件概述

1.6 FMEA(故障状态分析) Saber的Testify工具包用于仿真系统在故障状态下的情况。

一、SABER 软件概述

1.3 模型库 Saber拥有市场上最大的电气、混合信号、混合技术

模型库,它具有很大的通用模型库和较为精确的具体型号 的器件模型,其元件模型库中有4700多种带具体型号的器 件模型,500多种通用模型,能够满足航空、汽车、船舶 和电源设计的需求。Saber模型库向用户提供了不同层次 的模型,支持自上而下或自下而上的系统仿真方法,这些 模型采用最新的硬件描述语言(HDL),最大限度地保证了 模型的准确性,支持模型共享。

一、SABER 软件概述

1.4 建模 不同类型的设计需要不同类型的模型,Saber提供了完整的建模功

能,可以满足各种仿真与分析的需求。其建模语言主要有MAST、 VHDL-AMS、Fortran,建模工具包括State-AMS、5维的图表建模工 具TLU,Saber可以对SPICE、Simulink模型进行模型转换,同时 Saber还拥有强大的参数提取工具,可以通过协同仿真实现模型复用。

Saber中文使用教程之软件仿真流程

Saber中文使用教程之软件仿真流程(1)今天来简单谈谈 Saber 软件的仿真流程问题。

利用 Saber 软件进行仿真分析主要有两种途径,一种是基于原理图进行仿真分析,另一种是基于网表进行仿真分析。

前一种方法的基本过程如下:a. 在 SaberSketch 中完成原理图录入工作;b. 然后使用 netlist 命令为原理图产生相应的网表;c. 在使用 simulate 命令将原理图所对应的网表文件加载到仿真器中,同时在Sketch 中启动 SaberGuide 界面;d. 在 SaberGuide 界面下设置所需要的仿真分析环境,并启动仿真;e. 仿真结束以后利用 CosmosScope 工具对仿真结果进行分析处理。

在这种方法中,需要使用 SaberSketch 和 CosmosScope 两个工具,但从原理图开始,比较直观。

所以,多数 Saber 的使用者都采用这种方法进行仿真分析。

但它有一个不好的地方就是仿真分析设置和结果观察在两个工具中进行,在需要反复修改测试的情况下,需要在两个窗口间来回切换,比较麻烦。

而另一种方法则正好能弥补它的不足。

基于网表的分析基本过程如下:a. 启动 SaberGuide 环境,即平时大家所看到的 Saber Simulator 图标,并利用 load design 命令加载需要仿真的网表文件 ;b. 在 SaberGuide 界面下设置所需要的仿真分析环境,并启动仿真;c. 仿真结束以后直接在 SaberGuide 环境下观察和分析仿真结果。

这种方法要比前一种少很多步骤,并可以在单一环境下实现对目标系统的仿真分析,使用效率很高。

但它由于使用网表为基础,很不直观,因此多用于电路系统结构已经稳定,只需要反复调试各种参数的情况;同时还需要使用者对 Saber 软件网表语法结构非常了解,以便在需要修改电路参数和结构的情况下,能够直接对网表文件进行编辑。

Saber_仿真讲座解析

一、SABER 软件概述

1.4 建模 不同类型的设计需要不同类型的模型,Saber提供了完整的建模功

能,可以满足各种仿真与分析的需求。其建模语言主要有MAST、 VHDL-AMS、Fortran,建模工具包括State-AMS、5维的图表建模工 具TLU,Saber可以对SPICE、Simulink模型进行模型转换,同时 Saber还拥有强大的参数提取工具,可以通过协同仿真实现模型复用。

一、SABER 软件概述

1.1 原理图输入和仿真

SaberSketch是Saber的原理图输入工具,通过它可以直接进入 Saber仿真引擎。在SaberSketch中,用户能够创建自己的原理图, 启动Saber完成各种仿真(偏置点分析、DC分析、AC分析、瞬态分 析、温度分析、参数分析、傅立叶分析、蒙特卡诺分析、噪声分析、 应力分析、失真分析等),可以直接在原理图上查看仿真结果, SaberSketch及其仿真功能可以帮助用户完成混合信号、混合技术 (电气、液压等)系统的仿真分析。SaberSketch中的原理图可以输 出成多种标准图形格式,用于报告、设计审阅或创建文档。

Logic: 执行逻辑运算 (与 或 非 等)

Trig: 完成一些三角运算 (sin cos tag等)

Stack: 管理堆栈寄存器

二、 SABER 的操作界面及仿真

Saber的波形测量

三、 SABER 的应用

➢ 指定顶级电路图 要用Saber对设计进行模拟,必须让SaberSketch知道设

计中哪个电路图是最上层的,因为Saber在打开时只能有一 个网表,所以在SaberSketch中只能指定一个顶级电路图。 如果电路图不包含层次设计,SaberSketch会默认打开的电 路图为顶级电路图。

Saber仿真软件入门教程

SABER讲义第一章使用Saber Designer创建设计本教材的第一部分介绍怎样用Saber Design创建一个包含负载电阻和电容的单级晶体管放大器。

有以下任务:*怎样使用Part Gallery来查找和放置符号*怎样使用Property Editor来修改属性值*怎样为设计连线*怎样查找一些常用模板在运行此教材前,要确认已正确装载Saber Designer并且准备好在你的系统上运行(找系统管理员)。

注:对于NT鼠标用户:两键鼠标上的左、右键应分别对应于本教材所述的左、右键鼠标功能。

如果教材定义了中键鼠标功能,还介绍了完成该任务的替代方法。

一、创建教材目录你需要创建两个目录来为你所建立的单级放大器电路编组数据。

1. 创建(如有必要的话)一个名为analogy_tutorial的目录,以创建教材实例。

2. 进入analogy_tutorial目录。

3. 创建一个名为amp的目录。

4. 进入amp目录。

二、使用Saber Sketch创建设计在这一部分中,你将使用Saber Sketch设计一个单级晶体管放大器。

1. 调用Saber Sketch(Sketch),将出现一个空白的原理图窗口。

2. 按以下方法为设计提供名称3) 通过选择File>Save As …菜单项,存储目前空白的设计。

此时将出现一个Save Schematic As对话框,如图1所示。

图 12) 在File Name字段输入名称Single_amp。

3) 单击OK。

3. 检查Saber Sketch工作面1)将光标置于某一图符上并保持在那里。

会显示一个文字窗口来识别该图符。

在工作面底部的Help字段也可查看有关图符的信息2)注意有一个名为Single_amp的Schematic窗口出现在工作面上。

三、放置部件在教材的这一部分你将按图2所示在原理框图上放置符号。

图中增加了如r1、r2等部件标号以便参照。

图 2 单级晶体管放大器部件布局1.按以下方式查找和放置npn晶体管符号:1) 单击Parts Gallery图符出现Parts Gallery对话框,如图3所示。

saber仿真模拟前序讲解

第二章仿真模拟前序在SaberSketch中画完电路图后,就可以对设计进行仿真了指定顶级电路图要用Saber对设计进行模拟,必须让SaberSketch知道设计中哪个电路图是最上层的,因为Saber在打开时只能有一个网表,所以在SaberSketch中只能指定一个顶级电路图。

如果电路图不包含层次设计,SaberSketch会默认打开的电路图为顶级电路图,可以略过此步,否则,要用SaberSketch中Design>Use>Design_name来指定顶级电路图。

当指定顶级电路图后,SaberSketch在用户界面右下角显示设计名称,同时创建一个包含其它模拟信息和层次管理的文件(Design.ai_dsn)。

如果电路图是层次的,SaberSketch会增加一个Design Tool(选择Tools>Design Tool或者点击工具栏中的Design Tool图标),如图2-1所示,可以用Design Tool来打开、保存、关闭层次图中的电路图,也可以在各个层次间浏览。

虽然只指定一个顶级图,但仍可以打开、浏览层次图以外的其它电路图。

图2-1 Design Tool网表由于Saber不能直接读取电路图,必须通过网表器产生的网表来进行模拟。

产生的网表器是一个ASCII文件,包含元件名、连接点和所有非默认的元件参数。

要进行模拟时,只要网表中的连接不同于设计中的,SaberSketch会自动对设计进行网表化。

例如:如果增加或修改一条连线,下次分析时,SaberSketch会自动对设计进行网表化并重新调入到Saber中。

如果改变连线的颜色,再去进行分析,Saber将使用原有的网表,因为设计的连接没有改变。

如果改变属性,SaberSketch会自动发送一条Alter命令到Saber中,改变内存网表,因而减少了重新网表化的需要。

设定网表器和Saber实施选项只有第一次运行分析时,Saber才会创建网表并运行,在SaberGuide中进行分析之前,应验证网表器和Saber实施选项。

浅谈Saber仿真步骤

浅谈Saber仿真步骤①绘制设计对象的电路。

首先进人SaberSketch 界面,点击Part。

二响按钮,调出所需要的元器件。

寻找元件的方法有两种,可以通过Search String搜索,也可以双击Available Categorie中的Mast Parts Library项,在各类别中寻找。

第二步编辑元器件属性,双击元器件即可编辑。

第三步将各元器件连接。

得到原理图。

如果电路图较复杂,则要为各分电路图创建符号,符号名要与电路图名一致,后缀为.Ai-sym。

符号要与电路或MAST 模板连接。

最后点击Design 菜单中的Netlist选项生成该设计的网络表。

点击Design 菜单中的Simulate 选项加载设计。

此后就可以进行仿真分析。

②电路分析。

Saber 中主要有直流工作点分析、直流传递特性分析、时域分析、频域分析、线性系统分析、灵敏度分析、参数扫描分析、统计特性分析(蒙特卡罗分析等)、傅立叶变换。

其中,直流工作点分析要注意Holldnodes项的设置以及算法的选择;直流传递特性的分析要注意在某一电源变化时电路中的参数随电源的变化规律;交流小信号分析要注意number of points项设置;暂态分析要注意Run DAnalysis First 项,Allow IP=EP项,Initial Point File 的设置。

计算直流工作点,点击Analyses > Operating Point >DOperating Point…,确定后即开始分析。

通过Results>Operating Point Report…生成的报告可以看到直流分析结果。

频域分析,点击Analyses >Frequency >Small-SignAC…,设定Start Frequency :0.1;End Frequency :1000;Number of Points:10000;Plot。

Saber仿真软件入门教程

Saber仿真软件入门教程SABER讲义第一章使用Saber Designer创建设计本教材的第一部分介绍怎样用Saber Design创建一个包含负载电阻和电容的单级晶体管放大器。

有以下任务:*怎样使用Part Gallery来查找和放置符号*怎样使用Property Editor来修改属性值*怎样为设计连线*怎样查找一些常用模板在运行此教材前,要确认已正确装载Saber Designer并且准备好在你的系统上运行(找系统管理员)。

注:对于NT鼠标用户:两键鼠标上的左、右键应分别对应于本教材所述的左、右键鼠标功能。

如果教材定义了中键鼠标功能,还介绍了完成该任务的替代方法。

一、创建教材目录你需要创建两个目录来为你所建立的单级放大器电路编组数据。

1. 创建(如有必要的话)一个名为analogy_tutorial的目录,以创建教材实例。

2. 进入analogy_tutorial目录。

3. 创建一个名为amp的目录。

4. 进入amp目录。

二、使用Saber Sketch创建设计在这一部分中,你将使用Saber Sketch设计一个单级晶体管放大器。

1. 调用Saber Sketch(Sketch),将出现一个空白的原理图窗口。

2. 按以下方法为设计提供名称3) 通过选择File>Save As …菜单项,存储目前空白的设计。

此时将出现一个Save Schematic As对话框,如图1所示。

图 12) 在File Name字段输入名称Single_amp。

3) 单击OK。

3. 检查Saber Sketch工作面1)将光标置于某一图符上并保持在那里。

会显示一个文字窗口来识别该图符。

在工作面底部的Help字段也可查看有关图符的信息2)注意有一个名为Single_amp的Schematic窗口出现在工作面上。

三、放置部件在教材的这一部分你将按图2所示在原理框图上放置符号。

图中增加了如r1、r2等部件标号以便参照。

(完整版)Saber仿真软件介绍

Saber 软件简介Saber软件主要用于外围电路的仿真模拟,包括SaberSketch和SaberDesigner 两部分。

SaberSketch用于绘制电路图,而SaberDesigner用于对电路仿真模拟,模拟结果可在SaberScope和DesignProbe中查看。

Saber的特点归纳有以下几条:1.集成度高:从调用画图程序到仿真模拟,可以在一个环境中完成,不用四处切换工作环境。

2.完整的图形查看功能:Saber提供了SaberScope和DesignProbe来查看仿真结果,而SaberScope功能更加强大。

3.各种完整的高级仿真:可进行偏置点分析、DC分析、AC分析、瞬态分析、温度分析、参数分析、傅立叶分析、蒙特卡诺分析、噪声分析、应力分析、失真分析等。

4.模块化和层次化:可将一部分电路块创建成一个符号表示,用于层次设计,并可对子电路和整体电路仿真模拟。

5.模拟行为模型:对电路在实际应用中的可能遇到的情况,如温度变化及各部件参数漂移等,进行仿真模拟.第一章用SaberSketch画电路图在SaberSketch的画图工具中包括了模拟电路、数字电路、机械等模拟技术库,也可以大致分成原有库和自定义库。

要调用库,在Parts Gallery中,通过对库的描述、符号名称、MAST模板名称等,进行搜索。

画完电路图后,在SaberSketch界面可以直接调用SaberGuide对电路进行模拟,SaberGuide 的所有功能在SaberSketch中都可以直接调用。

➢启动SaberSketchSaberSketch包含电路图和符号编辑器,在电路图编辑器中,可以创建电路图。

如果要把电路图作为一个更大系统的一部分,可以用SaberSketch将该电路图用一个符号表示,作为一个块电路使用。

启动SaberSketch:▲UNIX:在UNIX窗口中键入 Sketch▲Windows NT:在SaberDesigner程序组中双击SaberSketch图标下面是SaberSketch的用户界面及主要部分名称,见图1-1:退出SaberSketch用 File〉Exit。

Saber中级仿真培训教材

第一章SABER 的建模方法研究一、 前SABER 仿真软件中的器体模型库很丰富,各种器件模型多达1万个,但它们均是 一些通用的器件模型,可以满足大多数情况下的仿真需求。

但在下列三种情况下,就 要自己建立模型进行仿真。

1、 S ABER 提供的仿真模型不能满足一些特殊要求,如在进行参数扫描仿真分析时, 不能将儿个参数同时变化扫描进行仿真。

2、 在对控制策略和系统进行仿真时,对于特定的控制算法或调节器通用软件本身不会 提供现成的算法模型,此时就必须进行建模。

3、 S ABER 提供的模型本身存在缺陷,仿真不能真实地反映电路或系统的工作情况。

如果遇到上述情况之一,为了取得较好的仿真结果和现实指导意义,建立仿真模型 将不可避免。

通常建立仿真模型的方法有两种,一种是基于SABER 模型库中己有的模 型进行组合,将由多个器件组成的电路打包成一个器件,这种方法也称之为电路等级 建模法;另一种是用MAST 语言进行编写,对器件的行为进行描述,这在研究控制算 法中应用较多。

下面列举实例,从这两个方而进行具体介绍建模的操作方法和思路。

二、 基于电路基本器件的建模方法:电路等级建模法。

实例:在进行三相对称电路仿真时,在三相输入或输出的三根相线中串联三个电 抗器La 、Lb 、Lc 和并联三个电容进行滤波,并需要三个电抗器的电感值或三个电容值 同时变化进行参数扫描分析,为了简化电路和仿真分析,可将它们组合成一个电路符 号,并对三个电感和电容进行归一化处理。

1、画屯路图:在SabeiSketch 中,将三个电感和电容接成如图1-1所示的电路。

refilll:lfref 12 l:lf图1・1、三相滤波电路图ref:l3 l:lfref:c1 c:cfref:c2 ref:c3 c:cf c :cf 中2、定义与外电路相连的接线端□和参数:在SABER 的器件库界而下,利用关键词hierarchical 查找,可以查找出四种接线端: Hieiaichical Analogs Hieiaiclucal Bidiiection> Hierarchical Input 、Hieiarclucal Output0 个接线端曰,它们均可放入电路图中与接线端相连,分别适用于模拟、双向、输入和 输出端口。

Saber仿真新手入门就看这几步(经典)

Saber仿真新⼿⼊门就看这⼏步(经典)Saber2011仿真步骤1.画好原理图。

例如:2.保存,格式命为XX.ai_sch3.DC⼯作点分析,主要是求解系统的静态⼯作点,为其他分析提供初始值。

设置如下:采样点密度进度显⽰控制调试释放保留点⾃动显⽰结果结束⽂件是否使⽤初始条4.瞬态(transient)分析(时域分析),瞬态分析⽤于检验系统的时域特性,此分析通常从静态⼯作点开始。

但对于⾃激振荡电路应从零时刻开始:结束时间时间步长显⽰进度先运⾏DC分析5.显⽰瞬态分析结果:点击Results > Operating Point Report,弹出:下划线可以减少空间点击Design > Back-Annotate > Place Across Values,查看每个点的电压值。

6.在设计⽂件中放探头(probe)查看时域波形:在原理图的连线上点击右键,选择probe,就会弹出⼀个⽅框显⽰各点波形,拖动箭头可以显⽰各点的波形(电压---时间)。

7.交流⼩信号分析:点击OK后将会弹出CosmosScope窗⼝双击每个点将会显⽰波形,例如双击n_1得到下图:8.测量波形中每个点的值;还是在CosmosScope窗⼝的左下⽅单击,将会弹出:单击可以显⽰所测的项⽬。

9.参数变化时,为每个电阻值分析:直流⼯作点分析,瞬态分析,⼩信号分析。

下⾯以三极管的发射极电阻(re)变化时的分析举例:在saber sketch窗⼝中单击,显⽰:单击上⾯对话框中的显⽰窗⼝应更改后的对话框如下:后单击Accept,回到Looping Commands中单击选择Within Loop(s)> Transient显⽰下窗⼝:点击弹出:只需要修改InputOut的参数,所以点击并修改参数后如下所⽰:然后点击Accept.回到Looping Commands对话框中单击显⽰如下:只需要修改InputOutput,修改后如下:点击Accept,后点击OK10.显⽰参数扫描结果a.打开CosmosScope窗⼝,点击清除先前的波形;b.关掉先前的XX.vary_ac.ai_pl窗⼝;c.从Signal Manager中单击在新的对话框中按Shift键选择后点击“打开”,显⽰:后选择下的各点显⽰波形:可以从上图中删除(DEG):F(Hz)图形,剩下就是我们需要的图形:d.双击XX.vary_tr.ai_pl中的每个点,(V):t(s)图形也将会显⽰在Graph中。

saber基础篇

Saber电源仿真——基础篇电路仿真作为电路计算的必要补充和论证手段,在工程应用中起着越来越重要的作用。

熟练地使用仿真工具,在设计的起始阶段就能够发现方案设计和参数计算的重大错误,在产品开发过程中,辅之以精确的建模和仿真,可以替代大量的实际调试工作,节约可观的人力和物力投入,极大的提高开发效率。

Saber仿真软件是一个功能非常强大的电路仿真软件,尤其适合应用在开关电源领域的时域和频域仿真。

但由于国内的学术机构和公司不太重视仿真应用,所以相关的研究较少,没有形成系统化的文档体系,这给想学习仿真软件应用的工程师造成了许多的困扰,始终在门外徘徊而不得入。

本人从事4年多的开关电源研发工作,对仿真软件从一开始的茫然无知,到一个人的苦苦探索,几年下来也不过是了解皮毛而已,深感个人力量的渺小,希望以这篇文章为引子,能够激发大家的兴趣,积聚众人的智慧,使得我们能够对saber仿真软件有全新的认识和理解,能够在开发工作中更加熟练的使用它,提高我们的开发效率。

下面仅以简单的实例,介绍一下saber的基本应用,供初学者参考。

在saber安装完成之后,点击进入saber sketch,然后选择file—> new—>schematic,进入原理图绘制画面,如下图所示:在进入原理图绘制界面之后,可以按照我们自己的需要来绘制电路原理图。

首先,我们来绘制一个简单的三极管共发射极电路。

第一步,添加元器件,在空白处点击鼠标右键菜单get part—>part gallery有两个选择器件的方法,上面的左图是search画面,可以在搜索框中键入关键字来检索,右图是borwse画面,可以在相关的文件目录下查找自己需要的器件。

通常情况下,选择search方式更为快捷,根据关键字可以快速定位到自己想要的器件。

如下图所示,输入双极型晶体管的缩写bjt,回车确定,列表中显示所有含有关键字bjt的器件,我们选择第三个选择项,这是一个理想的NPN型三极管,双击之后,在原理图中就添加了该器件。

Saber电源仿真--基础篇

Saber电源仿真——基础篇电路仿真作为电路计算的必要补充和论证手段,在工程应用中起着越来越重要的作用。

熟练地使用仿真工具,在设计的起始阶段就能够发现方案设计和参数计算的重大错误,在产品开发过程中,辅之以精确的建模和仿真,可以替代大量的实际调试工作,节约可观的人力和物力投入,极大的提高开发效率。

Saber仿真软件是一个功能非常强大的电路仿真软件,尤其适合应用在开关电源领域的时域和频域仿真。

但由于国内的学术机构和公司不太重视仿真应用,所以相关的研究较少,没有形成系统化的文档体系,这给想学习仿真软件应用的工程师造成了许多的困扰,始终在门外徘徊而不得入。

本人从事4年多的开关电源研发工作,对仿真软件从一开始的茫然无知,到一个人的苦苦探索,几年下来也不过是了解皮毛而已,深感个人力量的渺小,希望以这篇文章为引子,能够激发大家的兴趣,积聚众人的智慧,使得我们能够对saber仿真软件有全新的认识和理解,能够在开发工作中更加熟练的使用它,提高我们的开发效率。

下面仅以简单的实例,介绍一下saber的基本应用,供初学者参考。

在saber安装完成之后,点击进入saber sketch,然后选择file—> new—>schematic,进入原理图绘制画面,如下图所示:在进入原理图绘制界面之后,可以按照我们自己的需要来绘制电路原理图。

首先,我们来绘制一个简单的三极管共发射极电路。

第一步,添加元器件,在空白处点击鼠标右键菜单get part—>part gallery有两个选择器件的方法,上面的左图是search画面,可以在搜索框中键入关键字来检索,右图是borwse画面,可以在相关的文件目录下查找自己需要的器件。

通常情况下,选择search方式更为快捷,根据关键字可以快速定位到自己想要的器件。

如下图所示,输入双极型晶体管的缩写bjt,回车确定,列表中显示所有含有关键字bjt的器件,我们选择第三个选择项,这是一个理想的NPN型三极管,双击之后,在原理图中就添加了该器件。

Saber仿真软件介绍之欧阳物创编

Saber 软件简介Saber软件主要用于外围电路的仿真模拟,包括SaberSketch和SaberDesigner两部分。

SaberSketch用于绘制电路图,而SaberDesigner用于对电路仿真模拟,模拟结果可在SaberScope和DesignProbe中查看。

Saber的特点归纳有以下几条:1.集成度高:从调用画图程序到仿真模拟,可以在一个环境中完成,不用四处切换工作环境。

2.完整的图形查看功能:Saber提供了SaberScope和DesignProbe来查看仿真结果,而SaberScope功能更加强大。

3.各种完整的高级仿真:可进行偏置点分析、DC分析、AC分析、瞬态分析、温度分析、参数分析、傅立叶分析、蒙特卡诺分析、噪声分析、应力分析、失真分析等。

4.模块化和层次化:可将一部分电路块创建成一个符号表示,用于层次设计,并可对子电路和整体电路仿真模拟。

5.模拟行为模型:对电路在实际应用中的可能遇到的情况,如温度变化及各部件参数漂移等,进行仿真模拟。

第一章用SaberSketch画电路图在SaberSketch的画图工具中包括了模拟电路、数字电路、机械等模拟技术库,也可以大致分成原有库和自定义库。

要调用库,在Parts Gallery中,通过对库的描述、符号名称、MAST模板名称等,进行搜索。

画完电路图后,在SaberSketch界面可以直接调用SaberGuide对电路进行模拟,SaberGuide的所有功能在SaberSketch中都可以直接调用。

➢启动SaberSketchSaberSketch包含电路图和符号编辑器,在电路图编辑器中,可以创建电路图。

如果要把电路图作为一个更大系统的一部分,可以用SaberSketch将该电路图用一个符号表示,作为一个块电路使用。

启动SaberSketch:▲UNIX:在UNIX窗口中键入 Sketch▲Windows NT:在SaberDesigner程序组中双击SaberSketch 图标下面是SaberSketch的用户界面及主要部分名称,见图1-1:退出SaberSketch用 File>Exit。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章仿真模拟前序在SaberSketch中画完电路图后,就可以对设计进行仿真了指定顶级电路图要用Saber对设计进行模拟,必须让SaberSketch知道设计中哪个电路图是最上层的,因为Saber在打开时只能有一个网表,所以在SaberSketch中只能指定一个顶级电路图。

如果电路图不包含层次设计,SaberSketch会默认打开的电路图为顶级电路图,可以略过此步,否则,要用SaberSketch中Design>Use>Design_name来指定顶级电路图。

当指定顶级电路图后,SaberSketch在用户界面右下角显示设计名称,同时创建一个包含其它模拟信息和层次管理的文件(Design.ai_dsn)。

如果电路图是层次的,SaberSketch会增加一个Design Tool(选择Tools>Design Tool或者点击工具栏中的Design Tool图标),如图2-1所示,可以用Design Tool来打开、保存、关闭层次图中的电路图,也可以在各个层次间浏览。

虽然只指定一个顶级图,但仍可以打开、浏览层次图以外的其它电路图。

图2-1 Design Tool网表由于Saber不能直接读取电路图,必须通过网表器产生的网表来进行模拟。

产生的网表器是一个ASCII文件,包含元件名、连接点和所有非默认的元件参数。

要进行模拟时,只要网表中的连接不同于设计中的,SaberSketch会自动对设计进行网表化。

例如:如果增加或修改一条连线,下次分析时,SaberSketch会自动对设计进行网表化并重新调入到Saber中。

如果改变连线的颜色,再去进行分析,Saber将使用原有的网表,因为设计的连接没有改变。

如果改变属性,SaberSketch会自动发送一条Alter命令到Saber中,改变内存网表,因而减少了重新网表化的需要。

设定网表器和Saber实施选项只有第一次运行分析时,Saber才会创建网表并运行,在SaberGuide中进行分析之前,应验证网表器和Saber实施选项。

1、在SaberGuide中验证网表器(Edit>Saber/Netlister Setting),网表器用下面的选项创建网表,网表包含了电路的所有特性,如图2-2:图2-2 网表器设置●Hypermodels:使模拟信号与数字信号匹配,如果没有制定Hypermodel,网表器将使用默认的理想的Hypermodel,其表现特点类似于CMOS技术,输出的默认理想的Hypermodel的表现类似于理想的电压源,其参考电压定义于Netlister/Basic 标签的Power net name和Ground net name。

●Map Files:使符号与它们相应的MAST模板匹配,MAST是能够被Saber模拟器读取的模型语言。

已提供的模拟元件的Map Files能够自动调入网表器中,提供的Map Files必须位于saber_home/bin目录中,在Saber/Netlister Setting框中的Map Files中具体制定的匹配文件必须位于SABER_DATA_PATH环境变量制定的目录中。

2、设定Saber实施选项(Edit>SaberGuide Preferences),如图2-3所示。

图2-3 Saber实施选项对设计进行模拟在验证完网表器和Saber实施选项后,下一步将进行模拟,一般情况下,先要验证设计的功能。

由于设计的电路是工作在理论条件下,所以要调节设计的参数,以减少设计成本和提高电路的可靠性。

Saber软件包含了多种分析,在验证前选择合适的分析类型,分析前,SaberSketch会决定是否有必要重新生成网表,如果有必要,它将会重新生成网表。

如果没有制定顶级电路就进行分析,将会提示制定顶级电路图或者取消分析,除非所设计的电路图是单层的。

●验证设计功能对所设计的功能,可在时域和频域上进行验证,Saber提供了以下的分析方法:▲要验证设计在时域上的规范,可用瞬态分析来看系统在时间上的响应。

傅立叶分析(Fourier analysis)和快速傅立叶分析(FFT analysis)将时域上的波形转变成频谱。

▲要验证设计在频域上的规范,用交流分析(AC analysis)来决定系统小信号频率响应,iFFT分析将频域的波形转换成时域上的波形。

▲直流传输分析(DC Transfer analysis)来扫描独立源和计算每个操作点的扫描值。

●调节设计参数Saber用下列方法来调节设计参数,如设计中的元件数值及容限等:▲Vary:用Vary可以对设计或元件的一系列设定的参数进行描述,对每个参数都进行一系列的分析。

▲Monte Carlo:用蒙特卡诺分析对设计或元件参数随机变化,进行各种分析,对模拟结果进行评估。

▲Sensitivity:对不同设计或元件的参数的改变,性能测量的敏感度。

▲Stress:在精确的DC、DC传输或瞬态分析中,分析元件是否会过应力。

●检查Saber 脚本点击SaberDesigner用户界面右上角的Saber Transcript图标(>cmd)来查看Saber 运行的信息,Saber将信息存在与网表相同的目录,名称为design.out的文件。

查看分析的波形SaberSketch提供两种查看波形的方法,一种是用SaberScope波形分析器,另一种是用SaberSketch中的DesignProbes。

下面将介绍怎样在信号列表中加入节点,怎样查看模板的内部信号,怎样使用SaberSketch中的DesignProbes:●具体制定SaberSketch中的节点或管角来创建波形Saber用信号列表来决定哪个信号加入到画图文件中,可用SaberScope或DesignProbes来查看存于画图文件中的信号的波形。

默认情况下,Saber为设计的根目录中的所有节点都会创建波形,可以手动添加或创建节点或管教到信号列表,也可以通过下面的方法:1、确定设计中有.ai_grm文件,如果没有,可以对设计进行网表化即可生成(Design>Netlist designname)。

2、选择要分析的连线,然后选择所需的分析类型(如瞬态分析)。

3、在Input/Output标签中,点击Select按钮创建或修改信号列表,从弹出的菜单中使用其中的一项:▲All Toplevel Signals:分析顶级设计中的所有信号▲All Signals:分析设计中所有的信号▲Get Selected Signals:分析已选的节点或管脚名称▲Append Selected Signals:在目前的信号列表中追加已选的信号4、在Include Signal Types处,选择下面其中一种:▲Across Variables Only:仅分析变量两端▲Through Variables Only:仅分析通过变量的数据▲All Variables:都分析5、验证分析框中的其它参数设置,点击OK按钮即可运行分析,分析完成后,可用SaberScope或DesignProbes查看节点或管脚的波形。

●在连线或管脚上添加DesignProbes,查看波形Probe是SaberSkech中仅有的有波形查看功能的图形窗口,可以在任意一点添加Probe,和SaberScope一样,SaberSketch中的Probe用信号管理器(Signal Manager)控制DesignProbes需要调用和查看的画图文件(Plot Files)。

当运行分析时,会覆盖目前的画图文件,SaberSketch会在Probe中刷新波形,如果要保留波形,可以指定一个不同的画图文件名称。

1、在设计中添加Probe:将鼠标光标移到连线或管脚处,点击右键,在快捷菜单中选择Probe。

要为元件具体管脚添加Probe,将鼠标移到元件符号处,从右键快捷菜单中选Probe,会出现Select Port对话框,如图2-4所示,从中选择要添加的管脚。

图2-4 选择元件符号的管脚2、在已有的Probe窗口中探测不同点的波形:将Probe箭头指向连线或管脚即可查看相应的波形,只要相应的信号在画图文件中,就可指向该管脚或连线。

(注:本人在用的过程中,如图2-4的情况,选择信号后,可能在Probe中显示不出来,只要把Probe的箭头移到其它地方,再移回来就可以了)3、指定Probe要使用的画图文件:用Probe的信号管理器指定要调用的画图文件(Probe>Probe Signal Manager),或者在Probe上的快捷菜单中选择Display Plotfiles,可以控制要调用的画图文件。

例:图2-5是在一个电路图中改变r6的参数时,两次波形的比较,操作方法如上所述,r6=10k时,选择的画图文件是tr,如图2-6中a所示;r6=20k时,选择的画图文件是tr1,如图2-6中b所示。

图2-5 在Probe中显示波形示例图2-6 修改Plot File处可以在Probe中显示不同的波形改变设计当分析结束后,如果分析的结果不满足要求,可以改变相应的设计,再进行仿真模拟,知道结果符合要求。

●在SaberSketch中改变属性值当在设计中改变属性值时,Saber会发送一条Alter命令将内存网表修改成新值,该方法允许在SaberSketch中修改属性并模拟而不必重新网表化。

●在Saber中改变属性值用Edit>List/Alter菜单项可以查看元件名称、连接点和参数值等。

该菜单显示List/Alter Design框,该框允许改变的参数用于分析中,但是改变的属性不能传回到SaberSketch设计中。

▲Netlist:如图2-7所示,面板中列出了设计中的元件及其相应的连接的节点和自变量,可以用Filter来约束Hierarchical Instance List中陈列出的元件。

例如:如果在Filter处键入r.*,表格将只显示设计中的电阻元件。

除列出元件外,也可以改变元件参数,选择元件,点击Edit按钮,该操作显示Alter Components对话框,在Value处键入新的参数值,点击Apply或OK按钮使改变生效。

图2-7 Netlist面板内容▲Parameters:如图2-8所示,通过该面板也可以改变设计参数,在Parameter 栏中指定参数名称,在Value栏中指定数值。

例如:要将设计温度改为34℃,可以在Parameter栏中查找或键入temp,在Value栏中键入34,点击Ok或Apply 按钮使改变生效。

图2-8 Parameters面板内容▲History:如图2-9所示,在该面板那,允许重新应用已改变的的参数,调用和保存改变命令(Alter)到命令文件(.scs)。