占空比可调的分频器设计

占空比可调的方波发生器电路设计(0~100%可调)

华中师范大学武汉传媒学院课程设计课程名称__________________题目__________________专业__________________ 班级__________________ 学号__________________ 姓名__________________ 成绩__________________ 指导教师_________________________年_______ 月_______日实现占空比可调发生器1.目标(1)占空比可调范围0<D<100%(2)输出方波电压值:Vo=2v(3)振荡频率:f=1kHz(4)波形稳定2.思路根据555定时器改变阀值电压的值使之输出高电平或低电平的原理,就可以产生方波,通过电位器改变电阻的阻值来控制高低电平的时间就可以调节占空比了;通过调节输入的电压值,再通过万用表测量输出的电压值就可以保证输出幅度为某一定值;根据振荡频率公式,已知电阻值和输出振荡频率就可以算出需要电容值,以保证振荡频率为某一定值;为保证波形稳定,采用差分电路形式,用555定时器组成的多谐振荡器的振荡频率受电源电压和温度变化的影响很小;而为了简化电路及运算,采用两个二极管的单向导电特性,使电容器的充放电回路分开,回路不再重复,计算更加简便。

3.电路图(1)输入模块二极管D1,D2的单向导电性,使电容器C的充放电回路分开,调节电位器,就可以调节多谐振荡器的占空比。

(2)处理模块:555定时器各引脚功能如下:1脚:外接电源负极或接地(GND)。

2脚:TR触发输入。

3脚:输出端(OUT或Vo)。

4脚:RD复位端,移步清零且低电平有效,当接低电平时,不管TR、TH输入什么,电路总是输出“0”。

要想使电路正常工作,则4脚应与电源相连。

5脚:控制电压端CO(或VC)。

若此端外接电压,则可改变内部两个比较器的基准电压,当该端不用时,应将该端串入一只0.01μF电容接地,以防引入干扰。

基于vhdl的占空比可调奇分频器设计

分频器在各种数字电路系统设计中均有广泛的应用,其有奇分频器和偶分频器之分,后者相较前者实现较为方便。

目前很多厂家都提供特定的电路模块对时钟进行分频、倍频以及特定相移等,利用VHDL语言和可编程逻辑芯片实现分频则具有便于修改,可靠性高,利于产品升级等优势。

本文设计一种预设参数控制的任意进制奇数分频器,既能实现占空比为50%的任意奇数分频器,又能实现占空比在1/2m到(2m-1)/2m之间调控的任意奇数m分频器。

并在CPLD芯片中实现。

在传统数字系统设计中,频率源一般只提供单一时钟脉冲,其由石英晶振等产生,多采用专用模块实现分频,但针对性强,分频系数固化,成本高;通过VHDL语言,用CPLD实现,便于修改,可靠性高,成本降低,便于产品升级换代,且通过预置参数适应电子系统对时钟频率多种类要求。

本设计使用max-plusII设计平台,利用VHDL语言完成了程序的设计,通过改变预置参数,在CPLD 上EPM7128SLC84-15芯片上实现任意奇数分频器,并能实现占空比50%,以及占空比较宽范围内调控。

1 任意进制奇数分频器原理分析1.1 设计思路要实现占空比为50%的任意奇数m分频器,由于m是奇数,m的一半不是整数,这样如果均在上升沿或均在下降沿实现高低电平转换,则高低电平持续时间会相差0.5个时钟周期。

因此,只有同时利用时钟脉冲上升沿和下降沿切换计数,方能实现占空比为50%的奇数分频。

本设计中实体端口中preset为分频预置数,在实际操作中可通过改变拨动开关状态来更改;clk是时钟信号,clkout是计数分频输出信号,如图1所示。

其设计思路是引入内部计数器counter 对时钟信号计数,同时引入temp1,temp2数据类型为std_logics的两个内部信号。

为了使输出波形占空比仍为50%。

,相对于偶数分频器而言,奇数分频器的设计要复杂一些,需要通过两个进程(process)分别检测时钟信号上升沿和下降沿,对驱动时钟的上升沿和下降沿一同计数。

占空比50的7分频器仿真代码

任务名称:占空比50的7分频器仿真代码一、介绍占空比是指信号中高电平(1)和低电平(0)的时间占比。

在电子设备的设计和控制中,占空比是一个重要参数。

本文将介绍一个用于生成占空比50%的7分频信号的仿真代码。

二、原理7分频是指将输入信号的频率除以7,得到一个输出信号。

占空比50%意味着输出信号的高电平和低电平时间相等。

要实现占空比50%的7分频器,可以采取以下步骤:1.设置一个计数器,初始值为0。

2.在每个时钟周期中,将计数器加1。

3.当计数器的值达到7时,将输出信号设置为1,并将计数器清零。

4.否则,将输出信号设置为0。

三、代码实现根据上述原理,我们可以编写如下的Verilog代码来实现占空比50%的7分频器。

module SevenDivider(input wire clk,output reg out);reg [2:0] count;always @(posedge clk) beginif (count == 6) beginout <= 1;count <= 0;endelse beginout <= 0;count <= count + 1;endendendmodule四、代码仿真为了验证代码的正确性,我们可以使用仿真工具进行验证。

以下是使用ModelSim 进行仿真的步骤:1.创建一个新项目,并将上述Verilog代码添加到项目中。

2.编译代码,检查是否存在语法错误。

3.创建仿真文件,设置仿真时钟,并将测试输出连接到仿真波形。

4.运行仿真,并观察输出波形。

五、仿真结果分析通过对仿真波形的观察,可以得出以下结论:1.输入信号的频率为f。

2.输出信号的频率为f/7。

3.输出信号的占空比为50%。

六、优化方案在实际的电路设计中,我们可以根据需求进行一些优化,以提高电路的性能。

以下是一些优化方案:1.使用更快的时钟源:如果需要更高的输出频率,可以使用更快的时钟源。

EDA课设占空比可调分频器设计报告

华侨大学EDA设计报告--占空比可调分频器姓名:学号:班级:学院:信息科学与工程学院课题难度:0.9摘要本课题为可占空比可调分频器,系统要求为占空比3:10,输出信号频率3MHz;外部时钟信号12MHz。

从题目可知系统功能分为分频和占空比可调两个部分,由于系统要求是能发生占空比为3:10的波形,故先对输入波形十分频,然后调解其占空比为3:10.由于十分频后频率达不到系统要求,故在分频器前加锁相环起到倍频作用,总电路功能是对输入信号四分频并任意调节其占空比,满足设计要求。

关键字:分频器,占空比可调,EDA目录一、系统设计 (3)1、设计要求 (3)2.系统设计方案 (3)二、单元电路设计 (3)1.锁相环 (3)2.分频器 (4)三、软件设计 (5)1.软件设计平台 (5)2.实现方法 (5)四、系统测试 (6)1.软件测试 (6)2.硬件测试 (7)五、结论 (7)六、参考文献 (7)七、附录 (8)总体原理图 (8)分频器源程序 (8)一、系统设计1、设计要求原设计要求:占空比3:10,输出信号频率3MHz;外部时钟信号12MHz。

新扩展要求:占空比任意可调,对任意输入信号四分频。

2.系统设计方案方案一:先通过锁相环把频率扩大为原来的2.5倍,若系统输入频率为12MHz,则锁相环输出频率为30MHz,再把30MHz的方波经分频器十分频,同时按输入的占空比值调节占空比(例如,输入3,则占空比为30%),即可得到设计要求的波形。

方案二:通过锁相环直接调节输入波形的占空比,输出12MHz(锁相环输出频率须大于10MHz,故不能直接输出3MHz的波形),占空比为3:10的波形,再通过四分频器输出3MHz 的波形。

方案对比:两种方案均能实现设计要求,但方案一可以实现任意调节占空比,方案二只能输出固定为3:10占空比的波形,可知方案一更为先进而实用。

故选用方案一。

二、单元电路设计1.锁相环锁相环原理:锁相环是一种基于输入信号与输入信号反馈给振荡控制器的信号之间的相位差的闭环频率控制系统。

基于FPGA 的等占空比任意整数分频器的设计

图 5 6 分频波形仿真图

将分频电路配置到 F lex10K10 芯片中, 在 12 M H z 输 入信号下, 以N = 3 为例进行分频测试, 观察输出波形, 其 结果与设计要求是吻合的。仿真和实测结果都表明分频器 的设计方法是正确的。

本设计利用 V HDL 硬件描述语言和原理图输入方 式, 通过M ax+ P lu s 开发软件, 使用AL T ERA 公司的 FL EX 系列 EPF10K10L C84 4 型 FPGA 器件方便地实现 了符合上述要求的分频器电路设计。

2 设计原理

对于 2N 分频, 可以方便地用模 N 的计数器与一个 T ′触发器 (二分频器) 来简单实现 50% 占空比分频输出。 而对于 2N - 1 的奇数分频, 为了获得 50% 占空比的输出

电子元器件

图 1 5 分频 (N = 1) 的波形示意图

计数器触发边沿前移可以通过时钟信号反相来实现,

时钟信号 CP 与反相控制信号 Q 的异或: CP′= CP Q +

CPQ , 当 Q = 1 时, CP′= CP, 即时钟反相。

对于奇数分频, 当N 计数器进位时, 需对时钟CP 进行

反相, 所以反相控制信号Q 可以由以下状态方程式给出:

关键词: FPGA ; 整数分频器; 等占空比; 电路仿真 中图分类号: TN 791 文献标识码: B 文章编号: 1004 373X (2005) 16 008 02

D es ign of the Equa l D uty Ra t io Arb itrary In teger Frequency D iv ider Ba sed on FPGA

几种简单的占空比可调脉冲电路

几种简单的占空比可调脉冲电路几种简单的占空比可调脉冲电路常用的PWM 电路的实质就是一个方波周期一定占空比可调电路,它的基本工作原理是将一个频率一定的锯齿波信号与一个直流控制电压在比较器进行比较,当直流控制电压改变时,输出占空比就跟随改变。

在没有专用PWM 电路的情况下,可以使用以下介绍的电路。

1.使用双比较器构成的占空比可调电路图1是双比较器构成的占空比可调电路,电路使用一片双比较器,比较器(1)为一个方波振荡器,在其振荡电容上引出锯齿波送到比较器(2)的反相输入端,比较器(2)的同相输入端接控制电压,调节RP 即可调节输出的占空比(即输出脉宽),其工作波形如图2所示。

由图可知,直流控制电压越高,输出脉宽越宽,占空比越大;反之,脉宽变窄、占空比变小,而输出频率由锯齿波的频率决定。

2.使用单运放的占空比可调电路电路如图3所示,单运放构成一个脉冲发生器电路,其振荡频率f =1/2RfC ,电路中Rf =Rf1+Rf2,电容器C 充电经D2、Rf2,放电经D1、Rfl ,改变Rf1与Rf2的比例就可以改变输出的占空比,其占空比为:供应LCD驱动IC,LED电源IC,开关电源IC详情咨询151****2665刘小姐QQ:544845945深圳市和骅芯科技有限公司q(%)=Rf1/Rf×100%3.使用CMOS反相器的占空比可调电路电路如图4所示,它是一个由奇数的CMOS反相器构成的多谐振荡器。

图中的RP、C决定振荡频率。

电容C的充、放电回路由D1、D2隔离,调节RP即可调节占空比。

其振荡频率:f =1.4RPC其占空比:q(%)=Rp1/RP×100%4.使用555定时器的占空比可调电路电路如图5所示,这是一个555构成的典型多谐振器电路,为使占空比可调,加入了二极管D。

由图可知,电容C的充电回路经RP1→D→C;放电回路经C→RP2→555的⑦脚。

其占空比如下:q(%)=RP1/RP×100%调节RP即可调节输出脉宽。

基于FPGA的中频电源的任意占空比的n分频器设计

Value Engineering 0引言在中频电源的数字电路设计中,常常会用到多个时钟脉冲信号。

而FPGA 的主时钟频率(如50MHz )一般比较高,不适合中频感电源输出中频如10KHz 等频率,所以中频电源的分频器设计具有重要地位,若一个数字电路中需要多种频率的脉冲作为驱动,但FPGA 只有一个晶振的频率,若用几个的不同频率的晶振来产生几种输出脉冲的方法,不论是从经济上,还是从数字电路的结构上来讲都是不合理的,因此我们利用FPGA 的主频率进行n 分频从而实现不同频率的方波脉冲,同时也能实现任意占空比调节脉冲。

1任意占空比的n 分频器设计中频感应电源的频率在1K -10KHz 范围内,而基于FPGA 的中频电源设计中重要一项为中频频率脉冲输出,而FPGA 的主时钟频率为50MHz ,要输出如10KHz 的中频输出,必须进行分频器设计即5000分频比,而传统的分频器虽然能行分频但占空比为一般为50%,在中频调压电路通过调节IGBT 的晶闸的占空比来达到调节输出电压且保持输出频率不变,这样即要保证调节电压又满足输出中频频率不变的需要。

我们可以用Verilog HDL 来实现上述功能。

若设FPGA 的主频为50MHZ ,用m 控制占空比,用n 控制分频比即输出的频率,即占空比为m/n ;输出频率f=50M/n 。

我们以输出频率为10KHz 、占空比为0.8为例:当n=50000000/10000=5000(十进制)=01001110001000(二进制),m =n*0.8=4000(十进制)=00111110100000(二进制)时,输出频率为f=10KHz,所以调节n 、m 可达到任意整数频率和占空比的调节。

下面是分频比为5000,占空比为0.8的Verilog HDL 程序和功能仿真图。

Verilog HDL 程序:module nfpzltg(clk,m,n,out);parameter bitsize=14;//计数器二进制位数input clk;input [13:0]m;//占空比调节input [13:0]n;//n 分频output out;reg out;reg[bitsize:0]counter=0;always@(posedge clk)beginif(m==0)out=0;else beginif(m>=n)out=1;else beginif(counter<(m-1))out=1;else out=0;beginif (counter<(n-1))counter=counter +1;//计数else begin out=~out;counter=0;end end end end endendmodule2结束语本文介绍用Verilog HDL 硬件语言实现任意占空比的n 分频器设计,能方便地对任意占空比和n 分频器进行调节达到实现任意占空比的任意n 值的分频的目的。

Verilog-实现任意占空比、任意分频的方法

Verilog-实现任意占空比、任意分频的方法分频程序虽然简单,但我觉得由简入难是学习的一个必然阶段,慢慢的我们自然会成长起来。

所以如果有时间的话,大家都可以将自己的这种“小程序”贴到论坛上来。

如果你的程序好,其他人也可以学习;如果你的程序有问题,大家可以一起帮你找问题,共同进步。

还有,我觉得在发贴的时候,最好能将原理说一下。

一来大家看你的贴能学到东西;二来也方便解答你的问题,不然还得解答者自己去找资料搞懂原理,然后再回答你,回答你问题的人自然也就不多了。

说了一些题外话,下面转入正文:在verilog程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求这样的话,对于程序有一定的要求,现在我在前人经验的基础上做一个简单的总结,实现对一个频率的任意占空比的任意分频。

比如:我们FPGA系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。

我们很容易想到用计数的方式来分频:50000000/880 = 56818这个数字不是2的整幂次方,那么怎么办呢?我们可以设定一个参数,让它到56818的时候重新计数不就完了吗?呵呵,程序如下:module div(clk, clk_div);input clk;output clk_div;reg [15:0] counter;always @(posedge clk)if(counter==56817) counter <= 0;else counter <= counter+1;assign clk_div = counter[15];endmodule//module div(clk,rst,clk_div);input clk,rst;output reg clk_div;reg[15:0] counter;salways@(posedge clk)if(!rst)begincounter<=0;clk_div<=0;endelse if (counter==56817)begincounter<=0;clk_div<~clk_div;endelsecounter<=counter+1;endmodule下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter 为0到32767的时候为低,在32767到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么怎么办呢?不用急,慢慢来。

50%占空比三分频器的设计方法.

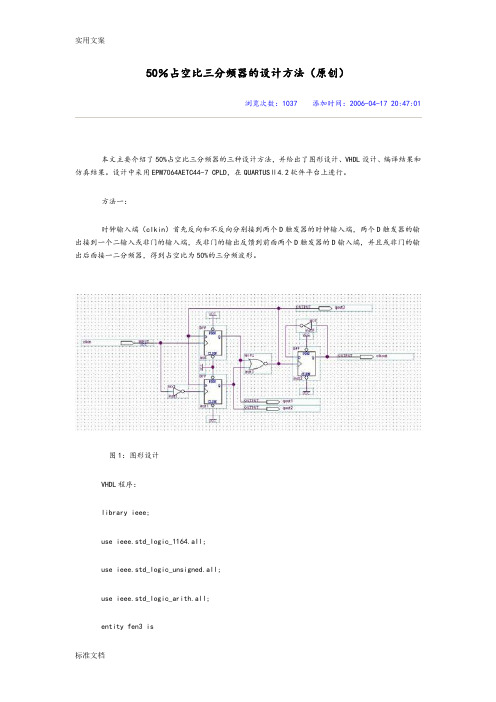

50%占空比三分频器的设计方法(原创)浏览次数:1037 添加时间:2006-04-17 20:47:01本文主要介绍了50%占空比三分频器的三种设计方法,并给出了图形设计、VHDL设计、编译结果和仿真结果。

设计中采用EPM7064AETC44-7 CPLD,在QUARTUSⅡ4.2软件平台上进行。

方法一:时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。

图1:图形设计VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen3 isport(clkin : in std_logic; --时钟输入qout1 : buffer std_logic;qout2 : buffer std_logic;qout3 : buffer std_logic;clkout : out std_logic --占空比为1/2的三分频输出);end fen3;architecture behave of fen3 isbeginqout3<=qout1 nor qout2;process(clkin)beginif clkin'event and clkin='1' then --在上升沿触发qout1<=qout3;end if;end process;process(clkin)beginif clkin'event and clkin='0' then --在下降沿触发qout2<=qout3;end if;end process;process(qout3)variable tem:std_logic;beginif qout3'event and qout3='1' then --二分频tem:=not tem;end if;clkout<=tem;end process;end behave;图2:编译结果图3:仿真结果方法二:设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

50%占空比三分频器地设计方法

50%占空比三分频器的设计方法〔原创〕浏览次数:1037 添加时间:2006-04-17 20:47:01本文主要介绍了50%占空比三分频器的三种设计方法,并给出了图形设计、VHDL设计、编译结果和仿真结果。

设计中采用EPM7064AETC44-7 CPLD,在QUARTUSⅡ4.2软件平台上进展。

方法一:时钟输入端〔clkin〕首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反应到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。

图1:图形设计VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen3 isport(clkin : in std_logic; --时钟输入qout1 : buffer std_logic;qout2 : buffer std_logic;qout3 : buffer std_logic;clkout : out std_logic --占空比为1/2的三分频输出 );end fen3;architecture behave of fen3 isbeginqout3<=qout1 nor qout2;process(clkin)beginif clkin'event and clkin='1' then --在上升沿触发qout1<=qout3;end if;end process;process(clkin)beginif clkin'event and clkin='0' then --在下降沿触发qout2<=qout3;end if;end process;process(qout3)variable tem:std_logic;beginif qout3'event and qout3='1' then --二分频 tem:=not tem;end if;clkout<=tem;end process;end behave;图2:编译结果图3:仿真结果方法二:设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

50%占空比三分频器地设计方法

50%占空比三分频器的设计方法(原创)浏览次数:1037 添加时间:2006-04-17 20:47:01本文主要介绍了50%占空比三分频器的三种设计方法,并给出了图形设计、VHDL设计、编译结果和仿真结果。

设计中采用EPM7064AETC44-7 CPLD,在QUARTUSⅡ4.2软件平台上进行。

方法一:时钟输入端(clkin)首先反向和不反向分别接到两个D触发器的时钟输入端,两个D触发器的输出接到一个二输入或非门的输入端,或非门的输出反馈到前面两个D触发器的D输入端,并且或非门的输出后面接一二分频器,得到占空比为50%的三分频波形。

图1:图形设计VHDL程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fen3 isport(clkin : in std_logic; --时钟输入qout1 : buffer std_logic;qout2 : buffer std_logic;qout3 : buffer std_logic;clkout : out std_logic --占空比为1/2的三分频输出 );end fen3;architecture behave of fen3 isbeginqout3<=qout1 nor qout2;process(clkin)beginif clkin'event and clkin='1' then --在上升沿触发qout1<=qout3;end if;end process;process(clkin)beginif clkin'event and clkin='0' then --在下降沿触发qout2<=qout3;end if;end process;process(qout3)variable tem:std_logic;beginif qout3'event and qout3='1' then --二分频 tem:=not tem;end if;clkout<=tem;end process;end behave;图2:编译结果图3:仿真结果方法二:设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

占空比为50%的任意整数分频器

占空比为50%的任意整数分频器一、分频原理1.1偶数倍分频偶数倍分频通过计数器计数是很容易实现的。

如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2-1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。

以此循环下去。

这种方法可以实现任意的偶数分频。

1.2奇数倍分频奇数倍分频通过计数器也是比较容易实现的,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。

即是在计数值在邻近的1和2进行了两次翻转。

这样实现的三分频占空比为1/3或者2/3。

要实现占空比为50%的三分频时钟,可以通过待分频时钟下降沿触发计数,和上升沿同样的方法计数进行三分频,然后下降沿产生的三分频时钟和上升沿产生的时钟进行相或运算,即可得到占空比为50%的三分频时钟。

这种方法可以实现任意的奇数分频。

归类为一般的方法为:对于实现占空比为50%的N倍奇数分频,首先进行上升沿触发进行模N计数,计数选定到某一个值进行输出时钟翻转,然后经过(N-1)/2再次进行翻转得到一个占空比非50%奇数n分频时钟。

与此同时进行下降沿触发的模N 计数,到和上升沿触发输出时钟翻转选定值相同值时,进行输出时钟时钟翻转,同样经过(N-1)/2时,输出时钟再次翻转生成占空比非50%的奇数n分频时钟。

两个占空比非50%的n分频时钟相或运算,得到占空比为50%的奇数n分频时钟。

二、设计方案及功能现实2.1设计方案综合上述两种分频分式到同一模块,在时钟上升沿用计数器count_p计数,时钟的下降沿用计数器count_n计数。

不论是偶数分频还是奇数分频,其比较条件都是一样的,在0 ≤count_p < (F_DIV/2-1)时,时钟clk_p输出0,在(F_DIV/2-1) ≤ count_p < F_DIV -1 时钟clk_p 输出1(上述说到的奇数分频的计数选定值在这里选0,为结合偶数分频,这里的奇数分频比较点取N/2-1,与上述原理取(N-1)/2有所区别,所以奇数分频最后的结果是上升沿计数输出的时钟(clk_p)和下降沿计数输出的时钟(clk_n)做“与”运算,即clk_out = clk_p & clk_n,但原理是一样的)。