半导体制作工艺流程+版图设计必备

半导体制造工艺流程大全

半导体制造工艺流程大全首先是晶圆切割。

晶圆是通过单晶片生长得到的,为了制造半导体器件,需要将晶圆划分成小块。

切割过程通常使用钻孔或锯片进行,切割后需要将晶圆边缘进行光刻处理。

接下来是晶圆清洗。

切割后的晶圆上会附着一些杂质和残留物,需要通过化学溶液进行清洗,以确保表面的纯净度。

然后是研磨抛光。

为了使晶圆表面更加平整和光滑,需要进行研磨和抛光处理。

通过旋转研磨盘和特殊磨料进行处理,可以去除晶圆表面的不平整和杂质。

接下来是掩膜光刻。

在晶圆上制作电路图案,需要使用掩膜光刻技术。

将铬掩膜覆盖在晶圆表面,通过紫外光和化学反应来形成图案。

掩膜光刻是制造半导体器件中最为关键的步骤之一然后是化学气相沉积。

掩膜光刻后需要进行一层绝缘层的沉积,以保护电路。

接下来是扩散。

为了控制晶体电阻,需要在晶圆表面扩散一层掺杂物。

将晶圆放入炉内,在高温下进行热扩散,使掺杂物渗入到晶圆表面。

然后是离子注入。

离子注入是制造器件的关键步骤之一,通过注入高能粒子改变晶圆表面的材料特性。

注入的离子种类和剂量会对晶圆的电学性质产生重要影响。

接下来是金属薄膜制备。

为了制造金属电极和连线,需要在晶圆表面蒸镀一层金属薄膜。

这层金属薄膜主要用于电子连接和传导。

最后是封装测试。

将制造好的晶圆进行封装,以保护器件免受环境和机械损坏。

通过测试和筛选,可以保证器件的质量和性能。

总结以上所述,半导体制造工艺流程包括晶圆切割、晶圆清洗、研磨抛光、掩膜光刻、化学气相沉积、扩散、离子注入、金属薄膜制备等多个关键步骤。

这些步骤不仅要求高度精确和耐心,而且需要高科技设备和专业技能的支持。

半导体制造工艺的不断改进和创新将推动半导体技术的进一步发展和应用。

半导体制造工艺流程

半导体制造工艺流程

《半导体制造工艺流程》

半导体制造工艺流程是一项复杂而精密的过程,它涉及到众多工艺步骤和高科技设备的运用。

从原料准备到最终产品的制造,整个过程需要严格的控制和监测。

以下是一般的半导体制造工艺流程:

1. 原料准备:半导体材料通常是硅晶圆,因此首先需要准备高纯度的硅原料。

这些原料经过一系列的化学处理,确保其纯度和稳定性。

2. 晶圆生长:通过化学气相沉积或其他方法,在硅片上生长一层极薄的绝缘层或者介质层,作为半导体器件的基质。

3. 掩模制作:使用光刻技术,在晶圆表面涂覆液体光刻胶、曝光和显影,以形成所需的芯片图案。

4. 电子束和离子注入:使用电子束或离子注入技术,将芯片上的电器元件按设计要求添加掺杂剂。

5. 清洗和去除残留物:使用化学溶液或气体等方法,将晶圆表面的零散杂质和残留物清洗干净。

6. 金属沉积:在晶圆上涂覆一层金属,形成导电线路和引脚。

7. 碳化层形成:在晶圆表面生成一层碳化物薄膜,以增加晶圆

的表面硬度和耐高温性能。

8. 封装和测试:将晶圆切割成单个的芯片,然后进行封装和测试,确保半导体器件的性能符合标准要求。

半导体制造工艺流程需要高度的自动化和精密控制,以确保产品质量和生产效率。

同时,对于半导体行业而言,不断的技术创新和设备更新也是不可或缺的。

随着科技的不断进步,半导体制造工艺流程也在不断优化和改进,以满足市场的需求和提高产品性能。

半导体制造工艺流程 ppt课件

2020/10/28

4

一、晶圆处理制程

• 晶圆处理制程之主要工作为在矽晶圆上制作电路与

电子元件(如电晶体、电容体、逻辑闸等),为上 述各制程中所需技术最复杂且资金投入最多的过程 ,

I2L(饱和型)

2020/10/28

9

半导体制造工艺分类

• 二 MOSIC的基本制造工艺: 根据栅工艺分类

• A 铝栅工艺 • B 硅 栅工艺 • 其他分类 1 、(根据沟道) PMOS、NMOS、

CMOS 2 、(根据负载元件)E/R、E/E、E/D

2020/10/28

10

半导体制造工艺分类

• 三 Bi-CMOS工艺: A 以CMOS工艺为基础 P阱 N阱

19

第一次光刻—N+埋层扩散孔

• 1。减小集电极串联电阻 • 2。减小寄生PNP管的影响

要求: 1。 杂质固浓度大

SiO2

2。高温时在Si中的扩散系数小,

以减小上推

N+-BL

3。 与衬底晶格匹配好,以减小应力

P-SUB

涂胶—烘烤---掩膜(曝光)---显影---坚膜—蚀刻—清洗 —去膜--清洗—N+扩散(P)

半导体制造工艺流程

2020/10/28

1

半导体相关知识

• 本征材料:纯硅 9-10个9

250000Ω.cm

• N型硅: 掺入V族元素--磷P、砷As、锑

Sb

• P型硅: 掺入 III族元素—镓Ga、硼B

• PN结:

P

-

-

++ + ++

半导体IC的制做工艺图解

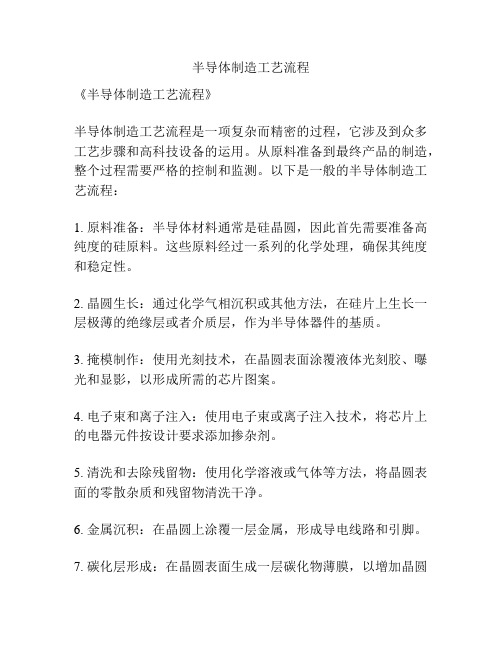

芯片的制造过程可概分为晶圆处理工序(Wafer Fabrication)、晶圆针测工序(Wafer Probe)、构装工序(Packaging)、测试工序(Initial Test and Final Test)等几个步骤。

其中晶圆处理工序和晶圆针测工序为前段(Front End)工序,而构装工序、测试工序为后段(Back End)工序。

1、晶圆处理工序:本工序的主要工作是在晶圆上制作电路及电子元件(如晶体管、电容、逻辑开关等),其处理程序通常与产品种类和所使用的技术有关,但一般基本步骤是先将晶圆适当清洗,再在其表面进行氧化及化学气相沉积,然后进行涂膜、曝光、显影、蚀刻、离子植入、金属溅镀等反复步骤,最终在晶圆上完成数层电路及元件加工与制作。

2、晶圆针测工序:经过上道工序后,晶圆上就形成了一个个的小格,即晶粒,一般情况下,为便于测试,提高效率,同一片晶圆上制作同一品种、规格的产品;但也可根据需要制作几种不同品种、规格的产品。

在用针测(Probe)仪对每个晶粒检测其电气特性,并将不合格的晶粒标上记号后,将晶圆切开,分割成一颗颗单独的晶粒,再按其电气特性分类,装入不同的托盘中,不合格的晶粒则舍弃。

3、构装工序:就是将单个的晶粒固定在塑胶或陶瓷制的芯片基座上,并把晶粒上蚀刻出的一些引接线端与基座底部伸出的插脚连接,以作为与外界电路板连接之用,最后盖上塑胶盖板,用胶水封死。

其目的是用以保护晶粒避免受到机械刮伤或高温破坏。

到此才算制成了一块集成电路芯片(即我们在电脑里可以看到的那些黑色或褐色,两边或四边带有许多插脚或引线的矩形小块)。

4、测试工序:芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。

经测试后的芯片,依其电气特性划分为不同等级。

而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。

半导体制作工艺流程

半导体制作工艺流程第一步:芯片设计芯片设计是半导体制作的第一步,主要由工程师根据需求设计出电路的布局和结构,并进行功能电路的分析和模拟。

第二步:晶圆制备晶圆制备是指通过将高纯度的单晶硅材料经过晶体生长,然后切割成一片薄的圆盘状。

晶圆的制备过程包括硅材料的提纯、晶体生长技术、硅晶圆的切割和去除杂质等步骤。

第三步:化学气相沉积(CVD)化学气相沉积是一种将气体中的化学物质在热腔中化学反应生成固态材料的过程。

CVD可以用来在晶圆表面沉积薄膜,例如用于电子器件的绝缘层、金属线等。

第四步:物理气相沉积(PVD)物理气相沉积是指将固态材料通过蒸发或溅射技术直接沉积在晶圆表面上。

PVD可以用来制备金属层、合金层、氧化层等。

第五步:光刻光刻是一种将芯片设计图案转移到晶圆上的技术。

首先,在晶圆上涂覆一层光刻胶,然后使用光刻机将设计图案通过光刻胶曝光到晶圆上。

曝光后,通过显影将未曝光的区域去除,形成所需电路的图案。

第六步:蚀刻蚀刻是一种将晶圆上的特定区域物质溶解或者刻蚀掉的过程。

蚀刻可以通过湿蚀刻或干蚀刻的方式进行。

湿蚀刻使用化学试剂将晶圆表面的材料溶解,而干蚀刻则通过物理或化学反应将晶圆表面的材料移除。

第七步:离子注入离子注入是指将离子束注入到晶圆中,并通过控制注入的能量和剂量来改变晶圆表面或内部的材料性质。

离子注入可以用来增强或改变半导体材料的导电性能。

第八步:金属化金属化是指对晶圆进行金属薄膜的沉积、电镀和制作金属导线等工艺。

通过金属化,可以连接晶圆上不同区域的电路,形成完整的电子器件结构。

第九步:封装封装是将芯片组装到封装盒中,保护芯片并提供连接器和引脚等功能。

封装工艺包括晶圆切割、引脚焊接、封装胶固化等步骤,在这一步骤完成后,半导体芯片即可用于实际应用。

总结:半导体制作工艺流程是一个非常复杂和精密的过程,涉及到多种工艺技术和设备。

只有经过严格的流程控制和质量检测,才能确保芯片的质量和性能。

随着半导体技术的不断发展,工艺流程也在不断演变,为芯片的性能和制造成本提供更好的平衡。

半导体工业流程图

(涂怖光阻)

光 4.Expouse (暴光) (Stepper)

光

Photo mask 光掩膜

5.Developing (显影) (Developer)

6.Etching (蚀刻)

7.不純物注入 (离子(ion)注入法、拡散法)

8.Resist stripping (剥离) (Stripper)

以上1~(7)、8を繰返し、回路 Pattern を形成する。 反复操作以上 1 到(7),8 程序,形成回路 Pattern。

(涂怖光阻)

4.Expouse (暴光) (Stepper)

5.Developing (显影) (Developer)

Chemical Dispense System

6.Etching (蚀刻) WET bench

Day Tank

P

MDM pump 7.不純物注入 (离子(ion)注入法、拡散法)

8.Resist stripping (剥离) (Stripper)

测试工序

製品

产品

出荷

发货

Semiconductor manufac工程

基板工序

1.Cleaning (洗净) Silicon wafer 2.Deposition (成膜) (CVD 法/熱酸化法等)

3.Photoresist Coating (Spin coater)

Semiconductor manufacturing process (半导体工艺流程)

基板工程と pump

基板工序和 pump

1.Cleaning (洗净) machine WET bench

2.Deposition (成膜) (CVD 法/熱酸化法等)

半导体制造工艺课件(PPT 98页)

消除损伤

退火方式:

炉退火

快速退火:脉冲激光法、扫描电子束、连续波激 光、非相干宽带频光源(如卤光灯、电弧灯、石墨 加热器、红外设备等)

氧化工艺

氧化:制备SiO2层 SiO2的性质及其作用 SiO2是一种十分理想的电绝缘材料,

去掉氮化硅层

P阱离子注入,注硼

推阱

去掉N阱区的氧化层 退火驱入

形成场隔离区

生长一层薄氧化层 淀积一层氮化硅

光刻场隔离区,非隔离区被 光刻胶保护起来

反应离子刻蚀氮化硅 场区离子注入 热生长厚的场氧化层 去掉氮化硅层

形成多晶硅栅

生长栅氧化层 淀积多晶硅 光刻多晶硅栅 刻蚀多晶硅栅

掺杂的均匀性好 温度低:小于600℃ 可以精确控制杂质分布 可以注入各种各样的元素 横向扩展比扩散要小得多。 可以对化合物半导体进行掺杂

离子注入系统的原理示意图

离子注入到无定形靶中的高斯分布情况

退火

退火:也叫热处理,集成电路工艺中所有的 在氮气等不活泼气氛中进行的热处理过程都 可以称为退火

Salicide工艺

淀积多晶硅、刻蚀 并形成侧壁氧化层;

淀积Ti或Co等难熔 金属

RTP并选择腐蚀侧 壁氧化层上的金属;

最后形成Salicide 结构

形成硅化物

淀积氧化层 反应离子刻蚀氧化层,形成侧壁氧化层 淀积难熔金属Ti或Co等 低温退火,形成C-47相的TiSi2或CoSi 去掉氧化层上的没有发生化学反应的Ti或Co 高温退火,形成低阻稳定的TiSi2或CoSi2

氧化层刻蚀掉,并去掉光刻胶 进行大剂量As+注入并退火,形成n+埋层

半导体工艺流程简介ppt

半导体工艺流程的成就与挑战

进一步缩小特征尺寸

三维集成技术

绿色制造技术

智能制造技术

未来半导体工艺流程的发展趋势

01

02

03

04

THANKS

感谢观看

互连

通过金属化过程,将半导体芯片上的电路元件连接起来,实现芯片间的通信和电源分配功能。

半导体金属化与互连

将半导体芯片和相关的电子元件、电路板等封装在一个保护壳内,以防止外界环境对芯片的损伤和干扰。

封装

对封装好的半导体进行功能和性能的检测与试验,以确保其符合设计要求和实际应用需要。

测试

半导体封装与测试

半导体工艺流程概述

02

半导体制造步骤-1

1

半导体材料的选择与准备

2

3

通常使用元素半导体,如硅(Si)、锗(Ge)等,或化合物半导体,如砷化镓(GaAs)、磷化铟(InP)等。

材料类型

高纯度材料对于半导体制造至关重要,杂质含量需要严格控制。

纯净度要求

材料应具有立方、六方或其他特定晶体结构。

晶格结构

蚀刻

使用化学试剂或物理方法,将半导体基板表面未被光刻胶保护的部分进行腐蚀去除。根据蚀刻方法的不同,可以分为湿蚀刻和干蚀刻两种。

去胶

在完成蚀刻后,使用去胶液等化学试剂,去除光刻胶。去胶过程中需要注意控制温度和时间,以避免对半导体基板造成损伤或污染。

半导体的蚀刻与去胶

05

半导体制造步骤-4

金属化

通常使用铝或铜作为主要材料,通过溅射、蒸发或电镀等手段,在半导体表面形成导线图案。

涂布

在半导体基板上涂覆光刻胶,使其覆盖整个基板表面。通常使用旋转涂布法,将光刻胶滴在基板中心,然后通过旋转基板将其展开并涂布在整个表面上。

半导体制造工艺流程18432670

半导体相关知识

• 本征材料:纯硅 9-10个9

250000Ω.cm

• N型硅: 掺入V族元素--磷P、砷As、锑 Sb

• P型硅: 掺入 III族元素—镓Ga、硼B

• PN结:

P

-

-

++ + ++

N

半 导体元件制造过程可分为

• 前段(Front End)制程 晶圆处理制程(Wafer Fabrication;简称 Wafer Fab)、 晶圆针测制程(Wafer Probe);

• A 铝栅工艺 • B 硅 栅工艺 • 其他分类 1 、(根据沟道) PMOS、NMOS、CMOS 2 、(根据负载元件)E/R、E/E、E/D

半导体制造工艺分类

• 三 Bi-CMOS工艺: A 以CMOS工艺为基础 P阱 N阱

B 以双极型工艺为基础

双极型集成电路和MOS集成电 路优缺点

双极型集成电路 中等速度、驱动能力强、模拟精度高、功耗比 较大 CMOS集成电路

0.2um 0.3um 7.5 3 75 30 750 300

NA NA

0.5um 1 10 100

1000

5.0um NA NA NA 7

半 导体元件制造过程

前段(Front End)制程---前工序

晶圆处理制程(Wafer Fabrication; 简称 Wafer Fab)

典型的PN结隔离的掺金TTL电路工艺流程

SiO2

P+ N-epi P+ N-epi P+

N+-BL

N+-BL

P-SUB

涂胶—烘烤---掩膜(曝光)---显影---坚膜—蚀刻—清洗 —去膜--清洗—P+扩散(B)

半导体集成电路工艺流程

集成电路制造工艺流程晶体的生长晶体切片成wafer晶圆制作功能设计à模块设计à电路设计à版图设计à制作光罩工艺流程1) 表面清洗晶圆表面附着一层大约 2um 的 Al2O3 和甘油混合液保护之 , 在制作前必须进行化学刻蚀和表面清洗。

2) 初次氧化有热氧化法生成 SiO2 缓冲层,用来减小后续中 Si3N4 对晶圆的应力氧化技术干法氧化Si( 固 ) + O2 = SiO2( 固 )湿法氧化Si( 固 ) +2H2O =SiO2( 固 ) + 2H2干法氧化通常用来形成,栅极二氧化硅膜,要求薄,界面能级和固定电荷密度低的薄膜。

干法氧化成膜速度慢于湿法。

湿法氧化通常用来形成作为器件隔离用的比较厚的二氧化硅膜。

当 SiO2 膜较薄时,膜厚与时间成正比。

SiO2 膜变厚时,膜厚与时间的平方根成正比。

因而,要形成较厚的 SiO2 膜,需要较长的氧化时间。

SiO2 膜形成的速度取决于经扩散穿过 SiO2 膜到达硅表面的 O2 及 OH 基等氧化剂的数量的多少。

湿法氧化时,因在于 OH 基在 SiO2 膜中的扩散系数比 O2 的大。

氧化反应, Si 表面向深层移动,距离为 SiO2 膜厚的 0.44 倍。

因此,不同厚度的 SiO2 膜,去除后的 Si 表面的深度也不同。

SiO2 膜为透明,通过光干涉来估计膜的厚度。

这种干涉色的周期约为 200nm ,如果预告知道是几次干涉,就能正确估计。

对其他的透明薄膜,如知道其折射率,也可用公式计算出(d SiO2) / (d ox) = (n ox) / (n SiO2) 。

SiO2 膜很薄时,看不到干涉色,但可利用 Si 的疏水性和 SiO2 的亲水性来判断 SiO2 膜是否存在。

也可用干涉膜计或椭圆仪等测出。

SiO2 和 Si 界面能级密度和固定电荷密度可由 MOS 二极管的电容特性求得。

(100) 面的 Si 的界面能级密度最低,约为 10E+10 -- 10E+11/cm – 2 .e V -1 数量级。

半导体制造工艺流程课件

04

半导体制造的后处理

金属化

01

02

03

金属化

在半导体制造的后处理中 ,金属化是一个关键步骤 ,用于在芯片上形成导电 电路。

金属材料

通常使用铜、铝、金等金 属作为导电材料,通过物 理或化学沉积方法将金属 薄膜沉积在芯片表面。

连接电路

金属化过程将芯片上的不 同元件连接成完整的电路 ,实现电子信号的传输和 处理。

高纯度材料

半导体制造需要使用高纯度材料,以确保芯片的性能和可 靠性。然而,高纯度材料的制备和加工难度较大,需要克 服许多技术难题。

制程控制

半导体制造过程中,制程控制是至关重要的。制程控制涉 及温度、压力、流量、电流、电压等众多参数,需要精确 控制这些参数以确保芯片的性能和可靠性。

环境影响

能源消耗

半导体制造是一个高能耗的过程 ,需要大量的电力和能源。随着 半导体产业的发展,能源消耗也 在不断增加,对环境造成了很大 的压力。

废弃物处理

半导体制造过程中会产生大量的 废弃物,如化学废液、废气等。 这些废弃物如果处理不当,会对 环境造成很大的污染和危害。

碳排放

半导体制造过程中的碳排放也是 一个重要的问题。减少碳排放是 半导体产业可持续发展的关键之 一。

未来发展趋势

先进封装技术

随着摩尔定律的逐渐失效,先进封装技术成为半导体制造的重要发展方向。通过将多个 芯片集成在一个封装内,可以实现更小、更快、更低功耗的芯片系统。

沉积薄膜质量

影响沉积薄膜质量的因素包括反应温度、气体流量、压强等,需通 过实验优化获得最佳工艺参数。

外延生长

外延生长目的

在半导体材料表面外延生长一层单晶层,用 于扩展器件尺寸、改善材料性能和提高集成 度。

半导体制造工艺流程

半导体制造工艺流程半导体制造工艺流程是指将硅晶圆上的电子器件(如晶体管、集成电路等)逐步形成的一系列工艺步骤。

半导体工艺流程是一项高度精密的工作,需要对材料的性质进行深入了解,以及对各种设备的操作技术进行精准掌握。

下面将介绍一般的半导体制造工艺流程:一、晶圆制备晶圆是半导体工艺中的基本材料,通常是由高纯度的硅片制成。

在晶圆制备阶段,首先对硅片进行择优,然后将其进行表面处理,以确保表面的平整度和光洁度。

接着在硅片上涂覆光刻胶,以便在后续的工艺中进行图案的刻蚀。

二、光刻在光刻阶段,将已经涂覆光刻胶的硅片放置在光刻机上,通过照射UV光源的方式将图案光刻在光刻胶上。

然后使用显微镜进行目视检查,确保图案的准确性。

三、刻蚀在刻蚀阶段,将经过光刻的硅片放置在刻蚀机中,通过化学或物理的方式将未经保护的硅片部分刻蚀掉,形成所需的结构。

刻蚀过程需要严格控制液体的浓度和温度,以保证刻蚀的精度和稳定性。

四、沉积在沉积阶段,将金属或其他材料沉积在经过刻蚀后的硅片表面,形成电极、导线等电子器件的组成部分。

沉积过程通常采用化学气相沉积或物理气相沉积等技术,通过在特定的条件下控制气体流量和温度来实现材料的沉积。

五、退火在退火阶段,通过加热硅片,使硅片中的金属或其他材料发生晶格结构的重新排列,从而改善材料的性能和稳定性。

退火过程通常需要控制加热速率和温度梯度,以避免材料变形和应力积聚。

六、清洗和检测在清洗和检测阶段,将经过以上工艺的硅片进行清洗,去除表面的杂质和残留物。

然后使用显微镜、电子显微镜等仪器对硅片进行检测,确保器件的准确性和可靠性。

七、封装在封装阶段,将经过工艺流程的硅片切割成单个的芯片,然后将芯片封装在塑料封装体内,形成最终的电子器件。

封装过程需要控制焊接温度和时间,以确保器件的封装质量和可靠性。

总结起来,半导体制造工艺流程是一项极其复杂的工作,需要精密的操作技术和严格的质量控制。

只有在专业技术人员的精心操作和管理下,才能生产出高性能和高可靠性的半导体器件。

半导体制造工艺流程

半导体制造工艺流程N型硅:掺入V族元素--磷P、砷As、锑SbP型硅:掺入III族元素—镓Ga、硼BPN结:半导体元件制造过程可分为前段(FrontEnd)制程晶圆处理制程(WaferFabrication;简称WaferFab)、晶圆针测制程(WaferProbe);後段(BackEnd)构装(Packaging)、测试制程(InitialTestandFinalTest)一、晶圆处理制程晶圆处理制程之主要工作为在矽晶圆上制作电路与电子元件(如电晶体、电容体、逻辑闸等),为上述各制程中所需技术最复杂且资金投入最多的过程,以微处理器(Microprocessor)为例,其所需处理步骤可达数百道,而其所需加工机台先进且昂贵,动辄数千万一台,其所需制造环境为为一温度、湿度与含尘(Particle)均需控制的无尘室(Clean-Room),虽然详细的处理程序是随著产品种类与所使用的技术有关;不过其基本处理步骤通常是晶圆先经过适当的清洗(Cleaning)之後,接著进行氧化(Oxidation)及沈积,最後进行微影、蚀刻及离子植入等反覆步骤,以完成晶圆上电路的加工与制作。

二、晶圆针测制程经过WaferFab之制程後,晶圆上即形成一格格的小格,我们称之为晶方或是晶粒(Die),在一般情形下,同一片晶圆上皆制作相同的晶片,但是也有可能在同一片晶圆上制作不同规格的产品;这些晶圆必须通过晶片允收测试,晶粒将会一一经过针测(Probe)仪器以测试其电气特性,而不合格的的晶粒将会被标上记号(InkDot),此程序即称之为晶圆针测制程(WaferProbe)。

然後晶圆将依晶粒为单位分割成一粒粒独立的晶粒三、IC构装制程IC構裝製程(Packaging):利用塑膠或陶瓷包裝晶粒與配線以成積體電路目的:是為了製造出所生產的電路的保護層,避免電路受到機械性刮傷或是高溫破壞。

半导体制造工艺分类半导体制造工艺分类一双极型IC的基本制造工艺:A在元器件间要做电隔离区(PN结隔离、全介质隔离及PN结介质混合隔离)ECL(不掺金)(非饱和型)、TTL/DTL(饱和型)、STTL(饱和型)B在元器件间自然隔离I2L(饱和型)半导体制造工艺分类二MOSIC的基本制造工艺:根据栅工艺分类A铝栅工艺B硅栅工艺其他分类1、(根据沟道)PMOS、NMOS、CMOS2、(根据负载元件)E/R、E/E、E/D半导体制造工艺分类三Bi-CMOS工艺:A以CMOS工艺为基础P阱N阱B以双极型工艺为基础双极型集成电路和MOS集成电路优缺点半导体制造环境要求主要污染源:微尘颗粒、中金属离子、有机物残留物和钠离子等轻金属例子。

半导体制造流程PPT课件

2019/9/10

3

晶圆处理制程

融化(MeltDown)

颈部成长(Neck Growth)

晶柱成长制程

晶冠成长(Crown Growth)

晶体成长(Body Growth)

尾部成长(Tail Growth)

2019/9/10

4

晶圆处理制程

切片 (Slicing)

圆边 (Edge Polishin

2019/9/10

16

晶圆处理制程

• 离子注入是另一种掺杂技术,离子注入掺杂也分为两 个步骤:离子注入和退火再分布。离子注入是通过高 能离子束轰击硅片表面,在掺杂窗口处,杂质离子被 注入硅本体,在其他部位,杂质离子被硅表面的保护 层屏蔽,完成选择掺杂的过程。进入硅中的杂质离子 在一定的位置形成一定的分布。通常,离子注入的深 度(平均射程)较浅且浓度较大,必须重新使它们再分 布。掺杂深度由注入杂质离子的能量和质量决定,掺 杂浓度由注入杂质离子的数目(剂量)决定。

• 一个现代的IC含有百万个以上的独立组件,而其尺寸通 常在数微米,在此种尺寸上,并无一合适的机械加工机 器可以使用,取而代之的是微电子中使用紫外光的图案 转换(Patterning),这个过程是使用光学的图案以及光感 应膜來将图案转上基板,此种过程称为光刻微影 (photolithography)

2019/9/10

11

晶圆处理制程

曝光(exposure) • 在光刻微影过程,首先为光阻涂布,先将适量光阻滴上基

板中心,而基板是置于光阻涂 布机 的真空吸盘上,转盘 以每分钟數千转之转速,旋转30-60秒,使光阻均匀涂布 在 基板上,转速与旋转时间,依所需光阻厚度而定。 • 曝照于紫外光中,会使得光阻的溶解率改变。紫外光通过 光罩照射于光阻上,而在光照及阴影处产生相对应的图形 ,而受光照射的地方,光阻的溶解率产生变化,称之 为光 化学反应, 而阴影处的率没有变化,这整个过称之为曝光 (exposure)。

半导体制造工艺流程课件PPT(共 105张)

三、IC构装制程

• IC構裝製程(Packaging):利用塑膠 或陶瓷包裝晶粒與配線以成積體電路

• 目的:是為了製造出所生產的電路的保 護層,避免電路受到機械性刮傷或是高 溫破壞。

半导体制造工艺分类

MOS型

双极型

PMOS型 NMOS型 CMOS型 饱和型

非饱和型

BiMOS TTL I2L ECL/CML

SiO2

P+ N-epi P+ N-epi P+

N+-BL

N+-BL

P-SUB

涂胶—烘烤---掩膜(曝光)---显影---坚膜—蚀刻—清洗 —去膜--清洗—P+扩散(B)

第三次光刻—P型基区扩散孔

决定NPN管的基区扩散位置范围 SiO2

外延层淀积

1。VPE(Vaporous phase epitaxy) 气相外延生长硅 SiCl4+H2→Si+HCl 2。氧化

Tepi>Xjc+Xmc+TBL-up+tepi-ox SiO2

N-epi

N+-BL

N+-BL

P-SUB

第二次光刻—P+隔离扩散孔

• 在衬底上形成孤立的外延层岛,实现元件的隔离.

半导体制造工艺流程

半导体相关知识

• 本征材料:纯硅 9-10个9

250000Ω.cm

• N型硅: 掺入V族元素--磷P、砷As、锑 Sb

• P型硅: 掺入 III族元素—镓Ga、硼B

• PN结:

P

-

-

++ + ++

N

半导体元件制造过程可分为

• 前段(Front End)制程 晶圆处理制程(Wafer Fabrication;简称 Wafer Fab)、 晶圆针测制程(Wafer Probe);

半导体生产工艺流程

半导体的生产工艺流程微机电制作技术,尤其是最大宗以硅半导体为基础的微细加工技术(silicon-basedmicromachining),原本就肇源于半导体组件的制程技术,所以必须先介绍清楚这类制程,以免沦于夏虫语冰的窘态。

一、洁净室一般的机械加工是不需要洁净室(cleanroom)的,因为加工分辨率在数十微米以上,远比日常环境的微尘颗粒为大。

但进入半导体组件或微细加工的世界,空间单位都是以微米计算,因此微尘颗粒沾附在制作半导体组件的晶圆上,便有可能影响到其上精密导线布局的样式,造成电性短路或断路的严重后果。

为此,所有半导体制程设备,都必须安置在隔绝粉尘进入的密闭空间中,这就是洁净室的来由。

洁净室的洁净等级,有一公认的标准,以class10为例,意谓在单位立方英呎的洁净室空间内,平均只有粒径0.5微米以上的粉尘10粒。

所以class后头数字越小,洁净度越佳,当然其造价也越昂贵。

为营造洁净室的环境,有专业的建造厂家,及其相关的技术与使用管理办法如下:1、内部要保持大于一大气压的环境,以确保粉尘只出不进。

所以需要大型鼓风机,将经滤网的空气源源不绝地打入洁净室中。

2、为保持温度与湿度的恒定,大型空调设备须搭配于前述之鼓风加压系统中。

换言之,鼓风机加压多久,冷气空调也开多久。

3、所有气流方向均由上往下为主,尽量减少突兀之室内空间设计或机台摆放调配,使粉尘在洁净室内回旋停滞的机会与时间减至最低程度。

4、所有建材均以不易产生静电吸附的材质为主。

5、所有人事物进出,都必须经过空气吹浴(airshower)的程序,将表面粉尘先行去除。

6、人体及衣物的毛屑是一项主要粉尘来源,为此务必严格要求进出使用人员穿戴无尘衣,除了眼睛部位外,均需与外界隔绝接触(在次微米制程技术的工厂内,工作人员几乎穿戴得像航天员一样。

)当然,化妆是在禁绝之内,铅笔等也禁止使用。

7、除了空气外,水的使用也只能限用去离子水(DIwater,de-ionizedwater)。

半导体制造工艺流程图文

激光技术

激光技术在半导体制造中主要用于材料加工、表面处理和 检测等领域。

通过高能激光束对材料表面进行快速加热和冷却,可以实 现高精度和高效率的加工和表面处理。

激光技术在半导体制造中主要用于划片、打标和表面处理 等方面。

04 制造工艺中的设备与材料

通过控制反应气体和温度等参数,可以在硅片 上形成均匀、连续和高质量的薄膜。

常用的化学气相沉积技术包括热化学气相沉积、 等离子增强化学气相沉积和金属有机化学气相 沉积等。

物理气相沉积

物理气相沉积是一种利用物理过程在硅片上沉积薄膜 的方法。

通过控制气体流量和能量等参数,可以在硅片上形成 具有高附着力和致密性的薄膜。

光刻与刻蚀、离子注入和化学机械平坦化等步骤。

这些步骤的精确控制对于制造高性能、高可靠性的半导体器件

03

至关重要。

晶圆制备

01

02

03

晶圆制备是半导体制造 工艺的起始步骤,涉及 切割和研磨单晶硅锭, 以获得平滑、无缺陷的

晶圆表面。

晶圆制备过程中,需要 严格控制温度、压力和 化学试剂的浓度,以确 保晶圆的表面质量和几

03 制造工艺中的关键技术

真空技术

01

真空技术是半导体制造中不可或缺的关键技术之一,主要用 于制造薄膜和清洗表面。

02

在真空环境下,可以控制各种物理和化学过程,从而实现高 质量的薄膜沉积和表面处理。

03

常用的真空技术包括真空蒸发、溅射和化学气相沉积等。

化学气相沉积

化学气相沉积是半导体制造中常用的方法之一, 用于在硅片上沉积各种薄膜材料。

制造工艺设备

清洗设备

用于清除晶圆表面的杂质和污 染物,确保表面的洁净度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

N+ N+ P-

P+

N-Si

PSG P+

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 12。光刻Ⅷ---引线孔光刻。

N+ N+ P-

P+

N-Si

PSG P+

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 13。光刻Ⅸ---引线孔光刻(反刻AL)。

PSG

N+ N+ P-

N+-BL

P-SUB

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗—蒸铝

CMOS工艺集成电路

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 1。光刻I---阱区光刻,刻出阱区注入孔

SiO2

N-Si

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

三、IC构装制程

• IC構裝製程(Packaging):利用塑膠 或陶瓷包裝晶粒與配線以成積體電路

• 目的:是為了製造出所生產的電路的保 護層,避免電路受到機械性刮傷或是高 溫破壞。

半导体制造工艺分类

MOS型

双极型

PMOS型 NMOS型 CMOS型 饱和型

非饱和型

BiMOS TTL I2L ECL/CML

第五次光刻—引线接触孔

•

SiO2

P P+

N+-BL

P N-epi P+ N-epi

N+ P+

N+-BL

P-SUB

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗

第六次光刻—金属化内连线:反刻铝

•

AL

P

P

P+

N-epiP+N-epi

N+ P+SiO2

N+-BL

• 2。阱区注入及推进,形成阱区

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 3。去除SiO2,长薄氧,长Si3N4 Si3N4

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 4。光II---有源区光刻

Si3N4

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

曝光方式:紫外线、X射线、电子束、极紫外

蝕刻技術(Etching Technology)

蝕刻技術(Etching Technology)是將材料使用化學反 應物理撞擊作用而移除的技術。可以分為:

濕蝕刻(wet etching):濕蝕刻所使用的是化學溶液, 在經過化學反應之後達到蝕刻的目的.

乾蝕刻(dry etching):乾蝕刻則是利用一种電漿蝕 刻(plasma etching)。電漿蝕刻中蝕刻的作用,可 能是電漿中离子撞擊晶片表面所產生的物理作用, 或者是電漿中活性自由基(Radical)与晶片表面原 子間的化學反應,甚至也可能是以上兩者的复合作 用。

现在主要应用技术:等离子体刻蚀

常见湿法蚀 刻 技 术

腐蚀液

被腐蚀物

H3PO4(85%):HNO3(65%):CH3COOH(100%):H2O: Al NH4F(40%)=76:3:15:5:0.01

NH4(40%):HF(40%)=7:1

SiO2,PSG

H3PO4(85%)

Si3N4

HF(49%):HNO3(65%):CH3COOH(100%)=2:15:5 Si

衬底制备 一次氧化 隐埋层光刻 隐埋层扩散

外延淀积

基区光刻

再氧化

隔离扩散

隔离光刻

基区扩散 再分布及氧化 发射区光刻 背面掺金

热氧化 发射区扩散

铝合金

反刻铝

铝淀积

接触孔光刻 再分布及氧化

淀积钝化层 压焊块光刻

中测

纵向晶体管刨面图

CBE P

N

N+ C

B

P

NPN晶体管刨面图

SiO2

第一次光刻—N+埋层扩散孔

• 1。减小集电极串联电阻 • 2。减小寄生PNP管的影响

要求: 1。 杂质固浓度大

SiO2

2。高温时在Si中的扩散系数小,

以减小上推

N+-BL

3。 与衬底晶格匹配好,以减小应力

P-SUB

涂胶—烘烤---掩膜(曝光)---显影---坚膜—蚀刻—清洗 —去膜--清洗—N+扩散(P)

半导体制造工艺流程

半导体相关知识

• 本征材料:纯硅 9-10个9

250000Ω.cm

• N型硅: 掺入V族元素--磷P、砷As、锑 Sb

• P型硅: 掺入 III族元素—镓Ga、硼B

• PN结:

P

-

-

++ + ++

N

半 导体元件制造过程可分为

• 前段(Front End)制程 晶圆处理制程(Wafer Fabrication;简称 Wafer Fab)、 晶圆针测制程(Wafer Probe);

第四次光刻—N+发射区扩散孔

• 集电极和N型电阻的接触孔,以及外延层的反偏孔。 • Al—N-Si 欧姆接触:ND≥1019cm-3,

P P+

N+-BL

N+

P+ NP-epi

P+

N+-BL

P-SUB

SiO2

去SiO2—氧化--涂胶—烘烤---掩膜(曝光)---显影---坚膜 —蚀刻—清洗—去膜—清洗—扩散

P+ P+

N-Si

VDD SP

D

IN

OUT

D

SN

集成电路中电阻1

基区扩散电阻

SiO2 P+

R+ P

R-

N-epi N+-BL

VCC AL

N+

P+

P-SUB

集成电路中电阻2

发射区扩散电阻

SiO2

R

P+ N+

N-epi N+-BL

P-SUB

R P+

集成电路中电阻3

基区沟道电阻

SiO2 P+

R

N+

P N-epi

• 9。光ⅤI---P+区光刻,P+区注入。形成 PMOS管的源、漏区及P+保护环。

B+

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

• 10。光Ⅶ---N管场区光刻,N管场区注入, 形成NMOS的源、漏区及N+保护环。

As 光刻胶

P-

N-Si

CMOS集成电路工艺 --以P阱硅栅CMOS为例

P-SUB

Al P+

主要制程介绍

矽晶圓材料(Wafer)

圓晶是制作矽半導體IC所用之矽晶片,狀似圓 形,故稱晶圓。材料是「矽」, IC (Integrated Circuit)厂用的矽晶片即 為矽晶體,因為整片的矽晶片是單一完整的晶 體,故又稱為單晶體。但在整體固態晶體內, 眾多小晶體的方向不相,則為复晶體(或多晶 體)。生成單晶體或多晶體与晶體生長時的溫 度,速率与雜質都有關系。

半导体制造工艺分类

• 一 双极型IC的基本制造工艺: • A 在元器件间要做电隔离区(PN结隔离、

全介质隔离及PN结介质混合隔离) ECL(不掺金) (非饱和型) 、

TTL/DTL (饱和型) 、STTL (饱和型) B 在元器件间自然隔离

I2L(饱和型)

半导体制造工艺分类

• 二 MOSIC的基本制造工艺: 根据栅工艺分类

• 後段(Back End) 构装(Packaging)、 测试制程(Initial Test and Final Test)

一、晶圆处理制程

• 晶圆处理制程之主要工作为在矽晶圆上制作电路与 电子元件(如电晶体、电容体、逻辑闸等),为上 述各制程中所需技术最复杂且资金投入最多的过程 , 以微处理器(Microprocessor)为例,其所需处理 步骤可达数百道,而其所需加工机台先进且昂贵, 动辄数千万一台,其所需制造环境为为一温度、湿 度与 含尘(Particle)均需控制的无尘室(CleanRoom),虽然详细的处理程序是随著产品种类与所 使用的技术有关;不过其基本处理步骤通常是晶圆 先经过适 当的清洗(Cleaning)之後,接著进行氧 化(Oxidation)及沈积,最後进行微影、蚀刻及离 子植入等反覆步骤,以完成晶圆上电路的加工与制 作。

• A 铝栅工艺 • B 硅 栅工艺 • 其他分类 1 、(根据沟道) PMOS、NMOS、CMOS 2 、(根据负载元件)E/R、E/E、E/D

半导体制造工艺分类

• 三 Bi-CMOS工艺: A 以CMOS工艺为基础 P阱 N阱

B 以双极型工艺为基础

双极型集成电路和MOS集成电 路优缺点

双极型集成电路 中等速度、驱动能力强、模拟精度高、功耗比 较大 CMOS集成电路

KOH(3%~50%)各向异向

Si

NH4OH:H2O2(30%):H2O=1:1:5 HF(49%):H2O=1:100 HF(49%):NH4F(40%)=1:10

Ti ,Co TiSi2

CVD化學气相沉積

是利用热能、电浆放电或紫外光照射等化学 反应的方式,在反应器内将反应物(通常 为气体)生成固态的生成物,并在晶片表 面沉积形成稳定固态薄膜(film)的一种 沉积技术。CVD技术是半导体IC制程中运用 极为广泛的薄膜形成方法,如介电材料 (dielectrics)、导体或半导体等薄膜材 料几乎都能用CVD技术完成。