Altera Cyclone III系列FPGA开发板简介

Altera嵌入式系统开发套件加速Cyclone Ⅲ FPGA嵌入式设计开发

其 中, z的 取 值 范 围 是 0 2 5 V , ~ . y的 取 值 范 围 是 0 ~ 20 0 0 。 0 ×1 ~ 用标 准 的 C 气 体 标 定 后 测 出 几 组 数 据 , O 便 可 以用 待 定 系 数法 求 得 K 和 b的值 。

所 显 示 的浓 度值 并 不 一 定 为 零 。 这 时 无 论 值 是 多 少 都 视 其 为零 , 将 此 值 作 为仪 器 的“ 点 ” 并 零 。实 际 的测 量 值 是 通

Al r t a的 C c n I F G 版 嵌 入 式 系统 开 发 套 件含 有精 选 的预 构 建 处 理 器 系统 、 识 产 权 (P 、 作 系统 和 应 用 软件 用 e yl eI P A o I 知 I )操

户 可 以从 大量 的板 上 实例 处理 器 系统 、 示设 计 和参 考 设 计 中进 行 选 择 , 立 自己 的 F G 嵌 入 式 系统 。 演 建 PA

社 ,0 5:1 20 4—1 . 6

[ ]单 成 祥. 传 感 器 的 理 论 与设 计 基 础 及 应 用 I I北 京 : 防 3 - . M- 国

工 业 出 版社 , 9 9 6 1 9 :4 1—4 2 6.

E ]王 玲 生 , 仲 春 . C Y 一 4 贾 X O 1型 三 电极 一 氧 化碳 检 测 报警 仪 的

结 语

C 作 为 一 种剧 毒 性 气 体 , 染 大 气 , 响 人 体 健 康 。 O 污 影

通过对本文设计的报警仪调试 使用 , 个仪器 运行稳定 , 整 所 要 求 功 能 已基 本 实 现 。 当仪 器 运 行 时 , 含 有 C 的混 用 0 合 气 体 进 行 测 试 , 以 显 示 出 气 体 中 CO 的 浓 度 , 进 行 可 并

FPGA开发板

FPGA开发板FPGA开发板ALTERA FPGA是世界上十几家生产CPLD/FPGA的公司中最大的可编程逻辑器件供应商之一,生产的FPGA产品有:FLEX6000/8000/10K、APEX20K、ACEX1K、APEXⅡ、Mercury、Excalibur、Cyclone、Stratix、CycloneⅡ和StratixⅡ等系列。

Altera的FPGA器件采用钢铝布线的先进CMOS技术,具有非常低的功耗和相当高的速度,而且采用连续式互连结构,提供快速的、连续的信号延时。

Altera器件密度从300门到400万门,能很容易地集成现有的各种逻辑器件,高集成度的FPGA提供更高的系统性能,更高的可靠性,更高的性能价格比。

Altera Cyclone系列FPGA是Altera公司2003年9月份推出的,基于1.5V,0.13μm 工艺,Cyclone 是一个性价比很高的FPGA系列。

其中EP1C3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。

本公司因此特推出Cyclone EP1C3T144C8 FPGA开发板,该开发板功能强大,接口丰富,可做大型综合实验。

FPGA开发板硬件资源主要有:1、Altera EP1C3T144C8 FPGA芯片2、Altera 串行配置芯片EPCS13、DAC0832芯片4、ADC0809芯片5、液晶接口6、TP3057PCM编解码芯片7、八位高亮数码管8、八位拨码开关9、4×4阵列键盘10、4个复位轻触按键11、9个高亮发光二极管(红、绿、黄色各三灯)12、双刀双掷继电器13、异步通信串口(UART)14、双有源晶振(24MHz和32.768MHz)15、5V,3.3V,1.5V电源管理系统FPGA开发板带以下DEMO程序:1、FPGA实现流水灯实验2、FPGA实现电子钟实验3、FPGA实现串口发送实验4、FPGA实现串口接收、点阵显示实验5、FPGA实现矩阵键盘和点阵显示(实时扫描方式)6、FPGA实现矩阵键盘和数码管显示(延时扫描方式)7、FPGA实现AD转换、数码显示和拨码选择通道实验8、FPGA实现DA转换,产生锯齿、三角、正弦波;拨码开关选择波形9、FPGA实现液晶显示(并行控制)10、FPGA实现液晶显示(串行控制)11、FPGA实现TP3057音频编解码12、简单密码锁实验(按键+继电器实验)FPGA开发板上的所有模块单元都已连线,省去了连线的烦恼,同时FPGA芯片所有可用I/O都通过自锁紧插座引出,方便做扩展实验,而且FPGA芯片由于管脚密集,在引脚插座旁都标有对应的管脚号,使您对所用的管脚一目了然。

FPGA及其开发板简介

FPGA开发工具

目前,FPGA主要的开发工具有:

• Quartus II • MAX+PLUS II • SOPC Builder(可编程片上系统开发工具) • DSP Builder(内嵌DSP开发工具) • ModelSim(仿真工具) • Synplify/Synplify Pro(综合工具)

目前,应用最广泛的可编程逻辑器件有复杂可编程逻辑 器件(CPLD)、现场可编程门阵列(FPGA)。

FPGA概述

FPGA是现场可编程门阵列(Field Programmable Gate Array)的简称。FPGA器件及其开发系统是开发大规 模数字集成电路的新技术。它利用计算机软件,绘制出实现 用户逻辑的原理图或用硬件描述语言等方式作为设计输入; 然后经一系列转换程序、自动布局布线、模拟仿真的过程, 最后生成配置FPGA器件的数据文件,下载到FPGA器件中, 从而实现了满足用户需求的专用集成电路,真正达到了用户 自行设计集成电路的目的。

开发人员通过软件手段向该芯片中写入特定的指令, 就可以更改、配置器件内部连接结构和逻辑单元,使其完 成一定的功能。

FPGA模块

EP2C5Q208C8N的主要特性:

现在的 FPGA器件内部功能模块越来越丰富,如片内 RAM、锁相环(PLL)、数字信号处理(DSP)模块、 甚至嵌入式CPU等等。

FPGA模块

FPGA模块

▪ nSTATUS(121脚):专用的配置状态脚。双向脚,当它是输出脚时,

是漏极开路的。在上电之后,FPGA立刻将nSTATUS脚置成低电平, 并在上电复位完成后,释放它,将它置为高电平。作为状态输出脚时, 在配置过程中如果有任何一个错误发生了,nSTATUS脚会被置低。 作为状态输入脚时,在配置或初始化过程中,外部控制芯片可以将这 个脚拉低,这时候FPGA就会进入错误状态。这个脚不能用作普通I/O 脚。nSTATUS脚必须上拉一个10K欧的电阻。

FPGA具体型号及参数

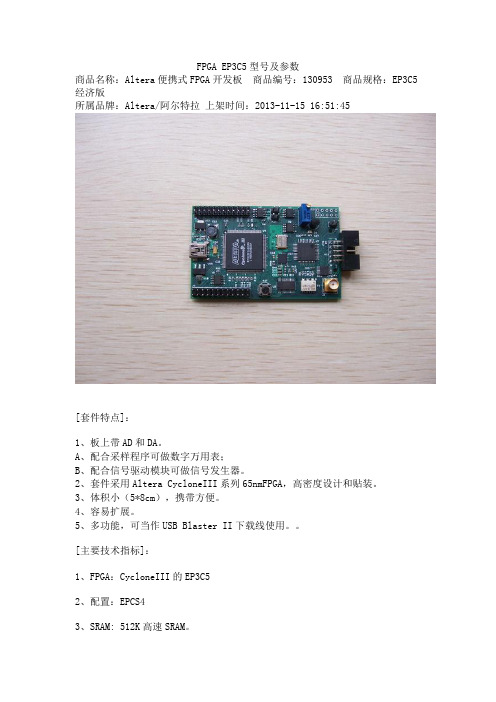

FPGA EP3C5型号及参数

商品名称:Altera便携式FPGA开发板商品编号:130953 商品规格:EP3C5经济版

所属品牌:Altera/阿尔特拉上架时间:2013-11-15 16:51:45

[套件特点]:

1、板上带AD和DA。

A、配合采样程序可做数字万用表;

B、配合信号驱动模块可做信号发生器。

2、套件采用Altera CycloneIII系列65nmFPGA,高密度设计和贴装。

3、体积小(5*8cm),携带方便。

4、容易扩展。

5、多功能,可当作USB Blaster II下载线使用。

[主要技术指标]:

1、FPGA:CycloneIII的EP3C5

2、配置:EPCS4

3、SRAM: 512K高速SRAM。

4、常用电压型DA :1 路10Bit,1.25 MHz maximum update rate

5、AD :1 路10Bit,1.25 MSPS

6、1个LED指示

7、1个复位按钮

8、24M有源晶振

9、2个24针扩展座,支持20个扩展IO,4个CLK输入。

10、四层板,通过全板EMC/EMI和SI仿真。

11、高速电流型DA:可选1 路14Bit 165MSPS(完全版才有此项)。

de0简介(1)

DE0开发板框图

DE0组件

Cyclone IIII 3C16 FPGA 15,408 LEs 56 M9K Embedded Memory Blocks 504K total RAM bits 56 embedded multipliers 4 PLLs 346 user I/O pins FineLine BGA 484-pin package

VGA

输出彩色图像 选择VGA选项卡 插入D-sub线,连接DE0开发板和LCD显示器 LCD显示器上显示控制面板窗口上同样的图像 可以显示单独的颜色

使用DE0开发板——配置 Cyclone III FPGA

DE0开发板有一个串行EEPROM芯片, 存储Cyclone III FPGA的配置数据。 每次上电时,配置数据自动从 EEPROM载入FPGA,该非易失性数据 也能修改。

串行读SDRAM:读SDRAM的内 容并写入一个文件

在“Adress”指定开始地址 在“Length”给定读取长度,如果 读取整个SDRAM,则选择 “Entire Memory” 点击“Load Memory Content to a File” 当控制面板跳出对话窗要求目标文 件时,指定目标文件。

JTAG编程:配置数据流直接下载到 Cyclone III FPGA。当断电时,该配置 丢失。 AS编程:配置数据流下载到Altera EPCS4串行EEPROM芯片。当断电时, 该配置并不丢失。

串行写SDRAM

串行写入:写入文件到SDRAM

1.给定开始地址 2.给定写入长度;如果选择“File Length”,则写入整个文件 3.点击“Write a File to Memory”, 初始化写入的数据 4.当控制面板跳出对话窗要求源文 件时,指定源文件

Cyclone III资料

Cyclone III原型开发调试转载:/ilove314/1819329/Message.aspx 最近设计的Cyclone III原型板是特权同学第一次接触Cyclone III的器件。

原理图、PCB绘制、管脚分配上都碰到了一些问题,这些问题或多或少都是由于个人对新器件不熟悉、设计的时候有一些粗心大意造成的。

主要针对板级的硬件设计,这里凌乱的罗列一下,做一点总结,今后要多吸取教训,低级的失误要尽量避免。

1. 首先要提一个没有解决的问题,EP3C5E144/EP3C10E144/ EP3C16E144/ EP3C 25E144(是管脚完全兼容的不同资源的器件,Altera在这一点上是非常值得称道的)器件的PIIN11和PIN12存在不可同时使用的问题,这个问题出现在架构了一个NIOS2系统里集成了EPCS控制器的时候,在Cyclone II中是不需要分配这个EPCS控制器的管脚的(内部自动映射),而Cyclone III则需要手动分配(事先需要到Setting里动动手脚)。

EPCS的DCLK需要分配到PIN12上,工程中分配了一个SDRAM的D0脚给PIN11,编译到Fitting阶段就Error了。

在handbook里海找没什么成效,求助于搜索引擎,最终看到有人遇到相同的问题,但是给出的却是不是办法的解决办法:不用PIN11或者不用PI N12。

这个问题上特权同学也很是无可奈何,估计是Cyclone III器件的这两个脚做了一些信号耦合之类的检查,也不知道是否在工具选项里做一些设置可以取消此类检查。

也很期待有相同遭遇的朋友现身说法,告诉特权如何解决问题。

2. 再说两个很低级的错误,错的很傻,没有什么技术含量,只能给自己敲个警钟:干活的时候脑子一定要清醒。

两个错误分别和BOM表和网络标号有关。

先说和BOM表有关的,这个错误源于原理图上两个三端稳压器-1.2和-2.5的标示刚好反过来了,因为管脚定义和封装都一样所以也没留意,好在最后只影响BOM表的标示,但这也导致了第一块样板焊接的时候出现了1.2V和2.5V互换位置的惨剧,结果可想而知,EP3C10E144C7就这样挂了,非常的心疼。

在65nm Cyclone III FPGA中实现低功耗

在65nm Cyclone III FPGA中实现低功耗低功耗、低成本和高性能FPGA――CycloneIII系列,采用了TSMC的65nm工艺,含有5K至120K逻辑单元,288个DSP乘法器,存储器达到4Mb,比前一代产品逻辑单元成本降低20%,主要针对消费类、汽车、工业和无线通信等市场。

CycloneIII在单个器件中集成了SDR信号处理,静态功耗低于0.5W,可满足软件无线电的应用。

与前一代产品和竞争产品相比,CycloneIIIFPGA的低功耗、高密度和充足的DSP功能,使设计人员可以在无线应用中使用低成本系列产品,例如无线微基站的数字IF和基带功能等。

在视频系统I/O、视频压缩编码以及视频和图像处理应用中,客户能够以低于20美元的成本实现全H.264编码器,或低于5美元的成本实现高清晰缩放功能。

CycloneIII器件针对显示应用进行了优化,能够满足所有1080pHDTV性能需求。

采用专业显示I/O接口(mini-LVDS、低摆幅差分信号和点对点差分信号)来构建CycloneIII系列,与前一代产品相比,每个锁相环(PLL)有更多的输出,动态配置PLL支持可变刷新率。

客户可以针对多种显示尺寸和分辨率设计单一平台,成本只有4美元。

还可以结合现有的ASIc/ASSP器件来使用cycloneIII器件,以提高图像质量和功能。

工程师可以在QuartnsII设计软件7.0中开始CycloneIII 系列设计,该软件的订购版和免费的网络版支持所有的系列型号。

传统上,人们总是期望新一代FPGA具有更好的特性和性能。

然而,设计工程师必须将这些新特性和高性能集成在与上一代产品相同、甚至更小尺寸的芯片上,并要保持芯片功耗不变。

此外,某些应用还必须要满足一些特殊的功耗要求。

结果,功耗在设计工程师的FPGA选择标准中扮演了越来越重要的角色。

为了能够以最低的功耗来实现65nm工艺节点的低成本和高性能特性,Altera结合硅工艺优化和Quartus II PowerPlay 功耗分析及优化技术,生产了功耗非常低的65nm低成本FPGA――Cyclone III。

Altera Cyclone芯片分析

摘要Cyclone系列芯片是Altera公司推出的新一代低成本、中等规模的FPGA,其价格仅为Altera现有主流器件的30%~50%。

它通过去掉DSP块,MegaRAM,降低LVDS接口速率等指标后,可适应大多数设计的要求,同时分担用户所面临的成本压力。

本论文的开头部分详细介绍了Cyclone系列芯片的体系结构。

该芯片采用0.13μm,全铜SRAM工艺,1.5v内核,同时还拥有2910个逻辑单元到20060个逻辑单元以及59904位RAM到294912位RAM,这使得它可用于实现多种复杂的功能。

此外,该芯片还提供了用于时钟管理的锁相环和用于连接工业标准外部存储器的专用I/O接口;而且,多种IP核及Altera发布的Nios嵌入式微处理器软核均能在其上实现。

之后,论文对Cyclone系列芯片的配置方法进行了探讨,并着重介绍了低成本的串行配置方案。

接着,论文对此次毕业设计中用到的主要开发工具进行了简要介绍,其中包括Protel 99SE和Quartus II软件。

最后,我们具体实现了一个基于Cyclone FPGA的电子时钟的设计。

可编程器件方面,我们选用的是240管脚PQFP封装的EP1C12器件;配置时则是采用主动串行配置方案下的EPCS1器件。

在此,论文主要讲解了板卡的组成、内部设计及仿真,其中内部实现包括:原理图、PCB图的绘制和VHDL程序的编写。

关键词:Cyclone,逻辑阵列块,逻辑单元,互连,锁相环,I/O元素,串行配置器件,Quartus IIABSTRACTAltera®Cyclone™FPGAs—the lowest-cost FPGAs ever—are half the cost of competing devices. Cyclone FPGAs are the optimal solution for high-volume, price-sensitive applications that previously required the use of fixed solutions such as gate arrays and standard cells.At the beginning of the dissertation, we describes the Cyclone architecture in detail. Cyclone FPGAs are built on a cost-optimized, all-copper 1.5-V SRAM process. With up to 20,060 logic elements (LEs) and 288 Kbits of RAM, Cyclone FPGAs can integrate many complex functions. Cyclone FPGAs offer multiple full-featured phase-locked loops (PLLs) to manage board-level clock networks and dedicated I/O interfaces for interfacing with industry standard external memory devices. Altera's Nios® embedded processor and a full intellectual property (IP) portfolio is available for development with Cyclone FPGAs.Then we discuss the configuration schemes of the Cyclone devices,especially the low-cost active serial configuration scheme.After that, we talk about the tools which we used in this graduation design. These tools contain Potel 99SE and Quartus II .Lastly, we use the EP1C12 device in the 240-pin PQFP package and the EPCS1 device which is used to configure EP1C12 in the active serial configuration scheme to implement an electronic clock. In this part, the thesis mainly explains the composition, internal design (including drawing schematic diagram, drawing PCB diagram and programming in VHDL) and simulation of the board.KEY WORDS: Cyclone, LAB, LE, Interconnect, PLL, IOE, Serial Configuration Device, Quartus II目录第一章绪论 (1)1.1.可编程逻辑与ASIC简介 (1)1.2.课题来源及意义 (1)1.3.作者所做工作 (2)1.4.论文结构安排 (2)第二章Cyclone系列芯片的结构分析 (3)2.1.概述 (3)2.1.1.Cyclone主要特性 (3)2.1.2.功能描述 (4)2.2.逻辑阵列块(LAB) (5)2.2.1. LAB互连 (6)B控制信号 (6)2.2.3.逻辑单元(LE) (7)2.2.4.LUT链和寄存器链 (8)2.2.5.addnsub信号 (8)2.2.6.LE的操作模式 (8)2.2.7.进位选择链 (9)2.2.8.清零/重置逻辑控制 (9)2.3.多通道互连(MultiTrack Interconnect) (9)2.4.嵌入式存储器 (10)2.4.1.存储模式 (11)2.4.2.支持奇偶校验位 (11)2.4.3.支持移位寄存器 (12)2.4.4.存储器的配置大小 (12)2.4.5.字节使能 (13)2.4.6.独立时钟模式 (13)2.4.7.输入/输出时钟模式 (13)2.4.8.读/写时钟模式 (13)2.4.9.单端口模式: (14)2.5.全局时钟网络和锁相环 (14)2.5.1.全局时钟网络 (14)2.5.2.双效时钟管脚 (15)2.5.4.锁相环(PLLs) (15)2.6.I/O结构 (16)第三章Cyclone系列芯片的主动串行配置方法 (19)3.1.Cyclone系列芯片主要配置方法简介 (19)3.2.串行配置的实现 (20)3.2.1.配置多个层叠状态的器件 (21)3.2.2.对串行配置器件进行编程 (22)3.2.3.串行配置器件的管脚描述 (22)第四章Protel 99SE及Quartus II软件简介 (23)4.1.Protel电子电路设计软件 (23)4.2.Quartus II开发工具 (24)4.2.1.Quartus II概述 (24)4.2.2.Quartus II的功能 (24)第五章基于Cyclone系列芯片的简单应用 (27)5.1.板卡的组成及结构图 (27)5.2.板卡的逻辑设计 (29)5.2.1.七段显示器模块的逻辑设计 (29)5.2.2.电子时钟时间计数模块的逻辑设计 (32)5.2.4.弹跳消除电路模块的逻辑设计 (34)5.2.3.电子时钟时间设定及其时间显示模块的逻辑设计 (36)附录一消除弹跳电路及微分电路组合模块的程序代码 (41)附录二自由计数器模块及状态转换模块的程序模块 (43)结束语 (45)致谢 (46)参考文献 (47)第一章绪论1.1.可编程逻辑与ASIC简介可编程逻辑器件(PLD)是由用户编程实现所需要逻辑功能的数字集成电路。

cyclone3的配置方式

cyclone3的配置方式cyclone3的配置方式cyclone3器件使用SRAM单元保存配置信息。

因为SRAM掉电易失的特性,fpga芯片上电的时候必须重新配置。

根据期间密度和封装选择,它有如下5中配置方案(红色部分为常用配置方案,并不是所有FPGA芯片都能使用所有配置方案,具体可查看cyclone3的器件手册):1. Active serial (AS)主动串行配置2. Active parallel (AP)主动并行配置3. Passive serial (PS)被动串行配置4. Fast passive parallel (FPP)快速被动并行配置5. Joint Test Action Group (JTAG)AS和AP配置方案需要外部FLASH存储器存储配置信息。

其它3种配置方案需要外部的控制器或者下载电缆。

主动配置方案以及JTAG方案常用于单芯片系统设计。

下面重点介绍AS,AP和JTAG。

以AS配置为例介绍。

Cyclone3器件的配置芯片通常选择EPCS64,EPCS16以及EPCS4或者flash.这些芯片能够提供廉价,方便(引脚少)的解决方案。

因为FPGA芯片容量的限制,它对配置信息的大小也有所限制。

EP3C80系列器件可提供21MBITS的配置信息流容量。

MSEL【3:0】为FPGA器件的输入,用于确定配置方式。

AS模式下,它连接1101.AP模式下,它连接1011.注意要直接接 VCCA or GND,更不能悬空,避免无效配置。

查看手册可得到其它配置值。

在JTAG模式下,忽略MSEL配置,JTAG模式有优先权。

AS模式支持配置信息压缩,AP模式不支持。

压缩信息可以节约空间以及配置时间。

在Device & Pin Options――Configuration中可以选择压缩与否。

选择好器件后,参考下图连接。

POR――上电复位.复位时间由MSEL【3:0】决定。

复位结束后开始发送配置控制信号。

Cyclone FPGA系列简介

Cyclone FPGA系列简介Altera®Cyclone™ FPGA是目前市场上性价比最优且价格最低的FPGA(1)。

Cyclone器件具有为大批量价格敏感应用优化的功能集,这些应用市场包括消费类、工业类、汽车业、计算机和通信类。

Cyclone器件现正在发售中。

器件基于成本优化的全铜1.5V SRAM工艺,容量从2910至20060个逻辑单元,具有多达294912bit嵌入RAM,见表1。

Cyclone FPGA支持各种单端I/O标准如LVTTL、LVCMOS、PCI和SSTL-2/3,通过LVDS和RSDS标准提供多达129个通道的差分I/O支持。

每个LVDS通道高达640Mbps。

Cyclone器件具有双数据速率(DDR) SDRAM和FCRAM接口的专用电路。

Cyclone FPGA中有两个锁相环(PLLs)提供六个输出和层次时钟结构,以及复杂设计的时钟管理电路。

这些业界最高效架构特性的组合使得FPGA系列成为ASIC最灵活和最合算的替代方案。

注释:1. Cyclone FPGA是现今成本最低和经成品认证的FPGA。

表1归纳了Cyclone FPGA系列产品、性能及供货情况注释:2. 有关这些器件供货的详细情况,请和当地Altera销售代表处联系。

表2是Cyclone器件封装和I/O管脚数注释:3. TQFP = 薄四方扁平封装4. PQFP = 四方扁平封装5. BGA = 球栅阵列表3是Cyclone开发包和供货情况。

表4是合适Cyclone器件的配置器件。

联系AlteraAltera只通过销售代表处和分销商销售可编程逻辑器件(PLD)。

如您需要购买Altera产品,请与我们的销售代表处和分销商联系。

ALTERA系列芯片解密

Arria GX,Arria-II GX

24小时服务热线:086-0755-83003639

E-mail:market2@

【责任编辑:pcbsjx文章来源:/article/pcb1558.html】

acex系列ep1k10ep1k30ep1k50ep1k100apex20k系列ep20k30eep20k60eep20k100ep20k100eep20k160eep20k20k200ep20k200eep20k200cep20k300eep20k400ep20k400eep20k400cep20k600eep20k600cep20k1000eep20k1000cep20k1500eapexii系列ep2a15ep2a25ep2a40ep2a70cyclone系列ep1c3ep1c4ep1c6ep1c12ep1c20cycloneii系列ep2c5ep2c8ep2c20ep2c50ep2c70excalibur系列epxa1epxa4epxa10flex10k系列epf10k10epf10k10aepf10k20epf10k30epf10k30aepf10k30eepf10k40epf10k50epf10k50vepf10k50eepf10k50sepf10k70epf10k100aepf10k100eepf10k130eepf10k200eepf10k200sepf10k250aflex6000系列epf6010aepf6016epf6016aepf6024amax3000a系列epm3032aepm3064aepm3128aepm3256aepm3512a尾缀不限脚数都不限max7000系列epm7032sepm7032saeepm7032bepm7064sepm7064aeepm7064b尾缀不限脚数都不限epm7128sepm7128aeepm7256sepm7256aeepm7512ae尾缀不限脚数都不限maxii系列epm240epm570epm1270epm2210mercury系列ep1m120ep1m350stratix系列ep1s10ep1s20ep1s25ep1s30ep1s40ep1s60ep1s80stratixgx系列ep1sgx10cep1sgx10dep1sgx25cep1sgx25dep1sgx25fep1sgx40dep1sgx40gstratixii系列ep2s15ep2s30ep2s60ep2s90ep2s130ep2s180stratixiii系列stratixiiilstratixiiistratixiv系列stratixivstratixivgxstratixivg

Cyclone III FPGA系列

Cyclone III FPGA系列:一切皆有可能前所未有的同时实现了低功耗、高性能和低成本Cyclone® III FPGA系列前所未有的同时实现了低功耗、高性能和低成本,大大提高了您的竞争力。

其特性以及Cyclone III FPGA体系结构为您的大批量、低功耗、低成本应用提供了理想的解决方案。

为满足您独特的设计需求,这一FPGA系列包括:∙Cyclone III:功耗最低、成本最低的高性能FPGA∙Cyclone III LS:具有安全特性、功耗最低的FPGA Cyclone III LS器件具有200K逻辑单元、8 Mbits嵌入式存储器以及396个嵌入式乘法器,是高性能处理、低功耗应用的理想选择,包括:轻松达到您的功耗目标具有200K逻辑单元(LE)、8-Mbits存储器,而静态功耗不到1/4瓦,该系列设立了功耗标准。

采用台积电(TSMC)的低功耗(LP)工艺技术进行制造,无论是通信设备、手持式消费类产品,还是软件无线电设备,这些FPGA都能够轻松满足您的功耗预算。

设计安全性Cyclone III LS FPGA利用低功耗、高性能FPGA平台,在硬件、软件和知识产权(IP)层面上率先实现了一系列安全特性。

一系列安全特性保护了您的IP不被篡改、逆向剖析和克隆。

而且,这些器件还使您能够通过设计分离特性,在一个芯片中实现冗余功能,从而减小了实际应用的体积、重量和功耗。

全面的设计资源为确保流畅、成功的设计流程,帮助您更快的将构思变为收益,Altera 提供全面的Cyclone III FPGA设计环境,包括:∙Quartus® II开发软件∙成熟的IP库∙Nios® II,世界上最通用的嵌入式处理器∙低成本开发套件∙专用参考设计将您的设计从构思变为产品,更迅速推向市场。

采用Cyclone III FPGA,一切皆有可能。

相关链接∙观看划分FPGA设计,实现冗余和信息安全网播∙下载Cyclone III FPGA手册(PDF)∙观看Cyclone III FPGA视频Cyclone III 器件系列体系结构Cyclone® III FPGA前所未有地同时实现了低功耗、低成本和高性能。

Cyclone V开发板

Cyclone V开发板Altera 的Cyclone V 实现了业界最低的系统成本和功耗,其性能水平使得该器件系列成为突出您大批量应用优势的理想选择。

与前几代产品相比,总功耗降低了40%,具有高效的逻辑集成功能,提供集成收发器型号以及具有基于ARM® 的硬核处理器系统(HPS) 的SoC FPGA 型号。

Cyclone® V FPGA为业界提供系统成本最低、功耗最低的FPGA 解决方案,以及小尺寸封装选项。

这些优点结合其性能和逻辑利用率特性,实现了能够突出您大批量应用优势的器件。

内核ARM+FPGA 架构中精度可调数字信号处理(DSP) 模块、多端口存储器控制器和多功能PCI Express Gen2 增强IP 等丰富的硬核知识产权(IP) 模块帮助您以更低的系统总成本和更短的设计时间完成更多的工作。

作为一种可以马上使用的功能,这些硬核IP 模块简化了您的开发过程,进一步降低了功耗,在增强存储器控制器方面,相对于软核逻辑占用了更少的电路板空间。

而且还节省了很多的逻辑资源,从而用于实现独特的功能,突出您的产品优势。

Cyclone V 收发器低成本收发器各有不同。

借助Altera Cyclone® V FPGA 系列的灵活性,您可以全面利用所有收发器资源,在体积更小、成本更低的器件中实现设计。

Cyclone V FPGA 能够非常灵活的通过增强构建模块以尽可能低的功耗来实现独立协议和专用协议。

Cyclone V SoCFPGA使用宽带互联干线链接,Altera SoC 集成了基于ARM 的硬核处理器系统(HPS),包括处理器、外设和存储器接口。

Cyclone® V SoC 在一个基于ARM 的用户可定制芯片系统(SoC) 中集成了分立处理器、FPGA 和数字信号处理(DSP) 功能,帮助您降低了系统功耗、系统成本,减小了电路板面积,提高了系统性能。

Altera FPGA 同时实现了硬核知识产权(IP) 的性能和低功耗特性以及可编程逻辑的灵活性。

Altera最新FPGA

Stratix III FPGA系列简介

表1. Stratix III 逻辑器件简介

Stratix III L Family Variants 器件 EP3S L50 19,000 47,500 38,000 108 6 1,836 594 216 EP3S L70 27,000 67,500 54,000 150 6 2,214 844 288 EP3SL 110 42,600 106,500 85,200 275 12 4,203 1,331 288 EP3SL 150 56,800 142,000 113,600 355 16 5,499 1,775 384 EP3SL 200 79,560 198,900 159,120 468 24 7,668 2,486 576 EP3SE 260 101,760 254,400 203,520 864 48 14,688 3,180 768 EP3SL 340 135,200 338,000 270,400 1,144 48 17,208 4,225 576

Stratix IV FPGA系列简介

表 2. Stratix IV E 增强型器件简介

Stratix IV E 型号 特性 等价逻辑单元 (LE) 自适应逻辑模块 (ALM) 寄存器 M9K 存储器模块 M144K 存储器模块 嵌入式存储器 (Kbits) MLAB (Kbits) 18 x 18 Multipliers (1) EP4SE110 105,600 42,240 84,480 660 16 8,244 1,320 512 EP4SE230 228,000 91,200 182,400 1,235 22 14,283 2,850 1,288 EP4SE290 291,200 116,480 232,960 936 36 13,608 3,640 832 EP4SE360 353,600 141,440 282,880 1,248 48 18,144 4,420 1,040 EP4SE530 531,200 212,480 424,960 1,280 64 20,736 6,640 1,024 EP4SE680 681,100 272,440 544,880 1,529 64 22,977 8,514 1,360

Altera DE3 高阶开发平台

Altera DE3 开发教学板拥有世界上容量最大、效能最好的FPGA ─ Stratix III,提供工程师以及研究开发者进行开发研究。

从其最基本款的Stratix III 3SL150型号开始,DE3就是创造划时代可程序逻辑设计的绝佳平台,它有别于世上其它的开发板系统,DE3可以藉由多片板子堆栈组成更多的等效闸数(Gate count)来提高效能。

DE3系列中还有 DE3-340和 DE3-260两个型号,其内建了更多的乘法器(Multipliers),能够更有效满足DSP开发研究者的需求。

此外,不管哪个型号的DE3皆可堆栈在一起,并支持友晶科技所设计的各种接口子卡,例如,在环境受限时,它可垂直堆栈多达10块的DE3以节省空间;亦可水平扩充来增加高速接头以满足连接外部子卡的需要。

可垂直堆栈多达10块的DE3以节省空间可水平扩充来增加高速接头以满足连接外部子卡的需要FPGA DevicesStratix III EP3SL150 (DE3-150)o142,000 logic elements (LEs)o5,499K total memory Kbitso384 18x18-bit multipliers blockso736 user I/Os∙Stratix III EP3SE260 (DE3-260)o 254,400 logic elements (LEs)o14,688K total memory Kbitso768 18x18-bit multipliers blockso736 user I/Os∙Stratix III EP3SL340 (DE3-340)o338,000 logic elements (LEs)o16,272K total memory Kbitso576 18x18-bit multipliers blockso736 user I/OsDE3开发板拥有最强大的功能,让使用者可以轻松利用丰富的开发资源以及各种设计接口,其中,DE3尤其为针对高速讯号处理的应用以及复杂的算法设计计划提供了一个完美的平台。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ETL-002 Altera Cyclone III

系列FPGA开发板简介

概述

ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。

除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述

主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。

开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。

开发板同时支持AS模式下载和JTAG模式下载。

程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。

丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。

这些接口主要包括:

PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上

PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上

VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。

开发板自带了动态彩条显示的功能

双串口接口:可以与任何的串口设备相接。

开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。

开发板自带的演示程序实时地显示分钟和秒钟的信息。

4位LED灯:用于指示状态。

开发板自带了跑马灯实验。

4位按键开关:可用于复位等作用。

4位拨码开关:可用于电路的选择作用

教学实验

除了开发板的丰富的硬件资源外,我们还提供了数十个学习实验。

通过这些实验,您可以学习FPGA芯片,Quartus II软件和设计仿真和下载等FPGA的设计流程,然后将试验中程序执行的信息通过数码管,LED 灯,串口等板上的硬件直观的显示出来。

我们提供的《ETL-002 Altera FPGA开发板实验手册》中提供的实

验列表如下:

目录

1...实验概述.. (3)

2...实验分类 (5)

2.1 滑动开关亮灯实验 (5)

2.1.1 实验要求 (5)

2.1.2 实验步骤 (5)

2.1.3 实验现象 (11)

2.2 跑马灯实验 (13)

2.2.1 实验要求 (13)

2.2.2 实验步骤 (13)

2.2.3 实验现象 (13)

2.3 数字时钟显示实验 (14)

2.3.1 实验要求 (14)

2.3.2 实验步骤 (14)

2.3.3 实验现象 (14)

2.4 RS-232串口通信实验 (15)

2.4.1 实验要求 (15)

2.4.3 实验步骤 (15)

2.4.3 实验现象 (15)

2.5 PS/2键盘编码显示实验 (16)

2.5.1 实验要求 (16)

2.5.2 实验步骤 (16)

2.5.3 实验现象 (16)

2.6 PS/2鼠标移动显示实验 (17)

2.6.1 实验要求 (17)

2.6.2 实验步骤 (17)

2.6.3 实验现象 (17)

2.7 VGA彩条显示实验 (18)

2.7.1 实验要求 (18)

2.7.2 实验步骤 (18)

2.7.3 实验现象 (18)

最为重要的是,该开发板所带的演示程序全部是Verilog源代码程序,您买了该开发板之后,可以对照

代码边读边看硬件的实验结果,还可以在这些代码的基础上做二次开发。

我们所提供的实验和源代码程序全部都是经过验证过的,您可以在开发板上直接看实验的结果。

发货清单

ETL-002开发板套装提供下列的发货清单及图片:1)测试好的ETL-002 FPGA开发板一块。

2)USB线一条,用于从PC机USB端口取电。

3) Altera Byte Blaster II并行下载电缆线一条。

4) 标准串口电缆一根

5)学习光盘一张(原理图,开发板用户手册,开发板实验手册和实验程序,Altera全套Quartus II 9.0开发软件一套,Verilog/VHDL 学习资料等。

资料多多,不断丰富中……)

除了上述的标配的商品外,我们还提供了电源适配器,PS2鼠标,PS2键盘等可选配件。

如下图所示:。