集成电路设计练习题

集成电路技术集成电路工艺原理试卷(练习题库)(2023版)

集成电路技术集成电路工艺原理试卷(练习题库)1、用来做芯片的高纯硅被称为(),英文简称(),有时也被称为()。

2、单晶硅生长常用()和()两种生长方式,生长后的单晶硅被称为()。

3、晶圆的英文是(),其常用的材料是()和()。

4、晶圆制备的九个工艺步骤分别是()、整型、()、磨片倒角、刻蚀、()、清洗、检查和包装。

5、从半导体制造来讲,晶圆中用的最广的晶体平面的密勒符号是()、O 和()。

6、CZ直拉法生长单晶硅是把()变为()并且()的固体硅锭。

7、CZ直拉法的目的是()。

8、影响CZ直拉法的两个主要参数是O和()。

9、晶圆制备中的整型处理包括()、()和()。

10、制备半导体级硅的过程:1、();2、();3、O011、热氧化工艺的基本传输到芯片的不同部分。

77、多层金属化指用来连接硅片上高密度堆积器件的那些金属层。

78、阻挡层金属是淀积金属或金属塞,其作用是增加上下层材料的附着。

79、关键层是指那些线条宽度被刻蚀为器件特征尺寸的金属层。

80、传统互连金属线的材料是铝,即将取代它的金属材料是铜。

81、溅射是个化学过程,而非物理过程。

82、表面起伏的硅片进行平坦化处理,主要采用将低处填平的方法。

83、化学机械平坦化,简称CMP,它是一种表面全局平坦化技术。

84、平滑是一种平坦化类型,它只能使台阶角度圆滑和侧壁倾斜,但高度没有显著变化。

85、反刻是一种传统的平坦化技术,它能够实现全局平坦化。

86、电机电流终点检测不适合用作层间介质的化学机械平坦化。

87、在CMP为零的转换器。

133、CD是指硅片上的最小特征尺寸。

134、集成电路制造就是在硅片上执行一系列复杂的化学或者物理操作。

简而言之,这些操作可以分为四大基本类:薄膜135、人员持续不断地进出净化间,是净化间沾污的最大来源。

136、硅片制造厂可分为六个的区域,各个区域的照明都采用同一种光源以达到标准化。

137、世界上第一块集成电路是用硅半导体材料作为衬底制造的。

1+X集成电路理论练习题含参考答案

1+X集成电路理论练习题含参考答案一、单选题(共40题,每题1分,共40分)1、在电子产品测试中需保证测试环境稳定,其中使用环境稳定是指()。

A、使用人员操作得当B、硬件的工作参数稳定C、软件的工作参数稳定D、模拟真实用户使用时的场景正确答案:D2、以全自动探针台为例,关于上片的步骤,下列所述正确的是:( )。

A、打开盖子→花篮放置→花篮下降→花篮到位→花篮固定→合上盖子B、打开盖子→花篮放置→花篮到位→花篮下降→花篮固定→合上盖子C、打开盖子→花篮放置→花篮下降→花篮固定→花篮到位→合上盖子D、打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子正确答案:D答案解析:以全自动探针台为例,上片的步骤为:打开盖子→花篮放置→花篮固定→花篮下降→花篮到位→合上盖子。

3、转塔式分选机设备进行编带后,进入( )环节。

A、上料B、测试C、外观检查D、真空包装正确答案:C答案解析:转塔式分选机设备芯片检测工艺的操作步骤一般为:上料→测试→编带→外观检查→真空包装。

4、通常情况下,一个内盒中装入的DIP管装芯片( )颗。

A、3000B、1000C、5000D、2000正确答案:D答案解析:一般情况下,一个内盒中装入的DIP管装芯片2000颗。

5、元器件的引线直径与印刷焊盘孔径应有()的合理间隙。

A、0.1~0.4mmB、0.2~0.3mmC、0.1~0.3mmD、0.2~0.4mm正确答案:D6、在电子电路方案设计中最简单的显示平台是()。

A、OLEDB、LCDC、LEDD、数码管正确答案:C7、平移式分选机进行料盘上料时,在上料架旁的红色指示灯亮的含义是( )。

A、上料机构故障B、上料架上有料盘C、上料架上有空料盘D、上料架上没有料盘正确答案:B答案解析:平移式分选机进行料盘上料时,上料架上是否有料盘可以通过上料架旁的传感器进行检测。

当传感器指示灯为红色时,表明上料架上还有料盘,可以继续进行上料,当传感器指示灯为绿色时,表明上料架上无料盘,停止上料。

1+X集成电路理论习题及答案

1+X集成电路理论习题及答案1、在电子产品测试中需保证测试环境稳定,其中使用环境稳定是指()。

A、软件的工作参数稳定B、模拟真实用户使用时的场景C、使用人员操作得当D、硬件的工作参数稳定答案:B2、单晶硅锭切片后需要进行倒角,其目的是( )。

A、确定定位面B、产生精确的材料直径C、去除硅锭两端的不符合直径要求的部分D、去除硅片边缘锋利的棱角答案:D定位面研磨时为了确定硅锭的定位面。

径向研磨获得更精确的直径。

切割分段是为了去除硅锭两端的不符合直径要求的部分。

倒角是为了去除硅片边缘锋利的棱角使硅片边缘获得平滑的半径周线。

3、在使用万用表之前先应()。

A、机械调零B、选择合适的量程C、选择合适的挡位D、表笔短接答案:A4、下列描述正确的是()。

A、DIP和S0P封装一般为重力式分选B、PLCC和LCCC封装一般为重力式分选C、QFP和SOP封装一般为重力式分选D、BGA封装一般为重力式分选答案:A5、一般情况下,待编至( )颗时,需更换卷盘,并在完成编带的卷盘上贴上小标签,便于后期识别。

A、2000B、4000C、6000D、8000答案:B一般情况下,待编至4000颗左右时,需要更换卷盘,即一盘编带一般装有4000颗的芯片。

6、二氧化硅和碳在( )℃的环境下反应可生成粗硅。

A、100~200B、500~700C、700~900D、1600~1800答案:D因为硅—氧之间的键结很强,所以二氧化硅非常稳定,因此要用碳进行还原反应则需要很高的温度。

一般工业上将二氧化硅和碳在1600~1800℃的温度下反应,破坏硅—氧之间的键结,进而生成粗硅和一氧化碳。

7、重力式分选机进行芯片检测时,测试机对芯片测试完毕后,将检测结果通过()把结果传回分选机。

A、串口B、GPIBC、数据线D、VGA答案:B8、下面选项中不属于激光打字的优点的是()。

A、塑封体上易反复进行B、字迹清晰C、精度高D、不易擦除答案:A9、塑封一般采用()为塑封料。

数字集成电路习题

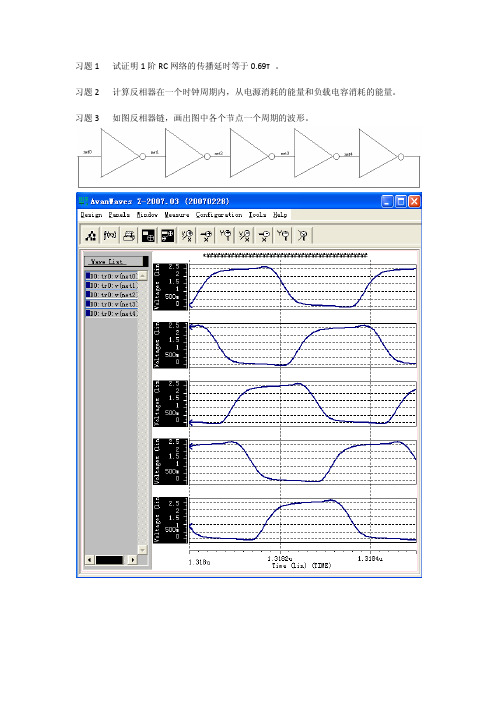

带入延迟公式可得,反相器链的延迟

t p N t p 0 (1

N

F

) 5 70 ps (1

5

2000 ) 1960 ps 2ns 1

c. 方法 a 的延迟时间

t p t p 0 (1

j 1

N

C g , j 1

C g , j

) t p 0 (1

解:VGS=VDS=2.5V,管子工作在饱和区。 栅沟电容 CGC=W*L*Cox=0.36um*0.24um*6fF/um2=0.52fF 栅与源漏区的交叠电容 Cov=CGSO=CGDO=W*Co=0.36um*0.31fF/um=0.11fF 栅电容 CG=CGC+2Cov=0.52 fF +2*0.11 fF=0.74fF 栅源电容 CGS=2CGC/3+Cov=2*0.52fF/3+0.11=0.46fF 栅漏电容 CGD=Cov=0.11fF 管子的源区和衬底都接地,所以源衬底扩散结处于零偏状态。有 Cs,bottom=W*LD*Cj0=0.36um*0.625um*2fF/um2=0.45fF Cs,sw=(W+2LD)*Cjsw0=(0.36um+2*0.625um)*0.28um/fF=0.45fF CSB= Cs,bottom + Cs,sw =0.45fF+0.45fF=0.9fF 管子的漏区接 2.5V,衬底接地,所以漏衬底扩散结处于反偏状态。有 CD,bottom=W*LD*Cj0/(1-VD/φ b)mj =0.36um*0.625um*2(fF/um2)/[1-(-2.5V)/0.9V]0.5 =0.23fF CD,sw=(W+2LD)*Cjsw0/(1-VD/φ bsw)mjsw =(0.36um+2*0.625um)*0.28(um/fF)/[1-(-2.5V)/0.9]0.44 =0.25fF CDB= CD,bottom + CD,sw =0.23fF+0.25fF=0.48fF

【精品】数字集成电路电路、系统与设计第二版课后练习题第六章CMOS组合逻辑门的设计

【精品】数字集成电路--电路、系统与设计(第二版)课后练习题第六章CMOS组合逻辑门的设计第六章 CMOS组合逻辑门的设计1.为什么CMOS电路逻辑门的输入端和输出端都要连接到电源电压?CMOS电路采用了MOSFET(金属氧化物半导体场效应管)作为开关元件,其中N沟道MOSFET(NMOS)和P沟道MOSFET(PMOS)分别用于实现逻辑门的输入和输出。

NMOS和PMOS都需要连接到电源电压,以使其能够正常工作。

输入端连接到电源电压可以确保信号在逻辑门中正常传递,输出端连接到电源电压可以确保输出信号的正确性和稳定性。

2.为什么在CMOS逻辑门中要使用两个互补的MOSFET?CMOS逻辑门中使用两个互补的MOSFET是为了实现高度抗干扰的逻辑功能。

其中,NMOS和PMOS分别用于实现逻辑门的输入和输出。

NMOS和PMOS的工作原理互补,即当NMOS导通时,PMOS截止,当PMOS导通时,NMOS截止。

这样的设计可以在逻辑门的输出上提供高电平和低电平的稳定性,从而提高逻辑门的抗干扰能力。

3.CMOS逻辑门的输入电压范围是多少?CMOS逻辑门的输入电压范围通常是在0V至电源电压之间,即在低电平和高电平之间。

在CMOS逻辑门中,低电平通常定义为输入电压小于0.3Vdd(电源电压的30%),而高电平通常定义为输入电压大于0.7Vdd(电源电压的70%)。

4.如何设计一个基本的CMOS逻辑门?一个基本的CMOS逻辑门可以由一个NMOS和一个PMOS组成。

其中,NMOS的源极连接到地,栅极连接到逻辑门的输入,漏极连接到PMOS的漏极;PMOS的源极连接到电源电压,栅极连接到逻辑门的输入,漏极连接到输出。

这样的设计可以实现逻辑门的基本功能。

5.如何提高CMOS逻辑门的速度?可以采取以下方法来提高CMOS逻辑门的速度:•减小晶体管的尺寸:缩小晶体管的尺寸可以减小晶体管的电容和电阻,从而提高逻辑门的响应速度。

•优化电源电压:增加电源电压可以提高晶体管的驱动能力,从而加快逻辑门的开关速度。

《超大规模集成电路设计》习题(含答案)

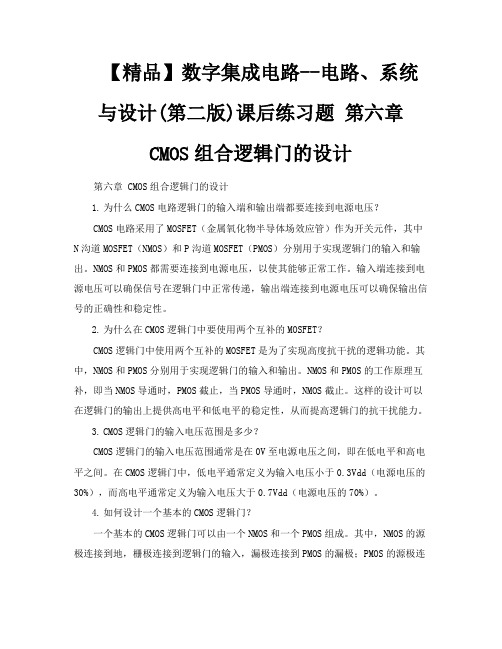

《超大规模集成电路设计》习题1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC ,SSI)•中规模集成电路(Medium Scale IC ,MSI)•大规模集成电路(Large Scale IC ,LSI) •超大规模集成电路(Very Large Scale IC ,VLSI)•特大规模集成电路(Ultra Large Scale IC ,ULSI)•巨大规模集成电路(Gigantic Scale IC ,GSI )2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI 减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI 内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得. 3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI 后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI 组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS 工艺制作CMOS 反相器的工艺流程过程。

4.在VLSI 设计中,对互连线的要求和可能的互连线材料是什么?5.在进行版图设计时为什么要制定版图设计规则?划分集成电路规模的标准数字集成电路类别MOS IC 双极IC 模拟集成电路SSI <102<100 <30 MSI 102~103100~500 30~100 LSI 103~105500~2000 100~300 VLSI 105~107>2000 >300 ULSI 107~109GSI >109在芯片尺寸尽可能小的前提下,使得即使存在工艺偏差也可以正确的制造出IC,尽可能地提高电路制备的成品率6.版图验证和检查主要包括哪些方面?u DRC(Design Rule Check):几何设计规则检查;对IC的版图做几何空间检查,保证能在特定的工艺条件下实现所设计的电路,并保证一定的成品率;u ERC(Electrical Rule Check):电学规则检查;检查电源(power)/地(ground)的短路,浮空的器件和浮空的连线等指定的电气特性;u LVS(Loyout versus Schematic):网表一致性检查;将版图提出的网表和原理图的网表进行比较,检查电路连接关系是否正确,MOS晶体管的长/宽尺寸是否匹配,电阻/电容值是否正确等;u LPE(Layout Parameter Extraction):版图寄生参数提取;从版图中提取晶体管的尺寸、结点的寄生电容、连线的寄生电阻等参数,并产生SPICE 格式的网表,用于后仿真验证;u POSTSIM:后仿真,检查版图寄生参数对设计的影响;提取实际版图参数、电阻、电容,生成带寄生量的器件级网表,进行开关级逻辑模拟或电路模拟,以验证设计出的电路功能的正确性和时序性能等,并产生测试向量。

(完整版)集成电路设计复习题及解答

集成电路设计复习题绪论1.画出集成电路设计与制造的主要流程框架。

2.集成电路分类情况如何?集成电路设计1.层次化、结构化设计概念,集成电路设计域和设计层次2.什么是集成电路设计?集成电路设计流程。

(三个设计步骤:系统功能设计逻辑和电路设计版图设计)3.模拟电路和数字电路设计各自的特点和流程4.版图验证和检查包括哪些内容?如何实现?5.版图设计规则的概念,主要内容以及表示方法。

为什么需要指定版图设计规则?6.集成电路设计方法分类?(全定制、半定制、PLD)7.标准单元/门阵列的概念,优点/缺点,设计流程8.PLD设计方法的特点,FPGA/CPLD的概念9.试述门阵列和标准单元设计方法的概念和它们之间的异同点。

10.标准单元库中的单元的主要描述形式有哪些?分别在IC设计的什么阶段应用?11.集成电路的可测性设计是指什么?Soc设计复习题1.什么是SoC?2.SoC设计的发展趋势及面临的挑战?3.SoC设计的特点?4.SoC设计与传统的ASIC设计最大的不同是什么?5.什么是软硬件协同设计?6.常用的可测性设计方法有哪些?7. IP的基本概念和IP分类8.什么是可综合RTL代码?9.么是同步电路,什么是异步电路,各有什么特点?10.逻辑综合的概念。

11.什么是触发器的建立时间(Setup Time),试画图进行说明。

12.什么是触发器的保持时间(Hold Time),试画图进行说明。

13. 什么是验证,什么是测试,两者有何区别?14.试画图简要说明扫描测试原理。

绪论1、 画出集成电路设计与制造的主要流程框架。

2、集成电路分类情况如何?集成电路设计1. 层次化、结构化设计概念,集成电路设计域和设计层次分层分级设计和模块化设计.将一个复杂的集成电路系统的设计问题分解为复杂性较低的设计级别,⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎪⎪⎪⎪⎪⎪⎩⎪⎪⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎪⎪⎪⎩⎪⎪⎪⎪⎨⎧⎩⎨⎧⎪⎩⎪⎨⎧按应用领域分类数字模拟混合电路非线性电路线性电路模拟电路时序逻辑电路组合逻辑电路数字电路按功能分类GSI ULSI VLSI LSI MSI SSI 按规模分类薄膜混合集成电路厚膜混合集成电路混合集成电路B iCMOS B iMOS 型B iMOS CMOS NMOS PMOS 型MOS双极型单片集成电路按结构分类集成电路这个级别可以再分解到复杂性更低的设计级别;这样的分解一直继续到使最终的设计级别的复杂性足够低,也就是说,能相当容易地由这一级设计出的单元逐级组织起复杂的系统。

1+X集成电路理论模拟练习题+答案

1+X集成电路理论模拟练习题+答案一、单选题(共40题,每题1分,共40分)1、芯片完成编带并进行清料后,会将完成编带的芯片放在( )上。

A、已检查品货架B、待检查品货架C、待外检货架D、合格品货架正确答案:B答案解析:芯片完成编带并进行清料后,将将编带盘、随件单放入对应的中转箱中,并将中转箱放在待检查品货架上等待外观检查。

2、利用平移式分选设备进行芯片检测时,芯片在该区域的操作完成后会进入()区域。

A、分选B、待测C、上料D、测试正确答案:A3、晶圆检测工艺对环境的其中一项——温度的要求范围是( )℃。

A、22±3B、20±5C、25±3D、20±3正确答案:A答案解析:晶圆检测工艺对环境的要求:测试车间符合10万级洁净区标准,温度常年保持在22±3℃,湿度保持在45±15%。

4、编带过程中,在进行热封处理后,需要进行( )环节。

A、芯片放入载带B、密封C、编带收料D、光检正确答案:C答案解析:转塔式分选机进行编带的步骤是:芯片光检→载带移动→热封处理→编带收料→清料。

5、平移式分选机设备的上料步骤正确的是:( )。

A、待测芯片上料→吸嘴转移芯片→空料盘替换B、吸嘴转移芯片→待测芯片上料→空料盘替换C、空料盘替换→待测芯片上料→吸嘴转移芯片D、吸嘴转移芯片→空料盘替换→待测芯片上料正确答案:A答案解析:平移式分选机设备的上料步骤为:待测芯片上料→吸嘴转移芯片→空料盘替换。

6、单晶炉中籽晶轴的作用是( )。

A、保证炉内温度均匀分布及散热B、带动籽晶上下移动和旋转C、起支撑作用D、提供一个原子重新排列标准正确答案:B答案解析:籽晶轴的作用是带动籽晶上下移动和旋转;籽晶的作用是提供一个原子重新排列的标准;坩埚外的高纯石墨坩埚托起支撑作用;炉腔可以保证炉内温度均匀分布及散热。

7、晶圆贴膜过程中,需要外加一个(),它起到支撑的作用。

A、晶圆基底圆片B、晶圆贴片环C、蓝膜支撑架D、固定挂钩正确答案:B答案解析:在贴膜过程中,需要外加一个厚度与晶圆一致但环内径比晶圆直径大的金属环,也就是晶圆贴片环。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

集成电路设计练习题2009

1、说明一个半导体集成电路成本的组成。

2、简述CMOS工艺流程。

简述CMOS集成电路制造的过程中需要重复进行的工艺步骤。

3、描述你对集成电路工艺的认识。

列举几种集成电路典型工艺。

工艺上常提到0.25,0.18指的是什么?简述CMOS工艺技术的发展趋势。

4、你知道的集成电路设计的表达方式有哪几种?

5、现有一用户需要一种集成电路产品,要求该产品能够实现如下功能:y=lnx 其中,x为4位二进制整数输入信号。

y为二进制小数输出,要求保留两位小数。

电源电压为3~5v 假设公司接到该项目后,交由你来负责该产品的设计,试讨论该产品的设计全程。

6、请谈谈对一个系统设计的总体思路。

针对这个思路,你觉得应该具备哪些方面的知识?

7、描述你对集成电路设计流程的认识。

8、集成电路前端设计流程,后端设计流程,相关的工具。

9、从RTL synthesis到tape out之间的设计flow,并列出其中各步使用的tool.

10、简述FPGA等可编程逻辑器件设计流程。

11、简述半定制数字电路的设计流程。

12、简要说明并比较数字集成电路几种不同的实现方法。

13、什么是集成电路的设计规则。

14、同步电路和异步电路的区别是什么?

15、画出CMOS电路的晶体管级电路图,实现Y=AB+C(D+E)

16、在CMOS电路中,要有一个单管作为开关管精确传递模拟低电平,这个单管你会用P管还是N 管,为什么?

17、硅栅COMS工艺中N阱中做的是P管还是N管,N阱的阱电位的连接有什么要求?

18、名词解释:VLSI, CMOS, EDA, VHDL, DRC, LVS, DFT, STA

19、画出CMOS与非门的电路,并画出波形图简述其功能。

20、latch与register的区别,为什么现在多用register。

行为级描述中latch如何产生的。

21、FPGA和ASIC的概念,他们的区别。

22、Please explain how we describe the resistance in semiconductor. Compare the resistance of a metal, poly and diffusion in traditional CMOS process.(威盛笔试题circuit design-beijing-03.11.09)

23、Please show the CMOS inverter schematic, layout and its cross section with P-well process. Plot its transfer curve (Vout-Vin). And also explain the operation region of PMOS and NMOS for each segment of the transfer curve?

24、Please draw the transistor level schematic of a CMOS 2 input AND gate and explain which input has faster response for output rising edge.(less delay time)。

25、To design a CMOS inverter with balance rise and fall time, please define the ration of channel width of PMOS and NMOS and explain?

26、为什么一个标准的倒相器中P管的宽长比要比N管的宽长比大?

27、画出CMOS晶体管的CROSS-OVER图(应该是纵剖面图),给出所有可能的传输特性和转移特性。

(Infineon笔试试题)

28、目前集成电路产业发展到IP/Soc阶段,你是怎么理解IP复用技术的?

29、可编程逻辑器件在现代电子设计中越来越重要,请问:a) 你所知道的可编程逻辑器件有哪些?

b) 试用VHDL或VERILOG描述8位D触发器逻辑。

30、评价数字集成电路设计质量的指标有哪些?他们分别用什么来表示(或衡量)?

31、你认为目前数字集成电路设计中亟待解决的问题有哪些?为什么?

32、MOSFET本征寄生电容的来源是什么。

计算一个具有以下参数的NMOS管零偏置时所有相关电容的值。

33、特征尺寸的不断缩小对MOS管的工作特点和性质以及间接的对数字电路设计指标等有什么影响。

34、工艺尺寸的缩小对互连线有什么影响?

35、集成电路的导线引哪些寄生参数效应,他们对电路的特性有什么影响?

36、叙述静态CMOS的重要特性。

37、降低电源电压对CMOS管稳定性有何影响。

38、推导反相器一阶传播延时的表达式(一阶分析),说明减小一个门的传播延时的方法。

39、讨论晶体管尺寸与能耗之间的关系。

40、对于由N个反相器组成的具有固定输入和输出电容的反相器链,为使通过反相器链的延时最小,如何确定反向器链的尺寸及级数。

41、CMOS电路的功耗与哪些因素有关,如何降低电路的功耗?

42、如何降低大扇入电路的延时?

43、逻辑门的动态功耗可以通过减小它的实际电容和开关活动性来降低,降低开关活动性的设计技术有哪些?

44、动态逻辑门有哪些特性?

45、时序逻辑电路(锁存器和寄存器)有静态和动态两类,试对这两类电路进行比较。

46、流水线是优化时序电路的一种重要方法,NORA-CMOS逻辑形式的流水线结构有哪些特性。

47、一般数字信号处理器由哪些模块构成,对各模块进行简要说明。

48、说明模拟和验证的区别。

49、什么是Setup 和Holdup时间?setup和holdup时间,区别

50、解释setup time和hold time的定义和在时钟信号延迟时的变化。

51、解释setup和hold time violation,画图说明,并说明解决办法。

52、如何解决亚稳态。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

53、时钟周期为T ,触发器D1的建立时间最大为T1max ,最小为T1min 。

组合逻辑电路最大延迟为T2max ,最小为T2min 。

问触发器D2的建立时间T3和保持时间应满足什么条件。

54、给出某个一般时序电路的图,有Tsetup, Tdelay, Tck->q,还有clock 的delay, 写出决定最大时钟的因素,同时给出表达式。

55、给出一个门级的图,又给了各个门的传输延时,问关键路径是什么,还问给出输入,使得输出依赖于关键路径。

56、CMOS 单元负载较大的电容时,只有提高W ,这样会使W*L 增加,相对前级又时一个大电容,如何解决这一矛盾?

57、在设计数字处理器IC 时可采用哪些方法或技术以降低数据通路部分的功耗。

58、为什么数字处理器IC 中数据通路常常组织成位片式结构?

59、数字处理器IC 中加法器对计算结构的性能有重要的影响,为提高多位二进制加法器的运算速度,可以采用哪些方法或技术?

60、如图,已知时序参数:寄存器最小延时

(tc-q,cd )和最大传播延时(tc-q ),寄存器的建立时间(tsetup )和保持时间(thold ),组合逻

辑的最小延时(tlogic,cd )和最大延时(tlogic ),

时钟CLK1和CLK2上升沿相对于全局参考时钟的位置tclk1和tclk2。

时钟偏差(δ)和时钟抖动(tjitter )。

求:不考虑时钟偏差和时钟抖动时满足寄存器建立时间和保持时间要求的时序约束表达式,以及考虑时钟偏差和时钟抖动时满足寄存器建立时间和保持时间要求的时序约束表达式。

61、时钟偏差和时钟抖动是如何产生的,哪些因素可以造成时钟偏差,哪些可造成时钟抖动。

减少时钟偏差和抖动的设计技术有哪些?

c -q t c -q,c

d t su, t hold logic

t logic,cd。