ARM9-2410的CPLD设计说明-V3

基于ARM9处理器S3C2410的LCD显示系统设计,ARM.

基于ARM9处理器S3C2410的LCD显示系统设计,ARM处理器,S3C2410,

TFT-LCD,显示控制

引言S3C2410是三星公司生产的基于ARM920T内核的RISC微处理器,其主频可达203MHz[1],适用于信息家电、PDA、手持设备、移动终端等领域,本文介绍了基于S3C2410的显示系统的硬件电路及驱动软件设计方法。

TFT-LCD模块的时序要求本显示模块选用的LQ080V3DG01是Sharp公司的TFT-LCD器件,该器件的分辨率为640×480,控制时序图如图1所示,时间参数如表1所列[2]。

引言

S3C2410是三星公司生产的基于ARM920T内核的RISC微处理器,其主频可达203MHz[1],适用于信息家电、PDA、手持设备、移动终端等领域,本文介绍了基于S3C2410的显示系统的硬件电路及驱动软件设计方法。

TFT-LCD模块的时序要求

本显示模块选用的LQ080V3DG01是Sharp公司的TFT-LCD器件,该器件的分辨率为640×480,控制时序图如图1所示,时间参数如表1所列[2]。

第3章ARM9芯片S3C2410片上资源

除用户模式以外,其余的所有6种模式特权模式。 每种工作模式下均有其附加的某些寄存器,因此,

即使有异常情况发生,异常模式下的处理程序也不 至于破坏用户模式的数据及状态。

ARM9处理器有两种工作状态:ARM状态和Thumb 状态。

3.0.3 I/O端口的访问方式

I/O端口的访问有两种方式,一种是端口地址 和存储器统一编址,即存储器映射方式;另一 种是I/O端口地址与存储器分开独立编址,即 I/O映射方式(独立编址)。

ARM9体系结构使用存储器映射方式实现I/O端 口的访问。由于存储器映射方式是为每个I/O 端口分配特定的存储器地址,当从这些地址读 出或向这些地址写入时,实际上就完成了I/O 功能。即从存储器映射的I/O加载即是输入, 而向存储器映射的I/O地址存储即是输出。

3.1.3 S3C2410处理器管理系统

支持大端(Big Endian)/小端(Little Endian)模式; 地址空间为每个内存块128MB(一共1CB),每个内存

块支持8/16/32位数据总线编程; 8个内存块,6个用于ROM、SRAM和其它,2个用于

ROM/SRAM/SDRAM; 1个起始地址和大小可编程的内存块 (Bank7); 7个起始地址固定的内存块(Bank0~Bank6); 所有内存块可编程寻址周期; 支持SDRAM自动刷新模式; 支持多种类型ROM启动,包括NOR/NAND Flash、

③ 分支指令:ARM9和ARM7的分支指令周期相同,没 有采用分支预测。

2.ARM9体系结构的五级流水线

(1)取指:从存储器中取出指令放入指令流水线 (fetch)。

ARM9S3C2410x中文datasheet资料(绝对完整版)03S3c2410中断异常处理概述

使用中断的步骤:1、当发生中断IRQ时,CPU进入“中断模式”,这时使用“中断模式”下的堆栈;当发生快中断FIQ时,CPU进入“快中断模式”,这时使用“快中断模式”下的堆栈。

所以在使用中断前,先设置好相应模式下的堆栈。

2、对于“Request sources(without sub -register)”中的中断,将INTSUBMSK寄存器中相应位设为03、将INTMSK寄存器中相应位设为04、确定使用此的方式:是FIQ还是IRQ。

a.如果是FIQ,则在INTMOD寄存器设置相应位为1b.如果是IRQ,则在RIORITY寄存器中设置优先级使用中断的步骤:5、准备好中断处理函数,a.中断向量:在中断向量设置好当FIQ或IRQ被触发时的跳转函数,IRQ、FIQ的中断向量地址分别为0x00000018、0x0000001c b.对于IRQ,在跳转函数中读取INTPND寄存器或INTOFFSET 寄存器的值来确定中断源,然后调用具体的处理函数c.对于FIQ,因为只有一个中断可以设为FIQ,无须判断中断源d.中断处理函数进入和返回6、设置CPSR寄存器中的F-bit(对于FIQ)或I-bit(对于IRQ)为0,开中断s3c2410 中断异常处理在进入正题之前,我想先把ARM920T的异常向量表(Exception Vectors)做一个简短的介绍。

:]ARM920T的异常向量表有两种存放方式,一种是低端存放(从0x00000000处开始存放),另一种是高端存放(从0xfff000000处开始存放)。

关于为什么要分两种方式进行存放这点我将在介绍MMU的文章中进行说明,本文采用低端模式。

ARM920T能处理有8个异常,他们分别是:Reset,Undefined instruction,Software Interrupt,Abort (prefetch),Abort (data),Reserved,IRQ,FIQ下面是某个采用低端模式的系统源码片段:/****************************************************** ***********************_start:b Handle_Resetb HandleUndefb HandleSWIb HandlePrefetchAbortb HandleDataAbortb HandleNotUsedb HandleIRQb HandleFIQ…..…..other codes…...******************************************************* **********************/上面这部分片段一般出现在一个名叫“head.s”的汇编文件的里,“b Handle_Reset”这条语句就是系统上电之后运行的第一条语句。

ARM9S3C2410时钟和功率管理

ARM9S3C2410时钟和功率管理概述时钟和功率治理模块由三部分组成:时钟操纵,USB操纵和功率操纵。

S3C2410A的时钟操纵逻辑能够产生系统所需要的时钟,包括CPU的FCLK,AHB总线接口的HCLK,和APB总线接口的PCLK。

S3C2410A有两个PLL,一个用于FCLK,HCLK,PCLK,另一个用于USB模块(48MHZ)。

时钟操纵逻辑能够由软件操纵不将PLL连接到各接口模块以降低处理器时钟频率,从而降低功耗。

S3C2410A有各种针对不同任务提供的最佳功率治理策略,功率治理模块能够使系统工作在如下4种模式:正常模式,低速模式,闲暇模式和掉电模式。

正常模式:功率治理模块向CPU和所有外设提供时钟。

这种模式下,当所有外设都开启时,系统功耗将达到最大。

用户能够通过软件操纵各种外设的开关。

例如,假如不需要定时器,用户能够将定时器时钟断开以降低功耗。

低速模式:没有PLL的模式。

与正常模式不同,低速模式直截了当使用外部时钟(XTIpll或者EXTCLK)作为FCLK,这种模式下,功耗仅由外部时钟决定。

闲暇模式:功率治理模块仅关掉FCLK,而连续提供时钟给其他外设。

闲暇模式能够减少由于CPU核心产生的功耗。

任何中断要求都能够将CPU从中断模式唤醒。

掉电模式:功率治理模块断开内部电源。

因此CPU和除唤醒逻辑单元以外的外设都可不能产生功耗。

要执行掉电模式需要有两个独立的电源,其中一个给唤醒逻辑单元供电,另一个给包括CPU在内的其他模块供电。

在掉电模式下,第二个电源将被关掉。

掉电模式能够由外部中断EINT[15:0]或RTC唤醒。

功能描述时钟结构图7-1描述了时钟架构的方块图。

主时钟源由一个外部晶振或者外部时钟产生。

时钟发生器包括连接到一个外部晶振的振荡器和两个PLL(MPLL和UPLL)用于产生系统所需的高频时钟。

时钟源选择表7-1描述了模式操纵引脚(OM3和OM2)和选择时钟源之间的对应关系。

OM[3:2]的状态由OM3和OM2引脚的状态在nRESET的上升沿锁存得到。

arm9 s3c2410实验环境搭建

实验1:arm9 s3c2410实验环境搭建实验目的:学会ADS 软件的安装,为后续试验提供软环境实验内容:1 安装ADS 软件软件安装结束,可以进行第二部分ADS 的应用练习。

第二部分:ADS应用1、通过桌面快捷方式或者开始菜单来打开软件了。

2.在ADS1.2的开发环境中,新建一个工程,此步骤有二种方法,一是点击工具栏中NEW 按钮,二是在FILE菜单中选择NEW菜单:在工程中为用户提供了七种工程模板,1.ARM Executable Image:用于由ARM指令的代码生成一个ELF格式的可执行映射文件2.ARM Object Library:用于由ARM指令的代码生成一个armar格式的目标文件库;3.Emety project:用于创建一个不包含任何库或源文件的工程;4.Makefile Importer Wizard:用于将Visual C的nmake或GUN make 文件转入到CodeWarrior IDE工程文件中;5.Thumb ARM Interworking Image:用于由ARM指令和Thumb指令的混合代码生成一个可执行的ELF映射文件;6.Thumb Executalbe Image:用于由Thumb指令的代码生成一个ELF格式的可执行代码;7.Thumb Object Library:用于由Thumb指令的代码生成一个armar格式的目标文件库;我选择了第一种工程模板,在Project Name中填写工程的名字,这里我填写了Holle,点击Location的文本框的SET按钮,我们可选择工程的保存路径,完成后点击确定,就会产生一个一个Holle.MCP文件的窗口。

Holle.MCP窗口有三个标签选项,分别是Files、Link Order、Targets,默认的是Files 标签,在此标签下点击右键就可添加源文件到工程中,如果没有源文件,我们可新建一个源文件,我们点击File菜单下的NEW菜单,就可以生成一个新的源文件的窗口,点击File标签,并在File name下面的文本框中填写文件名,我填写的是Holle.s(s为汇编程序的后缀)。

ARM9硬件平台设计

主时钟 电路

RTC时钟 电路

主时钟及USB 时钟滤波

最小系统的设计

时钟电路

1、根据S3C2410X的最高工作频率以及PLL电路的工作方式, 选择12MHz的无源晶振。12MHz的晶振频率经过S3C2410X片内 的PLL电路倍频后,可达到202.8MHz的频率。

4通道PWM定时器及一个内部定时器;

117个通用I/O口; 24个外部中断源;

两个USB主/一个USB从;

8通道10位ADC;

实时时钟及看门狗定时器等。

S3C2410X概述

S3C2410X特性

内核:1.8V I/O及存储器 : 3.3V 电源管理模式:Normal、Slow、Idle、Power off 272-FBGA

最小系统的设计

最小系统简介

1、一个嵌入式处理器是不能独立工作的,必须给它 供电、加上时钟信号、提供复位信号,如果芯片没 有片内程序存储器,则还要加上存储器系统,然后 嵌入式处理器才可能工作。

2、这些提供嵌入式处理器运行所必须的条件的电路 与嵌入式处理器共同构成了这个嵌入式处理器的最 小系统。

3、大多数基于ARM9处理器核的微控制器都有调试接 口,这部分在芯片实际工作时不是必需的,但因为 这部分在开发时很重要,所以把这部分也归入到最 小系统中。

S3C2410X概述

S3C2410X的引脚分布图

S3C2410X的存储器映射

S3C2410X的引脚信号描述

总线控制信号

S3C2410X的引脚信号描述

SDRAM/SRAM

S3C2410X的引脚信号描述

NAND Flash

S3C2410X的引脚信号描述

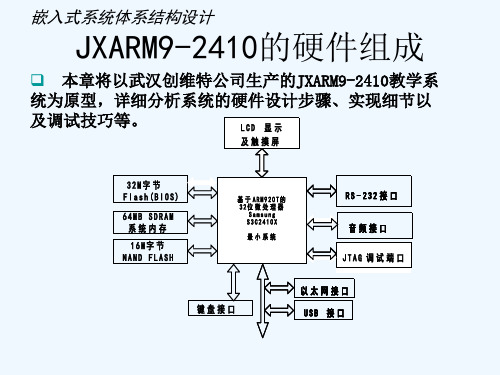

jxarm92410课程设计

jxarm92410课程设计一、教学目标本课程的教学目标是使学生掌握JXARM92410微控制器的原理和编程方法,能够运用该微控制器设计简单的嵌入式系统。

具体分解为以下三个目标:1.知识目标:使学生了解JXARM92410微控制器的内部结构、工作原理和指令系统;掌握C语言在微控制器编程中的应用;理解嵌入式系统的设计流程。

2.技能目标:培养学生具备JXARM92410微控制器的程序设计能力,能够独立完成简单的嵌入式系统设计;培养学生运用C语言进行微控制器编程的能力。

3.情感态度价值观目标:培养学生对嵌入式系统的兴趣,提高学生独立思考和解决问题的能力,培养学生的创新精神和团队合作意识。

二、教学内容本课程的教学内容主要包括以下几个部分:1.JXARM92410微控制器的基本原理:包括内部结构、工作原理、指令系统等。

2.C语言在微控制器编程中的应用:包括C语言的基本语法、编程技巧、编译环境等。

3.嵌入式系统设计:包括嵌入式系统的设计流程、硬件选型、软件设计等。

4.实例分析:分析一些典型的嵌入式系统设计案例,使学生能够更好地理解和掌握嵌入式系统的设计方法。

三、教学方法为了达到本课程的教学目标,我们将采用以下教学方法:1.讲授法:讲解JXARM92410微控制器的基本原理、C语言编程基础等理论知识。

2.讨论法:学生进行小组讨论,探讨嵌入式系统设计中的问题和解决方案。

3.案例分析法:分析典型的嵌入式系统设计案例,引导学生掌握设计方法。

4.实验法:安排学生进行实验,使学生能够将理论知识应用于实际操作。

四、教学资源为了保证本课程的顺利进行,我们将准备以下教学资源:1.教材:《JXARM92410微控制器原理与编程》2.参考书:《嵌入式系统设计原理与应用》等3.多媒体资料:包括课件、教学视频等4.实验设备:JXARM92410微控制器开发板、编程器、实验器材等五、教学评估本课程的教学评估将采用多元化评价方式,全面客观地评价学生的学习成果。

ARM9 S3C2410开发板简介

Page 1 of 13S3C2410开发板数据手册强烈推荐这款2410开发板 超值提供ARM9 2410开发板+全新三星原装3.5三星TFT 带驱动板和触摸 1400元 LCD 单卖 550元 全新三星原装3.5三星TFT 带驱动板和触摸 GPRS 模块单卖 400元LCD 简介:生产商: SamSung 型 号: L TV350 成 色: 全新原装特 性: 26万色TFT 、分辨率320*240、带触摸屏、LED 背光 接 口: RGB/CPU 总线可选, 直接接S3C2410 附 件: 电压驱动板,2.0mm 双排插引出接口ARM9 2410硬件平台综述ARM9 2410平台由核心板(Core-Board)和底板(Bottom-Board)以及3.5寸LCD(带触摸)组成。

如下图所示:板子背面示意图:● ARM2410 的主要特点1、Core-Board(核心板)CPU: Samsung的S3C2410x处理器,工作频率达203MHz;FLASH ROM: 64MB Nand Flash,可选配为各种容量8位的NANDFLASH;NOR FLASH(SST39VF1601)提供2MBNor Flash;SDRAM : 64M (Samsung K4S561632H-Tc75) 2片4Banks×4Mbits ×16bits SDRAMPC100/PC133兼容;RTC 实时时钟: 外接32.768KHz的晶振,带有备份电池,可保持时钟NAND FLASH --NOR FLASH 启动选择开关两个I/O 口连接两个LED,方便用户调试自己的程序2、Bottom-Board (底板)LCD 接口: 支持各种TFT LCD(50PIN2.0排针)触摸屏接口:可接四线电阻式触摸屏;串口:两个RS232串口;1路TTL电平接口GPRS/GSM接口: SIMCOM公司GSM/GPRS模块USB Device接口: 1个DEVICE接口(USB 1.1协议)SPI 接口IIC总线接口ADC模数转换接口: 4路10位AD两个USB HOST: 1个USB Host A型接口(USB1.1协议),1个USBHost B型接口(USB1.1协议);SD/MMC 接口: 支持SD卡、同时兼容MMC卡;JTAG接口:标准ARM 20针JTAG&&Wiggle&&ICE 接口;IIS :采用UDA1341TS IIS 接口(立体声输出,MIC 输入),外部中断接口: 8路外部中断输入网卡:提供10M Ethernet芯片CS8900A,采用集成隔离变压器的RJ45接口,并带有Page 2 of 13Page 3 of 13ACT 、 LINK 指示灯蜂鸣器: 带驱动电路。

chapt03----ARM9 S3C2410处理器及实验系统概述

ARM微处理器的选型原则2 ARM微处理器的选型原则2 微处理器的选型原则

--系统的工作频率 --系统的工作频率

系统的工作频率在很大程度上决定了ARM微处理器 的处理能力。ARM7系列微处理器的典型处理速度为 0.9MIPS/MHz,ARM9系列微处理器的典型处理速度为 1 . 1 MIPS/MHz, 常 见 的 ARM9 的 系 统 主 时 钟 频 率 为 100MHz-233MHz ARM10 100MHz-233MHz,ARM10最高可以达到700MHz。不 700MHz 同芯片对时钟的处理不同,有的芯片只需要一个主时 钟频率,有的芯片内部时钟控制器可以分别为ARM核 和USB、UART、DSP、音频等功能部件提供不同频率 的时钟。 后面我们所讨论的S3C2410时钟频率为200MHz以上, 若更换成兼容的S3C2440时钟频率最高可达到400MHz。

• • • •

教学实验系统组成2 教学实验系统组成

• • • • •

SD卡主机(MMC)接口 SMC卡(Smart media card)接口 JTAG 接口(MULTI-ICE兼容) 实时时钟(RTC)单元 IIC总线接口(板载IIC接口的EEPROM 24C16 和IIC接口的数码管 驱动ZLG7290) • ADC接口,芯片内部集成8通道10bit ADC,板载输入有:

• CPU S3C2410X:16-/32-bit RISC 微处理器,通过200P SODIMM •

广嵌 ARM9 GEC2410v1.1 说明书

ARM9 GEC2410v1.1用户手册广东省嵌入式软件公共技术中心/广东省嵌入式软件公共技术中心简介(美的集团美泰科技有限公司)广东省嵌入式软件公共技术中心(简称“GEC”)是一个面向信息家电、汽车电子、数控机床、消费电子、网络通讯等嵌入式新技术、新产品领域的技术与产业中心。

目前,GEC已形成嵌入式技术与产品解决方案、嵌入式系统评测认证、技术培训服务和电子商务平台四大业务体系,以“专业诚信、开拓创新、行业引领、齐商共赢”的中心精神为指导,努力为客户的技术创新和产品升级提供支持。

在开发板系列产品方面,GEC目前已经形成了完善的产品体系结构,包括以下四个方面:1 多样化的开发板产品:目前GEC开发板系列产品包括2410开发板、2440开发板、实验箱等一系列产品,目标是向有志于从事嵌入式学习及开发的高校、学生、工程师以及企业客户提供完善的嵌入式开发平台的整体解决方案。

2 严谨的产品评测过程:本中心设立了专门的嵌入式产品评测团队,拥有完善的评测设备,保证每个出厂产品都经过严谨的评测过程,从而保证了产品的质量。

3 完善的售后服务:开发板产品出现质量问题10天包换,12个月免费保修。

保修时间之长堪称国内之最。

4 强大的技术支持:本中心拥有30多人的技术研发团队,拥有强大的技术研发力量,技术领域涉及到嵌入式开发的各个方面,为开发板客户提供全面的技术支持。

目录第一章 GEC2410 开发板套件介绍 (5)1.1 GEC2410 开发板外观 (5)1.2 GEC2410 开发板硬件构成 (5)1.3 硬件资源分配 (6)1.4 开发套件包含的内容 (8)1.5 操作系统支持的驱动 (9)第二章 GEC2410 开发板使用 (10)2.1 GEC2410开发板快速使用入门 (10)2.2 启动 LINUX和WINCE (13)2.3 GEC2410 的 BIOS 功能说明 (17)2.4 非操作系统下的外围资源测试 (19)2.5 Linux 操作系统下的外围资源测试 (30)2.6 用 SJF2410 工具将 BIOS 烧写到 NAND FLASH (32)第三章 烧写和启动 linux (37)3.1 烧写 LINUX 内核 (37)3.2 烧写根文件系统 (40)3.3 启动 LINUX (42)第四章 烧写 WINCE 和启动 WINCE (47)4.1 下载运行 WINCE (47)4.2 烧写 WINCE (49)4.3 自启动 WINCE (50)第五章用 ARM仿真器调试 GEC2410 (53)第六章嵌入式linux (60)6.1 安装工具链 (60)6.2 配置移植linux内核 (60)6.3 制造根文件系统 (63)65 第七章嵌入式GUI--Qt开发 ...................................................................................................7.1 Qt/Embedded开发环境的安装 (65)7.2 Qt/Embedded开发工具的安装 (65)7.2.1 tmake的安装... . .. ........... ........... ........... ........... (65)7.2.2 Qt X11 的安装... . .. ........... ........... . (65)7.2.3Qt/Embedded 安装... . (68)7.2.4交叉编译qtopia................. ........... ........... ........... (68)7.3 Qt/Embedded应用开发实例 (69)7.3.1 在ARM上的qt/embedded应用程序实例... . .. (69)7.3.2 在ARM上的qt/embedded应用程序实例 (72)第八章嵌入式WINCE (74)8.1 WINCE的安装 (74)8.1.1 安装开发环境 ................ .. (74)8.1.2 安装目录 ................ (74)8.1.3 构建新的平台、编译 (78)8.2 WINCE的image的运行 (90)8.3 通过以太网烧写WINCE映象文件 (90)8.4 在WINCE和桌面系统之间建立通讯连接 (100)第一章 GEC2410 开发板套件介绍1.1 GEC2410 开发板外观1.2 GEC2410 开发板硬件构成硬件功能介绍:◆ 采用三星公司的 S3C2410,主频可达 203MHz;◆ 64M 字节的 SDRAM,由两片 K4S561632 组成,工作在 32 位模式下;◆ 64M 字节 NAND Flash,采用的是 K9F1208,可以兼容 16M,32M 或 128M 字节;1M字节NOR Flash;◆ 10M 以太网接口,采用的是 CS8900Q3,带传输和连接指示灯;◆ LCD 和触摸屏接口;◆ 2 个 USB HOST,S3C2410 内置的,符合 USB 1.1,注意这两个 USB HOST 接口是复用的◆ 一个 USB Device,S3C2410 内置的,符合 USB 1.1;◆ 支持音频输入和音频输出,音频模块由 S3C2410 的 IIS 音频总线接口和 UDA1341 音频编码解码器组成,板上还集成了一个 MIC,用于音频输入;◆ 2 路 UART 串行口,波特率可高达 115200bps,并具有 RS232 电平转换电路;◆ SD 卡接口,兼容 SD Memory Card Protocol 1.0 和 SDIO Card Protocol 1.0;◆ Embedded-ICE (20 脚标准 JTAG)接口和并口式 JTAG 接口,支持 ADS,SDT 软件的下载◆ 和调试以及 FLASH 的烧写;◆ 串行 EEPROM : AT24C02 4Kbytes EEPROM,IIC 接口;◆ 蜂鸣器,4 个 LED 灯;◆ 16 个按键◆ 开关电源,分布式电源供电,3V 锂电池,提供 CPU 内置 RTC 操持电源;1.3 硬件资源分配1.3.1 地址空间分配以及片选信号定义S3C2410 支持两种启动模式:一种是从 NAND FLASH 启动; 一种是从外部 nGCS0 片选的 Nor Flash 启动(gec2410v1.00开发板没有Nor Flash)。

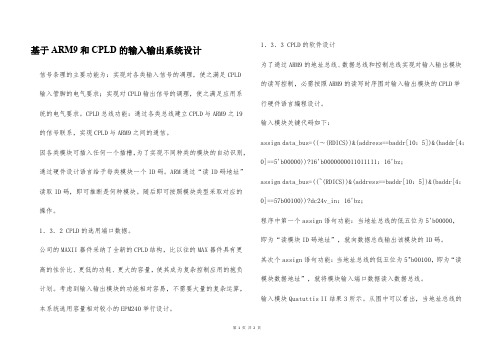

基于ARM9和CPLD的输入输出系统设计

基于ARM9和CPLD的输入输出系统设计信号条理的主要功能为:实现对各类输入信号的凋理,使之满足CPLD 输入管脚的电气要求;实现对CPLD输出信号的调理,使之满足应用系统的电气要求。

CPLD总线功能:通过各类总线建立CPLD与ARM9之19的信号联系,实现CPLD与ARM9之间的通信。

因各类模块可插入任何一个插槽,为了实现不同种类的模块的自动识别,通过硬件设计语言给予每类模块一个ID码。

ARM通过“读ID码地址”读取ID码,即可推断是何种模块。

随后即可按照模块类型采取对应的操作。

1.3.2 CPLD的选用端口数据。

公司的MAXII器件采纳了全新的CPLD结构,比以往的MAX器件具有更高的性价比、更低的功耗、更大的容量,使其成为复杂控制应用的抱负计划。

考虑到输入输出模块的功能相对容易,不需要大量的复杂运算,本系统选用容量相对较小的EPM240举行设计。

1.3.3 CPLD的软件设计为了通过ARM9的地址总线、数据总线和控制总线实现对输入输出模块的读写控制,必需按照ARM9的读写时序图对输入输出模块的CPLD举行硬件语言编程设计。

输入模块关键代码如下:assign data_bus=((~(RDICS))&(address==baddr[10:5])&(haddr[4:0]==5'b00000))?16'b0000000011011111:16'bz;assign data_bus=((~(RDICS))&(address==baddr[10:5])&(baddr[4:0]==57b00100))?dc24v_in:16'bz;程序中第一个assign语句功能:当地址总线的低五位为5'b00000,即为“读模块ID码地址”,就向数据总线输出该模块的ID码。

其次个assign语句功能:当地址总线的低五位为5"b00100,即为“读模块数据地址”,就将模块输入端口数据读入数据总线。

华清远见 GX-ARM9-2410EP 用户手册说明书

GX-ARM9-2410EP 硬件资源:GX-ARM9-2410EP 核心模块:● SAMSUNG ARM9 S3C2410处理器,主频200MHz● 64M SDRAM ● 通过可靠的SODIMM接口和主板相连接GX-ARM9-2410EP 主板资源:● 2M AMD 线性 FLASH:类似 PC BIOS 的功能,实现对系统的初始化和配置● 8M Intel线性FLASH:可通过主板的JTAG接口直接烧写 ● 1个SMC接口:系统支持直接从SMC卡启动 ● 本系统支持三种启动方式,通过跳线可以设置系统从AMD FLASH、Intel FLASH或者从外接的SMC卡启动 ● PCMCIA控制器扩展的PCMCIA接口:不仅可外接PCMCIA外设,而且可以通过转接卡连接带CF卡接口外设 ● Audio音频接口:音频的输入输出方式十分灵活,直接通过跳线选择,既可以是外接的MIC(MICROPHONE) Input及Line Output,还可以是板载的MIC及双声道喇叭 ● 1个SD卡接口● 2 个以太网卡接口:1 个是由 CS8900 外扩的 10M 网口,还有 1 个是由 DM9000 外扩的 10M/100M 自适应网口 ● 2 个USB接口:1 个USB Host,1 个USB Host/Device ● 2 个PS/2接口:可直接接PS/2接口的鼠标与键盘 ● 多功能扩展模块接口:通过两个 96Pin 的欧式座引出系统的 32 位总线、由 CPLD 扩展的大量 GPIO以及SPI、IIC、 UART等接口,针对各高等院校电子信息、计算机、自动化、测控等专业需求,可方便地扩展各个的专用模块, 实现功能无限扩展。

可选配GPS 模块、GPRS 模块、GPS&GPRS 模块、蓝牙扩展板、GX-SOPC-Nios II模 块、滑动式半导体指纹模块、802.15.4扩展板、射频卡&IC卡扩展板、GX-CAN&485扩展板、电机扩展板…… ● 液晶显示器模块和液晶显示器扩展接口电路:自带 3.5寸真彩TFT液晶屏,分辨率 320×240,LED背光,带触摸 屏,通过液晶屏扩展接口可扩展成更大尺寸的液晶屏……● 5 个 RS232 接口:其中 1个红外复用● 1 个IDE硬盘接口:可直接接笔记本硬盘● 1 个标准 25 针并行接口● 8 个 8 段的数码管:方便数字的显示● 10bit A/D 接口:电压输入可以是板载电位器、板载温度传感器或 D/A 的输出信号● DAC0832 扩展的 D/A 通道接口:信号可以直接输出,也可以作为 A/D 的一个信号源● 实时时钟 RTC:在 CPU 内部集成,通过主板上的 3V 锂电池提供掉电保护● I 2C接口的 E 2PROM :可通过 CPU 的 I 2C 接口实现对 E 2PROM 中的数据读写,数据掉电不丢失● SPI接口的 E 2PROM :可通过 CPU 的 SPI 接口实现对 E 2PROM中的数据的高速读写,数据掉电不丢失 ● 移植成功的 MIZILinux 及μC/OS II 嵌入式实时操作系统源代码公开。

基于S3C2410的系统硬件设计

基于S3C2410的系统硬件设计概述:S3C2410是一款由三星公司设计的嵌入式系统芯片,采用ARM9架构,主频为200MHz。

在嵌入式系统中,它被广泛应用于各种控制和通信设备。

在本文中,我们将介绍基于S3C2410的系统的硬件设计。

硬件设计:1.处理器:S3C2410芯片是嵌入式系统的核心,它具有强大的计算和控制能力。

在系统设计中,需要考虑处理器的供电和散热问题,以确保其稳定运行。

2.存储器:S3C2410芯片具有32KB的指令缓存和16KB的数据缓存,但通常还需要外部存储器来扩展系统的存储容量。

可以选择使用FLASH存储器作为程序和数据的存储介质。

3.外设接口:S3C2410芯片支持多种外设接口,包括UART、SPI、I2C、USB等。

在硬件设计中,需要根据应用需求选择合适的外设接口,并设计相应的接口电路。

4.显示屏:S3C2410芯片具有LCD控制器,可以驱动液晶显示屏。

在设计中,需要选择合适的显示屏,并设计相应的电路来连接S3C2410芯片和显示屏。

5.输入设备:系统通常需要一些输入设备,如按键、触摸屏等。

在硬件设计中,需要为这些输入设备设计相应的电路,并与S3C2410芯片进行连接。

6.时钟电路:S3C2410芯片需要外部时钟源来提供时钟信号。

在设计中,需要选择合适的时钟电路,并确保时钟信号的稳定性和准确性。

7.电源管理:S3C2410芯片需要稳定的供电电源。

在硬件设计中,需要设计相应的电源管理电路,以确保系统的正常运行。

8.其他外部接口:根据具体应用需求,可能还需要设计一些其他外设接口,如以太网接口、音频接口等。

总结:基于S3C2410的系统硬件设计需要考虑处理器、存储器、外设接口、显示屏、输入设备、时钟电路、电源管理等方面。

在设计过程中,需要充分考虑应用需求,选择合适的硬件组件,并设计相应的电路来连接这些组件。

通过合理的硬件设计,可以确保系统的稳定运行,并满足用户的需求。

第三章_ARM9_S3C2410片上资源.ppt

OM[1:0]=00 未用 SFR区 未用 SROM/SDRAM (nGCS7) SROM/SDRAM (nGCS6) SROM (nGCS5) SROM (nGCS4) SROM (nGCS3) SROM (nGCS2) SROM (nGCS1) 内部启动 SRAM(4KB) [使用NAND Flash作为ROM] 2MB/4MB/8MB/16MB /32MB/64MB/128MB 2MB/4MB/8MB/16MB /32MB/64MB/128MB 128MB 128MB 128MB 128MB 128MB 1GB HADDR[29:0] 可访问区域

3.1.4 S3C2410处理器存储器映射

S3C2410的存储空间映射如图3-2所示:

3.1.5 S3C2410处理器时钟和电源管理

1.时钟 S3C2410的主时钟由外部晶振或者外部时钟提供,选择后可 以产生3种时钟信号,分别是CPU使用的FCLK、AHB总线 使用的HCLK和APB总线使用的FCKL。时钟管理模块同时 拥有两个锁相环,一个称为MPLL,拥于FCLK、HCLK和 PCLK;另一个称为UPLL, 用于USB设备。 时钟源选择 对时钟的选择是通过S3C2410引脚上OM[3:2]实现的,JU具 体如表3-1所示。

// Memory control #define rBWSCON (*(volatile unsigned *)0x48000000) //Bus width & wait status #define rBANKCON0 (*(volatile unsigned *)0x48000004) //Boot ROM control #define rBANKCON1 (*(volatile unsigned *)0x48000008) //BANK1 control #define rBANKCON2 (*(volatile unsigned *)0x4800000c) //BANK2 cControl #define rBANKCON3 (*(volatile unsigned *)0x48000010) //BANK3 control #define rBANKCON4 (*(volatile unsigned *)0x48000014) //BANK4 control #define rBANKCON5 (*(volatile unsigned *)0x48000018) //BANK5 control #define rBANKCON6 (*(volatile unsigned *)0x4800001c) //BANK6 control

革新2410D开发板试用手记

革新2410D开发板试用手记嵌入式技术是一门新技术,它广泛应用于各行各业;嵌入式产品体积小、功耗低、处理能力强,在通讯、工控、电力、电子等领域发挥着重要作用。

GX-ARM9-2410D 型开发板集成了系统的大量资源,是国内可扩展性最强的开发板。

它不需要任何外部电路也可以独立使用,是学习开发的好平台;而且,可以方便地作为嵌入式主板嵌入式到用户设备中去,是设计、开发嵌入式设备的最佳选择。

核心板硬件参数CPU:S3C2410 ARM920T 内核主频200M 或S3C2440 ARM920T 内核主频400M;SDRAM:16M 乘以32bit (64M PC100);接口:200PIN SODIMM 接口;主板硬件参数Flash:4M Intel 线性FLASH,可通过SMC 卡扩展非线性Flash(系统支持两种启动方式,通过拨动开关,可以设置系统从Intel FLASH或者从外接的SMC 卡启动)。

1 个10M/100M 自适应网卡(DM9000);使用嵌入式音频芯片,多种输出输入方式,开关灵活选择,主板自带双声道扬声器。

USB 接口(USB1.1):2 个USB Host,1 个USB Host/Device;串行接口:3 个RS232 接口;JTAG 接口:可接ARM 仿真器;SMC 接口:系统支持直接从SMC 卡启动SD 卡接口:支持SD 卡或MMC 卡液晶屏:可选配4.3 寸TFT 480 乘以272 真彩液晶屏多功能扩展模块接口:通过IDC 接口扩展出了16 位总线、液晶屏、触摸屏、串口等通信接口。

针对各高等院校电子信息、计算机、自动化、测控等专业需求,可方便地扩展各个专用模块。

4 个按键; 4 个发光LED;CPU 内部集成RTC,通过主板上的3V 锂电池提供掉电保护;电源:外接5V/2A 直流电源;软件资源●Linux ●内核:Linux Kernel 2.4.21 ●系统引导程序:Boot Loader (源代码),PPCBoot ●文件系统:JFFS2,Ramdisk。

硬件说明

博创科技ARM2410 平台硬件说明一.开发板硬件资源1.串口:UART0和UART1由MAX3232驱动,DB9插座输出。

另有UART2只引到扩展槽。

2.USB:USB HOST和USB DEVICE接口,由2410 CPU直接驱动,HOST口带有自恢复保险。

3.网口:EtherNet接口由网卡芯片AX88796驱动,RJ-45输出。

4.JTAG:提供14Pin和20Pin两种插口。

5.A/D:板载3路分压电位器,并可由跳线选择CPU AD输入AD0\AD1\AD2三路为板载电位器还是扩展槽外部电压源。

同时AD电路的参考电压也可以通过跳线选择是板上3.3V还是扩展槽外部参考电压。

6.RTC:板载RTC后备纽扣电池。

7.KEYPAD/LED:键盘和数码管部分由芯片ZLG7290驱动,通过IIC总线和CPU 接口。

提供8位LED和17键键盘(同PC小键盘)。

8.LCD:液晶屏模块由CPU经74HC245隔离驱动,支持256色彩屏和24位真彩屏。

9.TouchScr:触摸屏由FM7843驱动,通过SPI和CPU接口。

10.Audio:音频模块由芯片UDA1341完成解码和DA,通过IIS总线和CPU接口。

同时具有由TDA2822构成的功放电路和扬声器,以及板载MIC,可以实现录音,放大器等功能。

11.开发板提供3个168Pin外部扩展槽,将所有的地址线、数据线、控制线、其他各种信号线以及尚未使用的IO口线都引出作为扩展只用。

12.ARM2410 内核板插槽:可以插配套的2410内核板,其上包括CPU S3C2410、SDRAM 57V561620、FLASH K9F2808等芯片。

二.电路原理说明1.开发板电源电压为5V,经AS1117-3.3V和AS1117-1.8V分别得到3.3V和1.8V 的工作电压。

开发板上的芯片多数使用了3.3V电压,而1.8V是供给S3C2410内核使用的。

5V电压供给音频功放芯片和LCD电路使用。

ARM9嵌入式系统设计——基于S3C2410与Linux_P296-301

Linux内核的结构操作系统内核的结构模式可分为两种:整体式的单内核模式和层次式的微内核模式。

1.单内核单内核也叫集中式操作系统。

整个系统是一个大模块,可以被分为若干逻辑模块,即处理器管理、存储器管理、设备管理和文件管理,其模块间的交互是通过直接调用其他模块中的函数实现的。

单内核模型以提高系统执行效率为设计理念,因为整个系统是一个统一的内核,所以其内部调用效率很高。

单内核的缺点也正是由于其源代码是一个整体而造成的:通常各模块之间的界限并不特别清晰,模块间的调用比较随意,所以进行系统修改或升级时,往往“其一发而动全身”,导致工作量加大,使其难以维护。

2.微内核微内核是指把操作系统结构中的内存管理、设备管理、文件系统等高级服务功能尽可能地从内核中分离出来,变成几个独立的非内核模块,而在内核中只保留少量最基本的功能,使内核变得简洁可靠。

微内核实现的基础的操作系统理论层面的逻辑功能划分。

几大功能模块在理论上是相互独立的,形成比较明显的界限,其优点如下:·充分的模块化设计,可独立更换任一模块而不会影响其他模块,从而方便第三方开发、设计模块。

·未被使用的模块功能不必运行,因而能大幅度减少系统的内存需求。

·具有很高的可移植性,理论上讲只需要单独对各微内核部分进行移植修改即可。

由于微内核的体积通常很小,而且互不影响,因此工作量很小。

微内核的明显缺点是系统运行效率低,因为各个模块与微内核之间是通过通信机制进行交互的。

Linux内核主要由5个子系统组成:进程调度、内存管理、虚拟文件系统、网络接口和进程间通信。

进程调度控制进程对CPU的访问,采用适当的调度策略使各进程能够合理的使用CPU。

内存管理(MM)允许多个进程安全的共享主内存区域。

Linux的内存管理支持虚拟内存,即在计算机中运行的程序,其代码、数据和堆栈的总量可以超过实际内存的大小,操作系统只是把当前使用的程序块保留在内存中,其余的程序块则保留在磁盘中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

JX2410教学实验平台——硬件设计说明

第一章 概述

JX2410教学实验平台,是专门为电子、计算机类本科生/研究生嵌入式教学实验建设而设计的。

通过对本JX2410教学实验平台及集成开发环境的了解和学习,使学生对32位嵌入式系统的组成原理、接口技术、开发流程有比较深刻的了解。

本教学实验平台,接口丰富,由浅入深,使学生易于学习和掌握。

第二章硬件组成

一、 接口或模块组成

1、立体声录放音:通过IIS进行操作,必须将跳线JP2的1、2及JP4的1、2短接。

2、步进电机控制:通过CPLD进行控制,设置控制寄存器1中的步进电机驱动使

能信号、正反转设置、步进电机转动模式控制位。

然后通过GPC11提供电机的驱动脉冲。

3、标准JTAG口/简易JTAG口:

标准仿真器通过标准JTAG口进行调试仿真。

ADT1000集成开发环境也可通过简易JTAG口进行调试仿真。

4、两个串口:最高速率为115200bps。

串口0带硬件流控,串口1不带硬件流控。

串口0和GPS的串口共用,串口1和GPRS的串口共用,可通过CPLD配置进行切换。

见CPLD部分。

5、RS485接口,CAN总线接口

6、RTC:通过后备电池及S3C2410的内部RTC电路实现。

7、IIC:通过S3C2410的IIC总线操作。

8、6个7段数码管:通过CPLD的数码管数据寄存器及数码管扫描控制寄存器实

现,见CPLD部分。

9、蜂鸣器:通过S3C2410的PWM接口实现。

10、两个外部中断测试按键:测试外部中断2、3功能。

11、4*4键盘接口:为4*4扫描式键盘。

12、CPLD:产生外设片选,控制信号,串口切换等。

13、4个跑马灯:通过锁存器实现。

14、10M 网络接口:通过RTL8019AS 网络接口芯片实现。

15、USB 接口:一个USB 从;一个USB 主/从可选。

16、GPRS 接口:通过GPRS 模块CMS91实现。

17、GPS 接口:通过GPS 模块AR2010-EB 实现。

18、并行接口:通过74系列的芯片实现。

19、CF 卡接口:通过CPLD 产生的时序电路实现。

20、IDE 接口: 21、SD 卡接口。

21、2个A/D 接口:通过S3C2410内置10BIT 的A/D 口及可调电位器实现。

22、显示器接口:256色STN 彩色显示器,分辨率为320*240。

23、触摸屏接口:四线电阻式触摸屏。

24、PS2键盘接口、PS2鼠标接口 二、

资源说明:

1、地址分配 地址区间

说明

数据宽度

读/写属性

0x00000000~0x0007fffff 0x00000000~0x000ffffff 0x00000000~0x001ffffff FLASH 存储器地址:

TE28F320:4M*2字节; TE28F640:8M 字节*2 TE28F128:16M 字节*2

32bit R/W

0x10000000 控制键盘扫描及跑马灯 8 bit W 0x10000002 读入键盘扫描值 8 bit R 0x10000004 数码管数据寄存器 8 bit W 0x10000006

数码管扫描控制寄存器

8 bit W 0x10080000~0x100807ff CF 卡MEMORY 模式属性寄存器 8/16 R/W 0x10080800~0x100808ff CF 卡MEMORY 模式公共寄存器 8/16 R/W 0x100c0000~0x100c07ff CF 卡I/O 模式 8/16 R/W 0x100c0000~0x100c00ff IDE 读写地址空间

8/16

R/W

0x18000300~0x1800031f 网络接口芯片RTL8019AS 读写

16 bit R/W 0x28000000 并口控制寄存器 8 bit W 0x28000000 并口状态寄存器 8 bit R 0x28000002 并口数据缓存器 8 bit R/W 0x28000004

控制寄存器0 8 bit W 0x28000006 控制寄存器1 8 bit W 0x28080000 控制寄存器2 8 bit W 0x20000000 读密码

8 bit R

0x38000000~0x38FFFFFF 0x38000000~0x39FFFFFF 0x38000000~0x3BFFFFFF SDRAM 存储器地址空间:

HY57V641620:8M 字节*2 HY57V281620:16 M 字节*2 HY57V561620:32 M 字节*2 32bit R/W

2、中断分配 中断口 说明 备注 INT0 IDE 中断 INT1 扩充口中断 INT2 中断测试 INT3 中断测试 INT4 网口中断 INT5 CAN 中断

3、A/D 口分配 A/D 口 说明

备注

AIN0 A/D 采集口测试0 用于A/D 测试 AIN1

A/D 采集口测试1 用于A/D 测试 AIN2、3、4、6 NUL

备用 AIN5 采集触摸屏的Y 坐标 用于触摸屏 AIN7

采集触摸屏的X 坐标

用于触摸屏

4、其他说明

0x10000000:控制键盘扫描。

低4位控制键盘扫描。

0x10000002:读入键盘扫描值。

地4位有效,为低时,对应列有键按下。

0x10000006:数码管扫描控制寄存器。

为低时,数码管数据寄存器的显示图样在对应的数码管上显示。

0x28000000:并口状态寄存器。

D7:nACK

D6:BUSY

D5:PE

D4:SELECT

D3:nERROR

0x28000000:并口控制寄存器。

D3:nSELECT_IN

D2:nINIT

D1:AUTOFEED

D0:nSTROBE

0x28000004:控制寄存器0,6BIT有效,复位后初始值为0X2C,用于控制串口切换和IDE操作。

各位说明如下:

D5: 0 — 复位IDE设备;1 — 通常操作

D4: IOIS16。

0 -- 16 bit;1 -- 8 bit

D3..D2:IDE片选:(D3—nCS_IDE1;D2—nCS_IDE0)(?)

00: 无效地址

01: 控制块寄存器

10: 命令块寄存器

11: 高阻

D1..D0: 串行口切换控制:

当控制寄存器1的b5为0时,实现如下切换:

00: 串口0接到EXT_UART,GPRS接到UART1

01: 串口0直接接出,串口1接到GPRS

10: 串口0接到GPS,串口1直接接出

11: 串口0直接接出,串口1直接接出

0x28000006:控制寄存器1,6BIT有效,复位后初始值为0。

各位说明如下: D5:为1时,两串口均直接通过DB9接口接出

D4:保留

D3:0 -- 关断步进电机驱动芯片;1 -- 打开步进电机驱动芯片

D2: 0 -- 正转;1 -- 反转

D1..D0: 00:半步模式;其它:通常模式

电机的驱动脉冲由GPC11引脚提供。

0x28080000:控制寄存器2,6BIT有效,复位后初始值为0X2C。

各位说明如下: D5..D4:保留

D3:复位CF卡。

0 — 通常操作;1 – 复位CF卡

D2:CF卡电源控制。

0:打开;1:关闭

D1..D0: nCS_CF1,nCS_CF0 (?)

00: 16bit

01: 16bit

10: 8bit

11: 高阻。