数字电子技术时序逻辑电路

王海光数字电子技术基础 第5章 时序逻辑电路

与触发器的对应关系,还应给出排序示范

图 ( 如 图 5.1.2 示 范 图 圆 圈 中 标 注 的 Q3Q2Q1 ),对含多个输入输出端的时序

电路,也应在示范图中标出(如图5.1.2中

指向线上标注的/Y)。

5.1.1 时序逻辑电路的人工分析

(5)电路功能判断说明。

对电路功能的判断应结合输入输出信号的具体物理含义来

5.1.1 时序逻辑电路的人工分析

*二、异步时序逻辑电路的分析

与同步时序电路不同的是,异步时序电路中的所有触发 器并非由同一时钟源触发,所以在根据电路的现态计算电路 的次态时,应特别注意各个触发器的时钟条件是否具备。只 有时钟条件具备的触发器才会按状态方程描述的逻辑关系转

换成次态,否则将维持现态不变。为此在分析异步时序电路

组合逻辑电路

Y1 Yj

Z Zk 存储电路

图5.0.1 时序逻辑电路结构示意框图

这四种信号之间的逻辑关系可用以下三个向量函数表示: 输出方程:Y(tn)=F1[X(tn),Q(tn)]

驱动方程:Z(tn)=F2[X(tn),Q(tn)]

状态方程: Q(tn+1)=F3[Z(tn),Q(tn)] 式中tn、tn+1是对电路进行考察的两个相邻的离散时间。

5.1.1 时序逻辑电路的人工分析

一、同步时序逻辑电路的分析 导出同步时序电路的状态转换表、状态转换图和时序波 形图,判断时序电路逻辑功能的通常步骤:

1.根据给定的时序电路列出电路的输出方程和驱动方程组。 2.将各个驱动方程代入对应触发器的特性方程得到整个时序 电路的状态方程组。 3.根据电路的状态方程组计算列出电路的状态转换表。 4.根据电路的状态转换表画出状态转换图或时序波形图。 5.根据状态转换图或时序波形图说明电路的逻辑功能,判断 电路能否自启动。

第六章时序逻辑电路-丽水学院

第六章 时序逻辑电路(14课时)本章教学目的、要求:1.掌握时序逻辑电路的分析方法。

2.掌握常用时序逻辑部件:寄存器、移位寄存器、由触发器构成的同步二进制递 增计数器和异步十进制递减计数器,及由集成计数器构成任意进制计数器。

3.熟悉常用中规模集成时序逻辑电路的逻辑功能及使用方法。

4.掌握同步时序逻辑电路的设计方法。

重点:时序逻辑电路在电路结构和逻辑功能上的特点;同步时序逻辑电路的分析方法;常用中规模集成时序逻辑电路的逻辑功能及使用方法;由集成计数器构成任意进制计数器。

难点:同步时序逻辑电路的设计方法第一节 概述(0.5课时)一、定义:1.定义:任一时刻电路的稳定输出不仅取决于当时的输入信号,而且还取决于电路原来的状态。

2.例:串行加法器:指将两个多位数相加时,采取从低位到高位逐位相加的方式完成相加运算。

需具备两个功能:将两个加数和来自低位的进位相加, 记忆本位相加后的进位结果。

全加器执行三个数的相加运算, 存储电路记下每次相加后的运算结果。

CP a i b i c i-1(Q ) s i c i (D )0 a 0 b 0 0 s 0 c 0 1 a 1 b 1 c 0 s 1 c 1 2 a 2 b 2 c 1 s 2 c2 3.结构上的特点:①时序逻辑电路通常包含组合电路和存储电路两部分,存储电路(触发器)是必不可少的;②存储器的输出状态必须反馈到组合电路的输入端,与外部输入信号共同决定组合逻辑电路的输出。

∑CI COCLKC1<1DQ 'Qia ic i-1c ib is 串行加法器电路二、时序电路的功能描述原状态:q1, q2, …, q l新状态:q1*,q2 *,…,q l*1.逻辑表达式。

Y = F [X,Q] 输出方程。

Z = G [X,Q] 驱动方程(或激励方程)。

Q* = H [Z,Q] 状态方程。

2.状态表、状态图和时序图。

三、时序电路的分类1. 按逻辑功能划分有:计数器、寄存器、移位寄存器、读/写存储器、顺序脉冲发生器等。

数字电子技术基础-第六章_时序逻辑电路(完整版)

T0 1

行修改,在0000 时减“1”后跳变 T1 Q0 Q0(Q3Q2Q1)

为1001,然后按

二进制减法计数

就行了。T2 Q1Q0 Q1Q0 (Q1Q2Q3 )

T3 Q2Q1Q0

50

能自启动

47

•时序图 5

分 频

10 分 频c

0

t

48

器件实例:74 160

CLK RD LD EP ET 工作状态 X 0 X X X 置 0(异步) 1 0 X X 预置数(同步) X 1 1 0 1 保持(包括C) X 1 1 X 0 保持(C=0) 1 1 1 1 计数

49

②减法计数器

基本原理:对二进 制减法计数器进

——74LS193

异步置数 异步清零

44

(采用T’触发器,即T=1)

CLKi

CLKU

i 1

Qj

j0

CLKD

i 1

Qj

j0

CLK0 CLKU CLKD

CLK 2 CLKU Q1Q0 CLK DQ1Q0

45

2. 同步十进制计数器 ①加法计数器

基本原理:在四位二进制 计数器基础上修改,当计 到1001时,则下一个CLK 电路状态回到0000。

EP ET 工作状态

X 0 X X X 置 0(异步)

1 0 X X 预置数(同步)

X 1 1 0 1 保持(包括C)

X 1 1 X 0 保持(C=0)

1 1 1 1 计数

39

同步二进制减法计数器 原理:根据二进制减法运算 规则可知:在多位二进制数 末位减1,若第i位以下皆为 0时,则第i位应翻转。

Y Q2Q3

数字电子技术第6章 时序逻辑电路

RD—异步置0端(低电平有效) 1 DIR—右移串行输入 1 DIL—左移串行输入 S0、S1—控制端 1 D0D1 D2 D3—并行输入

《数字电子技术》多媒体课件

山东轻工业学院

4、扩展:两片74LS194A扩展一片8位双向移位寄存器

《数字电子技术》多媒体课件

山东轻工业学院

例6.3.1的电路 (P276) 74LS194功能 S1S0=00,保持 S1S0=01,右移 S1S0=10,左移 S1S0=11,并入

(5)状态转换图

《数字电子技术》多媒体课件

山东轻工业学院

小结

1、时序逻辑电路的特点、组成、分类及描述方法; 2、同步时序逻辑电路的分析方法; 课堂讨论: 6.1,6.4

《数字电子技术》多媒体课件

山东轻工业学院

6.3 若干常用的时序逻辑电路

寄存器和移位寄存器 时序 逻辑电路 计数器 顺序脉冲发生器 序列信号发生器

移位寄存器不仅具有存储功能,且还有移位功能。 可实现串、并行数据转换,数值运算以及数据处理。 所谓“移位”,就是将寄存器所存各位数据,在每个移 位脉冲的作用下,向左或向右移动一位。

2、类型: 根据移位方向,分成三种:

左移 寄存器 (a) 右移 寄存器 (b) 双向 移位 寄存器 (c)

《数字电子技术》多媒体课件

学习要求 :

* *

自学掌握

1. 掌握寄存器和移位寄存器的概念并会使用; 2. 掌握计数器概念,熟练掌握中规模集成计数器74161 和74160的功能,熟练掌握用160及161设计任意进制计 数器的方法。

《数字电子技术》多媒体课件

山东轻工业学院

6.3.1寄存器和移位寄存器

一、寄存器

寄存器是计算机的主要部件之一, 它用来暂时存放数据或指令。

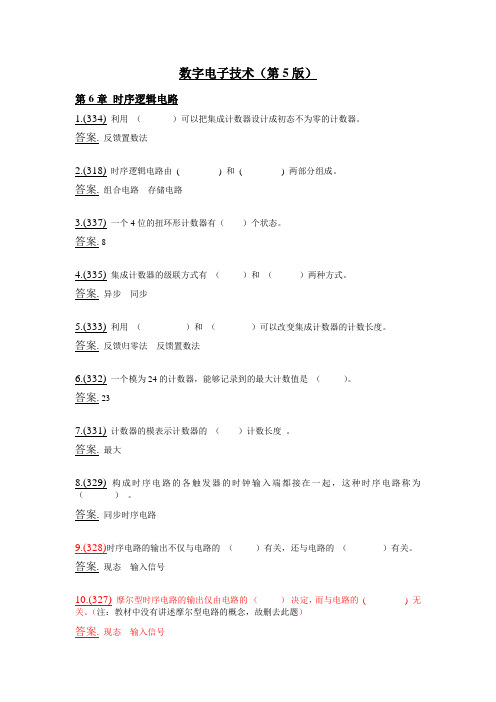

第6章_时序逻辑电路

数字电子技术(第5版)第6章时序逻辑电路1.(334)利用()可以把集成计数器设计成初态不为零的计数器。

答案.反馈置数法2.(318)时序逻辑电路由( ) 和( ) 两部分组成。

答案.组合电路存储电路3.(337)一个4位的扭环形计数器有()个状态。

答案. 84.(335)集成计数器的级联方式有()和()两种方式。

答案.异步同步5.(333)利用()和()可以改变集成计数器的计数长度。

答案.反馈归零法反馈置数法6.(332)一个模为24的计数器,能够记录到的最大计数值是()。

答案. 237.(331)计数器的模表示计数器的()计数长度。

答案.最大8.(329)构成时序电路的各触发器的时钟输入端都接在一起,这种时序电路称为()。

答案.同步时序电路9.(328)时序电路的输出不仅与电路的()有关,还与电路的()有关。

答案.现态输入信号10.(327)摩尔型时序电路的输出仅由电路的()决定,而与电路的( ) 无关。

(注:教材中没有讲述摩尔型电路的概念,故删去此题)答案.现态输入信号11.(326) 时序逻辑电路的功能描述有 ( ) 、 ( ) 、 ( ) 、 ( ) 。

答案. 逻辑方程式 状态表 状态图 时序图12.(330) 异步时序电路中的各触发器的状态转换 ( )同一时刻进行的。

答案. 不是在13.(336) 一个4位的环形计数器有( )个状态。

答案. 414.(325) 时序逻辑电路可分为 ( ) 和 ( ) 两大类。

答案. 同步时序电路 异步时序电路15.(354) 分析如图7307所示电路,说明其功能。

图7307输 入输 出CR LD T CT P CT CP 3D 2D 1D 0D 3Q 2Q 1Q 0QCO0 × × × × × × × × 000 10××↑3d 2d 1d 0d 3d 2d 1d 0d1111↑×××× 计数 110×××××× 保持 11××××××保持答案. 经分析知,采用了74LS160的同步置数功能。

数字电子技术时序逻辑电路

PPT文档演模板

数字电子技术时序逻辑电路

PPT文档演模板

图5-3 4位寄存器74LS175的逻辑图

数字电子技术时序逻辑电路

2. 移位寄存器 移位寄存器不仅具有存储的功能,而且还有移位功能,可以 用于实现串、并行数据转换。如图5-4所示为4位移位寄存器 的逻辑图。

PPT文档演模板

数字电子技术时序逻辑电路

5.1.2 异步时序逻辑电路的分析方法

异步时序电路的分析步骤:

① 写时钟方程; ② 写驱动方程; ③ 写状态方程; ④ 写输出方程。

PPT文档演模板

数字电子技术时序逻辑电路

[例5-2]试分析图示时序逻辑电路的逻辑功能,列出状态转换 表,并画出状态转换图。

PPT文档演模板

数字电子技术时序逻辑电路

解:图5-7所示电路为1个异步摩尔型时序逻辑电路。 写时钟方程:

数字电子技术时序逻辑电路

PPT文档演模板

图5-5 同步二进制加法计数器的数时字电序子图技术时序逻辑电路

PPT文档演模板

图5-8 同步4位二进制加法计数器74LS16数1字的电逻子技辑术图时序逻辑电路

表5-1 同步4位二进制加法计数器74LS161的功能表

PPT文档演模板

数字电子技术时序逻辑电路

写驱动方程:

写状态方程:

PPT文档演模板

数字电子技术时序逻辑电路

列状态转换表:

PPT文档演模板

数字电子技术时序逻辑电路

画状态转换图:

PPT文档演模板

数字电子技术时序逻辑电路

5.2 若干常用的时序逻辑电路 5.2.1寄存器

1. 基本寄存器

PPT文档演模板

图5-2 双2位寄存器74LS75的逻辑图

时序逻辑电路的分析方法

利用染色体畸变和基因

突变为指标监测环境污染 物的致突变作用

理生化变 化为指标

来监测环

单元1 时序逻辑电路的分析方法

一、生物监测的主要方法

《数字电子技术》

1.生物群落法(生态学方法) 利用生物群落组成和结构的变化及生态 系统功能的变化为指标监测环境污染。

(1)寻找指示生物

例如:蜗虫

水蚯蚓

(2)了解污染物对生物群落的影响

单元1 时序逻辑电路的分析方法

号作用前电路的输出状态有关。

时序逻辑电路 方框图

特点:(1)时序电路往往包含组合电路和存储电路两

部分,而存储电路是必不可少的。(2)存储电路输出 的状态必须反馈到输入端,与输入信号一起共同决定组 合电路的输出。

分类:同步时序逻辑电路:所有触发器的时钟端均连

在一起由同一个时钟脉冲触发,使之状态的变化都与输 入时钟脉冲同步。 异步时序逻辑电路:只有部分触发器的时钟端与输入时 钟脉冲相连而被触发,而其它触发器则靠时序电路内部 产生的脉冲触发,故其状态变化不同步。

时序图:在时钟脉冲序列作用下,电路状态、输出状态随时间变化的 波形图。

单元1 时序逻辑电路的分析方法

1.2 时序逻辑电路的分析方法

《数字电子技术》

[例1-1] 试分析电路的逻辑功能,并画出状态转换图和时序图。

解: 1、写方程式

(1)输出方程

(2)驱动方程

一单、元生1 时物序监逻辑测电的路主的分要析方方法法有哪些?

《数字电子技术》

[例1-1] 试分析电路的逻辑功能,并画出状态转换图和时序图。

解: 1、写方程式

(2)驱动方程

(3)状态方程

单元1 时序逻辑电路的分析方法

1.2 时序逻辑电路的分析方法

数字电子技术时序逻辑电路习题

5、画逻辑电路图

T1 = Q1 + XQ0 T0 = XQ0 + XQ0 Z = XQ1Q0

第43页/共55页

6、检查自启动

全功能状态转换表

现 入 现 态 次 态 现驱动入 现输出

Xn Q1n Q0nQ1n+1Q0n+1 T1 T0

Zn

1/0

0/0 0 0 0 0 1 0 1

0

现入 现态 次 态

X Q1 Q0 Q1 Q0 0 0 00 1 0 0 11 0 0 1 00 0

1 0 00 1 1 0 11 0 1 1 01 1 1 110 0

现驱动入 现输出

D1 D0 01 10 00

Z1 Z2

00 00 10

01 10 11 00

00 00 00 01

D1 = Q1Q0 + Q1Q0X

标题区

节目录

第14页/共55页

X/Z

S0 1/0

S1

1/1

0/0

S2

10101…

题6.2(1)的状态转移图

③ 状态间的转换关系

标题区

节目录

第15页/共55页

X/Z

0/0 S0 1/0

S1 1/0

1/1

11…

0/0

0/0

100…

S2

题6.2(1) 的原始状态转移图

标题区

节目录

第16页/共55页

(2) 解:① 输入变量为X、输出变量为Z;

S1 1/0

11…

0/0

1/1

0/0

100…

S2

题6.2(2) 的原始状态转移图

标题区

节目录

第19页/共55页

数字电子技术 时序逻辑电路的分析与设计 国家精品课程课件

《数字电子技术》精品课程——第6章

FF0

FF1

1J

Q0 1J

Q1

时序逻辑电路的分析与设计

&Z

FF2

1J

Q2

C1

C1

C1

1K

1K

1K

Q0

Q1

Q2

CP

➢驱动方程:

《数字电子技术》精品课程——第6章 时序逻辑电路的分析与设计

② 求状态方程

JK触发器的特性方程:

Qn1 JQ n KQn

将各触发器的驱动方程代入,即得电路的状态方程:

简化状态图(表)中各个状态。 (4)选择触发器的类型。

(5)根据编码状态表以及所采用的触发器的逻辑功能,导出待设计 电路的输出方程和驱动方程。

(6)根据输出方程和驱动方程画出逻辑图。

返回 (7)检查电路能否自启动。

《数字电子技术》精品课程——第6章 时序逻辑电路的分析与设计

2.同步计数器的设计举例

驱动方程: T1 = X T2 = XQ1n

输出方程: Z= XQ2nQ1n

(米利型)

2.写状态方程

T触发器的特性 方程为:

Qn1 TQn TQn

Q 1nQ1QX21nn TX1QQ1n1nXTQX11nQ1n X Q1n

Q1n

Qn1 2

T2 Q2n

T2Qn2

T Q n 将T1、 T2代入则得X到Q两1n Q2n XQ1nQn2

0T1 = X0 0 0 0 0 0

0

求T1、T2、Z

0T2

0

=ZX=01QX1nQ10 2nQ010n

0 0

0 1

1 0

0 0

由状态方程

求Q2n+1 、 Q1n+1

数字电子技术时序逻辑电路PPT

写驱动方程: J 0 K 0 1

J1 J2

Q3 K2

1

K1

1

J 3 Q1Q2

K3 1

写状态方程:

Q0n1 QQ1n2n11

n

Q0

Q3

n

Q2

n

Q1

(CP0 下降沿动作) (Q0 下降沿动作) (Q1下降沿动作)

Q3n 1

Q1Q2

画时序图: 该电路能够自启动。

5.1.2 异步时序逻辑电路的分析方法

异步时序电路的分析步骤:

① 写时钟方程; ② 写驱动方程; ③ 写状态方程; ④ 写输出方程。

[例5-2]试分析图示时序逻辑电路的逻辑功能,列出状态转换 表,并画出状态转换图。

解:图5-7所示电路为1个异步摩尔型时序逻辑电路。 写时钟方程:

Q3n(Q0

下降沿动作)

列状态转换表:

画状态转换图:

5.2 若干常用的时序逻辑电路 5.2.1寄存器

1. 基本寄存器

图5-2 双2位寄存器74LS75的逻辑图

图5-2所示为双2位寄存器74LS75的逻辑图。当 CPA = 1时,

送到数据输入端的数据被存入寄存器,当CPA =0时,存入

寄存器的数据将保持不变。

2n-1 M 2n

然后给电路的每一种状态分配与之对应的触发器状态组合。

4)确定触发器的类型,并求出电路的状态方程、驱动方程 和输出方程。 确定触发器类型后,可根据实际的状态转换图求出电路的状 态方程和输出方程,进而求出电路的驱动方程。

5)根据得到的驱动方程和输出方程,画出相应的逻辑图。

6) 判断所设计的电路能否自启动。

1.同步计数器 1)同步二进制计数器

数字电子技术 第5章 时序逻辑电路的分析

40

5.8异步计数器

1.异步计数器的概念:异步计数器中的 触发器不会同时改变状态,因为它们没 有共同的时钟脉冲

41

2. 三位异步二进制计数器

42

波形图

Q0:2分频 Q1:4分频 Q2:8分频

Q0 Q1’ Q2

43

3.四位异步十进制计数器

1 CP 2 3 4 5 6 7 8 9 10

起译码 作用

电路分析: Di输入的数据,在cp 上升沿作用下,逐位 向左移动,经过4个 脉冲,将把输入的第 1个数传送到输出D0。

电压波形

34

5.5.MSI移位寄存器

M=0 M=1

串行输出

74LS95右移 移位寄存器

并 行 输 出

(1)电路形式:电路接成串行移位右移,并行输入,并行输出。 (2)工作原理:当方式控制M=1时,允许数据以并行方式输入,在cp2作用下,并 行存入J-K FF,并以并行方式输出Data.Q0~Q3。当M=0时,并行输入被禁止, 允许串行输入到J-K FF,在cp1作用下逐位右移。

1

1

1

1

4位异步二进制计数器(74LS93)

电路特点: 74LS93是一个MSI.模2×8进制计数器。从电路形式上看,第1 个FF为2进制,第2~4个FF是8进制计数器。采用两个时钟脉冲 CPA,CPB,有2个复位输入端,为方便灵活使用。

46

74LS93应用

用74LS93构成模16计数器。 将QA(第一级FF输出)作为CPB 使用,成为模16计数器。

(4)将驱动方程分别代入J-K FF的特性方程:

001 000 (2)时序电路的输出为Q3Q2Q1

(3)各FF的驱动方程: J1=Q3 K1=1 J2=1 K2=1 J3=Q2Q1 K3=1

数字电子技术 第5章

锁存器电路图

(1)

E CP 1D 1

(11) 1

C1

(3)

1D Q

C1

EN

(2) 1Q

1

EN

(4) 2D

1D C1 Q

(5) 2 Q

1

EN

(6)

D

3Q

1

& ≥1 Q

(7) 3D

19) 4 Q

1D C1

Q

1

& ≥1

(12)

Q

5Q

EN

5D

(13)

1D C1 Q

1

CP

图5-13 一位D锁存器逻辑图

EN

(15)

6D

(14)

6Q

1D C1

Q

1

EN

(16)

7D

(17)

1D C1

Q

1

7Q

EN

8D

(18)

(19)

1D

Q

1

8Q

(3)移位寄存器

移位寄存器不仅可以存储代码,还可以将代码移位。 ⑴四位右移移位寄存器的原理:

并行输出

Q0 DI FF0 1D Q C1 CP FF1 1D Q1 FF2 1D Q C1 Q2 FF3 1D C1 Q Q3 DO

表5-4 74194的工作状态表

Rd

0 1 1 1 1

S1 S0 × 0 0 1 1 × 0 1 0 1

工作状态 清零 保持 右移 左移 送数

CP A

& & & & & & &

1

并行输出

FA QA Q 1 FB QB Q 1 1S C1 1R R FC Q C Q 1 FD QD Q 1S C1 1R R

74161的逻辑符号

数字电子技术课件第六章 时序逻辑电路(调整序列码)0609

(3)移入数据可控的并行输入移位寄存器

Z

M

Z D3 X Q3MX Q3NX

N 0 1 0 1

Q3n+1 置0 Q3不变 Q3计翻 置1

0 0 1 1

X 0, Z D3 同步(并行)置数 X 1, Z M Q3 NQ3 右移

右移数据由MN组合而定

3、双向移位寄存器 加选通门构成。

t1

t2

t3

存1 个 数 据 占 用1 个 cp

D1 D2 D3、 Q1 Q2 Q3波形略

二、移位寄存器

移位:按指令(cp),触发器状态可 向左右相邻的触发器传递。 功能:寄存,移位。

构成:相同的寄存单元(无空翻触发器)

共用统一的时钟脉冲(同步工作) 分类:单向、双向

1、单向移位寄存器(4位,右移为例,JK触发器构成) (1)电路:4个相同寄存单元(4个JK触发器); 同步cp为移位指令; 移1(即: Qn+1 =1) → J=1,K=0 移0(即: Qn+1 =0) → J=0,K=1

1

4个脉冲以后 可从Q3~Q0并 行输出1101

2、并行输入移位寄存器

可预置数的移 位寄存器

(1)选通门——与或逻辑,2选1数据选择器 A B X X:控制信号 F=AX+BX X=1,F=A X=0,F=B

1

&

≥1

F

(2)电路(4位,右移,JK触发器构成)

X控制信号:X=0,置数; X=1,右移。 Dr右移数据输入端。 D3~D0并行数据输入端。

X控制信号:X=0,左移,DL左移数据输入端。 X=1,右移,Dr右移数据输入端;

双向移位寄存器示例,X控制信号:X=0,左移, X=1,右移,

数字电子技术第5章

(4)逻辑功能分析:当Q1Q0=11时,输出Z=1;当取 其它值时,输出Z=0;在一个循环过程中,Z=1只出现一次, 故为进位输出信号。所以,此电路是带进位输出的同步4 进制加法计数器电路。

EXIT EXIT

第5章 时序逻辑电路

分析举例

【例5.1.2】图所示电路是异步时序逻辑电路的逻辑图, 试分析它的逻辑功能。

3. 求出对应状态值

设电路初始状态为 Q3Q2Q1 Q0 =0000 当某触发器时钟 条件满足时,计算 其状态方程的值; 触发器时钟没有到 来时,则不用计算 其状态方程的值, 保持原有状态。

演 示 文 稿 Presentation

0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1

EXIT EXIT

第5章 时序逻辑电路

画状态图和时序图

演 示 文 稿 Presentation

随着CP脉冲的递 1010至1111在 增,不论从电路输 计数循环外, 出的哪一个状态开 但可以进入计 始,触发器输出的 数循环,称为 变化都会进入同一 自启动 个循环过程

(4)逻辑功能分析:由状态图和时序图 可知,该电路是十进制计数器,或10分频器。

EXIT EXIT

第5章 时序逻辑电路

5.1.2 时序逻辑电路的分析方法

演 示 文 稿 Presentation

基本步骤:

1. 根据给定的电路,写出它的输出方程和驱动方程,并求 状态方程。 时序电路的输出逻辑表达式。 2. 列状态转换真值表。 各触发器输入信号的逻辑表达式。 将驱动方程代入相应触发器的特性方程中所得到的方程 3. 分析逻辑功能。 简称状态转换表,是反映电路状态转换的规律与条件的表格。 方法:将电路现态的各种取值代入状态方程和输 出方程进行计算,求出相应的次态和输出,从而列出 4. 根据状态转换真值表来说明电路逻辑功能。 画状态转换图和时序图。 状态转换表。 如现态起始值已给定,则从给定值开始计算。如 用圆圈及其内的标注表示电路的所有稳态, 没有给定,则可设定一个现态起始值依次进行计算。 在时钟脉冲 CP作用下,各触发器状态变化的波形图。 用箭头表示状态转换的方向,箭头旁的标注表示 状态转换的条件,从而得到的状态转换示意图。 EXIT EXIT

数字电子技术基础6时序逻辑电路

Q1 Q3 * Q2 * Q1 * Y

输 出 方 程

Y Q2Q3

Q1 Y

CLK Q3 Q2

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

0 0 0 1 1 1 0 0

0 1 1 0 0 1 0 0

1 0 1 0 1 0 0 0

DI 串行 输入

D Q3 Q D Q2 Q D Q1 D Q0 Q

0 0 0 0 0 0 1 1

0 0 0 0 0 1 0 1 0 缺少111为 0 1 1 初态的情况 1 0 0 1 0 1 1 1 0 1 1 1

0 0 0 0 0 0 1 1

7进制计数器

其中Q3Q2Q1为计数状态,Y为进位

我们可以把状态转换表表示为状态转换图的形式

/Y /0 /0

CLK Q3 0 1 0 0

*

Q

* 3

Q Q Q (Q )

1 2 3 0

C Q0Q3

设初态为0000

作状态转换图

可以看出这是一个异步十进制加法计数器! 3. 检验其能否自动启动 ?

什么叫 “自动启动” ? 四个触发器本应有十六个稳定状态 ,可 上图电路的状态图中只有十个状态。如果由 于某种原因进入了其余的六个状态当中的任 一个状态,若电路能够自动返回到计数链 ( 即有效循环 ) ,人们就称其为能自动启动。

*6.2.3

异步时序逻辑电路的分析方法

例6.2.4 分析图6.2.10所示电路的逻辑功能。

1、写三大方程

驱 动 方 程 状 Q0 Q 0 cp0 Q 0 (cp0 ) * 态 Q1 Q 3 Q 1 (cp1 ) Q 3 Q 1 (Q0 ) * 方 Q2 Q 2 (cp2 ) Q 2 (Q1 ) 程 *

《数字电子技术》康华光习题解答第6章时序逻辑电路

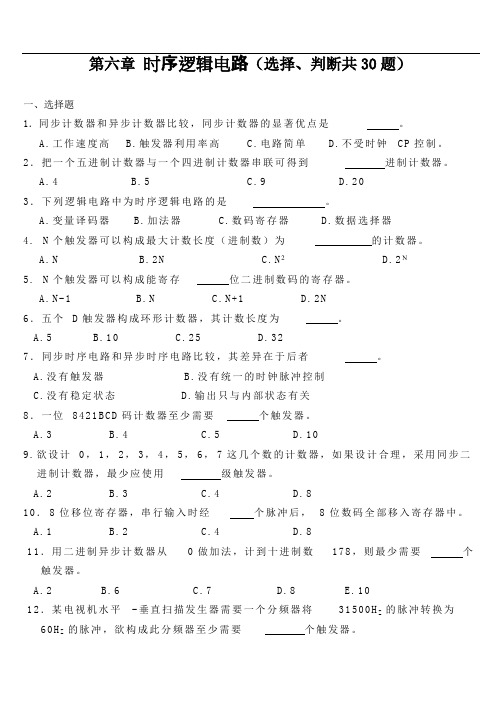

第六章时序逻辑电路(选择、判断共30题)一、选择题1.同步计数器和异步计数器比较,同步计数器的显著优点是。

A.工作速度高B.触发器利用率高C.电路简单D.不受时钟C P控制。

2.把一个五进制计数器与一个四进制计数器串联可得到进制计数器。

A.4B.5C.9D.203.下列逻辑电路中为时序逻辑电路的是。

A.变量译码器B.加法器C.数码寄存器D.数据选择器4.N个触发器可以构成最大计数长度(进制数)为的计数器。

A.NB.2NC.N2D.2N5.N个触发器可以构成能寄存位二进制数码的寄存器。

A.N-1B.NC.N+1D.2N6.五个D触发器构成环形计数器,其计数长度为。

A.5B.10C.25D.327.同步时序电路和异步时序电路比较,其差异在于后者。

A.没有触发器B.没有统一的时钟脉冲控制C.没有稳定状态D.输出只与内部状态有关8.一位8421B C D码计数器至少需要个触发器。

A.3B.4C.5D.109.欲设计0,1,2,3,4,5,6,7这几个数的计数器,如果设计合理,采用同步二进制计数器,最少应使用级触发器。

A.2B.3C.4D.810.8位移位寄存器,串行输入时经个脉冲后,8位数码全部移入寄存器中。

A.1B.2C.4D.811.用二进制异步计数器从0做加法,计到十进制数178,则最少需要个触发器。

A.2B.6C.7D.8E.1012.某电视机水平-垂直扫描发生器需要一个分频器将31500H Z的脉冲转换为60H Z的脉冲,欲构成此分频器至少需要个触发器。

A.10B.60C.525D.3150013.某移位寄存器的时钟脉冲频率为100K H Z ,欲将存放在该寄存器中的数左移8位,完成该操作需要时间。

A.10μSB.80μSC.100μSD.800m s 14.若用J K 触发器来实现特性方程为,则J K 端的方程为 。

AB Q A Q n 1n +=+A.J =A B ,K = B.J =A B ,K = C.J =,K =A B D.J =,K =A B B A +B A B A +B A 15.要产生10个顺序脉冲,若用四位双向移位寄存器CT74LS194来实现,需要 片。

数字电子技术 第6章 时序逻辑电路的设计

17

2.画出次态状态表 画出次态状态表

次态 y=0(down) Q2 Q1 Q0 1 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 1 0 1 1 1 1 0 1 y=1(up) Q2 Q1 0 0 0 1 0 1 1 1 1 1 1 0 1 0 0 0 Q0 1 1 0 0 1 1 0 0

为使电路能自启动,将卡诺图中的最小项 xxx取做有效状态例如010状态,这时Q2n+1 的卡诺图应修改为右图。化简后得到新状 态方程: Q1n+1= Q2n⊕Q3n Q2n+1= Q1n+ Q2nQ3n Q3n+1= Q2n 驱动方程:J1=Q2n⊕Q3n 输出方程:C= Q1n Q2n Q3n K1=Q2n⊕Q3n J2=Q1n+Q3n K2=Q1n J3= Q2n K3= Q2n

检查自启动:设初态为000,来第1个CP脉冲,将跳变为010,进入循环状态,该电路可 以自启动。

11

6.3同步时序逻辑电路设计 同步时序逻辑电路设计 (时钟同步状态机的设计)

1.用状态图设计同步时序逻辑电路 ①状态序有规则的时序电路; ②态序不规则的Moore型; ③Mealy型 2. 使用状态表设计时序逻辑电路 3.使用状态转换表设计时序状态机

8

例2:设计一个串行数据检测器。要求连续输入3个或3个以 上的1时,输出为1,其它情况下输出为0。

(1)因为输入多于3个1,有输出。设输入变量为x;检测 (5)最多连续输入m=3,可选用 结果为输出变量,定义为y;又因连续输入3个1以上有 (7)逻辑电路图: n=2,2个J-K FF,于是可画出次 输出,因此要求同步计数。 态及输出卡诺图。还可分解为3 个卡诺图。 (2)状态分析:初态S0为全0状态,设输入一个1时为S1 态,输入2个1时为S2,输入3个1及以上为S3。 Q1n+1 Q0n+1 y (3)状态转换图如图所示: (4)状态转换表。因为输入m>3和连续输入3个1(m=3)状态是相同的,都停留在S2上,故 (8)检查能否自启动: 状态转换图可以简化成如下。 当电路初态进入11状态后: (6)状态方程:Q1n+1=xQ0Q1+xQ 若x=1时,Q1n+1Q0n+1=10状态为 1 sn S S1 S2 S 0 X 次态;若x=0时,Q1n+1 Q0n+1=00 3 n 驱动方程:J1=xQ0 J0=xQ1 0 S0/0 S0/0 S0/0 S0/0 次态。 输出方程:y=xQ1n 1 S1/0 该电路可以自启动。S2/0 S3/1 S4/1 Q0n+1=xQ1Q0+1Q1 K1=x K0=1 自启动部分

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第5章 时序逻辑电路

2)同步十进制计数器

第5章 时序逻辑电路

写驱动方程: T 0 1

T1 T2

Q0 • Q3 Q1Q0

T 3 Q2 Q1Q0 Q3 Q0

写状态方程:

Q0n1 Q0 Q1n1 Q0 Q3 Q1

分析步骤: 1.写驱动方程; 2.写状态方程; 3.写输出方程。

第5章 时序逻辑电路

[例5-1]试分析图5-2所示时序逻辑电路的逻辑功能, 要求①写出驱动方程、状态方程和输出方程;②列 出状态转换表;③画出状态转换图;④画出时序 图;⑤判断电路能否自启动?

第5章 时序逻辑电路

解:该电路为1个摩尔型同步时序逻辑电路。

写驱动方程: J1 K1 1

J

2

Q1

•

Q3

J

3

Q1

•

Q2

K 2 Q1 K 3 Q1

写状态方程:QQ1n2n11

Q1 Q1

•

Q3ቤተ መጻሕፍቲ ባይዱ

n

Q2

Q1

Qn2

Q3n1

Q1

•

Q2

n

Q3

Q1 Q3n

写输出方程:

Y Q1 • Q3

第5章 时序逻辑电路

列出状态转换表:

第5章 时序逻辑电路

画出状态转换图:

第5章 时序逻辑电路

状态转换表:

第5章 时序逻辑电路

图5-4 同步二进制加法计数器的状态转换图

第5章 时序逻辑电路

图5-5 同步二进制加法计数器的时序图

第5章 时序逻辑电路

图5-8 同步4位二进制加法计数器74LS161的逻辑图

第5章 时序逻辑电路

表5-1 同步4位二进制加法计数器74LS161的功能表

这三个方程能够全面描述一个时序电路的逻辑功能。

第5章 时序逻辑电路

直观描述时序电路中全部状态转换关系的方法:状态转换 表、状态转换图和时序图。

状态转换表的列写方法:任意设定电路的1组输入变量取值 和1种初态,代入该电路的状态方程和输出方程,得到电路 的次态和输出;以得到的次态作为新的初态,连同此时的输 入变量取值,再代入状态方程和输出方程,得到新的次态和 输出,直至将电路中全部状态转换关系全部列成表格即可。

第5章 时序逻辑电路

画时序图:

该电路能够自启动。

第5章 时序逻辑电路

5.1.2 异步时序逻辑电路的分析方法

异步时序电路的分析步骤:

① 写时钟方程; ② 写驱动方程; ③ 写状态方程; ④ 写输出方程。

第5章 时序逻辑电路

[例5-2]试分析图示时序逻辑电路的逻辑功能,列出状态转换 表,并画出状态转换图。

第5章 时序逻辑电路

1.同步计数器 1)同步二进制计数器

第5章 时序逻辑电路

写驱动方程: T 0 1

T

1

T 2

Q0 Q1 Q

0

T 3 Q2 Q1Q0

写状态方程: QQQ1nn20n111Q(QQ001Q0Q)1 Q2 Q3n1 (Q2 Q1Q0) Q3

写输出方程: C Q3 Q2 Q1Q0

第5章 时序逻辑电路

数字电子技术

第5章 时序逻辑电路 范立南 代红艳 恩莉 刘明丹

中国水利水电出版社

第5章 时序逻辑电路

第5章 时序逻辑电路

5.1 时序逻辑电路的分析方法 5.2 若干常用的时序逻辑电路 5.3 时序逻辑电路的设计方法

第5章 时序逻辑电路

时序电路逻辑功能上的特点:任意时刻的输出不仅取决于该 时刻的输入,而与信号作用前电路原来的状态有关。时序逻 辑电路的框图如图5-1所示:

第5章 时序逻辑电路

图5-3 4位寄存器74LS175的逻辑图

第5章 时序逻辑电路

2. 移位寄存器 移位寄存器不仅具有存储的功能,而且还有移位功能,可以 用于实现串、并行数据转换。如图5-4所示为4位移位寄存器 的逻辑图。

第5章 时序逻辑电路

假设串行信号输入端,依次输入1011,并设初态为0,画出 电压波形图:

图5-1 时序逻辑电路的框图

第5章 时序逻辑电路

1)时序逻辑电路是由组合逻辑电路和存储电路两部分组 成,其中存储电路必不可少。2)存储电路的输出和输入信 号共同确定时序电路的输出。

驱动方程: Y (tn) F X (tn),Q(tn)

状态方程: Z (tn) G X (tn),Q(tn) 输出方程: Q(tn1) H Z (tn),Q(tn)

时序图是在一系列时钟脉冲的作用下,电路的状态和输出随 时间变化的波形图。 按照触发器状态翻转先后可分为:同步时序电路和异步时序 电路。 按照输出信号的特点不同可分为:摩尔型和米里型。

第5章 时序逻辑电路

5.1 时序逻辑电路的分析方法 5.1.1 同步时序逻辑电路的分析方法

同步时序逻辑电路的分析是已知同步时序逻辑电路的逻辑 图,找出其逻辑功能。

n

Q1

(CP0 下降沿动作) (Q0 下降沿动作) (Q1下降沿动作)

Q3n 1

Q1Q2

Q3n(Q0

下降沿动作)

第5章 时序逻辑电路

列状态转换表:

第5章 时序逻辑电路

画状态转换图:

第5章 时序逻辑电路

5.2 若干常用的时序逻辑电路 5.2.1寄存器

1. 基本寄存器

图5-2 双2位寄存器74LS75的逻辑图

第5章 时序逻辑电路

5.2.2计数器

计数器是能够用来记录输入脉冲的个数的逻辑电路。

按照计数器中的各个触发器状态翻转先后,可分为同步计数 器和异步计数器; 按照计数过程中,数字的增减可分为:加法计数器、减法计 数器和可逆计数器; 按照计数过程中数字的编码方式可分为:二进制计数器和二十进制计数器等。 按照计数容量可分为:十进制计数器、十六进制计数器、进 制计数器等。

第5章 时序逻辑电路

解:图5-7所示电路为1个异步摩尔型时序逻辑电路。 写时钟方程:

CP0 CP0 CP1 CP3 Q0 CP2 Q1

写驱动方程: J 0 K 0 1

J1 J2

Q3 K2

1

K1

1

J 3 Q1Q2

K3 1

写状态方程:

Q0n1 QQ1n2n11

n

Q0

Q3

n

Q2

第5章 时序逻辑电路

图5-2所示为双2位寄存器74LS75的逻辑图。当 CPA = 1时,

送到数据输入端的数据被存入寄存器,当CPA =0时,存入

寄存器的数据将保持不变。 如图5-3所示为4位寄存器74LS175的逻辑图。该寄存器具有 异步清零功能,当 =0时,触发器全部清零;当 =1, 出现上升沿时,送到R数D 据输入端的数据被存入寄存器RD,实现 送数功能。由于此寄存器是由边沿触发器构成,所以其抗干 扰能力很强。