跨时钟域信同步方法种

跨时钟域的方法

跨时钟域的方法

跨时钟域的方法,是指在两个或多个时钟之间进行同步的一种技术。

在现代通信和计算机网络中,不同设备的时钟往往有微小的差异,如果不进行同步,就可能导致通信中的时间戳错误或者计算机网络中的数据同步问题。

因此,跨时钟域的方法是保证不同设备之间时间同步的关键技术之一。

在实际应用中,跨时钟域的方法主要包括两种:硬件同步和软件同步。

硬件同步是指使用专门的硬件设备来进行时钟同步,例如使用GPS信号来同步时钟;软件同步则是指使用特定的软件算法来进行时钟同步,例如使用NTP协议来进行网络时间同步。

这两种方法各有优缺点,在具体应用中需要根据实际需求来选择合适的方法。

在跨时钟域的方法中,还需要考虑到时钟漂移和时钟抖动等问题。

时钟漂移指的是时钟频率的变化,而时钟抖动则是指时钟频率的波动。

这些问题会影响时钟同步的精度,因此需要采取相应的措施来进行补偿。

在硬件同步中,一般采用精密的晶振来提高时钟精度;在软件同步中,采用算法来进行时钟漂移和抖动的补偿。

总之,跨时钟域的方法是现代通信和计算机网络中非常重要的技术之一。

它可以保证不同设备之间的时间同步,从而确保通信和数据同步的准确性和可靠性。

在实际应用中,需要根据具体情况选择合适的同步方法,并且采取相应的措施来解决时钟漂移和抖动等问题。

跨时钟域信号同步的IP解决方案

IP Rick Kelly Synopsys2009 10 Z s âU©¶º·Â¤ Soc ½[IéÖà ÌÊ Myê-× ÑÐ Z U© âN 1J0 K h´×k i :©Å )å¬Z âU©Ð ÐjÆNY ? -x × Å 7X ©àÅ} \Ç ç~= c{½© Å !Cë¥ÎÁÝdÀRËZ Kë¥ E§ wZ âUÑÐ¦Ï g2 S ^?© a»íÑ âU CDC ãì%!ËZ¯vt:¦ 6Í'æp«uî l] Synopsys DesignWare n O . ËZ@ЩCDC È8 × o¨³/ ÌÊ MHè R+ !C+Wo¨`"BI Èß R âN 1J âUÑÐ<G âU E§©ËZµT©K ãì R$+|9 >L©ãìÝ¢C<« s © âU å¬ ãì© : e Û Z DesignWare È8 × ìNÈ8 >• V K — DW_sync• #K — DW_pulse_sync, DW_pulseack_sync• ³A &ÓK — DW_data_sync, DW_data_sync_na, DW_data_sync_1c • ¡K — DW_fifo_s2_sf, DW_fifo_2c_df, DW_stream_sync • Y* m — DW_reset_sync • «5 ⶺ K — DW_data_qsync_hl, DW_data_qsync_lhV K ãìu ¾ ⶺ©1Je¨,G 6 K © ⶺ©Ó4 gèÅc1JØÃK !Ô~ ¼ ØÃK g Ô~ m Q 1 ® Þ¨ Ab_P K ¿ª© âU©s Ó4(åׯ %:¦© ãì u ÉEP© Ó4W ÜÒ0¿ÜÒ1 ä©Õ£Õ°u E¹× ÉEP â1J I½ § ±z¦Ï ±z¦Ï I½E§RÉEP©r² ä 0 ä:¦ÙD ¦Ï È8 ±z #-6Ô¿ÜÒ1 ÜÒ0 Å © äáF 8 r² ä 0 äÄÙD © à°p Q 2Clock to Q delay â¿Q qÚ FF Minimum specs ÉEP f ÇQ 2 È8 ±z # ¨ äÜÒ > ¾Clk_d U©1JÜÒ > ¾Clk_d U©1J¸3;r²©¿Ó:qÚ© j â¸3;0 ©¿Ó:qÚ© j âj © â¿Q qÚR U Z bª¨ S<) ¤ «mb 7l=K1u ]¬]¬ªM@bª MTBF ¢L D!f clk c¥jb¦¯s f data c^[2,¯st res c # UX -vybªT 0;T1c " 1=z yL^ _I l3¡¢L w ? 6b J ?bN Cq yf %©x ^ {-v X 9ao\* «mªybª® Z E y #vb 95 ¥v 2 1= WyN& c #`k E B+bP?¥v 2 1=y #`k b¦iK %/ 1=FF1yb¦ Q Pb8yb¦:e 0FF2yQ b ª n A}G d|zG °^[ £sy°£Ovg . 7l= d5 ao T Cy MTBF r(c ?FPGA Ft`k Dh+ 3 '4d? 1 ? U Z C¨ybª H - FF2yQ bªyV$ 2 Yd5 1u U >3Sampe MTBF test … MTBF p x ~Error Counter§ ^=>3 3 7l =T0 T1"( 'G46 > 7 #+ ; $ % <& $ % I4 4'865B ,1 F "( LA?( 4 1J C *K - 2 : 6C M3 6MTBFHD M 3/3 @.5BE= ! 1T0 T16(I4F )0 MTBF ?94 4 1 > "(65B* ` 0 fAh" P6MTBF ~ R• P ;S~_D an Debora Grosse, Unisys, EDN, 1994 /archives/1994/062394/13df2.htm• _D PxQ Kleeman & Cantoni, IEEE Transactions on Computers, ol. C-36, No. 1, Jan., 1987 • Google:MTBF P2r/ >j2r©¬v+&T[u T[§ K¥| U¨E 9d¦= ªFzp ~T[$W Cl9T[u XLd g3 T[ !Oy3« Y V Oy ~d¦:}u d¦k) %h 0 ctp V & d¦=~( 1 85 9w = ª]! ¨E7 B\ 1/2d¦5i~M¤ T[u iª~p V ^ # ¢ ©¬ 9 ? T[oNd 0} @|7I¢ ¨E7b FzpK( ¡ / #ane9 J<~d¦= ª]! s -785a – T [u .Z '~ h 0 H =V -{£,8 5b – 9= ª@| ¨E 70 1/2d ¦5i ~ U85c – s D -7 0 U 1/2d ¦5i ~ U85 d ¦=T [u ©¬G >j2rk 40 |DesignWare ~DW_sync q h *_d¦m 1.Z'~d¦m 2d¦m 1¨E7.Z'~d¦m 2d¦m 1.Z'~d¦m 2•• f_sync_type P6• tst_mode:0 => 9 4 1=> j) 2 => ^bCY "• verif_en ( 7[\ 0!S )$ f_sync_type 65* P6 +W1(#63MKgT8/#6 h I DW_sync Q : U K P6B :> :l 2mX$ :i% ]TfaJ_ L .B:i% KfaJ_ >@ G* -R H N8D;hI(#73MK8A eckd& ?EOF% KVCls s%Clk d%#7b – `' )$k dc – <'K]Z8A ;= 8A#7 :i% K e L f a0 c e=RJfq xM 2 f +M ~ q f:>A w h UI f8E p A 0q 70NPfL +M cq G S" D) c @ NRZ +'bK? p u c@ RZ +'bK? /8Fj clk_d2O6 0- km1f + H r(#f ~O k0v5_! cfKZEvent in clk_s clk_sReturn to … Clk_dCaptured in… clk-d/8 NRZ +'b K?f ^l#M 2 fq ) c DW_pulse_sync%M q ,X. /9 T clk_s fs nV f {ey}t0clk_s ] M 2 pT clk_d fsnV f {ey}t0clk_d gf M 2 02 c NRZ +) 9`Q f 3a[ p d L & FuYf {ey z<Register… ) |parameter, reg_event0. 4 o;7.NRZ… x2f NRZ +Multiple… 5;7.,X.History… c W\(#f$*;7./9 DW_pulse_sync%M q ,X.Multiple … 5;7.,X.Multiple … 5;7.,X.Busy state… Bi_CNRZ feedback ack_delay=1 NRZ& ack_delay=1Multiple /Multiple /Busy state #83$NRZ feedback ack_delay=1 NRZ F ack_delay=110 7?6DW pulseack sync= /-E> F C5DW_pulseack_sync A) : +7?6= / 10%9 A IP & NRZ F < 0'7?2,& *G6 41D DW_pulseack_sync@& B;6." F!(= smbC u¿F¯®¢: u¿Fu C u¿Pn³² ` b µ¥½ u smb z;¡, u¤#s" B K } 110110019 01011010 8 b z3 7 q9 Ci 6 $ LCuU Na d+ Qz .8 ;¡, s" the initial value (11011001), the final value (01011010) and six possible intermediate values ( 11011000, 11011011, 11011010, 01011001, 01011000 and 01011011).Source… bDestination clk u¿1st … 1 = OL@2nd … 2 = OL@Intermediate value ² s"Intermediate value ² s"B11 u b s"C= smb u»& e¦ ² s" t w ½ Sz ¨ u = @ ´ º°; ½ UP¯®u¿± smµ¥= l ksm 7· ¬n8 7A Rn8 ¾r smOL@ DW_pulseack_sync ¡I7·^¦ ¬n8 ? Rn8S ¨!< smb = @DW_data_sync¡xJDMg Æ 3 IP Ä ² ¤jsm c; P(µ¥¼ p ua smL%¡1 B12Optional … ;¸ usmOL@Handshake… = lº°Send … 7·o/B12 S ¨ DW_data_sync b = @¨W¶ÁÇC u¿ u¿_]T H h | = u p ¨!< = @;¡ Y7uWÁÇK CV Z uW)z'Àa f -V £½ p0 ¨tX 4¹²ª 5s ack_delay= 0~µ¥¼K u¿ u¿_,\H -; = ¨!< sm; C . u¿1 >{* uÂ* q9 CuWTÅ'ÀaÁÇu yJ½ Ȩ ack_delay = 1ª K z W¶ -C|D ¾E*©[ ÆÃ2«vQw \J G tXw ack_delay = 0 ¹ §-[1]• clk_d >{ VZ²clk_s * >{ r_sync_type - 0.25• clk_s);' 45clk_d *);' f_sync_type - 0.25• f_sync_type = r_sync_type = 2, Fclk_d = 200 M Hz"— Max Fclk_s = Fclk_d * (2 - 0.25)— Max Fclk_s = 200 M Hz * 1.75 = 350 M Hz[1] &:6(. 1/ " "8 " 7 45clk_d"8 %)1/4 $ &* )#2,0+! 3 -9 AX ¹$¶´ ñêÜã Fclk_s * (f_sync_type + 1.25) [2] 3D !° ¿:´%FG Á Q ¶´ ñàs´x0 D ^ Ú @ æÎG gQ 4§T 1 ñK ´ ó. Ì O b ÷Ï?N d @ Q÷Ï W¼jR1a kL /{ rÏ´ëá²Þ "X Q^ [ ñ]YMæÎ g`-.\?ç4 ûêëá9S åº ¢bà [° [®å ¢ D î°DesignWare´ f¹Ô´ vÂG M DW_ data_sync_na P 13 IP # >I G û´ JHï = a´ëá²Þ ÚªÕ ñúÏ [2] Fclk_d Fclk_s * (f_sync_type + 1.25).Event … G ëá²ÞP 13 f ac ¹Ô%F ´DW_data_sync_na vÂG MvÂG ´« x0X Q 6 v C ?¯ A b ö¸ ö¸ã¦ 3¿:´V]YMG Å^ m?ã¦Í( ÇQ äî ñ ?¯ A ¾ Ì ´]YM DÈæ+ ½t å ` ßI '{ 'QÛXÝ ñTµ£Ó M´i°n ö¸vÂbà [° Ó M '´ ö¸*Öw!°à¿:´G }c Q Æ ´µ£ âz ´ kvÂG ´B º« x0¥=4 w¡ Øò ´§T clk_s "X w DÈÏø^ É ¡ #§ ñ´U³§´æ+Ë©.´·^ày´v ± ²Þ e k DÈ_Ê ó´ h)»Üã: ñK V]YMG b DÈì4Üã ñK ´ã¦Í( ' Qåºx0 w D !° ;E]YM £ |?¯´A8 g/Z ` èÄË© qLast value ´ ' New value' Control… 5¬t Counter Ó MHigh count û Óð^å x0 DesignWare # : ñ㨠vÂG M DW_data_sync_1c P 14 G M D ¤õYQû ó h)»«u ´ 㦠´ã¦ 'P 14 DW data sync 1c : ñ㨠v ÂG M[2] ùé°Ñ2(×Ò?Mk L ñ~7Q &í Üãclk_d ñK ´1/4 , ºx p ´ ÙÃÓÀ l Ú<Ðôo BQL ~ QL]8{S : ~QLS v_sQL ~ QL] d@' 8QL ~G 8"9J% S lKn n back-to-back EdQL, QL3\ur1 g < b DW_data_sync durRYm0 R QL] t8u;P dQL= o*d )q6#>an nEdQL, < b FIFO DesignWare Library#d+S FIFO z +i/RAM d b 715 ^:#dO }c|x y?QL$ (RAM med:#dF& }c|xy?QL RAM w-Push logic O }c|Pop logic F& }c|FIFO Controller FIFO N)5Push interface O M/Pop interface F&M/715 2+i/RAM d+S FIFO[ur b DesignWare k DW_ffoctl_s2_sf4DW_ffo_s2_sf U>a AT`IXH d3\ +S FIFO 716 p 1999BDh! jWV U k f8DesignWare Library IP#C.ZPush logic O }c|Pop logic F& }c|FIFO Controller FIFO N)5Push interface O M/Pop interface F&M/716 T`I X H d DesignWare+S FIFO N)55\[?S> _# aMTOz] ?S> _ N|FIFO 3z]DW_ ffo_2c_df)DW_ffoctl_2c_df c ,127 } ?S> ID / DW_ffoctl_2c_df H LZi -DW_ffoctl_s2_sf H _ /• ID0RAM ye• Rg RAM KE_{L4• H %U FIFO Xb f• H Rg RAM_o!'] $Pre-fetch cache ! vd2Push interface (…) GuF" lK*)[?Pop … < F" lK*)[?In-progress logic ~9Ckwq,17 y Q ?S> _DesignWare N|FIFOB` `8KEWjY&/xwq^pH 6 KE %s+hjY_N| ,18 -t :]= 1 -P7N;_A mKEWs+hjY _N|.(Return clock s+N|Return … s+KEQJReturn… s+KERequest clock nVN|Request information nV @Master Chip jYOff-ship logic jY/wq^p,18 /x w q^p R+ r_N|)K EEvent …. .@=2<19 4:3DW data sync na('#6 .,(' >0; 7 8/%* ; "3 A)C $ 5 (' >034 B1DW_data_sync_na 19 ! D?B-+ D &9('R tl ¿ ÀÜ X« ©Ì ÀÌ k] >ÕM tl .Ó±Ì ¢)N ¢tlS$©2 v R:xÏFIFO f>©g±Ì DW_ffo_2c_df C AW_ ffo_s2_sf ¦ y à ¢¦ S G ÚPʾ ¼ º Â| Ì ¥5tl ¿k]zÜ xbFIFO { v ÈÀ UtÎ DW_data_sync_na-type IWtlÄ®³O@G J*W T Ä®ÍuO (s R A F 20j¡ âtl ? Dv ¢V 7DW_stream_sync IP o! ,:xÏFIFO ³+v z xbCz[ ʾ ¼Receive control mqn1 Send control ;Æn1 To … ªclk_s ×`ʾ To… ªclk_d ×`ʾF 20 DW ? t l t l ? DW DW_stream_sync a depth 8tn1 ³O ÈËtÎ W _tl ¹ >Y a t"·§ f_sync_type + 2=±f ·´ » ~ \> Y DW_stream_sync Ô _tl ? )N »Q S$©2 ©QÌÒ xÏ^/j Ûtl 9tl Ð ÐÑxÐ%¶DW_stream_sync Å L3³O ÈË tÎ> µtl G£h tl xÏ xÏ Á® Gtl ;x °tl6 ³O ÈË tÎYÇ L3 G Uj±Ì¢ ³O ÈË tÎx ±¨0Ù ^/ 9 ;²Bubble … ¿-tl* ¯ xÏÉ xÏÉ Ð ^/Gtl ¿ xÏ x DW_stream_sync # i ¿-¤ |tl B} F 21y R H·§ ØK&t" ÈÀprefll_lvl 8t 9 a depth 8t .DW_stream_sync > ?x£c3dC£crhHM ¿' tl Ö©2W oÜtl G ½Z¸^¬E*<4x p eyVF 21 w t l t lSO: / /QuDesignWare Library G ]_,Y IP# 4 9.UeEp- %NEYSOqv i qv6 = 3/ 'Qu $Y@1I FIFO@ (YZY *R sjc Qu'nB ZY+G#b ?DY>o 8am"c 9# khmW / 5 %N(DW_reset_sync HtKM_qvY!V )22 M IP b0L[+ R-'ZY- YlgXfY%NQud2J5 [ ^T7;r`T7Y VSource … R @Dest. … ZY @)22 DW_reset_sync/ 5 %N(DW_reset_sync b0mWR ;ZY & YQuA H@ R-'ZY-YlgQuYL[5 )23 <\FR & CPYE5 )24<\ ZY CP)23 DW reset sync R & Y E524 DW_reset_sync54 4'/+! 6 'H9:>=G2 .; 'H4 'H ) EC'H*I 'H 81? G2 7J$4&-(A@D7'HB3(< %#Source … . "<(high …)JFDestination … 54 "<25a – 24'H,0Source … 9 *B%$ (high …) MJ"Destination … =< *B%$3E DW_data_qsync_lh . > ; LAML0K< 6/,- + DE /, G(<9" IAG'<=<" #40K7: 2 =<"<? C &1 FH8C )2C " 5H8!25b@ 2<0K 7:25 ; L A ML 0K < 6/,- DW data qsync lh/26C` s[DW_data_qsync_lh ofHE kJ\J< Q6RJ</C` IP _ 0Jt^ $]\Jt> VJtJ\+SHE kInternal … rk De;7. Previous data: "\HE/26. DW_data_qsync_lh J<(low-speed domain) q2 Control … G W?LTiming reference J<36N@=u j>\]\2,jB\V2 kHE s[( -DW_data_qsync_hl )h@81bZ5J<n p[ vdwvJt\ +SHEF's[ J<3 *M 9HE&#[\Q_J! /27 6 C` 6NJ<TX 2 :YIPs[ilUg%. 0n A KV2 [ sOMc]\2J<3 *\g%.s[ilUg%. /28C` DW_data_qsync_hl mfJ\J<//27a – J t T X 4 2/27b a 2\J t T X/27 [ v d wv J t \ +S H E F 'DW data qsync hlPrevious data ( d_>28. DW_data_qsync_hl fTCDC bc±¹? \E 64 E NI< H DW_sync § 8s S ´9¦ 6? f¯C"7[, «¢ £f >29 ^I? f¯Cbc ±¹Signal A … 6A«¢ ¡Signal B … 6B«¢ ¡Clk_s … clk_s CMultiple … ENI<8s<Logic combines … 7 k clk_s C 6 «¢ ¡Clk_d … clk_d C>29 f¯C b c. H Synopsys Leda¦n omQ! F '&CDC bc M ¦ Q!/ #L¦ b cg: ) ° x?±¹g ·ENI<8s< A*fU {Xj i 5 ? y r ¥rR S a &¦ ±¹ = ENI<8s<? fu qA |&K 8 fU ? MZ$ ? 63+ nf¯¬7 k9 3+if ª¤N f¯ N 8s © 0 ? Jf ¦ 3+ `N+1 f¯ ³ MTBF¶R D ¦ ±¹? y 2~WS ¸ ] 5 4i?%;¥ 9^ 2ow¦ n±¹ eVg? f zt 2<pB >30 g rH M n 4i?n 2<2~¨1| f ¦ ^ h &±¹ ¦ g lP2~ | YOµ - G® f²^ 7}@ vibc±¹ I?Clock … `¦ Q M+Noise 8>Metastability … Q /7l;930 y k s ¥h| /7l;b@|_qa¥y (5 ?y7| ¥hl; _qa= % :}|£ { I m:0)| ¥h` VZ |c ] 1d2 a 2 ] * c^ ] Ug '6e| ] :4o7| /7' ?y7` J2 ¢ [& ?y7gN ¥h |l; 931Missample … ¥h[&Synchronizer input 4o7History … +3HC7Two … 4oSychronizer output 4o7 $931 = ?y7| ¥h k s¥h_qL "K DW_sync " .Vd D¥y DW_sync|DesignWare CDC IP: O z §f]B/x7g\ Ip 4o7 |§f[& I Verilog ~ 2F ¥y vP|E vcs +defne+DW_MODEL_MISSAMPLES…I VHDL ¥y…_cfg_sim_ms¤I U1 DW_sync¥y¤ dw03.DW_sync_cfg_sim_ms; end for;R2¢ -]verif_en = 0 Yup G |! S# yn¨vP A 1V R d D verif_en¡W_j 932V verif_en = 1`|DW_sync| ¥h,wi9verif_en] 0 1 2`M 6e ?_sync_type?_sync_type to ?_sync_type + 1?_sync_type to ?_sync_type + 31 verif_en-]|]rT ?_sync_type X-]f_sync_type y t< }|<|`M U r_sync_type y }|< t<|`M |]Width ;AWidth ;ATo … sh1j/Yx)2Random … RN)`2Random … RN)`2332 4verif_en = 1Ob DW_sync} U W Z~]{ 4 O@ fD8O } UP-q47 O 0Q Ln:4 ,q4 a DW_data_sync_1c bt\6NM/YG I-m?w# 4|o verif_en = 2O DesignWare Library CDC l - 7 3 O 0QS Xi NM [^ 333Hd eG b} U(_V3 4 -q J 2 RN %K pb3 '.<:2Width ;AWidth ;ATo … sh1j/Yx)2Random … RN)`2Random … RN)`2333 4verif_en = 2Ob DW_sync} U W ZDW_sync H ab} UX5 - a Bg4=/ O$P )`+&bFk v UOP -q!^bcEu NMbX5 9Tz r>b|y * u N bC1 "- a e%( $ " DW_ sync ) # ' ! & 34Source … À ÝDestination … ÎÌ Ý1st … Ø1 I·idQ2nd … Ø2 I·idQIntermediate Ā¿ .Intermediate Ā¿ .T34 ä_ ëì/ .Ì÷Ċ±³YË ÷Ċ±UgĐāí CÉĘw& ĒĔU MTBFĔq&Ì 5 ąq ėÙ ~č ď äð8 CDC ª9Ï2ÌĎę ¶³YĊÊ DW_sync ąĀĆ ÷Ċ±í ÌĘÜCɬ @ĂÔĎę 3'¬ø U ´÷Ċ±x } DW_sync̹ %XąĀ 50%Ì Ā¿Æú ñ b®U HÇ ċÌCDC =[Ç4j DW_sync÷Ċ±y³ÌÛà"Ð <Ìö 7 GĔqÒ,gĐéÂ4 #CÉCDCĎęoè¡kĎęCDC I·Ï2ÌE ĸĎę¢^idQI·QL ©A0Ì¡k U Design Compiler l ñCQ¡k8 ΰuÌI í ¶o3# Gć1VĄ ä_Áü tđ9«!Ì¥mĕÕÌA0 ã ¢jI·¥aÌñCQ R¶ ąq ïąĀ > { ąĀå¨ {ÊpÑÌ × |@ ñCQ¬¤ Ă ñCQæDesignCompilerÌB-2008.09èzc nG f ^ × |@ ñCQU DesignWare CDCÞ! L ΰ ©Ì¡k æ>vÊ ¶Ėä;¢ąĀl synlib_preferred_ffs DC Dċû ©A0JÖ6îãÿ Ì )b b® Ì ©u?M JÖ FFSYNCFD1P FFSYNCFD2Ìpóf × |@ Ì IñC Q 7 O lgÆĂ A0̵ҡkset synlib_preferred_ffs “FFSYNCFD1 FFSYNCFD2”ù» ¶DC DċÌ .¢ AÅÌ ¨ 7 ¢ Tcl6î ã ¶ª9ÎÌF A ñCQ ©A0j B-2008.09:ÌDesign Compiler¬ø G (ÊTcl娬¯ õò ÌDW_sync I·QidQ rÊÊ fÌñCQg)¬¤ e G Ìùº *Ó)å¨DesignWare CDC ßDesignWare Library4?M ^ÔCDCĈ! Ă Ĉ!¾Í êShsÌý ČvÊ• Z¨I· DW_sync• !I· DW_pulse_sync, DW_pulseack_sync• ÚA $þI· DW_data_sync, DW_data_sync_na, DW_data_sync_1c• ¼I· DW_fifo_s2_sf, DW_fifo_2c_df, DW_stream_sync• \% t DW_reset_sync• Ï2 ČÛà I· DW_data_qsync_hl, DW_data_qsync_lhĂ Þ!X4â ÷Ċ±y³ { ô G UHÇÌ"Ð ď4²½8Ďę ã ēUgĐéÂāí `NÈç ¦K ä²½8Ďę ¶] ËB 9Ìĉâ { £+ j IPăí D ÁüvÊÌïºG áWë §2Synopsys DesignWare Library CDC IPÌ£^-/dw/buildingblock.phpIP … IP VwcInformation link L T935 DesignWare Library~u:Vwb z Z hNVw{a o ^> L T 935 TQ5WSi" 1AmI A mU*r ack_delay=0 Zo k (: m =U*r + o DW_data_sync z Z 6 N ' :jZ K CU*r 4fG :po< ?R '|%r oWS *D^X WSB@7Z D @::jZ d$ ,gx qm lU*r 3opoZ ,gZ D 2l_EM] o;] : sM# v r 4fB@7 t)R ' r 3 r 3O&&}P XWSJ'_K oHm n r 3o/8 s- M# o9 [ 9 m DW_data_sync!F`U*r . ack_delay0W o y4f D\r_sync_type 0W 2 o YeSynchronization …. :ack_delay=0, r_sync_type=2 1clk_s KZo4f- M#Internal … ! r 3Internal data to capture: R o! WSNew data XWSAck … clk_s $ ! " $ clk_d Second … $ ! " % $Data … clk_s clk_d #0NIoA!) BIp-ae, L7? ZI9jO? J , Q, m$ Z]h &1,clk_d LHZ6 pA!IR'I 1,A!Z clk_s ,Ll%bZ6 pI $ "V kP Ll%bZ6 pA!clk_d 5qf$X,TLHZ6 pA!clk_s KHZ ` s 8:c4 31*Cd data_d @fUZ BIpAdd …/ IoA! ]2> #=fZEDCd BIpInternal … m]h &Internal … fCdZ mEDHold time BIpNew data FED+R ;=r B [nYKG Z<;I Pclk_d clk_d Z(MPclk_s clk_sZ(M Fclk_d clk_dZtWFclk_s clk_s ZtWr_sync_type 'S_EJclk_d Clk_d Z6 pA!Jclk_s Clk_s Z6 pA!Thold ED31*Z BIpfUk g^ i .\+R ;=r B [KG Z<;J1) # / @ 5H F D% <>clk_d> : % +2 F D>clk_s : !6> F- L2) <# / @ 52 F D>clk_s>8 5H F D%>clk_s> : N !6> F- L N .I=> 9B1 *4 N = r_sync_type(7.C > , KG& E A?$;) clk_s"clk_d>5'!6J0/ 3 = ( >Jclk_s"Jclk_d)K B t DW_data_sync_na\v r ); t DW_data_sync_na\ wv\ v rL N ;p\ <4 !iX3 T YVv` [\* + &v\ T c p\ <vYV`HO_^ ;wv\ f# .n| ;t s YVX3eM vp\ .n 6vO" ; zO" { YVeM 5kBA9$ ?0 CYVeM vT 6 ;wv \ v3 7b 6 p< F!iX3 YV z/ q"; v\J: t DW_data_sync_na v }5k F^ f_sync_type1Y 2 \ ]Synchronization …. ;clk_s >N\ DW_data_sync_na P2sv5k/Internal data change flag YVX3eMInternal … T v YVNew data ZYV- Data… YVI; T YVX3eM 'U SyZYV4t- First …. YVX3eM5k9v{ }$ ?WYVeM vX3First stage … YVX3eM5k9v{ }ho(jX3Second … YVX3eM5k9v{ }ho(jX3Data captured … YVu clk_d PT 5\ZYV u clk_s ~A@d (\ Q,8 R\ `HO" v\J fD^ YVeM v3-2s;= G Q,` v clk_s .n j\ ;5 \ a clk_d v .n= G Q,v`[4 g C = G Q,`[4 v| xv clk_s .nc 2s\ F l= G Q,` 4 v clk_d .n % EBA9T data_d P mv R\Adding … ! Internal …Internal data …New …Hold … !Pclk_d clk_d T*JPclk_s clk_s T*JFclk_d clk_d TkQFclk_sclk_s TkQ f_sync_type (M[CJclk_d Clk_d T9 g?"Jclk_s Clk_s T9 g?"Thold :CA75,T @Fg`Nd aY b 0V1) . ?"X& IE'_ ]1$RT clk_d T #O 1 Ie'_ ]T clk_s #O ) *JT'_= i2) $R. ?"X& Ie'_ ]T clk_d T #O IE'_ ]1T clk_d T #O)N *J T'_= i N >fST(M[C! 8G N = f_sync_type+14K>\ T :%hc2 ^ ' ZW/P6 clk_s +clk_d TI3*JgB?"F ' S 4 T Jclk_s +Jclk_d 6-L 4 :<j @ UH D T;:G。

多比特信号跨时钟域同步电路以及方法

多比特信号跨时钟域同步电路以及方法English:Multi-bit signal cross-clock domain synchronization circuits and methods are commonly used in digital systems to ensure proper timing and data alignment between different clock domains. The main challenge in designing such circuits is to ensure reliable and robust synchronization while dealing with potential issues such as clock skew, metastability, and data corruption. One commonly used approach is to utilize synchronization elements such as flip-flops or latches along with proper clock domain crossing techniques. These techniques include two-flop synchronizers, synchronizers with handshake protocols, and self-timed synchronizers. Two-flop synchronizers are often used due to their simplicity and effectiveness in mitigating metastability issues, while protocols like the Gray code handshake can provide more robust synchronization. Additionally, self-timed synchronizers eliminate the need for a common clock signal, making them suitable for asynchronous systems. Overall, the design of multi-bit signal cross-clock domain synchronization circuits and methods requires careful consideration of timing requirements,synchronization element selection, and robustness against potential synchronization issues.中文翻译:多比特信号跨时钟域同步电路及方法通常在数字系统中广泛使用,以确保不同时钟域间的正确计时和数据对齐。

FPGA设计中跨时钟域信号同步方法

FPGA设计中跨时钟域信号同步方法邹晨【期刊名称】《航空计算技术》【年(卷),期】2014(000)004【摘要】随着FPGA系统设计的复杂化,系统内部的各个功能模块往往需要工作在不同频率的异步时钟域中,因此系统内核心功能模块与外设的通信设计无法避免地会涉及到跨时钟域的数据与信号的传递问题。

尽管跨时钟域的同步问题并不属于FPGA系统设计领域的新问题,但是随着多时钟域系统的常见化和复杂化,使得跨时钟域同步这一要求具备了新的重要意义。

在对跨时钟域设计中容易出现的亚稳态现象及其造成的影响进行简要概述与分析的基础上,为了减小亚稳态发生的概率和降低系统对亚稳态错误的敏感程度,提出了四种跨时钟域同步的解决方案,较为详细地阐述了设计方案,对设计进行了评估与分析,并给出了优化设计。

%With the complication of FPGA design ,the different modules in the design always work in the asynchronous clock domains .So the core module in the system has the problem of cross-clock domain when communicating with other modules .The cross-clock domain design becomes more and more impor-tant with complication of the design .The paper firstly introduces some basic concepts and elements of the metastable state occurred in the cross-clock domain design and its infection .In order to reduce the proba-bility of the metastable state ,this paper presents four FPGA-based synchronous units in detail and makes some discuss on the mend of thedesign .The performances analysis ,simulation and synthesis result is giv-en at the end of this paper .【总页数】4页(P131-134)【作者】邹晨【作者单位】中航工业西安航空计算技术研究所,陕西西安710068【正文语种】中文【中图分类】TP331.2【相关文献】1.跨时钟域信号的几种同步方法研究 [J], 赵晓海2.SoC中跨时钟域的信号同步设计 [J], 邵翠萍;史森茂;吴龙胜3.FPGA设计中跨时钟域同步方法的研究 [J], 唐辉艳;李绍胜4.FPGA设计中跨时钟域的问题与方法 [J], 王利祥;5.跨时钟域传递位数据的同步方法 [J], 高焕琦;岳亚杰;高俊锋因版权原因,仅展示原文概要,查看原文内容请购买。

跨时钟域信号的几种同步方法研究

跨时钟域信号的几种同步方法研究赵晓海【摘要】为使跨时钟域信号能够被目标时钟正确采集,提出并总结了几种同步方法,详尽论述了这些方法所涉及的存储器计算和synthesis设置。

跨时钟域信号的同步方法应根据源时钟与目标时钟的相位关系、该信号的时间宽度和多个跨时钟域信号之间的时序关系来选择。

如果两时钟有确定的相位关系,可由目标时钟直接采集跨时钟域信号,且在synthesis中应设此两时钟为同步关系;否则,需要借助FIFO (First in,First out),在synthesis时,此两时钟必须设为false path关系。

跨时钟域信号的宽度至少应为目标时钟周期的两倍。

对于彼此有确定时序关系的多个跨时钟域信号,在同步前应使其保持足够距离。

所述方法在CMOS(Complementary Metal Oxide Semiconductor)图像传感器的设计中被实际应用。

经仿真和芯片的系统验证,该图像传感器可以正确完成信号在各时钟间的同步,并以60帧/s的速率正确输出分辨率为1 280×720的数据。

%To have destination clock sample correctly signals across clock domains,this paper proposes the several synchronous methods and discusses how to calculate depth of corresponding memory and how to set the synthesisparameters.According to phase relation between source and destination clocks,width of signals and timing relation between the signals,the synchronous methods are chosen.If the phase relation iscertain,destination clock may directly sample signals across clock domains,and synchronous relation is set to the clocks insynthesis.Otherwise,FIFO(First in,First out) must be applied,and paths across the clock domains must be set to false path in synthesis.Width ofsignals is at least twice as long as period of destination clock.If signals have certain order relation with each other,sufficient distance must be held in source clock domain.The methods were applied in a practical design for CMOS(Complementary Metal Oxide Semiconductor) image sensor.By simulation and chip system verification,the sensor can synchronize signals between clock domains and transmit correctly images of resource 1280×720 at 60 fps.【期刊名称】《电子设计工程》【年(卷),期】2012(020)007【总页数】6页(P139-143,147)【关键词】集成电路;同步电路;图像传感器;时钟同步【作者】赵晓海【作者单位】北京思比科微电子技术股份有限公司数字部,北京100085【正文语种】中文【中图分类】TN79当前,实现图像采集、处理和压缩等功能的数字集成电路产品得到了广泛应用[1]。

跨时钟域信号的几种同步方法研究

V0 . 0 12 No7 .

电子 设计 工程

Elc r n c De i n En i e rn e to i sg g n e i g

21 0 2年 4月

Ap . 0 2 r2 1

跨 时钟 域信 号 的几种 同步方 法研 究

赵 晓 海

( 京 思 比科 微 电 子技 术 股 份 有 限 公 司数 字 部 北京 1 0 8 ) 北 0 0 5 摘 要 :为 使 跨 时钟 域信 号 能 够被 目标 时 钟 正 确 采 集 , 出 并 总 结 了 几 种 同 步 方 法 , 尽 论 述 了 这 些 方 法 所 涉 及 的 存 提 详

储 器 计 算 和 snh s 设 置 。 跨 时钟 域 信 号 的 同步 方 法应 根 据 源 时钟 与 目标 时 钟 的 相 位 关 系 、 信 号 的 时 间 宽 度 和 多 y tei s 该

个跨 时钟 域 信 号之 间 的 时序 关 系来 选 择 。 果 两 时钟 有 确 定 的 相 位 关 系 , 由 目标 时钟 直接 采 集跨 时钟 域 信 号 , 在 如 可 且 snl s v tei l s中应 设 此 两 时 钟 为 同 步 关 系 ; 则 , 要 借 助 FF Frtn Frt u) 在 sn ei 否 需 IO( i , i t, y t s si so h s时 , 两 时 钟 必 须 设 为 此 fl ah关 系 。 时钟 域 信 号 的 宽度 至 应 为 目标 时 钟 周 期 的 两 倍 。 于彼 此 有 确 定 时 序 关 系的 多个 跨 时 钟 域 信 号 , a eDt s 跨 对 在 同步 前 应 使 其 保 持 足 够 距 离。 述 方 法在 C S C mpe nayMe l xd e i n u t ) 所 MO ( o l metr t ieS m c d c r 图像 传 感 器 的设 计 中被 aO o o 实 际应 用 。经 仿 真 和 芯 片 的 系统 验 证 , 图像 传 感 器 可 以 正 确 完 成 信 号 在 各 时钟 间 的 同步 , 以 6 该 并 0帧/ 的 速 率 正 确 s

同步跨时钟域的约束处理

同步跨时钟域的约束处理同步跨时钟域的约束处理是数字设计中一个非常重要的问题,涉及到两个或多个时钟域之间的数据传输。

由于不同的时钟域有各自的时钟频率和相位,因此在从一个时钟域向另一个时钟域传输数据时,可能会出现数据丢失、数据冲突或者不确定状态等问题。

为了解决这些问题,需要进行同步处理。

以下是一些同步跨时钟域的约束处理方法:1. 建立时钟域之间的同步关系:在两个时钟域之间建立同步关系,使得它们之间的数据传输能够有序进行。

常用的同步方法有使用FIFO(先进先出)队列、使用双缓冲区、使用握手协议等。

2. 避免数据冲突:在跨时钟域的数据传输中,如果接收端无法及时接收数据,可能会导致数据冲突。

为了避免这种情况,可以采用以下方法:* 使用具有足够缓冲区的FIFO队列,以容纳接收端暂时无法处理的数据。

* 使用双缓冲区技术,将接收端的数据存储在两个缓冲区中,以避免在一个缓冲区中积累过多的数据。

* 在数据传输前进行握手协议,确保接收端准备好接收数据。

3. 消除不确定状态:在跨时钟域的数据传输中,由于时钟域之间的时钟频率和相位可能不同,可能会导致数据状态不确定。

为了消除这种不确定状态,可以采用以下方法:* 使用分频或倍频技术,使得发送端和接收端的时钟频率相同或相近。

* 使用同步器或去抖动器,将接收端的数据同步到发送端的时钟域中。

4. 考虑时序约束:在数字设计中,时序约束是非常重要的。

在进行跨时钟域的约束处理时,需要考虑时序约束,以确保数据传输的正确性。

例如,在建立FIFO队列时,需要考虑读写时序的约束;在使用同步器或去抖动器时,需要考虑信号传输的时序约束等。

综上所述,同步跨时钟域的约束处理是数字设计中一个非常重要的问题,需要进行综合考虑和处理。

跨时钟域信号如何处理

跨时钟域信号如何处理处理跨时钟域信号是一个复杂的问题,因为不同时钟频率下的信号在时间上是不对齐的。

这意味着在接收到一个跨时钟域信号后,需要确保在正确的时间窗口中捕获和解析该信号,以确保正确的数据传输。

处理跨时钟域信号的一种常见方法是使用握手协议。

在握手协议中,发送方和接收方之间进行多轮的交互,以确保数据的正确传输。

发送方首先发送一个同步信号,表明它开始传输数据。

接收方在接收到同步信号后,等待一段时间,然后发送一个确认信号,表示它已准备好接收数据。

发送方在接收到确认信号后,开始发送数据。

接收方在接收到数据后,发送一个确认信号,表示它已接收到数据。

发送方在接收到确认信号后,停止发送数据。

另一种处理跨时钟域信号的方法是使用FIFO(First-In-First-Out)缓冲区。

发送方将数据写入FIFO缓冲区,而接收方从FIFO缓冲区读取数据。

由于FIFO缓冲区可以在不同的时钟域中工作,因此可以用于在不同的时钟频率下传输数据。

但是,由于FIFO缓冲区的大小有限,可能会发生溢出或丢失数据的情况。

因此,需要合适的策略和算法来处理这些情况,以确保数据的正确传输。

此外,还可以使用专门的芯片或器件来处理跨时钟域信号,如时钟转换器或时钟域交叉。

时钟转换器可以将一个时钟转换为另一个时钟,以便在不同的时钟域中进行通信。

时钟域交叉器可以将两个时钟域之间的信号进行交叉,以实现跨时钟域通信。

总的来说,处理跨时钟域信号是一个复杂且需要精确和可靠的过程。

需要根据具体应用和系统要求选择合适的方法和技术来处理跨时钟域信号,以确保数据的正确传输和处理。

跨时钟域信号同步解决方案

跨时钟域信号同步解决⽅案为了确保拥有多个异步时钟域的系统级芯⽚(SoC)能够可靠运⾏,设计⼈员必须使这些跨越了多个域的时钟和数据信号保持同步。

尽管这并不属于新提出的要求,但随着多时钟域越来越常见和复杂化,使得这⼀要求具备了新的重要意义。

⼤规模集成加上对性能的严格要求以及频率调节都导致在许多不同频率下发⽣了很多时钟域跨越现象-就像⼀场数字化的“完美风暴”。

跨时钟域(CDC)问题会以许多种形式出现,其评估难度相当⾼。

幸好,Synopsys DesignWare库产品提供了许多卓越的CDC解决⽅案,这些⽅案应⽤简便,设计⼈员只需掌握在何时以及何处应⽤它们即可。

本⽂解释了在时钟和数据信号从⼀个时钟域跨越到另⼀个时钟域时所发⽣的许多类型的同步问题。

在任何情况下,本⽂所包含的问题都涉及到相互异步的时钟域。

随着每⼀个问题的提出,本⽂将概述⼀个或多个DesignWare解决⽅案。

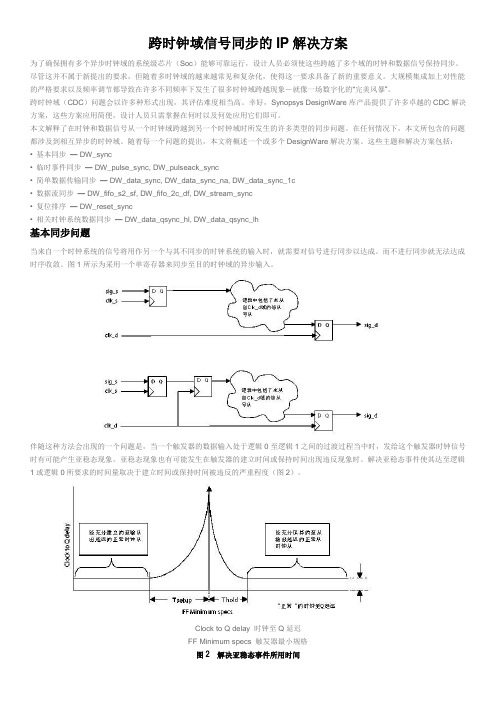

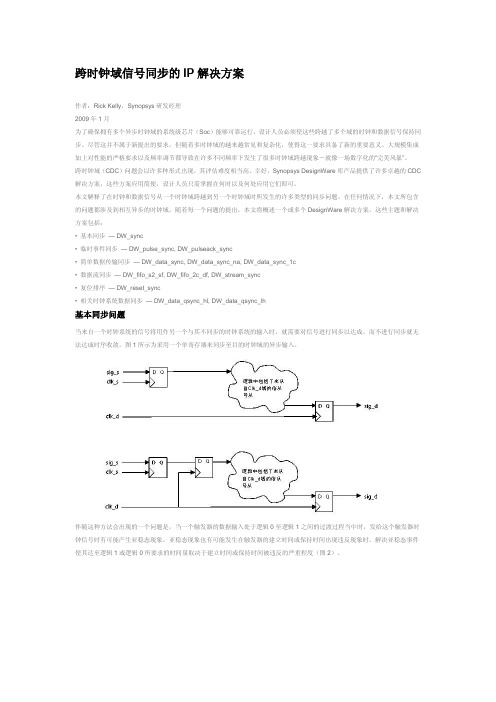

这些主题和解决⽅案包括:●基本同步—DW_sync●临时事件同步—DW_pulse_sync, DW_pulseack_sync●简单数据传输同步—DW_data_sync, DW_data_sync_na,DW_data_sync_1c●数据流同步—DW_fifo_s2_sf, DW_fifo_2c_df,DW_stream_sync●复位排序—DW_reset_sync●相关时钟系统数据同步—DW_data_qsync_hl,DW_data_qsync_lh1基本同步问题当来⾃⼀个时钟系统的信号将⽤作另⼀个与其不同步的时钟系统的输⼊时,就需要对信号进⾏同步以达成。

⽽不进⾏同步就⽆法达成时序收敛。

图1所⽰为采⽤⼀个单寄存器来同步⾄⽬的时钟域的异步输⼊。

伴随这种⽅法会出现的⼀个问题是,当⼀个触发器的数据输⼊处于逻辑0⾄逻辑1之间的过渡过程当中时,发给这个触发器时钟信号时有可能产⽣亚稳态现象。

亚稳态现象也有可能发⽣在触发器的建⽴时间或保持时间出现违反现象时。

同相不同频的跨时钟域路径介绍

同相不同频的跨时钟域路径介绍在数字电路中,时钟是一个非常重要的信号,它用于同步各个元件的操作。

然而,在一些特殊的情况下,我们可能需要在不同频率的时钟域之间进行数据传输。

这就涉及到了同相不同频的跨时钟域路径。

同相不同频的跨时钟域路径指的是在不同频率的时钟域之间传输数据的路径。

在这种情况下,由于不同时钟域之间的时钟信号不同步,可能会导致数据传输错误或者时序问题。

为了解决同相不同频的跨时钟域路径问题,我们可以采取一些特殊的设计和技术。

下面我们将介绍一些常用的方法。

一种常见的方法是采用异步通信方式。

在异步通信中,不同模块之间的数据传输是通过手握握手协议进行的,而不是依赖于同步的时钟信号。

这种方法可以避免时钟同步问题,但是需要额外的控制信号和协议来确保数据的正确传输。

我们可以使用FIFO(First-In-First-Out)缓冲区来实现同相不同频的数据传输。

FIFO缓冲区可以暂时存储来自不同时钟域的数据,然后根据需要进行转换和传输。

通过使用FIFO缓冲区,可以解决时钟域之间的时序问题,确保数据的正确性。

还可以使用握手信号来进行同相不同频的数据传输。

握手信号可以用于通知发送方何时发送数据以及接收方何时准备好接收数据。

通过合理设计握手协议,可以实现不同频率时钟域之间的数据传输。

还有一种常用的方法是使用同步器来实现同相不同频的数据传输。

同步器可以将来自不同时钟域的数据进行同步,然后再进行进一步的处理和传输。

同步器的设计需要考虑时钟频率的差异以及数据传输的时序关系,以确保数据的正确性和稳定性。

除了上述方法,还有一些其他的技术可以用于解决同相不同频的跨时钟域路径问题,例如使用专门的时钟域转换器、时钟域转换器以及时钟域复用器等。

总结起来,同相不同频的跨时钟域路径是一个在数字电路设计中需要注意的问题。

通过采用异步通信、FIFO缓冲区、握手信号、同步器以及其他相关技术,我们可以有效地解决这个问题,确保数据的正确传输和处理。

跨时钟域信号同步方法6种

跨时钟域信号同步方法6种ASIC中心1 引言??? 基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。

但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。

如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。

本文总结出了几种同步策略来解决跨时钟域问题。

2 异步设计中的亚稳态??? 触发器是FPGA设计中最常用的基本器件。

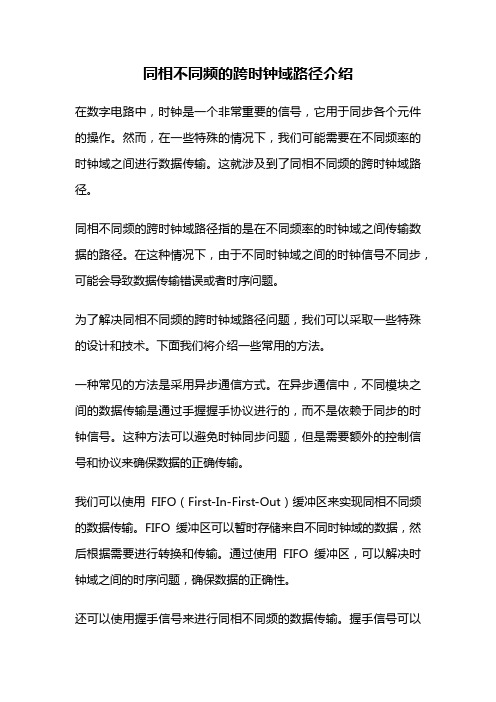

触发器工作过程中存在数据的建立(setup)和保持(hold)时间。

对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间。

而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间。

我们把这段时间成为setup-hold时间(如图1所示)。

在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的。

如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态 (Metastability)?图1??? 一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态。

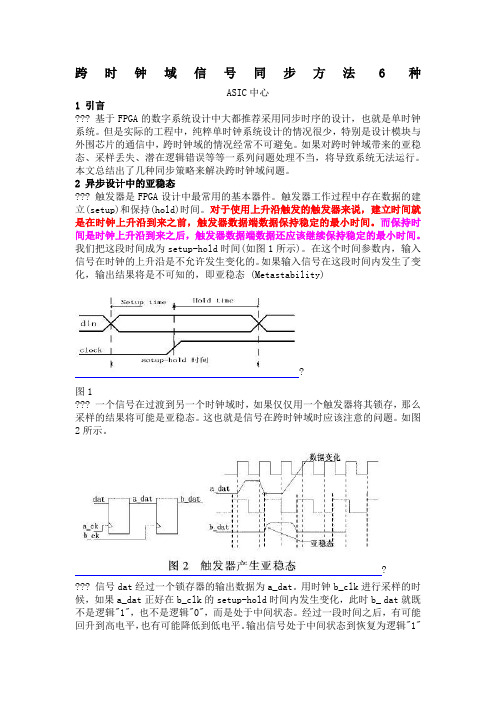

这也就是信号在跨时钟域时应该注意的问题。

如图2所示。

???? 信号dat经过一个锁存器的输出数据为a_dat。

用时钟b_clk进行采样的时候,如果a_dat正好在b_clk的setup-hold时间内发生变化,此时b_ dat就既不是逻辑"1",也不是逻辑"0",而是处于中间状态。

经过一段时间之后,有可能回升到高电平,也有可能降低到低电平。

输出信号处于中间状态到恢复为逻辑"1"或逻辑"0"的这段时间,我们称之为亚稳态时间。

???? 触发器进入亚稳态的时间可以用参数MTBF(Mean Time Between Failures)来描述,MTBF即触发器采样失败的时间间隔,表示为:?其中fclock表示系统时钟频率,fdata代表异步输入信号的频率,tmet代表不会引起故障的最长亚稳态时间,C1和C2分别为与器件特性相关的常数。

跨时钟域信号同步的IP解决方案

跨时钟域信号同步的IP解决方案为了确保拥有多个异步时钟域的系统级芯片(Soc)能够可靠运行,设计人员必须使这些跨越了多个域的时钟和数据信号保持同步。

尽管这并不属于新提出的要求,但随着多时钟域的越来越常见和复杂化,使得这一要求具备了新的重要意义。

大规模集成加上对性能的严格要求以及频率调节都导致在许多不同频率下发生了很多时钟域跨越现象-就像一场数字化的―完美风暴‖。

跨时钟域(CDC)问题会以许多种形式出现,其评估难度相当高。

幸好,Synopsys DesignWare库产品提供了许多卓越的CDC解决方案,这些方案应用简便,设计人员只需掌握在何时以及何处应用它们即可。

本文解释了在时钟和数据信号从一个时钟域跨越到另一个时钟域时所发生的许多类型的同步问题。

在任何情况下,本文所包含的问题都涉及到相互异步的时钟域。

随着每一个问题的提出,本文将概述一个或多个DesignWare解决方案。

这些主题和解决方案包括:• 基本同步— DW_sync• 临时事件同步— DW_pulse_sync, DW_pulseack_sync• 简单数据传输同步— DW_data_sync, DW_data_sync_na, DW_data_sync_1c• 数据流同步— DW_fifo_s2_sf, DW_fifo_2c_df, DW_stream_sync• 复位排序— DW_reset_sync• 相关时钟系统数据同步— DW_data_qsync_hl, DW_data_qsync_lh基本同步问题当来自一个时钟系统的信号将用作另一个与其不同步的时钟系统的输入时,就需要对信号进行同步以达成。

而不进行同步就无法达成时序收敛。

图1所示为采用一个单寄存器来同步至目的时钟域的异步输入。

伴随这种方法会出现的一个问题是,当一个触发器的数据输入处于逻辑0至逻辑1之间的过渡过程当中时,发给这个触发器时钟信号时有可能产生亚稳态现象。

亚稳态现象也有可能发生在触发器的建立时间或保持时间出现违反现象时。

跨时钟域信号同步解决方案

跨时钟域信号同步的IP解决方案作者:Rick Kelly,Synopsys研发经理2009年1月为了确保拥有多个异步时钟域的系统级芯片(Soc)能够可靠运行,设计人员必须使这些跨越了多个域的时钟和数据信号保持同步。

尽管这并不属于新提出的要求,但随着多时钟域的越来越常见和复杂化,使得这一要求具备了新的重要意义。

大规模集成加上对性能的严格要求以及频率调节都导致在许多不同频率下发生了很多时钟域跨越现象-就像一场数字化的―完美风暴‖。

跨时钟域(CDC)问题会以许多种形式出现,其评估难度相当高。

幸好,Synopsys DesignWare库产品提供了许多卓越的CDC 解决方案,这些方案应用简便,设计人员只需掌握在何时以及何处应用它们即可。

本文解释了在时钟和数据信号从一个时钟域跨越到另一个时钟域时所发生的许多类型的同步问题。

在任何情况下,本文所包含的问题都涉及到相互异步的时钟域。

随着每一个问题的提出,本文将概述一个或多个DesignWare解决方案。

这些主题和解决方案包括:• 基本同步— DW_sync• 临时事件同步— DW_pulse_sync, DW_pulseack_sync• 简单数据传输同步— DW_data_sync, DW_data_sync_na, DW_data_sync_1c• 数据流同步— DW_fifo_s2_sf, DW_fifo_2c_df, DW_stream_sync• 复位排序— DW_reset_sync• 相关时钟系统数据同步— DW_data_qsync_hl, DW_data_qsync_lh基本同步问题当来自一个时钟系统的信号将用作另一个与其不同步的时钟系统的输入时,就需要对信号进行同步以达成。

而不进行同步就无法达成时序收敛。

图1所示为采用一个单寄存器来同步至目的时钟域的异步输入。

伴随这种方法会出现的一个问题是,当一个触发器的数据输入处于逻辑0至逻辑1之间的过渡过程当中时,发给这个触发器时钟信号时有可能产生亚稳态现象。

信号跨时钟域的几种方法

在数字电路中,信号跨越不同时钟域时可能会引起时序问题。

以下是处理信号跨时钟域的几种常见方法:1. **双同步FIFO(First-In-First-Out):**- 使用双口RAM实现的FIFO,一个端口用于每个时钟域,允许数据在两个时钟域之间进行安全的同步传输。

- 数据从一个时钟域写入FIFO,在另一个时钟域被读取。

这样可以避免直接跨越时钟域传输信号,减少时序问题。

2. **同步器(Synchronizer):**- 使用两个触发器(寄存器)级联,将信号从一个时钟域同步到另一个时钟域。

第一个触发器使用源时钟域的时钟,第二个触发器使用目标时钟域的时钟。

- 这种方法可以帮助减少时序问题,但需要注意,过多的级联同步器可能会引入潜在的冒险条件和时序不确定性。

3. **双触发器同步器(Dual-Flip-Flop Synchronizer):**- 这种同步器使用两个同步器,但其中一个同步器的时钟源于目标时钟域的时钟。

- 这种方法可以提供更好的稳定性和抖动抑制。

4. **手动握手协议(Handshaking Protocols):**- 在两个时钟域之间建立一种通信协议,通过在数据传输前后进行握手来确保数据的正确性和同步性。

- 这种方式可以通过协议规定好的状态转换确保数据在不同时钟域之间的有效传输。

5. **异步FIFO:**- 异步FIFO允许在不同时钟域之间传输数据,不过需要特殊的异步FIFO设计,通常会引入更复杂的电路结构。

在处理信号跨时钟域时,确保采用合适的方法并考虑到不同时钟域之间的时序关系至关重要。

同时,最好在设计中尽量减少跨时钟域的信号传输,以减少潜在的时序问题。

源同步信号跨时钟域采集的两种方法

源同步信号跨时钟域采集的两种方法

对于数据采集接收的一方而言,所谓源同步信号,即传输待接收的数据和时钟信号均由发送方产生。

FPGA应用中,常常需要产生一些源同步接口信号传输给外设芯片,这对FPGA内部产生时钟或数据的逻辑和时序都有较严格的要求。

而对于一些FPGA采集信号的应用中,常常也有时钟和数据均来自外设芯片的情况,此时对数据和时钟的采集也同样需要关注FPGA内部的逻辑和时序。

当然,无论何种情况,目的只有一个,保证信号稳定可靠的被传送或接收。

对于一个如图1所示的某视频芯片产生的源同步信号,当FPGA对其进行采集同步到另一个时钟域时,特权同学通常的做法有两种,特权同学称之为脉冲边沿检测采集法和异步FIFO采集法。

下面简单的对这两种方法做一些讨论和说明。

图1。

跨时钟域信号处理方法

跨时钟域信号处理方法跨时钟域信号处理方法是在多个时钟域之间进行数据传输和处理的技术。

由于不同的时钟域可能存在时钟频率不同、时钟相位不同或是时钟源不同等问题,因此在进行跨时钟域信号处理时需要采取一些方法来解决时钟不一致性所带来的问题。

一种常见的跨时钟域信号处理方法是采用异步通信协议。

在异步通信中,发送方和接收方的时钟是相互独立的,它们之间并没有直接的时钟连接。

发送方会在数据中插入同步标志符号来指示数据的开始和结束。

接收方会通过检测这些标志符号来进行数据的同步和处理。

异步通信协议的优势是简单、灵活,能够适应不同时钟频率的情况。

然而,由于异步通信协议中不同时钟域之间没有严格的时钟同步,可能存在数据传输不可靠的问题,因此需要采取一些措施来保证数据的可靠性。

另一种跨时钟域信号处理方法是采用同步通信协议。

在同步通信中,发送方和接收方的时钟是相同的或有严格的时钟同步。

发送方会按照时钟周期发送数据,在接收方的时钟周期内进行数据采样和处理。

同步通信协议的优势是能够提供更高的数据传输可靠性,但是对于时钟频率差距较大的情况可能需要额外的时钟域转换电路来进行同步。

除了采用异步通信和同步通信协议外,还可以采用一些时钟域转换的方法来解决跨时钟域信号处理的问题。

一种常见的时钟域转换方法是使用FPGA(现场可编程门阵列)来进行时钟域转换。

FPGA可以实现多个时钟域之间的数据传输和处理,并且可以根据需要进行时钟频率转换和时钟域切换。

此外,还可以采用缓冲器、锁相环等电路来解决时钟不一致性所带来的问题。

总之,跨时钟域信号处理是一个复杂的问题,涉及到时钟频率、时钟相位和时钟源等多个方面的考虑。

通过采用异步通信协议、同步通信协议以及时钟域转换等方法,可以有效地解决跨时钟域信号处理的问题,提高数据传输的可靠性和性能。

跨时钟域处理方法fifo

跨时钟域处理方法fifo跨时钟域处理方法FIFO是用于在不同时钟域之间传输数据的一种常见技术。

在数字系统设计中,由于不同的模块可能使用不同的时钟信号,因此需要一种方法来处理这些不同时钟域之间的数据传输。

FIFO(First-In-First-Out)是一种常见的数据缓冲器,用于在不同时钟域之间进行数据传输和同步。

首先,让我们来看看FIFO是如何工作的。

FIFO包含一个读指针和一个写指针,它可以在不同时钟域之间缓存数据。

当数据被写入FIFO时,它被存储在FIFO的存储单元中,并且可以在另一个时钟域中被读取。

这样,FIFO提供了一种机制,可以在不同时钟域之间进行数据传输,同时保持数据的顺序。

在实际应用中,跨时钟域处理方法FIFO可以通过一些技术来实现。

例如,可以使用双口RAM来实现FIFO,其中一个端口用于写入数据,另一个端口用于读取数据。

此外,可以使用专门设计的同步电路来确保在不同时钟域之间进行数据传输时的正确同步。

另一种常见的方法是使用双缓冲区FIFO,其中一个缓冲区用于接收数据,另一个缓冲区用于发送数据。

这种方法可以确保在不同时钟域之间进行数据传输时的可靠性和稳定性。

除了硬件实现,还可以使用一些设计技巧来处理跨时钟域的数据传输。

例如,可以使用手动握手协议来确保在不同时钟域之间进行数据传输时的正确性,或者可以使用一些同步技术来确保数据在不同时钟域之间的正确传输。

总之,跨时钟域处理方法FIFO是一种常见的用于在不同时钟域之间进行数据传输的技术。

它可以通过硬件实现或者一些设计技巧来确保数据在不同时钟域之间的正确传输和同步。

在数字系统设计中,了解并掌握这种技术对于确保系统的可靠性和稳定性非常重要。

FPGA跨时钟域信号同步设计方法研究

CLK

Q

1 跨 时 钟 域 信 号 常 见 问题

1.1 亚 稳 态 问 题

在 FPGA 系 统 中 ,如 果 数 据 传 输 中 触 发 器 的 建 立 时 间 Tsu和保 持 时 间 Th不 满 足 ,或 者 复 位 过 程 中复 位 信 号

图 1 亚 稳 态 示 意 图

亚 稳 态 产 生 的 原 因是 触 发 器 Tsu和 Th时 间 不 满 足 。 对 于 同 时钟 域 的 信 号 ,可 以采 用 时 序 约 束 来 保 证 满 足 Tsu 和 Th时 间 的要 求 ,采 用 静 态 时 序 分 析 工 具 测 试 是 否 满 足

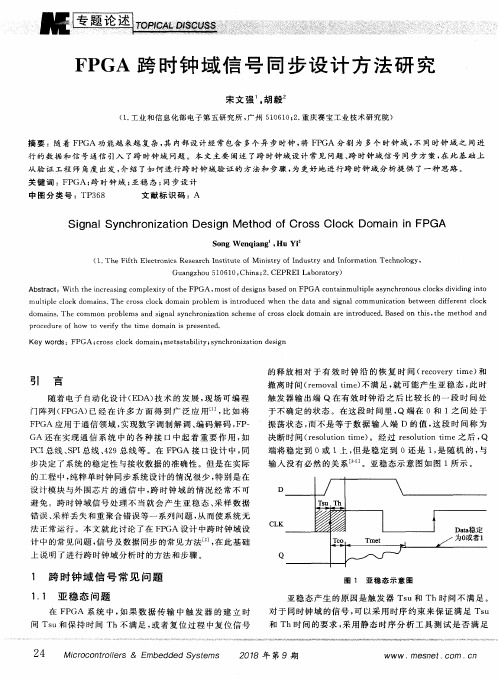

FPGA 跨 时钟 域 信 号 同 步 设 计 方 法 研 究

宋 文 强 ’。胡 毅

(1.工 业 和信 息 化 部 电 子 第 五 研 究 所 ,广 州 510610;2.重 庆 赛 宝 工 业 技 术 研 究 院 )

摘 要 :随 着 FPGA 功能 越 来 越 复 杂 ,其 内部 设 计 经 常 包含 多个 异 步 时 钟 ,将 FPGA 分 割 为 多个 时钟 域 ,不 同时 钟 域 之 间进

G uangzhou 510610,China;2.CEPR EI Laboratory) Abstract:W ith the increasing complexity of the FPGA ,most of designs based on FPGA containmultiple asynchronous clocks dividing into m ultiple clock dom ains.T he cross clock dom ain problem is introduced when the data and signal com m unication betw een different clock dom ains.T he com m on problem s and signal synchronization schem e of cross clock dom ain are introduced.Based on this,the m ethod and procedure of how to verify the tim e dom ain is presented.

从电路的角度出发,提出了一种新的SOC跨时钟域同步电路设计的方法

从电路的角度出发,提出了一种新的SOC跨时钟域同步电路设计的方法随着时间的推移,集成电路行业发展至今,已有类似如Intel这样先进的foundry,提出迈入10 nm制程的规划。

高集成度的推行,也使芯片规模越来越大,功能越来越复杂,设计难度越来越高[1]。

SOC的内部时钟的复杂化,导致跨时钟域的接口越来越多。

针对这些异步信号的处理,国外的先驱们提出了很多建设性意见。

但一般用到器件较多,考虑到成本因素,小规模IC将无法承受,并且如果输入脉冲高电平宽度低于最快时钟周期的话,一般无法适用。

因此要想很好地解决这个问题,要处理好4个方面工作:一是如何简化电路;二是如何适应最小输入脉宽的问题;三是解决好亚稳态问题;四是要提高设计可靠性[2]。

1 处理跨时钟域信号的常用方法实际使用时,往往会出现信号在频率不用的时钟域传递的情况,对于这种情况,一般用两种方法处理:结绳法、伴随有效控制信号法。

当信号从一个时钟域进入另一个时钟域的时候,往往出现亚稳态问题[4]。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。

当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。

信号同步的目的是防止上一级亚稳态对下一级产生不良影响,采用信号同步的方法就要设计信号同步器。

信号同步器主要有3种:电平同步器、边沿检测同步器、脉冲同步器[7-8]。

但是这些常用方法本身存在缺点和不适应性。

在解决实际问题中,需要根据具体情况,来设计具体的方案。

2 跨时钟域同步电路接口方法组成及工作原理整个电路包括两个时钟域以及一个复位电路。

时钟域1包含一个带有异步复位端的同步触发器。

此触发器带有异步复位端R和同步时钟端CK,低电平产生复位,时钟上升沿开始锁存数据输入端D的状态。

输出端有正相Q、反相/Q两种数据输出。

时钟域2由两个同样的触发器组成,跟前面的一样由异步复位端R和同步时钟端CK,数据输入端D组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

跨时钟域信号同步方法6种ASIC中心1 引言基于FPGA的数字系统设计中大都推荐采用同步时序的设计,也就是单时钟系统。

但是实际的工程中,纯粹单时钟系统设计的情况很少,特别是设计模块与外围芯片的通信中,跨时钟域的情况经常不可避免。

如果对跨时钟域带来的亚稳态、采样丢失、潜在逻辑错误等等一系列问题处理不当,将导致系统无法运行。

本文总结出了几种同步策略来解决跨时钟域问题。

2 异步设计中的亚稳态触发器是FPGA设计中最常用的基本器件。

触发器工作过程中存在数据的建立(setup)和保持(hold)时间。

对于使用上升沿触发的触发器来说,建立时间就是在时钟上升沿到来之前,触发器数据端数据保持稳定的最小时间。

而保持时间是时钟上升沿到来之后,触发器数据端数据还应该继续保持稳定的最小时间。

我们把这段时间成为setup-hold时间(如图1所示)。

在这个时间参数内,输入信号在时钟的上升沿是不允许发生变化的。

如果输入信号在这段时间内发生了变化,输出结果将是不可知的,即亚稳态 (Metastability)图1一个信号在过渡到另一个时钟域时,如果仅仅用一个触发器将其锁存,那么采样的结果将可能是亚稳态。

这也就是信号在跨时钟域时应该注意的问题。

如图2所示。

信号dat经过一个锁存器的输出数据为a_dat。

用时钟b_clk进行采样的时候,如果a_dat正好在b_clk的setup-hold时间内发生变化,此时b_ dat就既不是逻辑"1",也不是逻辑"0",而是处于中间状态。

经过一段时间之后,有可能回升到高电平,也有可能降低到低电平。

输出信号处于中间状态到恢复为逻辑"1"或逻辑"0"的这段时间,我们称之为亚稳态时间。

触发器进入亚稳态的时间可以用参数MTBF(Mean Time Between Failures)来描述,MTBF即触发器采样失败的时间间隔,表示为:其中fclock表示系统时钟频率,fdata代表异步输入信号的频率,tmet代表不会引起故障的最长亚稳态时间,C1和C2分别为与器件特性相关的常数。

如果MTBF很大,就认为这个设计在实际工作中是能够正常运行的,不会因为亚稳态导致整个系统的失效。

当触发器处于亚稳态,且处于亚稳态的时间超过了一个时钟周期,这种不确定的状态还会影响到下一级的触发器,最终导致连锁反应,从而使整个系统功能失常。

3 同步策略在异步设计中,完全避免亚稳态是不可能的。

因此,设计的基本思路应该是:首先尽可能减少出现亚稳态的可能性,其次是尽可能减少出现亚稳态并给系统带来危害的可能性。

以下是根据实际工作总结出来的几种同步策略。

3.1电平同步器为了避免进入亚稳态,应当使参数MTBF尽可能大。

通常采用的方法是双锁存器法,即在一个信号进入另一个时钟域之前,将该信号用两个锁存器连续锁存两次(如图3所示)。

理论研究表明这种设计可以将出现亚稳态的几率降低到一个很小的程度,但这种方法同时带来了对输入信号的一级延时,需要在设计时钟的时候加以注意。

对于上面的双锁存器法,如果a_clk的频率比b_clk的频率高,将可能出现因为dat变化太快,而使b_clk无法采样的问题。

即在信号从快时钟域向慢时钟域过渡的时候,如果信号变化太快,慢时钟将可能无法对该信号进行正确的采样,所以在使用双锁存器法的时候,应该使原始信号保持足够长的时间,以便另一个时钟域的锁存器可以正确地对其进行采样。

3.2 边沿同步器如果我们需要用跳变沿而不是电平又该怎样处理呢,在电平同步器之后再加一级触发器,用第二级触发器的输出和第三级触发器的输出来进行操作。

这种结构叫做边沿同步器。

always @ (posedge Clk)begininputs_reg1 <= inputs;inputs_reg2 <= inputs_reg1;inputs_reg3 <= inputs_reg2;if (inputs_reg2 == 1'b1 && inputs_reg3 == 1'b0)begin...end...end以上两种同步器在慢时钟域信号同步入快时钟域时工作的很好,但是反过来的话,可能就工作不正常了。

举一个很简单的例子,如果被同步的信号脉冲只有一个快时钟周期宽,且位于慢时钟的两个相邻跳变沿之间,那么是采不到的。

这时就需要采用脉冲同步器。

这种同步器也是由3个触发器组成,同时需要对发送信号做一些处理。

3.3 脉冲同步器脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路(下图)。

每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲。

图:脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路脉冲同步器的基本功能是从某个时钟域取出一个单时钟宽度脉冲,然后在新的时钟域中建立另一个单时钟宽度的脉冲。

脉冲同步器也有一个限制,即输入脉冲之间的最小间隔必须等于两个同步器时钟周期。

如果输入脉冲相互过近,则新时钟域中的输出脉冲也紧密相邻,结果是输出脉冲宽度比一个时钟周期宽。

当输入脉冲时钟周期大于两个同步器时钟周期时,这个问题更加严重。

这种情况下,如果输入脉冲相邻太近,则同步器就不能检测到每个脉冲。

3.4 结绳法由于双锁存器法在快时钟域向慢时钟域过渡中可能存在采样失效的问题,我们引入了一种安全的跨时钟域的方法:结绳法。

结绳法适合任何时钟域的过渡(clk1,clk2的频率和相位关系可以任意选定),如图4所示。

图4中的_clk1表示该信号属于clk1时钟域,_clk2的信号表示该信号属于clk2时钟域。

在两次src_req_clk1之间被src_vld_clk1结绳(Pluse2Toggle)。

将src_vld_clk1用双锁存器同步以后,该信号转换为dst_req_clk2(Toggle2Pluse)。

同理,用dst_vld_clk2将dat_req_clk2结绳,dst_vld_clk2表明在clk2时钟域中,src_dat_clk1已经可以进行正确的采样了。

最后将dst_vld_clk2转换为dst_ack_clk1(Synchronizer and Toggle2Pluse)。

dst_ack_clk1表明src_dat_clk1已经被clk2正确采样了,此后clk1时钟域就可以安全地传输下一个数据了。

可以看出,结绳法的关键是将信号结绳以后,使其保持足够长的时间,以便另一个时钟可以正确采样。

图5描述了结绳法的具体实现,主要包括3个基本单元:Pluse2Toggle、Synchronizer 和Toggle2Pluse。

Pluse2Toggle模块负责将两个脉冲信号结绳,即将单脉冲信号延长;Synchronizer模块用双锁存器法将得到的信号过渡到另一个时钟域;Toggle2Pluse模块与Pluse2Toggle功能相对,即将延长的脉冲信号还原为单脉冲,这里用到了异或门。

整体的设计思想就是用Pluse2Toggle将信号延长,用Synchronizer过渡,再用Toggle2Pluse还原,以保证另一个时钟域可以正确采样,而接收方用相反的流程送回响应信号。

结绳法可以解决快时钟域向慢时钟域过渡的问题,且适用的范围很广。

但是结绳法实现较复杂,在设计要求较高的场合应该慎用。

3.5 握手协议在许多应用中,跨时钟域传送的不只是简单的信号,数据总线、地址总线和控制总线都会同时跨域传输。

工程师们用一些其它的手段来处理这些情况,如握手协议等。

当几个电路不能预知相互的响应时间时,握手方法能让数字电路间实现有效的通信。

例如,仲裁总线结构可以让一个以上的电路请求使用单个的总线,用仲裁方法来决定哪个电路可以获得总线的访问权,例如 PCI 或 AMBA(高级微控制器总线架构)。

每个电路都发出一个请求信号,由仲裁逻辑决定谁是“赢家”。

获胜的电路会收到一个应答,表示它可以访问总线。

该电路于是中断请求,开始使用总线。

不同时钟域电路使用的握手协议有两种基本类型:全握手(Full-handshake)和部分握手(partial-handshake)。

每种类型的握手都要用同步器,每种都各有自己的优缺点。

对全握手信号,双方电路在声明或中止各自的握手信号前都要等待对方的响应(图4)。

首先,电路 A 声明它的请求信号,然后,电路 B 检测到该请求信号有效后,声明它的响应信号。

当电路 A 检测到响应信号有效后,中止自己的请求信号。

最后,当电路B 检测到请求无效后,它中止自己的响应信号。

除非电路 A 检测到无效的响应信号,否则它不会再声明新的请求信号。

图4,对全握手信号,双方电路在声明或中止各自的握手信号前都要等待对方的响应。

这种类型的握手使用了电平同步器。

设计人员将这种技术用在如下情况:响应电路(电路 B)需要告知请求电路(电路 A)它可以处理请求。

这种握手方法要求请求电路延迟它的下一个请求,直到它检测到响应信号无效。

可以用经验估算法判断这个协议的时序:信号跨越一个时钟域要花两个时钟周期的时间,信号在跨越多个时钟域前被电路寄存。

全部的时间序列是:A 时钟域中最多五个周期加上 B 时钟域最多六个周期。

全握手类型很强健,因为通过检测请求与响应信号,每个电路都清楚地知道对方的状态。

这种方式的不足之处是完成所有交互的整个过程要花费很多时钟周期。

另一种类型是部分握手,它可以缩短这些事件的过程。

使用部分握手信号时,通信双方的电路都不等对方的响应就中止各自的信号,并继续执行握手命令序列。

部分握手类型比全握手类型在健壮性方面稍弱,因为握手信号并不指示各自电路的状态,每一电路都必须保存状态信息(在全握手信号里这个信息被送出去)。

但是,由于无需等待其它电路的响应,完整的事件序列花费时间较少。

当使用部分握手信号方式时,响应的电路必须以正确的时序产生它的信号。

如果响应电路要求先处理完一个请求,然后才能处理下一个请求,则响应信号的时序就很重要。

电路用它的响应信号来指示它的处理任务何时完成。

一种部分握手方法混合了电平与脉冲信号,而其它的方法则只使用脉冲信号。

在第一种部分握手方法中,电路 A 以有效电平声明其请求信号,电路 B 则以一个单时钟宽度脉冲作为响应。

此时,电路 B 并不关心电路 A 何时中止它的请求信号。

但为了使这种方法成立,电路 A 中止请求信号至少要有一个时钟周期长,否则,电路 B 就不能区别前一个请求和新的请求。

在这种握手方式下,电路 B 为请求信号使用一个电平同步器,电路 A 为响应信号使用一个脉冲同步器。