stm32中断源与事件总结20130710

stm32单片机中断原理

STM32单片机中断原理1. 什么是中断?在计算机系统中,中断是一种硬件或软件的事件,它打断了正在执行的程序,使CPU能够立即响应某个特定的事件。

中断机制是一种实现多任务处理的重要技术,它能够提高系统的响应速度和处理效率。

2. 中断的基本原理中断的基本原理是通过打断正在运行的程序,跳转到一个中断服务程序(ISR,Interrupt Service Routine)来处理特定的事件。

当发生中断时,CPU会暂停当前的任务,保存上下文(包括程序计数器、寄存器等),然后跳转到中断服务程序执行。

中断服务程序完成后,CPU会恢复之前的任务继续执行。

3. STM32中断的分类在STM32单片机中,中断可以分为两类:外部中断和内部中断。

•外部中断:是由外部设备(如按键、传感器等)触发的中断。

STM32单片机通常具有多个外部中断引脚,可以通过配置外部中断触发源来响应外部设备的事件。

•内部中断:是由单片机内部的事件触发的中断。

例如,定时器溢出、串口接收完成等。

4. STM32中断的基本原理为了使用中断功能,需要进行以下几个步骤:步骤1:中断向量表的配置中断向量表是一个存储中断服务程序地址的表格,用于指示中断发生时应该跳转到哪个中断服务程序执行。

在STM32单片机中,中断向量表位于Flash的起始地址处。

需要在代码中定义中断向量表,并将每个中断的中断服务程序地址写入相应的中断向量表项。

步骤2:中断优先级的配置每个中断都有一个优先级,用于确定中断的相对重要性。

在STM32单片机中,中断优先级可以通过设置优先级分组和优先级子组来进行配置。

优先级分组决定了中断优先级的位数和分配方式,优先级子组决定了同一分组内部的优先级划分。

步骤3:中断源的配置在STM32单片机中,可以通过配置寄存器来选择特定的中断源。

例如,可以通过配置GPIO的寄存器来选择某个引脚触发的外部中断源。

步骤4:中断服务程序的编写中断服务程序是中断发生时需要执行的代码。

stm32中断和事件

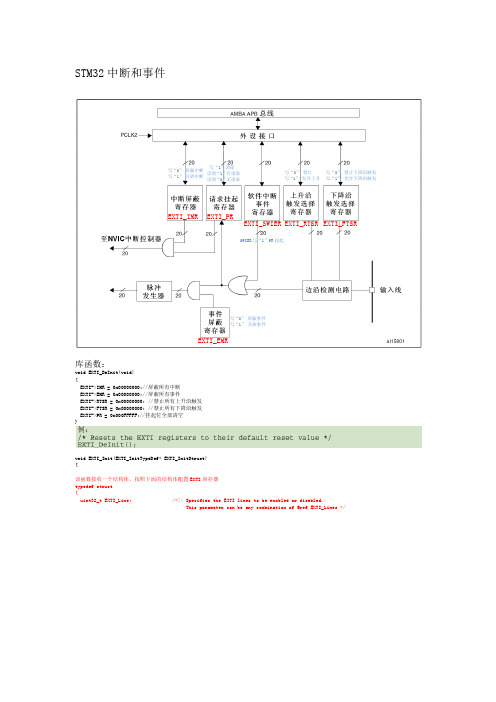

STM32中断和事件库函数:void EXTI_DeInit(void) {EXTI->IMR = 0x00000000;//屏蔽所有中断 EXTI->EMR = 0x00000000;//屏蔽所有事件EXTI->RTSR = 0x00000000; //禁止所有上升沿触发 EXTI->FTSR = 0x00000000; //禁止所有下降沿触发 EXTI->PR = 0x000FFFFF;//挂起位全部清空 }void EXTI_Init(EXTI_InitTypeDef* EXTI_InitStruct) {该函数接收一个结构体,按照下面的结构体配置EXTI 寄存器 typedef struct {uint32_t EXTI_Line; /*!< Specifies the EXTI lines to be enabled or disabled.This parameter can be any combination of @ref EXTI_Lines */EXTI_IMR EXTI_EMREXTI_RTSR EXTI_FTSREXTI_SWIER EXTI_PR写“1”清除读到“1”有请求读到“0”无请求写“0” 屏蔽中断写“1” 开放中断写“0” 屏蔽事件 写“1” 开放事件写“0” 禁止 写“1” 允许上升 写“0” 禁止下降沿触发 写“1” 允许下降沿触发SWIER 写“1”PR 挂起EXTIMode_TypeDef EXTI_Mode; /*!< Specifies the mode for the EXTI lines.This parameter can be a value of @ref EXTIMode_TypeDef */EXTITrigger_TypeDef EXTI_Trigger; /*!< Specifies the trigger signal active edge for the EXTI lines. This parameter can be a value of @ref EXTIMode_TypeDef */FunctionalState EXTI_LineCmd; /*!< Specifies the new state of the selected EXTI lines.This parameter can be set either to ENABLE or DISABLE */}EXTI_InitTypeDef;uint32_t tmp = 0;tmp = (uint32_t)EXTI_BASE;if (EXTI_InitStruct->EXTI_LineCmd != DISABLE){/* Clear EXTI line configuration 屏蔽中断和事件*/EXTI->IMR &= ~EXTI_InitStruct->EXTI_Line;EXTI->EMR &= ~EXTI_InitStruct->EXTI_Line;tmp += EXTI_InitStruct->EXTI_Mode;*(__IO uint32_t *) tmp |= EXTI_InitStruct->EXTI_Line; //开放中断或事件/* Clear Rising Falling edge configuration 禁止上升沿触发和下降沿触发*/EXTI->RTSR &= ~EXTI_InitStruct->EXTI_Line;EXTI->FTSR &= ~EXTI_InitStruct->EXTI_Line;/* Select the trigger for the selected external interrupts */if (EXTI_InitStruct->EXTI_Trigger == EXTI_Trigger_Rising_Falling)//允许上升沿触发和下降沿触发{/* Rising Falling edge */EXTI->RTSR |= EXTI_InitStruct->EXTI_Line;EXTI->FTSR |= EXTI_InitStruct->EXTI_Line;}else//允许上升沿触发或下降沿触发{tmp = (uint32_t)EXTI_BASE;tmp += EXTI_InitStruct->EXTI_Trigger;*(__IO uint32_t *) tmp |= EXTI_InitStruct->EXTI_Line;}}else//需要配置的线路取反再与Mode或运算,及相应线路的中断屏蔽位或事件屏蔽位写“0”,屏蔽事件或中断{tmp += EXTI_InitStruct->EXTI_Mode;/* Disable the selected external lines */*(__IO uint32_t *) tmp &= ~EXTI_InitStruct->EXTI_Line;}}void EXTI_GenerateSWInterrupt(uint32_t EXTI_Line) //软件中断事件寄存器EXTI_SWIER对应线路写“1”,产生一个软件触发{EXTI->SWIER |= EXTI_Line;}FlagStatus EXTI_GetFlagStatus(uint32_t EXTI_Line) //读取挂起寄存器PR对应线路的值{FlagStatus bitstatus = RESET;if ((EXTI->PR & EXTI_Line) != (uint32_t)RESET){bitstatus = SET;}else{bitstatus = RESET;}return bitstatus;}void EXTI_ClearFlag(uint32_t EXTI_Line)//挂起寄存器PR对应线路写“1”清除{EXTI->PR = EXTI_Line;}ITStatus EXTI_GetITStatus(uint32_t EXTI_Line)//如果对应线路开放该线路中断,则读取PR的值{ITStatus bitstatus = RESET;uint32_t enablestatus = 0;enablestatus = EXTI->IMR & EXTI_Line;if (((EXTI->PR & EXTI_Line) != (uint32_t)RESET) && (enablestatus != (uint32_t)RESET)){bitstatus = SET;}else{bitstatus = RESET;}return bitstatus;}void EXTI_ClearITPendingBit(uint32_t EXTI_Line) //挂起寄存器PR对应线路写“1”清除{EXTI->PR = EXTI_Line;}从ITStatus EXTI_GetITStatus(uint32_t EXTI_Line)函数和函数名来看,感觉IT是在中断函数中使用的,Flag是在中断和事件中使用的。

Stm32 学习笔记3--中断

Stm32 学习笔记3—外部中断1、外部中断程序编写方法①时钟(RCC)初始化②I/O端口初始化③EXTI 配置,在这里配置需要选择哪个引脚作为中断引脚④NVIC 配置,这也是比单片机多出来的部分,我们必须把NVIC 中对应的通道使能,并且设置优先级别⑤编写中断处理程序2、EXTI配置void exti_config(){EXTI_InitTypeDef EXTI_InitStructure;GPIO_EXTILineConfig(GPIO_PortSourceGPIOA, GPIO_PinSource0);/*设置PA0作为中断线路*//*EXTI_ClearITPendingBit(EXTI_Line0); */EXTI_InitStructure.EXTI_Line = EXTI_Line0; /*设置外部中断线0*/EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;/*设置线路为中断请求*/EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling; /*下降沿触发*/EXTI_InitStructure.EXTI_LineCmd = ENABLE;/*线路使能*/EXTI_Init(&EXTI_InitStructure);/*初始化中断*/}①EXTI_InitTypeDef 结构体EXTI_InitTypeDef定义于文件“stm32f10x_exti.h”:typedef struct {u32 EXTI_Line;EXTIMode_TypeDef EXTI_Mode;EXTIrigger_TypeDef EXTI_Trigger;FunctionalState EXTI_LineCmd;} EXTI_InitTypeDef;参数说明EXTI_Line16连接PVD输出,EXTI_Line17连接RTC报警事件,EXTI_Line18连接USB唤醒EXTI_LineCmd设为ENABLE或者DISABLE②函数GPIO_EXTILineConfig:选择GPIO管脚用作外部中断线路原型:void GPIO_EXTILineConfig(u8 GPIO_PortSource, u8 GPIO_PinSource)输入:GPIO_PortSource: 选择用作事件输出的GPIO端口原型:void EXTI_Init(EXTI_InitTypeDef* EXTI_InitStruct)输入:参见结构EXTI_InitTypeDef3、NVIC配置void nvic_config(){NVIC_InitTypeDef NVIC_InitStructure;NVIC_PriorityGroupConfig(NVIC_PriorityGroup_0);/*配置主从优先级*/NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQChannel;/*外部中断线0*/NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; /*抢断优先级*/NVIC_InitStructure.NVIC_IRQChannelSubPriority = 2; /*从优先级*/NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;NVIC_Init(&NVIC_InitStructure);/*初始化NVIC*/}①NVIC_InitTypeDef structureNVIC_InitTypeDef定义于文件“stm32f10x_nvic.h”:typedef struct{u8 NVIC_IRQChannel;u8 NVIC_IRQChannelPreemptionPriority;u8 NVIC_IRQChannelSubPriority;FunctionalState NVIC_IRQChannelCmd;} NVIC_InitTypeDef;参数说明:NVIC_IRQChannel设置NVIC_IRQChannel中的先占优先级。

STM32中外部中断与外部事件

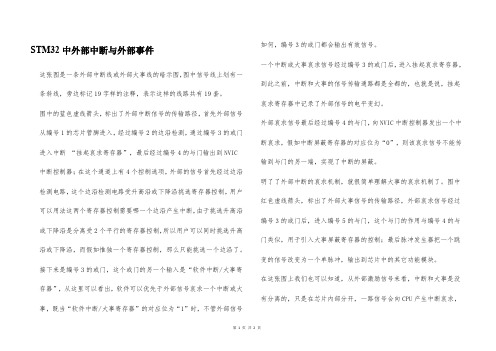

STM32中外部中断与外部事件这张图是一条外部中断线或外部大事线的暗示图,图中信号线上划有一条斜线,旁边标记19字样的注释,表示这样的线路共有19套。

图中的蓝色虚线箭头,标出了外部中断信号的传输路径,首先外部信号从编号1的芯片管脚进入,经过编号2的边沿检测,通过编号3的或门进入中断“挂起哀求寄存器”,最后经过编号4的与门输出到NVIC 中断控制器;在这个通道上有4个控制选项,外部的信号首先经过边沿检测电路,这个边沿检测电路受升高沿或下降沿挑选寄存器控制,用户可以用法这两个寄存器控制需要哪一个边沿产生中断,由于挑选升高沿或下降沿是分离受2个平行的寄存器控制,所以用户可以同时挑选升高沿或下降沿,而假如惟独一个寄存器控制,那么只能挑选一个边沿了。

接下来是编号3的或门,这个或门的另一个输入是“软件中断/大事寄存器”,从这里可以看出,软件可以优先于外部信号哀求一个中断或大事,既当“软件中断/大事寄存器”的对应位为“1”时,不管外部信号如何,编号3的或门都会输出有效信号。

一个中断或大事哀求信号经过编号3的或门后,进入挂起哀求寄存器,到此之前,中断和大事的信号传输通路都是全都的,也就是说,挂起哀求寄存器中记录了外部信号的电平变幻。

外部哀求信号最后经过编号4的与门,向NVIC中断控制器发出一个中断哀求,假如中断屏蔽寄存器的对应位为“0”,则该哀求信号不能传输到与门的另一端,实现了中断的屏蔽。

明了了外部中断的哀求机制,就很简单理解大事的哀求机制了。

图中红色虚线箭头,标出了外部大事信号的传输路径,外部哀求信号经过编号3的或门后,进入编号5的与门,这个与门的作用与编号4的与门类似,用于引入大事屏蔽寄存器的控制;最后脉冲发生器把一个跳变的信号改变为一个单脉冲,输出到芯片中的其它功能模块。

在这张图上我们也可以知道,从外部激励信号来看,中断和大事是没有分离的,只是在芯片内部分开,一路信号会向CPU产生中断哀求,另一路信号会向其它功能模块发送脉冲触发信号,其它功能模块如何相应这个触发信号,则由对应的模块自己打算。

stm32外部中断实验报告-STM32实例外部中断实验

stm32外部中断实验报告_STM32实例外部中断实验上⼀篇⽂章我们介绍了 STM32F10x 的中断,这次我们就来学习下外部中断。

本⽂中要实现的功能与按键实验⼀样,即通过按键控制LED,只不过这⾥采⽤外部中断⽅式进⾏控制。

学习时可以参考《STM32F10x 中⽂参考⼿册》-9 中断和事件章节。

外部中断介绍EXTI 简介STM32F10x 外部中断/事件控制器(EXTI)包含多达 20 个⽤于产⽣事件/中断请求的边沿检测器。

EXTI 的每根输⼊线都可单独进⾏配置,以选择类型(中断或事件)和相应的触发事件(上升沿触发、下降沿触发或边沿触发),还可独⽴地被屏蔽。

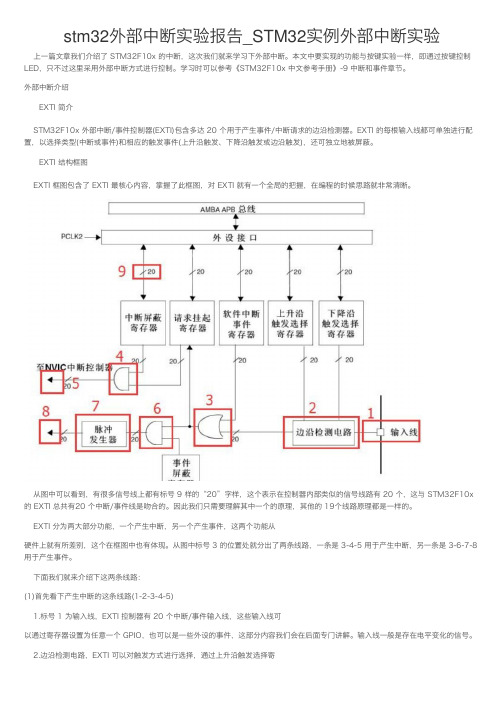

EXTI 结构框图EXTI 框图包含了 EXTI 最核⼼内容,掌握了此框图,对 EXTI 就有⼀个全局的把握,在编程的时候思路就⾮常清晰。

从图中可以看到,有很多信号线上都有标号 9 样的“20”字样,这个表⽰在控制器内部类似的信号线路有 20 个,这与 STM32F10x 的 EXTI 总共有20 个中断/事件线是吻合的。

因此我们只需要理解其中⼀个的原理,其他的 19个线路原理都是⼀样的。

EXTI 分为两⼤部分功能,⼀个产⽣中断,另⼀个产⽣事件,这两个功能从硬件上就有所差别,这个在框图中也有体现。

从图中标号 3 的位置处就分出了两条线路,⼀条是 3-4-5 ⽤于产⽣中断,另⼀条是 3-6-7-8⽤于产⽣事件。

下⾯我们就来介绍下这两条线路:(1)⾸先看下产⽣中断的这条线路(1-2-3-4-5)1.标号 1 为输⼊线,EXTI 控制器有 20 个中断/事件输⼊线,这些输⼊线可以通过寄存器设置为任意⼀个 GPIO,也可以是⼀些外设的事件,这部分内容我们会在后⾯专门讲解。

输⼊线⼀般是存在电平变化的信号。

2.边沿检测电路,EXTI 可以对触发⽅式进⾏选择,通过上升沿触发选择寄存器和下降沿触发选择寄存器对应位的设置来控制信号触发。

边沿检测电路以输⼊线作为信号输⼊端,如果检测到有边沿跳变就输出有效信号 1 给红⾊框 3 电路,否则输出⽆效信号 0。

STM32F4事件和中断使用步骤

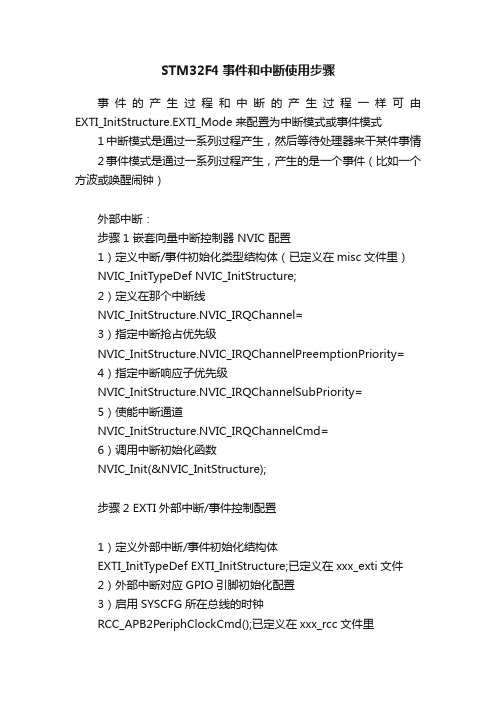

STM32F4事件和中断使用步骤事件的产生过程和中断的产生过程一样可由EXTI_InitStructure.EXTI_Mode来配置为中断模式或事件模式1中断模式是通过一系列过程产生,然后等待处理器来干某件事情2事件模式是通过一系列过程产生,产生的是一个事件(比如一个方波或唤醒闹钟)外部中断:步骤1 嵌套向量中断控制器 NVIC 配置1)定义中断/事件初始化类型结构体(已定义在misc文件里)NVIC_InitTypeDef NVIC_InitStructure;2)定义在那个中断线NVIC_InitStructure.NVIC_IRQChannel=3)指定中断抢占优先级NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=4)指定中断响应子优先级NVIC_InitStructure.NVIC_IRQChannelSubPriority=5)使能中断通道NVIC_InitStructure.NVIC_IRQChannelCmd=6)调用中断初始化函数NVIC_Init(&NVIC_InitStructure);步骤2 EXTI外部中断/事件控制配置1)定义外部中断/事件初始化结构体EXTI_InitTypeDef EXTI_InitStructure;已定义在xxx_exti文件2)外部中断对应GPIO引脚初始化配置3)启用SYSCFG所在总线的时钟RCC_APB2PeriphClockCmd();已定义在xxx_rcc文件里4)调用步骤1配置NVIC5)连接GPIO引脚到外部中断线SYSCFG_EXTILineConfig(EXTI_PortSourceGPIOx,EXTI_PinSou rcex);已定义在xxx_syscfg文件6)初始化外部中断/事件结构体的成员EXTI_InitStructure.EXTI_Line=EXTI_Linex;//中断线xEXTI_InitStructure.EXTI_Mode=; //中断模式或事件模式xxx_exti文件里EXTIMode_TypeDef结构体EXTI_InitStructure.EXTI_Trigger=; //触发方式上升,下降,边沿在EXTITrigger_TypeDef结构体EXTI_InitStructure.EXTI_LineCmd=ENABLE;//中断线的状态启用或禁用(DISABLE)EXTI_Init(&EXTI_InitStructure);//依据上面的参数初始化已在xxx_exti文件里定义。

STM32中断

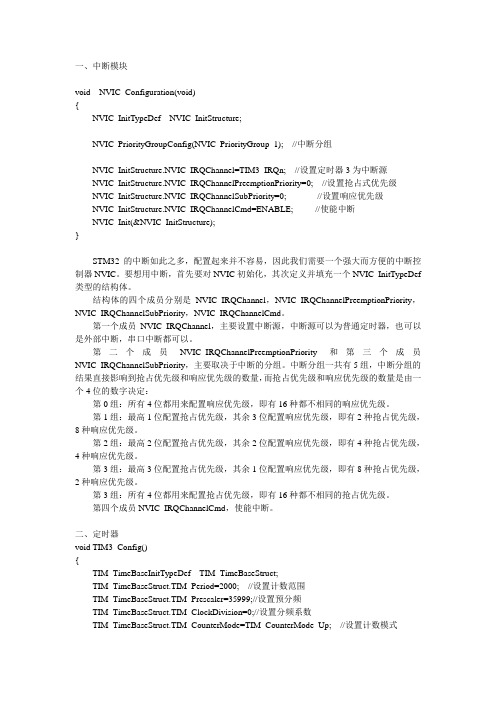

一、中断模块void NVIC_Configuration(void){NVIC_InitTypeDef NVIC_InitStructure;NVIC_PriorityGroupConfig(NVIC_PriorityGroup_1); //中断分组NVIC_InitStructure.NVIC_IRQChannel=TIM3_IRQn; //设置定时器3为中断源NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=0; //设置抢占式优先级NVIC_InitStructure.NVIC_IRQChannelSubPriority=0; //设置响应优先级NVIC_InitStructure.NVIC_IRQChannelCmd=ENABLE; //使能中断NVIC_Init(&NVIC_InitStructure);}STM32的中断如此之多,配置起来并不容易,因此我们需要一个强大而方便的中断控制器NVIC。

要想用中断,首先要对NVIC初始化,其次定义并填充一个NVIC_InitTypeDef 类型的结构体。

结构体的四个成员分别是NVIC_IRQChannel,NVIC_IRQChannelPreemptionPriority,NVIC_IRQChannelSubPriority,NVIC_IRQChannelCmd。

第一个成员NVIC_IRQChannel,主要设置中断源,中断源可以为普通定时器,也可以是外部中断,串口中断都可以。

第二个成员NVIC_IRQChannelPreemptionPriority和第三个成员NVIC_IRQChannelSubPriority,主要取决于中断的分组。

中断分组一共有5组,中断分组的结果直接影响到抢占优先级和响应优先级的数量,而抢占优先级和响应优先级的数量是由一个4位的数字决定:第0组:所有4位都用来配置响应优先级,即有16种都不相同的响应优先级。

STM32中断与事件

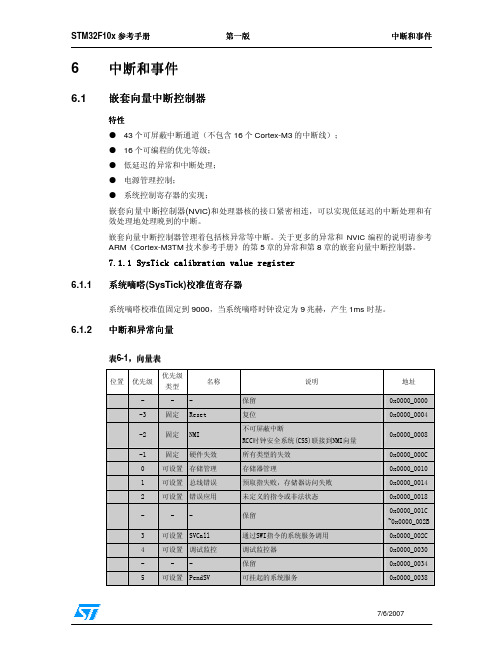

图6-1 外部中断/事件控制器框图

中断和事件

6.2.3 唤醒事件管理

6.2.4

Cortex-M3 可以处理外部时间或内部中断来唤醒内核。通过配置任何外部I/O端口、RTC 闹 钟和USB唤醒事件可以唤醒CPU(内核从WFE退出)。 使用外部 I/O 端口作为唤醒事件,请参见 6.2.4 节的功能说明

位31:19 位18:0

保留,必须始终保持为复位状态(0)。

MRx: 线x上的中断屏蔽 0:线x上的中断请求被屏蔽 1:线x上的中断请求不被屏蔽

事件屏蔽寄存器(EXTI_EMR) 偏移地址:04H 复位值:0000 0000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

7/6/2007

STM32F10x 参考手册

第一版

中断和事件

6.2

6.2.1

36

43 可设置 SPI2

37

44 可设置 USART1

38

45 可设置 USART2

39

46 可设置 USART3

40

47 可设置 EXTI15_10

41

48 可设置 RTCAlarm

42

49 可设置 USB唤醒

SPI2全局中断 USART1全局中断 USART2全局中断 USART3全局中断 EXTI线[15:10]中断 联到EXTI的RTC闹钟中断 联到EXTI的从USB待机唤醒中断

23

30 可设置 EXTI9_5

EXTI线[9:5]中断

24

31 可设置 TIM1_BRK

TIM1断开中断

25

32 可设置 TIM1_UP

TIM1更新中断

stm32F4 的中断解析

stm32F4 的中断2013年4月19日16:20Interrupt program status register 中断状态寄存器32位 31:9保留Bits 8:0 中断号,最多达256个中断stm32F4 用了98个0~98NVIC (Nested vectored interrupt controller) 嵌套向量中断控制器对于中断的优先级配置需要区分是Cortex-M4中断还是stm32中断System handler priority registers (SHPRx)SHPR1~SHPR3 3个32 位寄存器,每8位设置一个中断优先级共12个可配置的系统中断,8位里只用了高4 位,低4位,写无效,读为0。

还有3个中断的优先级为系统默认-3,-2,-1。

Interrupt priority registers (NVIC_IPRx)NVIC_IPR0~NVIC_IPR20 21个寄存器,每8位设置一中断优先级最多可设置84个,但stm32F4只有81个,保留了24位。

AIRCR (Application interrupt and reset control register) 应用中断和复位控制寄存器AIRCR[10:8] 可设置中断优先级分组要写这个寄存器,必须写0x5FA 到VECTKEY (AIRCR[23:16])SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;在misc.c 和core_cm4.h 中均有相应的设置函数(优先级分组,主优先级,从优先级,中断使能/禁止),但函数名不一样,通常调用的是misc.c里的。

但misc 中的函数只能对stm32F4的中断进行配置,不能对Core_M4系统中断配置。

用户对于优先级分组,主优先级,从优先级的配置很难协调。

用户既可以用misc.c 中的函数,也可以用core_cm4.h中的函数,各有优劣。

stm32中断学习总结

stm32中断学习总结经过了两天,终于差不多能看懂32的中断了,由于是⽤的库函数操作的,所以有些内部知识并没有求甚解,只是理解知道是这样的。

但对于要做简单开发的我来说这些已经够了。

我学习喜欢从⼀个例程来看,下⾯的程序是我粘贴但是改编的,⼤部分都做了注释。

其实主要步骤就是:1、将GPIO⼝配置成中断输⼊模式。

void Init_LED(void){GPIO_InitTypeDef GPIO_InitStructure; //定义⼀个GPIO结构体变量RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC | RCC_APB2Periph_GPIOD | RCC_APB2Periph_GPIOE |RCC_APB2Periph_GPIOG, ENABLE);//使能各个端⼝时钟,GPIO_InitStructure.GPIO_Pin = GPIO_Pin_14; //板上LED编号 D2GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(GPIOG, &GPIO_InitStructure);GPIO_InitStructure.GPIO_Pin = GPIO_Pin_13; //板上LED编号 D5GPIO_InitStructure.GPIO_Mode = GPIO_Mode_Out_PP;GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(GPIOD, &GPIO_InitStructure);}2、这个例程是做的按键,就是你要哪个地⽅产⽣中断,然后将其所在的总线配置成中断源,然后照猫画虎,填写中断结构体成员,就是配置外部事件的模式、触发条件、使能外部触发,但是别忘了打开复⽤功能(现在我还不理解)void Init_TI_KEY(void){EXTI_InitTypeDef EXTI_InitStructure; //定义⼀个EXTI结构体变量RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); //使能IO复⽤功能,使⽤中断功能重要/* 引脚选择 */GPIO_EXTILineConfig(GPIO_PortSourceGPIOC, GPIO_PinSource13);//配置端⼝C的13引脚为中断源重要!!板上标号INT2GPIO_EXTILineConfig(GPIO_PortSourceGPIOE, GPIO_PinSource0); //配置端⼝E的0引脚为中断源重要!!板上标号INT1/* 设置外部中断结构体的成员*/EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt; //中断模式为中断模式EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling; //下降沿触发EXTI_InitStructure.EXTI_Line = EXTI_Line0 | EXTI_Line13;EXTI_InitStructure.EXTI_LineCmd = ENABLE; //使能中断线EXTI_Init(&EXTI_InitStructure); //根据参数初始化中断寄存器}3、现在就该配置中断了。

(stm32f103学习总结)—stm32定时器中断

(stm32f103学习总结)—stm32定时器中断⼀、定时器介绍 STM32F1的定时器⾮常多,由2个基本定时器(TIM6、TIM7)、4个通 ⽤定时器(TIM2-TIM5)和2个⾼级定时器(TIM1、TIM8)组成。

基本定 时器的功能最为简单,类似于51单⽚机内定时器。

通⽤定时器是在基本 定时器的基础上扩展⽽来,增加了输⼊捕获与输出⽐较等功能。

⾼级定 时器⼜是在通⽤定时器基础上扩展⽽来,增加了可编程死区互补输出、 重复计数器、带刹车(断路)功能,这些功能主要针对⼯业电机控制⽅⾯1.1 通⽤定时器简介 STM32F1的通⽤定时器包含⼀个 16 位⾃动重载计数器(CNT),该计 数器由可编程预分频器(PSC)驱动。

STM32F1的通⽤定时器可⽤于多种 ⽤途,包括测量输⼊信号的脉冲宽度(输⼊捕获)或者⽣成输出波形(输出 ⽐较和PWM)等。

使⽤定时器预分频器和 RCC 时钟控制器预分频器,脉 冲长度和波形周期可以在⼏个微秒到⼏个毫秒间调整。

STM32F1 的每个 通⽤定时器都是完全独⽴的,没有互相共享的任何资源。

STM32F1的通⽤定时器TIMx (TIM2-TIM5 )具有如下功能:(1)16 位向上、向下、向上/向下⾃动装载计数器(TIMx_CNT)。

(2)16 位可编程(可以实时修改)预分频器(TIMx_PSC),计数器时钟频率的分频系数为 1~65535之间的任意数值。

(3)4个独⽴通道(TIMx_CH1-4),这些通道可以⽤来作为: A.输⼊捕获 B.输出⽐较 C. PWM ⽣成(边缘或中间对齐模式) D.单脉冲模式输出(4)可使⽤外部信号(TIMx_ETR)控制定时器,且可实现多个定时器互连(可以⽤1个定时器控制另外⼀个定时器)的同步电路。

(5)发⽣如下事件时产⽣中断/DMA请求: A.更新:计数器向上溢出/向下溢出,计数器初始化(通过软件或者内部/外部触发) B.触发事件(计数器启动、停⽌、初始化或者由内部/外部触发计数) C.输⼊捕获 D.输出⽐较(6)⽀持针对定位的增量(正交)编码器和霍尔传感器电路(7)触发输⼊作为外部时钟或者按周期的电流管理1.2 通⽤定时器结构框图我们把通⽤定时器结构框图分成 5 个⼦模块,按照顺序依次进⾏简单介绍。

(stm32f103学习总结)—stm32外部中断

(stm32f103学习总结)—stm32外部中断⼀、外部中断介绍1.1 EXTI简介 EXTI简介 STM32F10x外部中断/事件控制器(EXTI)包含多达 20 个⽤于产⽣事 件/中断请求的边沿检测器。

EXTI的每根输⼊线都可单独进⾏配置,以选 择类型(中断或事件)和相应的触发事件(上升沿触发、下降沿触发或 边沿触发),还可独⽴地被屏蔽。

(stm32f103有19个)1.2 EXTI结构框图1.3 外部中断/事件线映射 STM32F10x的EXTI具有20个中断/事件线,如下:(stm32f103有19个以太⽹唤醒事件没有;stm32f107有20个) STM32F10x 的 EXTI 供外部 IO ⼝使⽤的中断线有 16 根,但是我们使⽤的 STM32F103 芯⽚却远远不⽌ 16 个 IO ⼝,那么 STM32F103 芯⽚怎么解决这个问题的呢? 因为 STM32F103 芯⽚每个 GPIO 端⼝均有 16 个管脚,因此把每个端⼝的 16 个 IO 对应那 16 根中断线 EXTI0-EXTI15 。

⽐如:GPIOx.0-GPIOx.15(x=A,B,C,D,E,F,G)分别对应中断线 EXTI0-EXTI15,这样⼀来每个中断线就对应了最多 7 个 IO ⼝,⽐如:GPIOA.0、GPIOB.0、GPIOC.0、GPIOD.0、GPIOE.0、GPIOF.0、GPIOG.0。

但是中断线每次只能连接⼀个在 IO ⼝上,这样就需要通过 AFIO 的外部中断配置寄存器 1 的 EXTIx[3:0]位来决定对应的中断线映射到哪个GPIO 端⼝上,对于中断线映射到 GPIO 端⼝上的配置函数在stm32f10x_gpio.c 和 stm32f10x_gpio.h 中,所以使⽤到外部中断时要把这个⽂件加⼊到⼯程中,在创建库函数模板的时候我们默认已经添加。

EXTI 的 GPIO 映射图如图 18.1.3 所⽰:⼆、外部中断配置步骤 要使⽤外部中断我们就需要先配置它,通常都需经过这⼏步:(1)使能IO ⼝时钟,配置IO ⼝模式为输⼊(2)开启 AFIO 时钟,设置 IO ⼝与中断线的映射关系RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); //开启AFIO 时钟void GPIO_EXTILineConfig(uint8_t GPIO_PortSource, uint8_t GPIO_PinSource); //设置IO ⼝与中断线的映射关系即哪个io ⼝哪⼀个管脚作为中断输⼊线GPIO_EXTILineConfig(GPIO_PortSourceGPIOA, GPIO_PinSource0); //这⾥以配置GPIOA ⼝ GPIOA 的第0管脚作为中断输⼊线(3)配置中断分组(NVIC ),使能中断(4)初始化EXTI ,选择触发⽅式(5)编写EXTI 中断服务函数(中断函数固件库中已经定义必须使⽤下列函数名不能⾃⼰定义)EXTI0_IRQHandlerEXTI1_IRQHandlerEXTI2_IRQHandlerEXTI3_IRQHandlerEXTI4_IRQHandlerEXTI9_5_IRQHandlerEXTI15_10_IRQHandler三、编写外部中断控制程序 要实现外部中断⽅式控制LED ,程序框架如下:(1)初始化对应端⼝的EXTI (第三部分中的1-4⼩步)1 void EXTI_Init(EXTI_InitTypeDef* EXTI_InitStruct);2 typedef struct3 {4 uint32_t EXTI_Line; //中断/事件线5 EXTIMode_TypeDef EXTI_Mode; //EXTI 模式6 EXTITrigger_TypeDef EXTI_Trigger; //EXTI 触发⽅式7 FunctionalState EXTI_LineCmd; //中断线使能或失能8 }EXTI_InitTypeDef ;(2)编写EXTI中断函数(3)编写主函数1/*******************************************************************************2* 函数名 : My_EXTI_Init3* 函数功能 : 外部中断初始化4* 输⼊ : ⽆5* 输出 : ⽆6*******************************************************************************/7void My_EXTI_Init(void)8{9 NVIC_InitTypeDef NVIC_InitStructure;10 EXTI_InitTypeDef EXTI_InitStructure;1112 RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); //AFIO使能13 GPIO_EXTILineConfig(GPIO_PortSourceGPIOA,GPIO_PinSource0);//选择GPIO管脚⽤作外部中断线路14//EXTI0 NVIC 配置15 NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQn;//EXTI0中断通道16 NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority=2;//抢占优先级17 NVIC_InitStructure.NVIC_IRQChannelSubPriority =3; //⼦优先级18 NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; //IRQ通道使能19 NVIC_Init(&NVIC_InitStructure); //根据指定的参数初始化VIC寄存器20//初始化EXTI 配置21 EXTI_InitStructure.EXTI_Line=EXTI_Line0;22 EXTI_InitStructure.EXTI_Mode=EXTI_Mode_Interrupt;23 EXTI_InitStructure.EXTI_Trigger=EXTI_Trigger_Rising;24 EXTI_InitStructure.EXTI_LineCmd=ENABLE;25 EXTI_Init(&EXTI_InitStructure);26}1/*******************************************************************************2* 函数名 : EXTI0_IRQHandler3* 函数功能 : 外部中断0函数4* 输⼊ : ⽆5* 输出 : ⽆6*******************************************************************************/7void EXTI0_IRQHandler(void)8{9 if(EXTI_GetITStatus(EXTI_Line3)==1) //判断EXTI中断标志位状态函数10 {11 //填写中断中需要完成的程序12 }13 EXTI_ClearITPendingBit(EXTI_Line3); //在结束中断服务函数前,清楚中断标志位1415 }。

STM32中断应用总结

STM32中断应⽤总结STM32中断很强⼤,STM32中断可以嵌套,任何外设都可以产⽣中断,其中中断和异常是等价的.中断执⾏流程: 主程序执⾏过程可以产⽣中断去执⾏中断的内容(保护现场),然后在返回继续执⾏中断.中断分类:(可以在参考⼿册查看)系统异常:内核⽔平 10个外部中断:外设⽔平 60个有关具体的系统异常和外部中断可在标准库⽂件 stm32f10x.h 这个头⽂件查询到,在 IRQn_Type 这个结构体⾥⾯包含了 F103 系列全部的异常声明.(部分截图)NVIC简介NVIC: 嵌套向量中断控制器,属于内核外设,管理着包括内核和⽚上所有外设的中断相关的功能。

各个芯⽚⼚商在设计芯⽚的时候会对 Cortex-M3 内核⾥⾯的 NVIC 进⾏裁剪,把不需要的部分去掉,所以说 STM32 的 NVIC 是 Cortex-M3 的 NVIC 的⼀个⼦集。

两个重要的库⽂件:core_cm3.h(内核外设)和misc.h ,NVIC的库函数定义全在misc.h(外设在STM32F10X.h)在配置中断的时候我们⼀般只⽤ ISER、 ICER 和 IP 这三个寄存器, ISER ⽤来使能中断, ICER ⽤来失能中断, IP ⽤来设置中断优先级。

优先级分为主优先级和⼦优先级,当主和⼦优先级相同时,⽐较中断向量表中的位置号.(参考⼿册)NVIC 库函数描述void NVIC_EnableIRQ(IRQn_Type IRQn)使能中断void NVIC_DisableIRQ(IRQn_Type IRQn)失能中断void NVIC_SetPendingIRQ(IRQn_Type IRQn)设置中断悬起位void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority)设置中断优先级void NVIC_ClearPendingIRQ(IRQn_Type IRQn)清除中断悬起位uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn)获取悬起中断编号uint32_t NVIC_GetPriority(IRQn_Type IRQn)获取中断优先级void NVIC_SystemReset(void)系统复位优先级及优先级分组的定义在 NVIC 有⼀个专门的寄存器:中断优先级寄存器 NVIC_IPRx,⽤来配置外部中断的优先级, IPR 宽度为 8bit,原则上每个外部中断可配置的优先级为 0~255,数值越⼩,优先级越⾼。

STM32外部中断总结

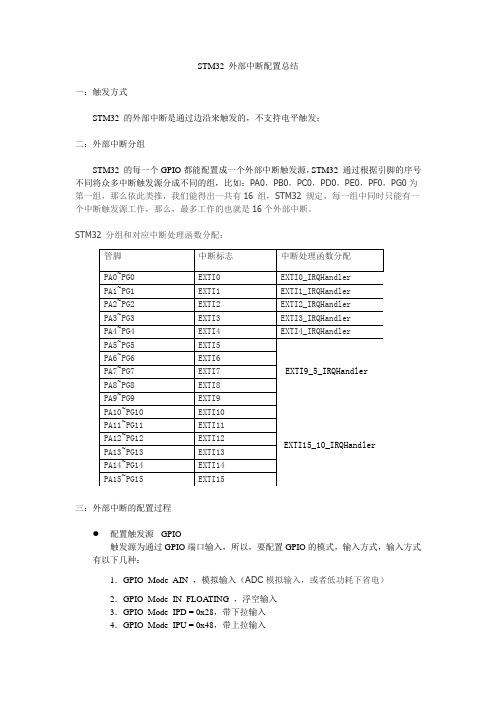

STM32 外部中断配置总结一:触发方式STM32 的外部中断是通过边沿来触发的,不支持电平触发;二:外部中断分组STM32 的每一个GPIO 都能配置成一个外部中断触发源,STM32 通过根据引脚的序号不同将众多中断触发源分成不同的组,比如:PA0,PB0,PC0,PD0,PE0,PF0,PG0为第一组,那么依此类推,我们能得出一共有16 组,STM32 规定,每一组中同时只能有一个中断触发源工作,那么,最多工作的也就是16个外部中断。

STM32 分组和对应中断处理函数分配:三:外部中断的配置过程配置触发源 -GPIO触发源为通过GPIO 端口输入,所以,要配置GPIO 的模式,输入方式,输入方式有以下几种:1.GPIO_Mode_AIN ,模拟输入(ADC 模拟输入,或者低功耗下省电)2.GPIO_Mode_IN_FLOATING ,浮空输入3.GPIO_Mode_IPD = 0x28,带下拉输入4.GPIO_Mode_IPU = 0x48,带上拉输入管脚 中断标志 中断处理函数分配PA0~PG0 EXTI0 EXTI0_IRQHandlerPA1~PG1 EXTI1 EXTI1_IRQHandlerPA2~PG2 EXTI2 EXTI2_IRQHandlerPA3~PG3 EXTI3 EXTI3_IRQHandler PA4~PG4 EXTI4 EXTI4_IRQHandler PA5~PG5 EXTI5 EXTI9_5_IRQHandler PA6~PG6 EXTI6 PA7~PG7 EXTI7 PA8~PG8 EXTI8 PA9~PG9 EXTI9 PA10~PG10 EXTI10 EXTI15_10_IRQHandler PA11~PG11 EXTI11 PA12~PG12 EXTI12 PA13~PG13 EXTI13 PA14~PG14 EXTI14 PA15~PG15 EXTI15●引脚与外部中断关联●外部中断AFIO时钟开启●外部中断配置这个主要是中断线路选择,中断触发方式,中断使能。

STM32 串口中断处理方法

调试发现是串口中断硬件 BUG:

1. USART_ITConfig(USART1, USART_IT_RXNE, ENABLE);使能了接收中断,那么 ORE 中断也同 时被开启了。

2. ORE 中断只能使用 USART_GetFlagStatus(USART1, USART_FLAG_ORE) 读到(没有使 能 USART_IT_ERR 中断时) 解决办法:

4.找资料 STM32F10x 微控制器参考手册(2009 年 12 月第 10 版)P541 发现如下说明:

也就是说只要接收中断打开,即 RXNEIE 设置为 1,那么 ORE 中断也自动打开了。 可是 USART_GetITStatus(USART1, USART_IT_ORE )== RESET!!!! 找到 USART_GetITStatus(USART1, USART_IT_RXNE)函数,发现只有当 USART_IT_ERR 中断使 能时,才能读到 ORE 中断。 在这里要指出这个 BUG:产生 ORE 中断了,但使用 USART_GetITStatus()函数却无法读到这个中断被 SET 起来!

}

2.为什么会一直跑到接收中断? 断点之后发现(USART_GetITStatus(USART1, USART_IT_RXNE)==RESET 的,也就是说没有数据 接收到也进了中断,而且在 USART 配置中我也只打开了接收中断!没有数据送过来应该是不可能进入中断 的!

3.响应了什么中断? 我想通过函数(USART_GetITStatus()把所有中断状态都读出来,但失败了,USART_IT_XXX 所有中断 状态都是 RESET!也就是说没有中断也进入到这个中断服务程序来了!?

STM32中断

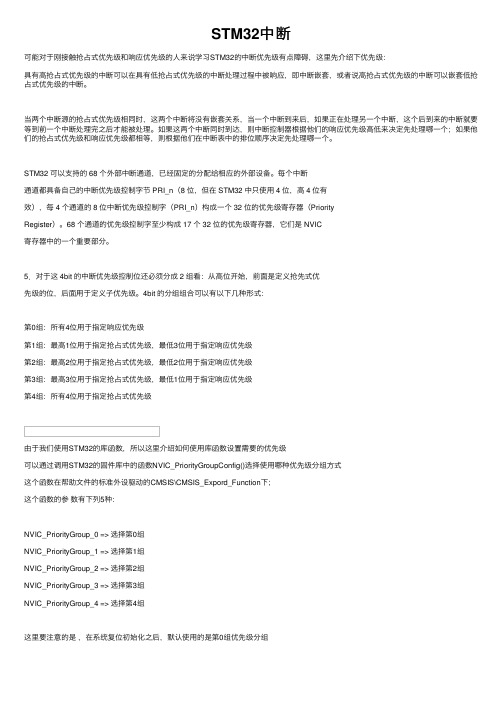

STM32中断可能对于刚接触抢占式优先级和响应优先级的⼈来说学习STM32的中断优先级有点障碍,这⾥先介绍下优先级:具有⾼抢占式优先级的中断可以在具有低抢占式优先级的中断处理过程中被响应,即中断嵌套,或者说⾼抢占式优先级的中断可以嵌套低抢占式优先级的中断。

当两个中断源的抢占式优先级相同时,这两个中断将没有嵌套关系,当⼀个中断到来后,如果正在处理另⼀个中断,这个后到来的中断就要等到前⼀个中断处理完之后才能被处理。

如果这两个中断同时到达,则中断控制器根据他们的响应优先级⾼低来决定先处理哪⼀个;如果他们的抢占式优先级和响应优先级都相等,则根据他们在中断表中的排位顺序决定先处理哪⼀个。

STM32 可以⽀持的 68 个外部中断通道,已经固定的分配给相应的外部设备。

每个中断通道都具备⾃⼰的中断优先级控制字节 PRI_n(8 位,但在 STM32 中只使⽤ 4 位,⾼ 4 位有效),每 4 个通道的 8 位中断优先级控制字(PRI_n)构成⼀个 32 位的优先级寄存器(PriorityRegister)。

68 个通道的优先级控制字⾄少构成 17 个 32 位的优先级寄存器,它们是 NVIC寄存器中的⼀个重要部分。

5.对于这 4bit 的中断优先级控制位还必须分成 2 组看:从⾼位开始,前⾯是定义抢先式优先级的位,后⾯⽤于定义⼦优先级。

4bit 的分组组合可以有以下⼏种形式:第0组:所有4位⽤于指定响应优先级第1组:最⾼1位⽤于指定抢占式优先级,最低3位⽤于指定响应优先级第2组:最⾼2位⽤于指定抢占式优先级,最低2位⽤于指定响应优先级第3组:最⾼3位⽤于指定抢占式优先级,最低1位⽤于指定响应优先级第4组:所有4位⽤于指定抢占式优先级由于我们使⽤STM32的库函数,所以这⾥介绍如何使⽤库函数设置需要的优先级可以通过调⽤STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使⽤哪种优先级分组⽅式这个函数在帮助⽂件的标准外设驱动的CMSIS\CMSIS_Expord_Function下;这个函数的参数有下列5种:NVIC_PriorityGroup_0 => 选择第0组NVIC_PriorityGroup_1 => 选择第1组NVIC_PriorityGroup_2 => 选择第2组NVIC_PriorityGroup_3 => 选择第3组NVIC_PriorityGroup_4 => 选择第4组这⾥要注意的是,在系统复位初始化之后,默认使⽤的是第0组优先级分组接下来就是指定中断源的优先级,下⾯以⼀个简单的例⼦说明如何指定中断源的抢占式优先级和响应优先级:如果应⽤程序储存在ROM中,并且不需要改变异常服务程序,则我们可以把整个向量表编码到ROM的起始区域(从0 地址开始的那段)。

STM32GPIO外部中断总结

GPIO引脚中断标志位中断处理函数PA0~PG0EXTI0EXTI0_IRQHandlerPA1~PG1EXTI1EXTI1_IRQHandlerPA2~PG2EXTI2EXTI2_IRQHandlerPA3~PG3EXTI3EXTI3_IRQHandlerPA4~PG4EXTI4EXTI4_IRQHandlerPA5~PG5EXTI5EXTI9_5_IRQHandler PA6~PG6EXTI6PA7~PG7EXTI7PA8~PG8EXTI8PA9~PG9EXTI9PA10~PG10EXTI10EXTI15_10_IRQHandler PA11~PG11EXTI11PA12~PG12EXTI12PA13~PG13EXTI13PA14~PG14EXTI14PA15~PG15EXTI15STM32GPIO外部中断总结⼀、STM32中断分组: STM32 的每⼀个GPIO都能配置成⼀个外部中断触发源,这点也是 STM32 的强⼤之处。

STM32 通过根据引脚的序号不同将众多中断触发源分成不同的组,⽐如:PA0,PB0,PC0,PD0,PE0,PF0,PG0为第⼀组,那么依此类推,我们能得出⼀共有16 组,STM32 规定,每⼀组中同时只能有⼀个中断触发源⼯作,那么,最多⼯作的也就是16个外部中断。

STM32F103 的中断控制器⽀持 19 个外部中断/事件请求。

每个中断设有状态位,每个中断/事件都有独⽴的触发和屏蔽设置。

STM32F103 的19 个外部中断为:线 0~15:对应外部 IO ⼝的输⼊中断。

线 16:连接到 PVD 输出。

线 17:连接到 RTC 闹钟事件。

线 18:连接到 USB 唤醒事件。

⼆:外部中断的配置过程: 1、配置触发源GPIO⼝: 因为GPIO⼝作为触发源使⽤,所以将GPIO⼝配置成输⼊模式,触发模式有以下⼏种: a.GPIO_Mode_AIN ,模拟输⼊(ADC模拟输⼊,或者低功耗下省电) b.GPIO_Mode_IN_FLOATING ,浮空输⼊ c.GPIO_Mode_IPD ,带下拉输⼊ d.GPIO_Mode_IPU ,带上拉输⼊ GPIO_InitTypeDef GPIO_InitStructure;//定义结构体 RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOE,ENABLE);//使能时钟 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;//选择IO⼝ PE2 GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU;//设置成上拉输⼊ GPIO_Init(GPIOE, &GPIO_InitStructure);//使⽤结构体信息进⾏初始化IO⼝ 2、使能AFIO复⽤时钟功能: RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO,ENABLE); 3、将GPIO⼝与中断线映射起来: GPIO_EXTILineConfig(GPIO_PortSourceGPIOE,GPIO_PinSource2); 4、中断线上进⾏中断初始化: EXTI_InitTypeDef EXTI_InitStructure;//定义初始化结构体 EXTI_InitStructure.EXTI_Line=EXTI_Line2; //中断线的标号取值范围为EXTI_Line0~EXTI_Line15 EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;//中断模式,可选值为中断 EXTI_Mode_Interrupt 和事件 EXTI_Mode_Event。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第0组:所有4位用于指定响应优先级

第1组:最高1位用于指定抢占式优先级,最低3位用于指定响应优先级

第2组:最高2位用于指定抢占式优先级,最低2位用于指定响应优先级

通过让优先级以MSB对齐,可以简化程序的跨器件移植。比如,如果一个程序早先在支持4位优先级的器件上运行,在移植到只支持3位优先级的器件后,其功能不受影响。但若是对齐到LSB,则会使MSB丢失,导致数值大于7的低优先级一下子升高了,甚至会反转小于等于7的高优先级。如,8号优先级因为损失了MSB,现在反而变成0号了!

优先级分组。为了更好的对大量的中断进行优先级管理和控制,NVIC支持优先级分组。通过设定应用中断和复位中断控制寄存器的PRIGROUP字段,可以将PRI_N字段分成2个部分:抢占优先级和次要优先级,如表2所列。抢占优先级可以认为是优先级分组,当多个挂起的异常具有相同的抢占优先级时,次要优先级就起作用。优先级分组和次要优先级共同作用确定了异常的优先级,当两个挂起的异常具有完全相同的优先级时,硬件位置编号低的异常优先级被激活。

NVIC的访问地址是0xE000 _E000。

每个外部中断都有一个对应的优先级寄存器,每个寄存器占用8位,但是允许最少只使用最高3位。4个相临的优先级寄存器拼成一个32位寄存器。如前所述,根据优先级组设置,优先级可以被分为高低两个位段,分别是抢占优先级和亚优先级。优先级寄存器都可以按字节访问,当然也可以按半字/字来访问。有意义的优先级寄存器数目由芯片厂商实现的中断数目决定,优先级配置寄存器的详细信息在附录D中给出

NVIC中有一个寄存器是“应用程序中断及复位控制寄存器”(内容见表7.5),它里面有一个位段名为“优先级组”。该位段的值对每一个优先级可配置的异常都有影响——把其优先级分为个位段:MSB所在的位段(左边的)对应抢占优先级,而LSB所在的位段(右边的)对应亚优先级。

抢占优先级决定了抢占行为:当系统正在响应某异常L时,如果来了抢占优先级更高的异常H,则H可以抢占L。亚优先级则处理“内务”:当抢占优先级相同的异常有不止一个悬起时,就优先响应亚优先级最高的异常。

原则上,CM3支持3个固定的高优先级和多达256级的可编程优先级,并且支持128级抢占(128的来历请见下文分解——译注)。但是,绝大多数CM3芯片都会精简设计。以致实际上支持的优先级数会更少,如8级,16级,32级等。它们在设计时会裁掉表达优先级的几个低端有效位,以达到减少优先级数的目的(可见,不管使用多少位,优先级号是以MSB对齐的——译注)。

c/执行TIME2的中断服务程序

所有TIME2的中断事件,都是在一个TIME2中断服务程序中完成的,所以进入中断程序后,中断程序需要首先判断是哪个TIME2的具体事件的中断,然后转移到相应的服务代码段去。

�支持多达19个中断/事件请求;

�检测脉冲宽度低于APB2时钟宽度的外部信号。

要产生中断,必须先配置好并使能中断线。根据需要的边沿检测设置2个触发寄存器,同时在中断屏蔽寄存器的相应位写’1’允许中断请求。当外部中断线上发生了期待的边沿时,将产生一个中断请求,对应的挂起位也随之被置’1’。在挂起寄存器的对应位写’1’,将清除该中断请求。

这种优先级分组规定:亚优先级至少是1个位。因此抢占优先级最多是7个位,造成了最多只有128级抢占的现象。

但是CM3允许从比特7处分组,此时所有的位都表达亚优先级,没有任何位表达抢占优先级,因而所有优先级可编程的异常之间就不会发生抢占——相当于在它们之中除能了

CM3的中断嵌套机制。当然还有凌架于法律之上的三位老大:复位,NMI和硬fault。它们无论何时出现,都立即无条件抢占所有优先级可编程的“平民异常”。

保证同时报告错误。下表列出了异常的类型、位置和优先级。位置是指中断向量在中断向量

表中的位置,是相对于中断限量表开始处字的偏移。优先级的值越小,优先级越高。

二、中断优先级

在CM3中,优先级对于异常来说很关键的,它会影响一个异常是否能被响应,以及何时可以响应。优先级的数值越小,则优先级越高。CM3支持中断嵌套,使得高优先级异常会抢占(preempt)低优先级异常。有3个系统异常:复位,NMI以及硬fault,它们有固定的优先级,并且它们的优先级号是负数,从而高于所有其它异常。所有其它异常的优先级则都是可编程的(但不能编程为负数)。

●EXTI线16连接到PVD输出

●EXTI线17连接到RTC闹钟事件

●EXTI线18连接到USB唤醒事件

●EXTI线19连接到以太网唤醒事件(只适用于互联型产品)

以

a/初始化过程

首先要设置寄存器AIRC中PRIGROUP的值,规定系统中的抢先优先级和子优先级的个数(在4个bits中占用的位数);

设置TIME2本身的寄存器,允许相应的中断,如允许UIE(TIME2_DIER的第[0]位)

此时内核硬件将TIME2中断通道的Pending标志置位(相当与中断通道标志置位),表示TIME2有中断申请。

如果当前有中断在处理,TIME2的中断级别不够高,那么就保持Pending标志,当然用户可以在软件中通过写ICPR寄存器中相应的位把本次中断清除掉。

当内核有空,开始响应TIME2的中断,进入TIME2的中断服务。此时硬件将IABR寄存器中相应的标志位置位,表示TIME2中断正在被处理。同时硬件清除TIME2的Pending标志位。

举例来说,如果只使用了3个位来表达优先级,则优先级配置寄存器的结构会如图7.1所示:

在图中,[4:0]没有被实现,所以读它们总是返回零,写它们则忽略写入的值。因此,对于3个位的情况,我们能够使用的8个优先级为:0x00(最高),0x20,0x40,0x60,0x80,0xA0,0xC0以及0xE0。

第3组:最高3位用于指定抢占式优先级,最低1位用于指定响应优先级

第4组:所有4位用于指定抢占式优先级

可以通过调用STM32的固件库中的函数NVIC_PriorityGroupConfig()选择使用哪种优先级分组方式,这个函数的参数有下列5种:

NVIC_PriorityGroup_0 =>选择第0组

NVIC_PriorityGroup_1 =>选择第1组

NVIC_PriorityGroup_2 =>选择第2组

NVIC_PriorityGroup_3 =>选择第3组

NVIC_PriorityGroup_4 =>选择第4组

二、

向量中断控制器,简称NVIC,是Cort ex‐M3不可分离的一部分,它与CM3内核的逻辑紧密耦合,有一部分甚至水乳交融在一起。NVIC与CM3内核同声相应,同气相求,相辅相成,里应外合,共同完成对中断的响应。N VIC的寄存器以存储器映射的方式来访问,除了包含控制寄存器和中断处理的控制逻辑之外,NVIC还包含了MPU的控制寄存器、SysT ick定时器以及调试控制。

通过软件设置的优先级权限高于硬件优先级。例如,如果设置IRQ[0]的优先级为1,IRQ[31]的优先级为0,则IRQ[31]的优先级比IRQ[0]的高。但通过软件设置的优先级对复位、不可屏蔽中断和硬件故障没有影响。

当多个中断具有相同的优先级时,拥有最小中断号的挂起中断优先执行。例如,IRQ[0]

和IRQ[1]的优先级都为1,则IRQ[0]优先执行。

c/当2(n)个相同抢先优先级和相同子优先级的中断出现,STM32首先响应中断通道所对应的中断向量地址低的那个中断(见ROM0008,表52)。具体一点:

0号抢先优先级的中断,可以打断任何中断抢先优先级为非0号的中断;1号抢先优先级的中断,可以打断任何中断抢先优先级为2、3、4号的中断;……;构成中断嵌套。如果两个中断的抢先优先级相同,谁先出现,就先响应谁,不构成嵌套。如果一起出现(或挂在那里等待),就看它们2个谁的子优先级高了,如果子优先级也相同,就看它们的中断向量位置了。

如果需要产生事件,必须先配置好并使能事件线。根据需要的边沿检测通过设置2个触发寄存器,同时在事件屏蔽寄存器的相应位写’1’允许事件请求。当事件线上发生了需要的边沿时,将产生一个事件请求脉冲,对应的挂起位不被置’1’。

通过在软件中断/事件寄存器写’1’,也可以通过软件产生中断/事件请求。

硬件中断选择

通过下面的过程来配置20个线路做为中断源:

2.

外部中断/事件控制器(EXTI)由19个产生事件/中断要求的边沿检测器组成。每个输入线可以独立地配合输入类型和对应的触发事件。每个输入线都可以被独立地屏蔽,由挂起寄存器保持着状态线的中断要求。

EXTI控制器的结构图如图5-1所示,其主要特性如下:

�每个中断/事件都有独立的触发和屏蔽;

�每个中断线都有专用的状态线;

在计算抢占优先级和亚优先级的有效位数时,必须先求出下列值:

◆芯片实际使用了多少位来表达优先级

◆优先级组是如何划分的。

二、异常的优先级

在处理器处理异常时,优先级决定了处理器何时以及如何进行异常处理。可以给中断设置软件优先级以及对其进行分组。

优先级NVIC支持通过软件设置的优先级。通过写中断优先级寄存器的PRI_N字段可以设置优先级,范围为0~255。硬件优先级随着中断号的增加而减小,优先级0为最高优先级,255为最低优先级。

异常

Cortex-M3处理器和NVIC对所有优先级进行划分和处理。所有的异常处理均在Handle模式下进行。当出现异常时,处理器的状态被自动保存到栈中;在中断服务子程序结束之后,又会自动从栈中恢复处理器的状态。获取中断向量和状态保存是同时进行的,这提高了进入中断处理的效率。Cortex-M3处理器支持尾链技术,即当发生背靠背中断时,无需保存和恢复状态,而是继续执行。Cortex-M3处理器的一下特性,提高了处理异常的效率并降低了时间的延迟。

◆为Handle和Thread模式分别提供独立的栈和访问权限等级;