MC9S12XS128核心板原理图

第8章MC9S12XS128模数转换模块及其应用实例59页PPT

8.2 ATD模块结构组成和特点

MC9S12XS128内置的ATD 模块如图8.1所示。

《MC9S12XS单片机原理及嵌入式系统开发》 单片机原理及嵌入式系统开发》

8.2 ATD模块结构组成和特点

ATD模块具有以下基本特征: 8位/10位/12位可选转换精度; 停止模式下转换使用内部时钟; 转换完成后为低功耗状态; 自动和可编程数值比较,可设定大于或者小于等于设定值时中断申请; 可编程采样时间; 左对齐/右对齐转换数值; 外部触发功能; 转换完成中断申请; 16路模拟输入通道多路开关; 可实现VRH、VRL和(VRH+VRL)/2特殊转换; 转换序列长度为1~16; 连续转换模式; 多通道扫描功能; 外部触发功能可配置为AD通道或4个外部附加触发输入端,外部触发源可选

《MC9S12XS单片机原理及嵌入式系统开发》 单片机原理及嵌入式系统开发》

8.3 ATD模块寄存器及设置

8.3.4 ATD控制寄存器3(ATDCTL3)

S8C、S4C、S2C、S1C:转换序列长度定义位。这4位控制每个序列转换的长度。A/D 转换序列长度定义详见表8-7。复位后,S4C默认为1,所以默认的A/D转换序列的长度为 4。

8.3 ATD模块寄存器及设置

8.3.3 ATD控制寄存器2(ATDCTL2)

ETRIGE:外部触发模式使能位。该位允许表8-3中描述的AD通道或者ETRIG3~0输入 端作为外部触发源。如果外部触发源是AD某通道,则使能该通道的数字输入缓冲功能。外部 触发允许与外部事件实现同步转换。停止模式下的AD转换,外部触发不工作。

《MC9S12XS单片机原理及嵌入式系统开发》 单片机原理及嵌入式系统开发》

8.3 ATD模块寄存器及设置

MC9S12XS128 PIT模块

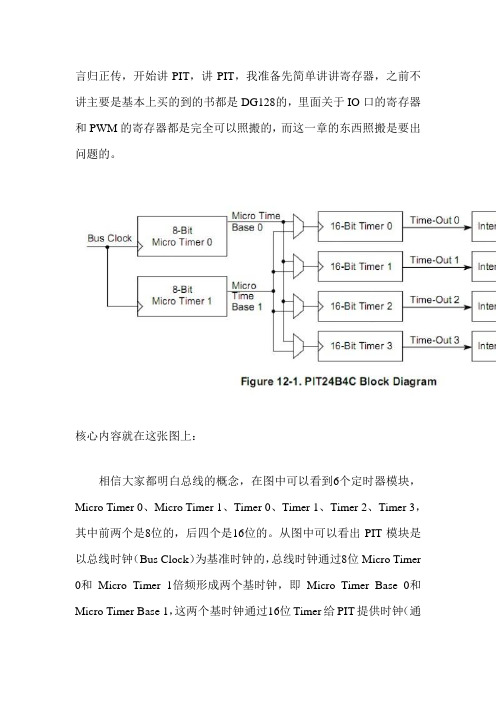

言归正传,开始讲PIT,讲PIT,我准备先简单讲讲寄存器,之前不讲主要是基本上买的到的书都是DG128的,里面关于IO口的寄存器和PWM的寄存器都是完全可以照搬的,而这一章的东西照搬是要出问题的。

核心内容就在这张图上:相信大家都明白总线的概念,在图中可以看到6个定时器模块,Micro Timer 0、Micro Timer 1、Timer 0、Timer 1、Timer 2、Timer 3,其中前两个是8位的,后四个是16位的。

从图中可以看出PIT模块是以总线时钟(Bus Clock)为基准时钟的,总线时钟通过8位Micro Timer 0和Micro Timer 1倍频形成两个基时钟,即Micro Timer Base 0和Micro Timer Base 1,这两个基时钟通过16位Timer给PIT提供时钟(通过寄存器PITMUX设置)。

原理讲完了,其实相对于PIT模块是一个24位的定时器(51单片机最多也就16位),这个计数范围还是蛮大的。

下面是一些寄存器的解释,解释完还是看代码吧。

S12PIT24B4CV1是一个模数递减计数器。

首先给计数寄存器设定一个初值,每经过一个总线周期,计数器进行一次减一操作,当计数器自减溢出时,触发中断。

因为总线周期是已知的,即可以通过计数器自减实现定时。

在XS128PIT模块中,需要用到得是如下几个寄存器。

1)、PIT Contorl and force Lad Micro Timer Register(PITCFLMT)该寄存器用于PIT模块的使能设置和工作方式设置。

通常设置该寄存器中的PITE为即可,即PITCFLMT_PITE=1,使PIT使能。

2)、PIT Channel Enable Register(PITCE)该寄存器用于对PIT模块中的4个通道使能进行设置。

如果使用某个通道时,对对应位进行置一即可,即PITCE_PCEx=1,其中x代表通道序号,为0~3。

飞思卡尔MC9S12XS128(定时器)ECT寄存器详解

1、定时器IC/OC功能选择寄存器TIOSIOS[7..0]IC/OC功能选择通道0 相应通道选择为输入捕捉(IC)1 相应通道选择为输出比较(OC)2、定时器比较强制寄存器 CFORCFOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。

【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。

3、输出比较7屏蔽寄存器 OC7MOC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于OC7的管理之下。

OC7M中的各位与PORTT口寄存器的各位一一对应。

当通过TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状态。

【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7DOC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。

当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。

OC7D中的各位与PORTT口寄存器的各位一一对应。

当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输出到PORTT的对应引脚。

【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。

比如:OC7M0=1,则通道0处在OC7的管理下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。

16蓝宙最小系统板MC9S12XS128-112 使用说明书

Freescale系列单片机MC9S12XS128-112最小系统板产品使用说明书版本:Version 1.0所有者:蓝宙电子研发部日期:2011.07.10目录最小系统板简介---------------------------------------- 最小系统板特性---------------------------------------- 最小系统板结构说明------------------------------------ 安装CodeWorror调试文件-------------------------------- 安装HC(S)12(X)内核CodeWorror调试文件----------------- 使用CodeWorror IDE烧写和调试程序的方法----------------简介:本店MC9S12XS128最小系统板是由多年专业项目开发经验的工程师根据当前实际单片机应用产品情况以及学生学习的角度定制,经过历多版和反复测试验证。

全部采用原装芯片和元器件,经典蓝板设计,PCB布局走线规范,采用高品质材料,稳定可靠,并采用回流焊工艺焊接,焊接质量高,系统板质量可靠。

这里描述的 9S12XS128 单片机基本系统模块是针对全国大学生飞思卡尔杯智能车模竞赛设计的,采用大赛组委会推荐的112引脚器件。

本开发板适用于嵌入式工程师与学生对M9S12系列单片机开发、学习,带CAN总线开发的工程项目。

MC9S12XS128微控制器产品满足了用户对设计灵活性和平台兼容性的需求,并在一系列汽车电子平台上实了可升级性、硬件和软件可重用性、以及兼容性。

S12XS 系列可以经济而又兼容地扩展至带 XGate 协处理器的S12XE 系列单片机,从为用户削减了成本,并缩小了封装尺寸。

S12XS系列帮助设计者迅速抓住市场机遇,同还能降低移植成本。

MC9S12XS128主要特性:S12XS系列单片机是在S12XE系列基础上去掉XGate协处理器的单片机。

MC9S12XS(DG)单片机--110108

CodeWarrior开发平台上可用汇编,也可用C语言编程。

CodeWarrior的使用

六、9S12XS/DG 的开发样例

1. 9S12XS/DG 的工程组织与通用I/O口的控制 2. PWM 输出编程 3.模拟信号采集 4定时器的功能与使用 5. 9S12XS/DG 的存储器控制 6. SCI/SPI串行数据通信 8.

;定义五个字的存储区,首址为X2

若要对X2的第三字赋值,可用如下语句:

STX X2+2

②数字常数/字符串常数定义伪指令:

格式: [<label>:] DC [.<size>] <expression> [ ,<expression>]…

功能:在Flash区定义一个size×n 个字节的存储区。

例: C1: DC .B $25

Freescale

车模用单片机原理与使用

讲座

车模电路组成

显示电路

路径检测 速度检测 电源电路

MCU

数据输入 电路

舵机控制

电机 速度控制

内容

一、飞思卡尔车模用单片机性能 二、9S12XS/DG 的硬件资源 三、9S12XS/DG 的硬件系统 四、9S12XS/DG的指令系统 五、 9S12XS/DG 的开发平台 六、9S12XS/DG 的开发样例

;定义一字节常数,即C1= $25

C2: DC .W $2538 ;定义一字常数,即C2= $2538

③常数赋值伪指令: 格式: <label>: EQU <expression> <label>: SET <expression> 功能:定义<label> 等于的值<expression>的值。 注意: <expression> 要有确定的值。 例: PI: EQU 3

mc9s12xs128程序教程

711 次

该寄存器是 0~7 通道 PWM 输出起始极性控制位,用来设置 PWM 输出的起始 电平。

用法:PWMPOL_PPOL0=1--- 通道 0 在周期开始时输出为高电平,当计数 器等于占空比寄存器的值时,输出为低电平。对外输出波形先是高电平然后再变 为低电平。

2、PWM 波形对齐寄存器 PWMCAE

该控制寄存器设定通道的级联和两种工作模式:等待模式和冻结模式。这 两种模式如图 10 和图 11 所示。

图 10 等待模式

图 11 冻结模式

只有当相应的通道关闭后,才能改变 这些控制字。 用法: PWMCTL_CON67=1 --- 通道6、7 级联成一个 16 位的 PWM 通道。此 时只有7 通道的控制字起作用,原通道 7 的使能位、PWM 输出极性选择位、时 钟选择控制位以及对齐方式选择位用来设置级联后的 PWM 输出特性 PWMCTL_CON67=0 --- 通道6,7 通道不级联 CON45、CON23、CON01 的用法同 CON67 相似。设置此控制字的意 义在于扩大了PWM 对外输出脉冲的频率范围。 PSWAI=1 --- MCU 一旦处于等待状态,就会停止时钟的输入。这样就不 会因时钟在空操作而费电;当它置为0,则MCU 就是处于等待状态,也允许 时钟的输入。 PFRZ=1 --- MCU 一旦处于冻结状态,就会停止计数器工作。 (责任编辑:dzsj8)

1、PWM 预分频寄存器 PWMPRCLK

PWMPRCLK 寄存器每一位如图 3 所示:

复位默认值:0000 0000B

813 次

图3 PWMPRCLK 寄存器

PWMPRCLK 寄存器包括 ClockA 预分频和 ClockB 预分频的控制位。ClockA、 ClockB 的值为总线时钟的 1/2n (0≤n≤7),具体设置参照图 4 和图 5

mc9s12xs128程序教程

PWMPRCLK 寄存器每一位如图 3 所示:

复位默认值:0000 0000B

813 次

图3 PWMPRCLK 寄存器

PWMPRCLK 寄存器包括 ClockA 预分频和 ClockB 预分频的控制位。ClockA、 ClockB 的值为总线时钟的 1/2n (0≤n≤7),具体设置参照图 4 和图 5

/*******************************************************************/

图 14 PWM 左对齐方式 2、中心对齐方式

在该方式下,脉冲计数器为双向计数,计数初值为 0 。 当 PWM 使能后,计数器 PWMCNT 从 0 开始对时钟信号递增计数,开始输出一个 周期。当计数器与占空比常数寄存器 PWMDTY 相等时,比较器 1 输出有效,触发器 翻转,而 PWMCNT 继续计数,当计数值与周期常数 PWMPER 相等时,比较器 2 输出 有效,此时改变 PWMCNT 的计数方向,使其递解计数;当 PWMCNT 再次与 PWMDTY 相 等时,比较器 1 再一次输出有效,使触发器再次翻转,而 PWMCNT 继续递减计数, 等待 PWMCNT 减回至 0,完成一个输出周期。原理参照图 15: /********************************************************************/ 玉良理解的就是计数器的值先增加到与 PWMDTY 相等后,比较器 1 置位,而计数器 继续计数,当数值与 PWMPER 中的值相等后,改变其计数方向,改为递减计数,当 再一次与 PWMDTY 中的值相等后,比较器再一次输出有效,使触发器反转,而计数 器继续递减计数直到计数器的值为 0,从而完成一个输出周期。 /*********************************************************************/

MC9S12DG128的结构与工作原理

❖ N——符号位(负标志) (Negative Flag) 当运算结果为负时,N=1,否则,N=0。

❖ H——辅助进位(半进位)标志(Half-carry Flag) 在加法过程中,若累加器A中的D3向D4位产生进位,H=1;否则,H=0。

❖ MC9S12DG128的内部结构 ❖ MC9S12DG128引脚功能 ❖ MC9S12DG128的运行模式 ❖ MC9S12DG128的存储器组织

1

概述

➢ MC9S12DG128的内核是16位中央处理单元CPU12, 有29个独立的数字I/O口(A、B、K和E),20个独 立的数字I/O口(H、P、J)具有中断和唤醒功能。

图2.7堆栈的类型

13

2.1 MC9S12DG128的内部结构

2.1.1 CPU12内核(Star Core)

❖ 向上生长型堆栈——栈底占用较低地址,栈顶占用较高地址。 ➢ 数据压入堆栈时,SP的内容自动加1,作为本次进栈的地址,然后再存

入信息。随着数据的存入,SP的值越来越大。数据从堆栈弹出后,SP的 内容自动减1。 ❖ 向下生长型堆栈——栈底占用较高地址,栈顶占用较低地址。 ➢ CPU12的堆栈属于向下生长型,将一个字节数据压入堆栈时,SP自动减 1。从堆栈中弹出一个字节数据时,SP自动加1。若操作数为双字节,则 SP每次加2或减2。因此,随着数据的存入,SP的值越来越小。 ➢ SP总是指向最后压入堆栈的一个字节数据,称为实栈顶。压栈操作时, 先调整指针(减1或减2),后保存数据。初始化时,一般将SP指向与栈底 相邻的单元,它不属于栈底,以此表示堆栈为空。

❖ 影响SP内容的指令有加载、目的操作数为SP的寄存器传送指令、压栈、 退栈、加减1、中断和子程序调用等。

S12XS128程序--ECT模块介绍

1、简述MC9S12XS128定时器模块与MC9S12DG128 ECT部分功能完全类似,以下均以ECT模块介绍xs128定时器模块。

HC12 增强型捕捉计时器模块在HCS12标准定时器的基础上增加了一些特点,用以扩展它的应用范围,特别是在汽车 ABS 方面。

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。

该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。

波形的脉宽可以在几微秒到数秒的范围内变化。

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到TSCR($06)的TSFRZ 位被置1。

等待:计数器保持运行,直到TSCR($06)的TSWAI 位被置1。

正常:计时器和计数器均保持运行,直到TSCR($06)的TEN 位和MCCTL($26)的MCEN 位被分别清0。

IC 通道组IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC/OC 寄存器 TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。

非缓冲通道没有保持寄存器,入口也没有延迟计数器,但每个通道入口设置了一个 2 输入端的多路器,事件触发信号可以是来自本通道的输入引脚PORTn,也可以是来自其关联通道PORT(n-4)的延迟计数器输出,使用更加灵活。

当延迟功能有效时,输入引脚检测到一个有效的边沿后,延迟计数器开始对P 时钟(模块时钟)进行计数,当到达设定的计数值后,延迟计数器在其输出端有条件地产生一个脉冲,这个条件就是延迟前后的引脚电平相反。

MC9S12XS128单片机简介

MC9S12XS128 单片机简介1、HCS12X 系列单片机简介Freescale 公司的16 位单片机主要分为HC12 、HCS12、HCS12X 三个系列。

HC12核心是16 位高速CPU12 核,总线速度8MHZ;HCS12 系列单片机以速度更快的CPU12 内核为核心,简称S12 系列,典型的S12 总线速度可以达到25MHZ。

HCS12X 系列单片机是Freescale 公司于2005 年推出的HCS12 系列增强型产品,基于S12 CPU 内核,可以达到25MHz 的HCS12 的2-5 倍性能。

总线频率最高可达40 MHz。

S12X 系列单片机目前又有几个子系列:MC9S12XA 系列、MC9S12XB 系列、MC9S12XD 系列、MC9S12XE 系列、MC9S12XF系列、MC9S12XH 系列和MC9S12XS 系列。

MC9S12XS128 就是S12X 系列中的一个成员。

2、MC9S12XS128 性能概述MC9S12XS128 是16 位单片机,由16 位中央处理单元(CPU12X)、128KB 程序Flash(P-lash)、8KB RAM、8KB 数据Flash(D-lash)组成片内存储器。

主要功能模块包括:内部存储器内部PLL 锁相环模块2 个异步串口通讯SCI1 个串行外设接口SPIMSCAN 模块1 个8 通道输入/输出比较定时器模块TIM周期中断定时器模块PIT16 通道A/D 转换模块ADC1 个8 通道脉冲宽度调制模块PWM输入/输出数字I/O 口3、输入/输出数字I/O 口MC9S12XS128 有3 种封装,分别为64 引脚、80 引脚、112 引脚封装。

其全名分别为MC9S12XS128MAE、MC9S12XS128MAA、MC9S12XS128MAL。

MC9S12XS 系列具有丰富的输入/输出端口资源,同时集成了多种功能模块,端口包括PORTA、PORTB、PORTE、PORTK、PORTT、PORTS、PORTM、PORTP、PORTH、PORTJ 和PORTAD 共11 个端口。

MC9S12XS128-AD转换详解知识讲解

M C9S12X S128-A D转换详解A/D转换模块详解1、A/D转换原理A/D转换的过程是模拟信号依次通过取样、保持和量化、编码几个过程后转换为数字格式。

a)取样与保持一般取样与保持过程是同时完成的,取样-保持电路的原理图如图16所示,由输入放大器A1、输出放大器A2、保持电容C H和电子开关S组成,要求 A V1 * A V2 = 1。

原理是:当开关S闭合时,电路处于取样阶段,电容器充电,由于 A V1 * A V2 = 1,所以输出等于输入;当开关S断开时,由于A 2输入阻抗较大而且开关理想,可认为CH没有放电回路,输出电压保持不变。

图16 取样-保持电路取样-保持以均匀间隔对模拟信号进行抽样,并且在每个抽样运算后在足够的时间内保持抽样值恒定,以保证输出值可以被A/D 转换器精确转换。

b)量化与编码量化的方法,一般有舍尾取整法和四舍五入法,过程是先取顶量化单位Δ,量化单位取值越小,量化误差的绝对值就越小,具体过程在这里就不做介绍了。

将量化后的结果用二进制码表示叫做编码。

2、A/D转换器的技术指标a)分辨率分辨率说明A/D转换器对输入信号的分辨能力,理论上,n位A/D转换器能区分的输入电压的最小值为满量程的1/2n 。

也就是说,在参考电压一定时,输出位数越多,量化单位就越小,分辨率就越高。

S12的ATD模块中,若输出设置为8位的话,那么转换器能区分的输入信号最小电压为19.53mV。

b)转换时间A/D转换器按其工作原理可以分为并联比较型(转换速度快ns级)、逐次逼近型(转换速度适中us级)、双积分型(速度慢抗干扰能力强)。

不同类型的转化的A/D转换器转换时间不尽相同,S12的ATD模块中,8位数字量转换时间仅有6us,10位数字量转换时间仅有7us。

S12内置了2组10位/8位的A/D模块:ATD0和ATD1,共有16个模拟量输入通道,属于逐次逼近型A/D转换器(这个转换过程与用天平称物的原理相似)。

mc9s12xs128内存映射和数据flash操作

解答

16位地址,寻址范围为0~65536,即64k MC9S12XS128的RAM为8K,P-FLASH为 128K,D-FLASH为8K。

*p=0x8000,访问的是P-FLASH

?

MC9S12XS128内存结构

MC9S12XS128使用global adress(全局地 址)对内存划分地址空间。全局地址共 23bit,寻址能力达到8M 使用全局地址划分的内存空间如下: 0x10_0000~0x10_1FFF:8K d-flash 0x7E_0000~0x7F_FFFF:128K p-flash 0x0F_E000~0x0F_FFFF:8K 非分页RAM 问题:CPU和BDM都是使用16bit local address(本地地址)我们在程序中定义的 指针变量默认都是near型,即16位地址, 如何解决?

D-flash状态寄存器

注意: 1. 开始新的FLASH命令之前必须等待上 一个命令结束,即需要查询CCIF标志。 2. 在启动flash命令之前,FSTAT寄存器中 的ACCERR和FPVIOL两个标志位必须 被清除,否则无法启动新的FLASH操 作。

完整的擦除操作

while(FSTAT_CCIF==0); if(FSTAT_ACCERR) //判断并清除标志位; FSTAT_ACCERR=1; if(FSTAT_FPVIOL) //判断并清除标志位; FSTAT_FPVIOL=1; FCCOBIX_CCOBIX=0x00; FCCOBHI=0x12; //高字节写入擦除命令 FCCOBLO=0x10; //低字节d-flash全局地址高8位,固定 为0x10 FCCOBIX_CCOBIX=0x01; FCCOB=ADDR16; //写入低16位的地址 FSTAT_CCIF=1; //启动执行命令 while(FSTAT_CCIF==0); //等待执行完成