EDA技术及应用—Verilog HDL版(第三版) (6)

EDA技术与Verilog_HDL(潘松)第四章与第六章课后习题答案

第4章

Verilog HDL设计初步

习

题

4-1 举例说明,Verilog HDL的操作符中,哪些操作符的运算结果总是一位的。 答: P74/74/80/92

4-4 举例说明,为什么使用条件叙述不完整的条件句能导致产生时序模块的综合结果? 答:● 当CLK发生了电平变化,但是从1变到0。这时无论D是否变化,都将启动

过程去执行if语句;但此时CLK=0,无法执行if语句,从而无法执行赋值语句 Q<=D,于是Q只能保持原值不变(这就意味着需要在设计模块中引入存储元件)。 ● 当CLK没有发生任何变化,且CLK一直为0,而敏感信号D发生了变化。这 时也能启动过程,但由于CLK=0,无法执行if语句,从而也就无法执行赋值语句 Q<=D,导致Q只能保持原值(这也意味着需要在设计模块中引入存储元件)。 在以上两种情况中,由于if语句不满足条件,于是将跳过赋值表达式Q<=D, 不执行此赋值表达式而结束if语句和过程.对于这种语言现象,Velilog综合器解 释为,对于不满足条件,跳过赋值语句Q<=D不予执行,即意味着保持Q的原值 不变(保持前一次满足if条件时Q被更新的值)。对于数字电路来说,当输入改变后 试图保持一个值不变,就意味着使用具有存储功能的元件,就是必须引进时序元 件来保存Q中的原值,直到满足if语句的判断条件后才能更新Q中的值,于是便产 生了时序元件。 module LATCH1 (CLK, D, Q); output Q; input CLK, D; reg Q; always @(D or CLK) if(CLK)Q<=D; //当CLK=1时D被锁入Q endmodule

EDA技术与Verilog设计第六章课后习题部分答案

6-15

6-16

设计一个74161的电路。

6-16

注意:异步清零、同步置位

CO= Q3 Q2 Q1 Q0 CTT

6-16

module wytest(reset,load,ctt,ctp,clk,data_in,out,co);//习题6-16 input reset,load,ctt,ctp,clk; input[3:0] data_in; output[3:0] out; output co; reg[3:0] out; reg co; always@(posedge clk or negedge reset) if(!reset) begin out<=4'b0; co<=1'b0; end else if(!load) out<=data_in; else if(!ctt) out<=out; else if(!ctp) out<=out;

always@(posedge clk) begin firsta[3:0]<=a[7:4]; seconda[3:0]<=a[3:0]; firstb[3:0]<=b[7:4]; secondb[3:0]<=b[3:0]; end

mul4x4 m1(outa, firsta,firstb,clk), m2(outb, seconda,firstb,clk), m3(outc, firsta,secondb,clk), m4(outd,seconda,secondb,clk);

6-13

6-14

试编写一个实现3输入与非门的verilog程序;

module

wytest(a,o); a;

EDA技术与Verilog_HDL(潘松)第6章习题答案

6-1 在Verilog设计中,给时序电路清零(复位)有两种不同方法,它们是什么,如何实现?答:同步清零、异步清零,在过程语句敏感信号表中的逻辑表述posedge CLK用于指明正向跳变,或negedge用于指明负向跳变实现6-2 哪一种复位方法必须将复位信号放在敏感信号表中?给出这两种电路的Verilog 描述。

答:异步复位必须将复位信号放在敏感信号表中。

同步清零:always @(posedge CLK) //CLK上升沿启动Q<=D; //当CLK有升沿时D被锁入Q异步清零:always @(posedge CLK or negedge RST) begin //块开始if(!RST)Q<=0; //如果RST=0条件成立,Q被清0else if(EN) Q<=D;//在CLK上升沿处,EN=1,则执行赋值语句end//块结束6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

module Statistics8(sum,A); output[3:0]sum;input[7:0] A;reg[3:0] sum;integer i;always @(A)beginsum=0;for(i=0;i<=8;i=i+1) //for 语句if(A[i]) sum=sum+1;else sum=sum;endendmodule module Statistics8(sum,A); parameter S=4;output[3:0]sum;input[7:0] A;reg[3:0] sum;reg[2*S:1]TA;integer i;always @(A)beginTA=A; sum=0;repeat(2*S)beginif(TA[1])sum=sum+1;TA=TA>>1;endendendmodulerepeat循环语句for循环语句module Statistics8(sum,A);parameter S=8;output[3:0]sum;input[7:0] A;reg[S:1] AT;reg[3:0] sum;reg[S:0] CT;always @(A) beginAT={{S{1'b0}},A}; sum=0; CT=S;while(CT>0) beginif(AT[1])sum=sum+1;else sum=sum;begin CT= CT-1; AT=AT>>1; end end endendmodule6-3 用不同循环语句分别设计一个逻辑电路模块,用以统计一8位二进制数中含1的数量。

EDA技术与Verilog设计王金明版第6章

6.2 块语句

并行块fork-join fork-join块中的所有语句是并发执行的。

ቤተ መጻሕፍቲ ባይዱ

比如: fork regb=rega; regc=regb; join 由于fork-join块内的语句同时执行,在上面的块语句执行完 后,regb更新为rega的值,而regc的值更新为没有改变前 regb的值,故执行完成后,regb与regc的值是不同的。

如果加上时序控制,则这个always语句将变为一条 非常有用的描述语句。见下例:

[例]:always #half_period areg = ~areg; 这 个 例 子 生 成 了 一 个 周 期 为 :period(=2*half_period) 的无限延续的信号波形, 常用这种方法来描述时钟信号,作为激励信号来测 试所设计的电路。 Verilog提供三种时序控制方法:基于延迟的时 序控制、基于事件的时序控制和电平敏感的时序控 制。

������ initial 过程块的使用主要是面向功能模拟的,通常用 来描述测试模块的初始化、监视、波形生成等功能; ������ always过程块的使用主要是对硬件功能模拟的行为进 行描述,也可以在测试模块用来对时钟进行描述。利用 always过程块可以实现触发器、锁存器和组合电路。 一个模块中可有多个initial和always语句,代表多个过程 块的存在,它们之间相互独立,并行运行

Verilog HDL行为语句

类别 initial 过程语句 块语句 always 串行块begin-end 并行块fork-join √ √ 语句 可综合性

赋值语句

持续赋值assign

过程赋值=、<= if-else

√

√ √ √ √

EDA应用技术 硬件描述语言Verilog HDL

第3章硬件描述语言Verilog HDL EDA应用技术EDA应用技术3.1 引言3.1 引言内容概要3.1 引言 3.1 引言3.1 引言形式化地表示电路的行为和结构;3.2 Verilog HDL基本结构内容概要3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构[例3.2.5¾Verilog HDLendmodule声明语句中。

模块是可以进行层次嵌套的。

3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构Verilog3.2 Verilog HDL基本结构 3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构Verilog3.2 Verilog HDL基本结构3.2 Verilog HDL基本结构HDL语言描述的“东西”都通过其名字来识别,3.2 Verilog HDL基本结构六、编写Verilog3.2 Verilog HDL基本结构1语汇代码的编写标准3.2 Verilog HDL基本结构1语汇代码的编写标准(续)3.2 Verilog HDL基本结构2综合代码的编写标准3.2 Verilog HDL基本结构(6)描述组合逻辑的always块,一定不能有不完全赋值,即所有输出变2综合代码的编写标准(续1)3.2 Verilog HDL基本结构(10)避免生成不想要的触发器。

2综合代码的编写标准(续2)3.2 Verilog HDL基本结构2综合代码的编写标准(续3)3.2 Verilog HDL基本结构2综合代码的编写标准(续4)3.3 数据类型及常量、变量内容概要3.3 数据类型及常量、变量一、数据类型3.3 数据类型及常量、变量(1)3.3 数据类型及常量、变量8’b1001xxxx8’b1010zzzz3.3 数据类型及常量、变量(3)3.3 数据类型及常量、变量3.3 数据类型及常量、变量(4)parameter常量(符号常量)3.3 数据类型及常量、变量 3.3 数据类型及常量、变量:利用特殊符号“#”3.3 数据类型及常量、变量3.3 数据类型及常量、变量三、变量1. nets型变量定义——输出始终随输入的变化而变化的变量。

《EDA技术与Verilog HDL》 第6章

实验与设计

6-3 VGA彩条信号显示控制电路设计

(1)实验目的: (2)实验原理:

实验与设计

6-3 VGA彩条信号显示控制电路设计

(1)实验目的: (2)实验原理:

(3) 实验内容1: (4) 实验内容2: (5) 实验内容3: (6) 实验内容4:

实验与设计

实验与设计

6-1 半整数与奇数分频器设计 (1)实验目的:学习利用Verilog完成实用程序的设计。 (2)实验内容1: (3)实验内容2: (4)实验内容3: (5)实验内容4:

实验与设计

6-2 数控分频器设计 (1)实验目的: (2)实验内容1: (3)实验内容2: (4)实验内容3:

(5)实验内容4: (6)实验内容5:

6.3 移位寄存器之Verilog HDL设计

6.3.4 使用循环语句设计乘法器 4. repeat语句

6.3 移位寄存器之Verilog HDL设计

6.3.4 使用循环语句设计乘法器 5. while语句

6.3 移位寄存器之Verilog HDL设计

6.3.4 使用循环语句设计乘法器 5. while语句

实验与设计

6-3 VGA彩条信号显示控制电路设计

(1)实验目的: (2)实验原理:

实验与设计

6-3 VGA彩条信号显示控制电路设计

(1)实验目的: (2)实验原理:

实验与设计

实验与设计

6-3 VGA彩条信号显示控制电路设计

(1)实验目的: (2)实验原理:

实验与设计

6-3 VGA彩条信号显示控制电路设计

6-4 基于时序电路的移位相加型8位硬件乘法器设计 (1)实验原理: (2)实验任务1: (3)实验任务2 : (4)实验任务3 :

eda技术及应用第三版课后答案谭会生

eda技术及应用第三版课后答案谭会生【篇一:《eda技术》课程大纲】>一、课程概述1.课程描述《eda技术》是通信工程专业的一门重要的集中实践课,是通信工程专业学生所必须具备的现代电子设计技术技能知识。

eda是电子技术的发展方向,也是电子技术教学中必不可少的内容。

本课程主要介绍可编程逻辑器件在电子电路设计及实现上的应用,介绍电路原理图和pcb图的设计技术。

开设该课程,就是要让学生了解大规模专用集成电路fpga和cpld的结构,熟悉一种以上的硬件描述语言,掌握一种以上的开发工具的使用等,掌握电路原理图和pcb图的现代设计技术与方法,从而提高学生应用计算机对电子电路和高速智能化系统进行分析与设计的能力。

2.设计思路本课程坚持“以学生为中心”的原则,以项目任务驱动的方式,采取理论知识与案例相结合的方式授课,提高学生的学习主动性。

通过必要的理论知识讲授、大量的实践训练和案例分析,培养学生的动手设计和实践能力,掌握eda开发的整个流程和基本技巧。

课程采用演示讲授和实践相结合,边讲边练的方法,让学生切身体会并掌握eda开发产品的流程和方法。

本课程集中2周时间开设,注重实践性,边讲边练,让学生切身体会并掌握eda开发技术。

3.实践要求(1)纪律和安全要求①不得将食物带入实验室,每次实训后请将使用后的废弃物带走。

违反者每次扣罚平时分2分。

②实训期间不得做与实训无关的其他事情,不得大声喧哗或做其他影响实训正常进行的事宜。

违反者每次扣罚平时分2分。

③实训期间,若学生有事不能正常参加实训,须提前以书面形式请假,并按指导教师的安排补做实训。

未经指导教师许可,学生不得任意调换实训时间和实训地点。

违反者每次扣罚平时分4分。

④学生不得以任何理由替代他人进行实训,违者直接取消实训成绩。

⑤学生除操作自己所分配的计算机外,不得操作实验室内其他任何设备。

违者每次扣罚平时分2分。

(2)业务要求实训所使用的软件protel和quartus ii,所有数据均通过服务器中转以及储存在服务器上,所以重启自己所用的电脑不会造成数据丢失。

《EDA技术与Verilog HDL》PPT第3版 第4章 FPGA硬件实现

图4-59 测频时序控制电路

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-60 测频时序控制电路工作波形

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-61 频率计顶层电路原理图

实验与设计

实验4-4 应用宏模块设计数字频率计

图4-62 频率计工作时序波形

4.8 安装Quartus II 13.1说明

图4-45 安装QuartusII 13.1设计文件界面,点击右侧安装按钮

4.8 安装Quartus II 13.1说明

图4-46 设定QuartusII 13.1设计文件安装路径

4.8 安装Quartus II 13.1说明

图4-47 选择安装软件。注意不要漏了ModelSim-Altera Starter Edition

图4-3 利用New Project Wizard创建工程CNT10 ⑵ 将设计文件加入工程中。

4.1 代码编辑输入和系统编译

4.1.2 创建工程 ⑶ 选择目标芯片。

图4-4 选择目标器件EP4CE55F23C8

4.1 代码编辑输入和系统编译

4.1.2 创建工程 ⑷ 工具设置。

图4-5 设计与验证工具软件选择

(3)原理图文件存盘。

图4-30 完成设计并将半加器封装成一个元件,以便在更高层设计中调用

4.4 电路原理图设计流程

4.4.1 设计一个半加器

(4)创建原理图文件为顶层设计的工程。

(5)绘制半加器原理图。

(6)仿真测试半加器。

4.4 电路原理图设计流程

4.4.2 完成全加器顶层设计

图4-31 在f_adder工程下加入半加器原件

EDA技术及应用—Verilog HDL版(第三版) (1)

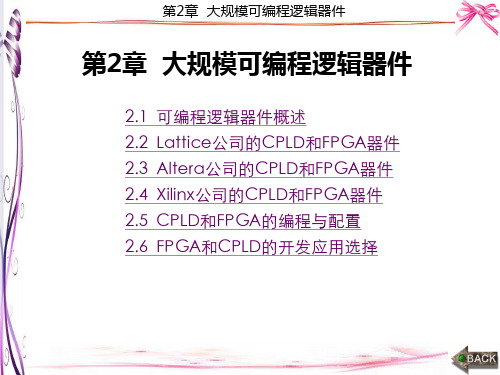

第2章 大规模可编程逻辑器件

(4) 封装代码。如Altera公司的EPM7128SLC84中的LC, 表示采用PLCC封装(Plastic Leaded Chip Carrier,塑料方形扁 平封装)。PLD封装除PLCC外,还有BGA(Ball Grid Array, 球形网状阵列)、C/JLCC(Ceramic /J-Leaded Chip Carrier,)、 C/M/P/TQFP(Ceramic/Metal/Plastic/Thin Quard Flat Package)、 PDIP/DIP(Plastic Double In line Package)、PGA(Ceramic Pin Grid Array)等,多以其缩写来描述,但要注意各公司稍有差 别,如PLCC,Altera公司用LC描述,Xilinx公司用PC描述, Lattice公司用J来描述。

第2章 大规模可编程逻辑器件

2.1.1 PLD的发展进程

最早的可编程逻辑器件出现在20世纪70年代初,主要是 可编程只读存储器(PROM)和可编程逻辑阵列(PLA)。20世 纪70年代末出现了可编程阵列逻辑(Programmable Array Logic,简称PAL)器件。20世纪80年代初期,美国Lattice公 司推出了一种新型的PLD器件,称为通用阵列逻辑(Generic Array Logic,简称GAL),一般认为它是第二代PLD器件。 随着技术进步,生产工艺不断改进,器件规模不断扩大,逻 辑功能不断增强,各种可编程逻辑器件如雨后春笋般涌现, 如PROM、EPROM、EEPROM等。

第2章 大规模可编程逻辑器件

采用ISP技术之后,硬件设计可以变得像软件设计那样灵活 而易于修改,硬件的功能也可以实时地加以更新或按预定的 程序改变配置。这不仅扩展了器件的用途,缩短了系统的设 计和调试周期,而且还省去了对器件单独编程的环节,因而 也省去了器件编程设备,简化了目标系统的现场升级和维护 工作。

EDA技术及应用第三版教学设计

EDA技术及应用第三版教学设计简介在目前快速发展的电子领域中,EDA(Electronic Design Automation,电子设计自动化)技术早已成为不可或缺的一环。

EDA技术主要包括从原理图设计开始一直到制卡和封装的全过程,是电子设计领域中近年来发展最快的技术之一。

通过本教学设计,旨在使学生掌握EDA基本原理,熟悉其常用工具与软件,了解EDA的应用领域及其趋势,为培养电子设计人才提供帮助。

教学内容第一章 EDA简介1.1 EDA的概述1.2 EDA的发展历程1.3 EDA在电子技术中的作用第二章 EDA基础原理2.1 EDA工具体系结构2.2 EDA中的计算机辅助设计2.3 EDA中的电路仿真与分析第三章 EDA工具与软件3.1 EDA工具介绍3.2 常用EDA软件及其应用第四章 EDA的应用领域4.1 EDA在电子产品设计中的应用4.2 EDA在通信设备中的应用4.3 EDA在汽车电子领域中的应用4.4 EDA在医疗器械中的应用第五章 EDA的未来趋势5.1 EDA的趋势与发展5.2 EDA技术的未来发展方向教学方法本教学设计采用优先使用案例、实验和练习的方式,将概念和理论知识应用于实际问题中。

同时,将以小组案例研究、课堂交流和讨论的方式,促进学生之间和教师之间的交流和互动。

评估方式本课程采用察看作业进展情况、小组案例分析和课堂讨论的方式对学生进行评估。

其中,作业每占总成绩的20%、案例分析与讨论每占30%。

参考文献•Alvin R. Lebeck. (2020), EDA技术及应用第三版, 人民邮电出版社, ISBN:978-7-115-55493-2•Stephen A. Thomas. (2017), EDA技术: 从基础入门到应用, 电子工业出版社, ISBN:978-7-121-32143-2结语EDA技术的发展已经推动了现代电子技术的进步,对于学习EDA的学生来说,了解基础原理和应用领域是至关重要的。

第3版教材VerilogHDL

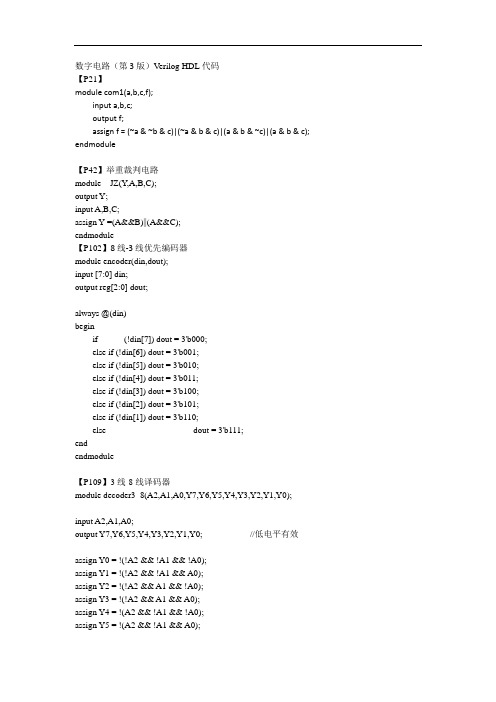

数字电路(第3版)Verilog HDL代码【P21】module com1(a,b,c,f);input a,b,c;output f;assign f = (~a & ~b & c)|(~a & b & c)|(a & b & ~c)|(a & b & c); endmodule【P42】举重裁判电路module JZ(Y,A,B,C);output Y;input A,B,C;assign Y =(A&&B)||(A&&C);endmodule【P102】8线-3线优先编码器module encoder(din,dout);input [7:0] din;output reg[2:0] dout;always @(din)beginif (!din[7]) dout = 3'b000;else if (!din[6]) dout = 3'b001;else if (!din[5]) dout = 3'b010;else if (!din[4]) dout = 3'b011;else if (!din[3]) dout = 3'b100;else if (!din[2]) dout = 3'b101;else if (!din[1]) dout = 3'b110;else dout = 3'b111;endendmodule【P109】3线-8线译码器module decoder3_8(A2,A1,A0,Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0);input A2,A1,A0;output Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0; //低电平有效assign Y0 = !(!A2 && !A1 && !A0);assign Y1 = !(!A2 && !A1 && A0);assign Y2 = !(!A2 && A1 && !A0);assign Y3 = !(!A2 && A1 && A0);assign Y4 = !(A2 && !A1 && !A0);assign Y5 = !(A2 && !A1 && A0);assign Y6 = !(A2 && A1 && !A0);assign Y7 = !(A2 && A1 && A0); Endmodulemodule encoder(din,dout);input [7:0] din;output reg[2:0] dout;always @(din)beginif (!din[7]) dout = 3'b000;else if (!din[6]) dout = 3'b001;else if (!din[5]) dout = 3'b010;else if (!din[4]) dout = 3'b011;else if (!din[3]) dout = 3'b100;else if (!din[2]) dout = 3'b101;else if (!din[1]) dout = 3'b110;else dout = 3'b111; endendmodule【P110】7段显示译码器ModuleLED7S(DIN,Y);input[3:0] DIN;output[6:0] Y;reg[6:0] Y;always @(DIN)begincase(DIN)4'b0000: Y= 7'b0111111;4'b0001: Y = 7'b0000110;4'b0010: Y = 7'b1011011;4'b0011: Y = 7'b1001111;4'b0100: Y = 7'b1100110;4'b0101: Y = 7'b1101101;4'b0110: Y = 7'b1111101;4'b0111: Y = 7'b0000111;4'b1000: Y = 7'b1111111;4'b1001: Y = 7'b1101111;4'b1010: Y = 7'b1110111;4'b1011: Y = 7'b1111100;4'b1100: Y = 7'b0111001;4'b1101: Y = 7'b1011110;4'b1110: Y = 7'b1111001;4'b1111: Y = 7'b1110001;default: Y = 7'b0000000;endcaseendendmodule【P114】4选1数据选择器(1)利用case语句module MUX41(d0,d1,d2,d3,SEL,Y);output Y;input d0,d1,d2,d3;input [1:0] SEL;reg Y;always@(A,B,C,D,SEL)case (SEL)2'b00:Y=d0;2'b01:Y=d1;2'b10:Y=d2;2'b11:Y=d3;default:Y=2'bx;endcaseendmodule(2)利用if语句module MUX41B(d0,d1,d2,d3,SEL,Y); output Y;input d0,d1,d2,d3;input [1:0] SEL;reg Y;always@(d0,d1,d2,d3,SEL)beginif (SEL==2'b00)Y=d0;else if(SEL==2'b01)Y=d1;else if(SEL==2'b10)Y=d2;elseY=d3;endendmodule【P116】4位数值比较器module compare4bit(A,B,AEQB,AGTB,ALTB); input[3:0] A,B;output AEQB,AGTB,ALTB;assign AEQB = (A==B);assign AGTB = (A>B);assign ALTB = (A<B);endmodule【P120】4位加法器module add4b(A,B,CIN,S,COUT);input[3:0] A;input[3:0] B;input CIN;output[3:0] S;output COUT;wire[4:0] CRLT;assign CRLT = {1'b0,A} + {1'b0,B} + {4'b0000,CIN};assign S = CRLT[3:0];assign COUT = CRLT[4];endmodule【P136】高有效的rs触发器module rs ( R, S, Q, QN );input R, S;output Q, QN;reg Q;//寄存器定义assign QN = ~Q;//assign语句,QB=/Q?always @( R,S )//在CLK的上跳沿,执行以下语句。

EDA第6章基本数字逻辑单元HDL描述

宽度为1至256通道(总数多达4096个触发通道) 且降低了对采样存储的需求。

每个触发端口多达16个单独的匹配单元,对应 每个触发器端口有多个匹配单元,增加了事件

每个触发条件的16个不同的比较

检测的灵活性同时保存了宝贵的资源。

对于用户时钟速率大于500MHz的情况,所有的 高速触发事件检测和数据捕获的能力

值和阻塞赋值。 原则6:不要在多个always块中为同一个变量赋值 原则7:用$strobe系统任务来显示用非阻塞赋值的变

量值。

基本数字逻辑单元HDL描述

--有限自动状态机HDL描述

有限自动状态机FSM(Finate State Machine)的设计 是复杂数字系统中非常重要的一部分,是实现高效率高 可靠性逻辑控制的重要途径。

Mealy型状态机的输出由状态机的输入和状态机的状态共同 决定;

有限自动状态机HDL描述

--FSM的分类及描述

该序列检测器将检测序列“1101”,当检测到该序列时, 状态机的输出z为1。

有限自动状态机HDL描述

--FSM的分类及描述

Moore状态机检测序列时,使用了5个状态,当为状态S4时, 输出为1。

大部分数字系统都是由控制单元和数据单元组成的。

数据单元负责数据的处理和传输,而控制单元主要是控制数据单元 的操作的顺序。

在数字系统中,控制单元往往是通过使用有限状态机实现的,有限 状态机接受外部信号以及数据单元产生的状态信息,产生控制信号 序列。

有限自动状态机HDL描述

--FSM设计原理

有限状态机可以由标准数学模型定义。此模型包括一组状

可编程逻辑器件调试

-概述

只能通过测试仪器或软件知道输入端口和输出端口, 而内部逻辑的运行情况不知道。

《EDA技术与Verilog HDL》PPT第3版 第1章 EDA技术概述

1.熔丝(Fuse)型器件 2.反熔丝(Anti-fuse)型器件 3.EPROM型 4.EEPROM型 5.SRAM型 6.Flash型

1.6 可编程逻辑器件

1.6.2 PROM可编程原理

图1-5 两种不同版本的国际标准逻辑门符号对照表

1.6 可编程逻辑器件

1.6.2 PROM可编程原理

1.6 可编程逻辑器件

1.8.3 内嵌Flash的FPGA器件

1.9 硬件测试技术

1.9.1 内部逻辑测试 1.9.2 JTAG边界扫描测试

1.10 编程与配置

基于电可擦除存储单元的EEPROM或Flash技术 基于SRAM查找表的编程单元。 基于反熔丝编程单元。

主动配置方式

被动配置方式

1.11 Quartus II

HDL

VHDL Verilog HDL SystemVerilog System C

在EDA设计中使用最多,也得到几 乎所有的主流EDA工具的支持

这两种HDL语言还处于完善过程中, 主要加强了系统验证方面的功能。

1.4 EDA技术的优势

1.保证设计过程的正确性,大大降低设计成本,缩短设计周期。 2.有各类库的支持。 3.极大地简化设计文档的管理。 4.日益强大的逻辑设计仿真测试技术。 5.设计者拥有完全的自主权,再无受制于人之虞。 6.良好的可移植与可测试性,为系统开发提供了可靠的保证。 7.能将所有设计环节纳入统一的自顶向下的设计方案中。 8.EDA不但在整个设计流程上充分利用计算机的自动设计能力,而 且在各个设计层次上利用计算机完成不同内容的仿真模拟,在系统 板设计结束后仍可利用计算机对硬件系统进行完整的测试。

1.5.3 适配(布线布局)

1.5 面向FPGA和CPLD的开发流程

EDA技术与应用(陈新华)Verilog_HDL_huawei

Four_bit_FA

FA FCin

A Sum B FA_struct Count Cin

FSum

FA_struct

FA_struct

A

FB

Sum B FA_struct Count Cin

FCount

Four_bit_FA

图5 两位全加器的结构示意图 代码: module Four_bit_FA (FA, FB, FCin, FSum, FCout ) ; parameter SIZE = 2; input [SIZE:1] FA;

2004-08-16 版权所有,侵权必究 第10页,共41页

Verilog HDL 入门教程

绝密 请输入文档编号

逻辑功能描述部分如: assign d_out = d_en ? din :'bz; mytri u_mytri(din,d_en,d_out); 功能描述用来产生各种逻辑(主要是组合逻辑和时序逻辑,可用多种方法进行描述,具体的 用法下面章节有介绍),还可用来实例化一个器件,该器件可以是厂家的器件库也可以是我们自 己用HDL设计的模块(相当于在原理图输入时调用一个库元件)。在逻辑功能描述中,主要用到 assign 和always 两个语句。 3、对每个模块都要进行端口定义,并说明输入、输出口,然后对模块的功能进行逻辑描述, 当然,对测试模块,可以没有输入输出口。 4、Verilog HDL 的书写格式自由,一行可以写几个语句,也可以一个语句分几行写。具体由 代码书写规范约束。 5、除endmodule 语句外,每个语句后面需有分号表示该语句结束。

2004-08-16 版权所有,侵权必究 第9页,共41页

//模块定义

Verilog HDL 入门教程

EDA技术及应用 Verilog HDL版(第三版) 第6章

6.1 8位加法器的设计

1.系统设计思路 加法器是数字系统中的基本逻辑器件,减法器和硬件乘 法器都可由加法器来构成。多位加法器的构成有两种方式: 并行进位和串行进位。 并行进位方式设有进位产生逻辑,运算速度较快;串行 进位方式是将全加器级联构成多位加法器。

并行进位加法器通常比串行级联加法器占用更多的资源。 随着位数的增加,相同位数的并行加法器与串行加法器的资 源占用差距也越来越大。因此,在工程中使用加法器时,要 在速度和容量之间寻找平衡点。

//4位二进制并行加法器adder4b.v module adder4b(a4, b4, c4, s4, co4); input [3:0] a4, b4; input c4; output [3:0] s4; output co4; assign {co4, s4} = a4 + b4 + c4; endmodule

2) 8位二进制加法器的源程序adder8b.v

//8位二进制并行加法器adder8b.v module adder8b(a8, b8, c8, s8, co8); input [7:0] a8, b8; input c8; output [7:0] s8; output co8; wire sc; adder4b u1(.a4(a8[3:0]), .b4(b8[3:0]), .c4(c8), .s4(s8[3:0]), .co4(sc)); adder4b u2(.a4(a8[7:4]), .b4(b8[7:4]), .c4(sc), .s4(s8[7:4]), .co4(co8)); endmodule

图6.2 adder4b的时序仿真结果

图6.3 adder8b的时序仿真结果

4.逻辑综合分析 图6.4是使用Quartus Ⅱ 8.0进行逻辑综合后adder8b的 RTL视图,图6.5是对adder8b的RTL视图中的adder4b进行展 开后的视图。图6.6是使用Quartus Ⅱ 8.0对adder8b进行逻辑 综合后的资源使用情况。

《EDA技术与Verilog HDL》PPT第3版 第6章 LPM宏模块用法

6.3 LPM_RAM宏模块用法

6.3.3 测试LPM_RAM

图6-19 图6-18的RAM仿真波形

6.3 LPM_RAM宏模块用法

6.3.4 Verilog代码描述的存储器初始化文件加载表述

6.3 LPM_RAM宏模块用法

6.3.5 存储器设计的结构控制

图6-20 例6-6的RTL电路模块图

6.6.1 建立嵌入式锁相环元件

图6-35 输出第二个时钟信号c1

6.6 LPM嵌入式锁相环调用

6.6.1 建立嵌入式锁相环元件

图6-36 采用了嵌入式锁相环作时钟的正弦信号发生器电路

6.6.2 测试锁相环

6.7 In-System Sources and Probes Editor用法

(1)在顶层设计中嵌入In-System Sources and Probes模块。 (2)设定参数。

图6-37 为In-System Sources and Probes模块设置参数

6.7 In-System Sources and Probes Editor用法

(3)与需要测试的电路系统连接好。

图6-38 在电路中加入In-System Sources and Probes测试模块

6.7 In-System Sources and Probes Editor用法

6.3.2 以原理图方式对LPM_RAM进行调用

图6-13 调用单口LPM RAM

6.3 LPM_RAM宏模块用法

6.3.2 以原理图方式对LPM_RAM进行调用

图6-14 设定RAM参数

6.3 LPM_RAM宏模块用法

6.3.2 以原理图方式对LPM_RAM进行调用

图6-15 设定RAM仅输入时钟控制

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第7章 EDA技术实验

2. 实验内容 设计并调试好一个计时范围为0.01 s~1 h的数字秒表, 用GW48-CK或其他EDA实验开发系统(事先应选定拟采用的 实验芯片的型号)进行硬件验证。

第7章 EDA技术实验

3. 实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个Verilog HDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

第7章 EDA技术实验

(2) 当交通灯处于无人自动控制工作状态时,若方向1绿 灯亮,则方向2红灯亮。计数55 s后,方向1的绿灯熄灭、黄 灯亮,再计数5 s后,方向1的黄灯熄灭、红灯亮,同时方向 2的绿灯亮,然后方向2重复方向1的过程,这样就实现了无 人自动控制交通灯。有关控制的定时使用倒计时方式,计时 过程用数码管进行显示。

第7章 EDA技术实验

3.实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个Verilog HDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

第7章 EDA技术实验

7.1 实验一:计数器电路的设计

1.实验目的 (1) 学习Quartus Ⅱ/ISE Design Suite/ispLEVER软件的基 本使用方法。 (2) 学习GW48-CK或其他EDA实验开发系统的基本使用 方法。 (3) 熟悉Verilog HDL程序的基本结构和元件实例化语句 的使用。

第7章 EDA技术实验

第7章 EDA技术实验

7.1 实验一:计数器电路的设计 7.2 实验二:算术运算电路的设计 7.3 实验三:可调信号发生器的设计 7.4 实验四:数字频率计的设计 7.5 实验五:数字秒表的设计 7.6 实验六:交通灯信号控制器的设计 7.7 实验七:FIR滤波器的设计 7.8 实验八:CORDIC算法的应用设计 7.9 实验报告范例

第7章 EDA技术实验

2.实验内容 设计一个可调信号发生器,可产生正弦波、方波、三角 波和锯齿波四种信号,能够实现信号的转换,并具有频率可 调的功能。 用GW48-CK或其他EDA实验开发系统(事先应选定拟采 用的实验芯片的型号)进行硬件验证。

第7章 EDA技术实验

3.实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个Verilog HDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

第7章 EDA技术实验

2. 实验内容 设计并调试好8位十进制数字频率计,用GW48-CK或其 他EDA实验开发系统(事先应选定拟采用的实验芯片的型号) 进行硬件验证。

第7章 EDA技术实验

3.实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个Verilog HDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

G(Z) = 124 214Z1 57Z2 33Z3

256 256 256 256

这时需注意:变换后的结果要除以256才是实际的输出。 用GW48-CK或其他EDA实验开发系统(事先应选定拟采用的 实验芯片的型号)进行硬件验证。

第7章 EDA技术实验

3. 实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个Verilog HDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

第7章 EDA技术实验

4. 参考资料 第4.3节、第4.4节、第4.5节、第5.1节、第5.2节和第6.7 节。信号控制器的设计

1. 实验目的 (1) 熟悉Quartus Ⅱ/ISE Design Suite/ispLEVER软件的基本 使用方法。 (2) 熟悉GW48-CK或其他EDA实验开发系统的基本使用方 法。 (3) 学习和掌握Verilog HDL过程区块语句、if条件语句、 case选择语句、for循环语句和元件实例化语句等的综合使用。 (4) 学习计数器、分频器、选择器等Verilog HDL基本逻辑 电路、动态扫描显示电路和状态机控制电路的综合设计应用。

第7章 EDA技术实验

4.参考资料 第4.3节、第4.4节、第4.5节、第5.1节、第5.2节和第6.6 节。

第7章 EDA技术实验

7.5 实验五:数字秒表的设计

1. 实验目的 (1) 熟悉Quartus Ⅱ/ISE Design Suite/ispLEVER软件的基 本使用方法。 (2) 熟悉GW48-CK或其他EDA实验开发系统的基本使用 方法。 (3) 学习和掌握Verilog HDL过程区块语句、if条件语句 和元件实例化语句等的综合使用。 (4) 熟悉计数器、分频器等Verilog HDL基本逻辑电路的 综合设计应用,掌握程序仿真时根据实际情况进行有关参数 调整的方法。

第7章 EDA技术实验

2. 实验内容 设计并调试好一个十字交叉路口的交通灯信号控制器, 具体要求为: (1) 为了控制的方便,设置了两个开关SW1和SW2,其 中固定开关SW1实现交通警察人为监督交通秩序和无人自动 控制交通秩序之间的切换,默认开关置于高电平端,为自动 控制模式——交通灯按照事先的规定工作,开关置于低电平 端时,为人为监督控制模式(交通灯不再工作)。点动开关 SW2用于整个系统的总复位,如系统出现故障时,就需要总 复位。

第7章 EDA技术实验

2. 实验内容 根据第6.10节图6.35所示的转置FIR滤波器的原理,完 成一个滤波器长度为4的Daubechies DB4转置FIR滤波器的设 计。该滤波器的系数为 G(Z)=0.48301+0.8365Z-1+0.2241Z-2-0.1294Z-3 若将系数设为8位(加上符号位)精度模式,则

第7章 EDA技术实验

2.实验内容 进行加法器、乘法器与除法器等算术运算电路的设计与 调试:① 设计并调试好一个由两个4位二进制并行加法器级 联而成的8位二进制并行加法器;② 设计并调试一个8位的 移位乘法器/定点乘法器/布斯乘法器;③ 设计并调试一个8 位的移位除法器/重存除法器/非重存除法器。并用GW48-CK 或其他EDA实验开发系统(事先应选定拟采用的实验芯片的 型号)进行硬件验证。

第7章 EDA技术实验

4. 参考资料 第4.3节、第4.4节、第4.5节、第5.1节、第5.2节和第6.4 节。

第7章 EDA技术实验

7.4 实验四:数字频率计的设计

1.实验目的 (1) 熟悉Quartus Ⅱ/ISE Design Suite/ispLEVER软件的基 本使用方法。 (2) 熟悉GW48-CK或其他EDA实验开发系统的基本使用 方法。 (3) 学习和掌握Verilog HDL过程区块语句、if条件语句、 连续赋值语句和元件实例化语句等的综合使用。 (4) 学习计数器、寄存器等Verilog HDL基本逻辑电路的 综合设计应用。

第7章 EDA技术实验

4. 参考资料 第4.3节、第4.4节、第4.5节、第5.1节、第5.2节和第6.8 节。

第7章 EDA技术实验

7.7 实验七:FIR滤波器的设计

1. 实验目的 (1) 熟悉Quartus Ⅱ/ISE Design Suite/ispLEVER软件的基本 使用方法。 (2) 掌握GW48-CK或其他EDA实验开发系统的基本使用 方法。 (3) 学习Verilog HDL程序设计中LPM兆功能块的程序调 用及参数传递方法。 (4) 学习数字信号处理算法的分析、设计、编程与调试方 法,包括参数的量化、数据的延迟、流水线的使用、仿真数 据的输入、仿真结果的分析等。

用GW48-CK或其他EDA实验开发系统(事先应选定拟采 用的实验芯片的型号)进行硬件验证。

第7章 EDA技术实验

3. 实验要求 (1) 画出系统的原理框图,说明系统中各主要组成部分 的功能。 (2) 编写各个Verilog HDL源程序。 (3) 根据系统的功能,选好测试用例,画出测试输入信 号波形或编好测试程序。 (4) 根据选用的EDA实验开发装置编好用于硬件验证的 管脚锁定表格或文件。 (5) 记录系统仿真、逻辑综合及硬件验证结果。 (6) 记录实验过程中出现的问题及解决办法。

第7章 EDA技术实验

4.参考资料 第4.3节、第4.4节、第4.5节、第5.1节、第5.2节和第 6.1~6.3节。

第7章 EDA技术实验

7.3 实验三:可调信号发生器的设计

1.实验目的 (1) 熟悉Quartus Ⅱ/ISE Design Suite/ispLEVER软件的基本 使用方法。 (2) 熟悉GW48-CK或其他EDA实验开发系统的基本使用 方法。 (3) 学习和掌握Verilog HDL过程区块语句、case选择语句、 if条件语句和元件实例化语句等的综合使用。 (4) 学习LPM兆功能只读存储块ROM的使用及存储器模 块的初始化方法。 (5) 学习使用Quartus Ⅱ 8.0中的SignalTap Ⅱ嵌入式逻辑分 析仪的使用。