超大规模集成电路CAD

集成电路CADPPT课件.ppt

算法描述、系统描述 物理域:掩膜单元,标准单元,宏单元,模

块,芯片

集成电路设计

集成电路设计中典型的Y型图 设计域:电路级,逻辑级,寄存器传输级,

算法级,系统级

半定制设计方法

全定制设计方法

(1)电路设计人员首先进行功能设计,得到设 计思路

按电路功能来分 模拟、数字、数模混合

按电路结构 半导体集成电路 混合集成电路(薄膜IC,厚膜IC等)

按器件结构分类 双极型集成电路 MOS集成电路(NMOS,PMOS,CMOS)

IC分类

ቤተ መጻሕፍቲ ባይዱ 按集成电路规模分类 SSI MSI LSI VLSI ULSI GSI

在Cadence软件中手工绘制集成电路版图

LVS是指从版图中提取出网表,与逻辑/电路设 计得到的网表进行比较,检查两者是否一致。

然后,进行后仿真(post simulation)

全定制设计方法

后仿真 将版图中的参数提取出来后,再进行模拟仿真,

与前仿真对比。

全定制设计方法

(4)集成电路的加工制造 将设计好的版图,通过工艺加工,形成集成电

操作 知识(☆) 理论

思维方式

微电子、电子科学与技术、计算机科学与技术、 通讯、自动控制专业

第三次技术革命 最具有新技术革命代表性的是以微电子技术为 核心的电子信息技术。 计算机、通讯的基础是微电子

微电子技术发展的理论基础是19世纪末到20 世纪30年代期间建立起来的现代物理学

微电子学的特点

微电子学是一门综合性很强的边缘学科,其中 包括了半导体器件物理、集成电路工艺和集成 电路及系统设计、测试等多方面的内容;涉及 了固体物理学、量子力学、热力学与统计物理 学、材料科学、电子线路、信号处理、计算机 辅助设计、测试与加工、图论、化学等多个领 域。

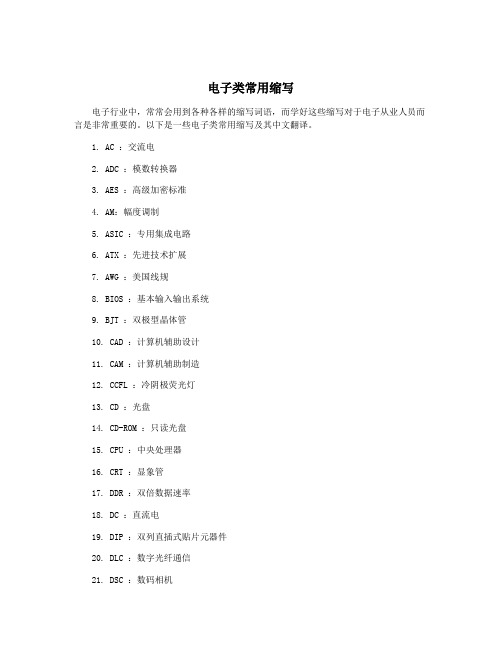

电子类常用缩写

电子类常用缩写电子行业中,常常会用到各种各样的缩写词语,而学好这些缩写对于电子从业人员而言是非常重要的。

以下是一些电子类常用缩写及其中文翻译。

1. AC :交流电2. ADC :模数转换器3. AES :高级加密标准4. AM:幅度调制5. ASIC :专用集成电路6. ATX :先进技术扩展7. AWG :美国线规8. BIOS :基本输入输出系统9. BJT :双极型晶体管10. CAD :计算机辅助设计11. CAM :计算机辅助制造12. CCFL :冷阴极荧光灯13. CD :光盘14. CD-ROM :只读光盘15. CPU :中央处理器16. CRT :显象管17. DDR :双倍数据速率18. DC :直流电19. DIP :双列直插式贴片元器件20. DLC :数字光纤通信21. DSC :数码相机22. DSP :数字信号处理器23. DVD :数码视频光盘24. EEPROM :电可擦可编程只读存储器25. ESD :电静电放电26. FET :场效应晶体管27. FIR :有限脉冲响应28. FM :频率调制29. FPGA :现场可编程门阵列30. FSK :频移键控31. FT :离散傅里叶变换32. GBIC :千兆位接口转换器33. GPS :全球卫星定位系统34. GUI :图形用户界面35. HDMI :高清晰度多媒体接口36. IC :集成电路37. IDE :集成开发环境38. IGBT :绝缘栅双极性晶体管39. IP :互联网协议40. ISP :互联网服务提供商41. LCD :液晶显示器42. LED :发光二极管43. LGA :Land Grid Array44. MAGI:微型MCU应用接口45. MCU :单片机46. MDR :主板数据率47. MEMS:微机电系统48. MIMO :多输入多输出49. MOS :金属氧化物半导体50. MPEG :动态图像压缩标准51. MSI :中小规模集成电路52. NAS :网络附加存储器53. NIC :网络接口卡54. OLED :有机发光二极管55. P2P :端对端56. PCI :外设连接总线57. PCMCIA :个人计算机内置扩展卡58. PWM :脉冲宽度调制59. RAM :随机存取存储器60. RISC :精简指令集计算机61. ROM :只读存储器62. RS-232 :串行接口协议63. SATA :串行高级技术附件64. SCSI :小型计算机系统接口65. SDRAM :同步动态随机存取存储器66. SIM :智能卡67. SMT :表面贴装技术68. SOC :系统级芯片69. SPDIF :数字音频接口格式70. SRAM :静态随机存取存储器71. TCP/IP :传输控制协议/互联网协议72. TDR :时域反射73. TTL :晶体管—晶体管逻辑74. UMTS :通用移动通信系统75. USB :通用串行总线76. VCD :视频光盘77. VGA :视频图形阵列78. VHDL :可综合硬件描述语言79. VLSI :超大规模集成电路80. VoIP :互联网语音电话81. WLAN :无线局域网82. XML :可扩展标记语言总结电子行业中缩写非常多,掌握这些缩写可以让从业人员更加便捷地进行工作和交流。

超大规模集成电路CAD 第一章 VLSI设计的概述教材

差))

1952 年,英国皇家雷达研究所的达默第一次提出“集成电 路”的设想; 1958年美国德克萨斯仪器公司基尔比为首的小组研制出世 界上第一块集成电路了双极性晶体管(由12个器件组成的 相移振荡和触发器集成电路),并于1959年公布—这就是 世界上最早的集成电路,是现代集成电路的雏形或先驱 ; (基尔比于2000年获得诺贝尔物理学奖) 1960年成功制造出MOS管集成电路; 1965年戈登· 摩尔发表预测未来集成电路发展趋势的文章, 就是“摩尔定律”的前身; 1968年Intel公司诞生。

2019/4/12 4

第1章 VLSI概述

集成电路的发展除了物理原理外还得益于许多新工艺的 发明:

50年美国人奥尔和肖克莱发明的离子注入工艺; 56年美国人富勒发明的扩散工艺; 60年卢尔和克里斯坦森发明的外延生长工艺; 60年kang和Atalla研制出第一个硅MOS管; 70年斯皮勒和卡斯特兰尼发明的光刻工艺,使晶体管从点接触 结构向平面结构过渡并给集成电路工艺提供了基本的技术支持。 因此,从70年代开始,第一代集成电路才开始发展并迅速成熟。

图1 – 1 “点接晶体管放大器” 2019/4/12 3

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

第1章 VLSI概述

1948年,威廉· 肖克莱(William Shockley)—“晶体管之 父” ,提出结型晶体管的想法; 1951年,威廉· 肖克莱领导的研究小组成功研制出第一个可 靠的单晶锗NPN结型晶体管;(温度特性差、提纯度差、表面防护能力差(稳定性

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

集成电路设计的CAD系统

高性能集成电路设计案例中,CAD系统发挥了关键作用。首先,CAD系统提供了多种电路结构供设计师选择和测试,以便找到最优设计方案。其次,通过使用CAD系统的模拟功能,设计师可以在实际制造之前预测电路的性能和行为。此外,CAD系统还提供了强大的布局和布线工具,帮助设计师高效地实现电路设计。这些工具可以根据设计规则对电路布局进行优化,并自动完成布线过程,从而大大提高了设计效率。

低功耗集成电路设计案例强调了CAD系统在降低芯片功耗和提高能效方面的应用价值。通过优化电路结构和元件参数,以及使用功耗分析和优化工具,设计师能够实现低功耗设计目标。这对于便携式电子设备的发展具有重要意义。

在低功耗集成电路设计案例中,CAD系统同样发挥了关键作用。首先,CAD系统提供了多种电路结构和元件参数供设计师选择和优化,以便降低芯片功耗和提高能效。其次,通过使用CAD系统的功耗分析功能,设计师可以精确地测量和分析电路的功耗行为。此外,CAD系统还提供了功耗优化工具,帮助设计师进一步降低功耗和提高能效。这些工具可以帮助设计师优化电路结构和元件参数,以满足低功耗设计的要求。

详细描述

总结词

详细描述

基于人工智能的cad系统利用机器学习和人工智能技术来自动化电路设计过程。

基于人工智能的cad系统是当前研究的热点领域,具有广阔的应用前景和发展潜力。

基于人工智能的cad系统适用于各种类型的集成电路设计,包括数字、模拟和混合信号电路。

基于人工智能的cad系统

04

集成电路设计的cad系统技术

布线算法

布线算法能够根据电路结构和元件之间的连接关系,自动规划出合理的布线路径。

优化目标

布局与布线技术的目标是实现电路性能、功耗和可靠性的最优化。

布局与布线技术

高级教程1

高级教程1.1习题查漏补缺本次测验目的在于帮助你找出还没掌握的知识点,请勿为了分数或者正确率自欺欺人。

完成测验后,请及时将还没掌握的知识点在书中重点标出。

1.1946年,世界上第一台数字式电子计算机诞生于美国(),命名为“电子数值积分器和计算机”,简称ENIAC。

[单选题] *加利福尼亚大学宾夕法尼亚大学(正确答案)麻省理工学院斯坦福大学2.第三代电子计算机采用的主要电子元器件是()。

[单选题] *电子管晶体管中、小规模集成电路(正确答案)大规模、超大规模集成电路3.我们目前所使用计算机采用的主要元器件是()。

[单选题] *电子管晶体管中、小规模集成电路大规模、超大规模集成电路(正确答案)4.第()代电子计算机主要用于科学计算。

[单选题] *一(正确答案)二三四5.第()代电子计算机除了计算机科学计算外,还被用于数据处理、事务处理以及工业控制等方面。

[单选题] *一二(正确答案)三四6.第()代电子计算机高级程序设计语言有了很大的发展。

计算机同时向标准化、多样化、通用化、机型系统化发展。

[单选题] *一二三(正确答案)四7.第()代电子计算机在系统结构方面发展了并行处理技术、分布式计算机系统和计算机网络等。

[单选题] *一二三四(正确答案)8.第()代电子计算机软件处于初始阶段,程序设计使用机器语言和汇编语言。

[单选题] *一(正确答案)二三四9.第( )代电子计算机软件也有了较大的发展,出现了FORTRAN、COBOL和ALGOL等高级语言。

[单选题] *一二(正确答案)三四10.第( )代电子计算机软件方面操作系统逐步完善,使得计算机在中心程序的控制协调下可以同时运行许多不同的程序。

[单选题] *一二三(正确答案)四11.第()代电子计算机软件方面发展了数据库系统、软件工程标准化系统等,应用软件已成为现代工业的一部分。

[单选题] *一二三四(正确答案)12.我们现在使用的电脑就属于第( )代电子计算机。

eda是什么

电子设计自动化(英语:Electronic design automation,缩写:EDA)是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

在电子设计自动化出现之前,设计人员必须手工完成集成电路的设计、布线等工作,这是因为当时所谓集成电路的复杂程度远不及现在。

工业界开始使用几何学方法来制造用于电路光绘的胶带。

到了1970年代中期,开发人应尝试将整个设计过程自动化,而不仅仅满足于自动完成掩膜草图。

第一个电路布局、布线工具研发成功。

设计自动化研讨会在这一时期被创立,旨在促进电子设计自动化的发展。

电子设计自动化发展的下一个重要阶段以卡弗尔·米德和琳·康维于1980年发表的论文《超大规模集成电路系统导论》为标志。

这一篇具有重大意义的论文提出了通过编程语言来进行芯片设计的新思想。

如果这一想法得到实现,芯片设计的复杂程度可以得到显著提升。

这主要得益于用来进行集成电路逻辑仿真、功能验证的工具的性能得到相当的改善。

随着计算机仿真技术的发展,设计项目可以在构建实际硬件电路之前进行仿真,芯片布局、布线对人工设计的要求降低,而且软件错误率不断降低。

直至今日,尽管所用的语言和工具仍然不断在发展,但是通过编程语言来设计、验证电路预期行为,利用工具软件综合得到低抽象级(或称“后端”)物理设计的这种途径,仍然是数字集成电路设计的基础。

从1981年开始,电子设计自动化逐渐开始商业化。

1984年的设计自动化会议上还举办了第一个以电子设计自动化为主题的销售展览。

Gateway设计自动化在1986年推出了一种硬件描述语言Verilog,这种语言在现在是最流行的高级抽象设计语言。

1987年,在美国国防部的资助下,另一种硬件描述语言VHDL被创造出来。

现代的电子设计自动化设计工具可以识别、读取不同类型的硬件描述。

集成电路设计的CAD系统的讲解

u2: half_adder PORT MAP (c_in,b,sum,c);

u3: or_gate PORT MAP (c, a, c_out);

End structural_view;

Configuration parts of full_adder IS For structural_view For u1,u2 : half_adder

延迟描述:反映时序,建立精确的电路硬件模型

什么是延迟? 传输延迟 惯性延迟:输入信号在指定延迟时间内保持不变,

元件的输出端才有响应。

进程为行为的基本单元 信号作为系统进程之间的数据通路

各进程并行执行

VHDL语言的建模机制 ——结构描述

结构描述:若干部件用信号线互连形成一个实体 部件:对某元件的调用(例元)

O1: out_ std_logic );

end component;

begin

U1: XOR port map(A,B,SUM); 元件引用,生成例元 (标号:元件名

端口映射)

U2: AND2 port map(A,B,CO);

end behavioral;

VHDL语言的建模机制 ——行为描述

电子实体中的 行为:反映信号的变化、组合和传播 行为的特点是信号的延迟和并行性

--设计实体count

GENERIC (tpd : Time:=10ns);

PORT(clock : IN Bit; q1,q0: OUT Bit); END ENTITY count;

ARCHITECTURE arch of count IS

-- count实体的结构体

BEGIN count_up : PROCESS(clock)

集成电路CAD

集成电路CAD1. 概述集成电路(Circuit of Integration,简称IC)是指将多个电子器件集成在一个芯片上的电路系统。

而集成电路CAD(Computer-Aided Design,简称CAD)是指通过计算机辅助设计的方法和工具,对集成电路进行设计和制造的过程。

本文将从CAD的背景、CAD的分类和应用以及CAD的发展趋势三个方面对集成电路CAD进行详细介绍。

2. CAD的背景随着信息技术的快速发展,计算机辅助设计(CAD)技术在各个领域的应用不断扩大。

在集成电路领域,CAD技术的出现极大地提高了设计的效率和准确性。

通过CAD技术,设计人员可以在计算机上进行电路的建模、仿真和验证,减少了实际物理实验的成本和时间,提高了设计的成功率。

3. CAD的分类和应用3.1 电路级CAD在集成电路CAD中,最基础的是电路级CAD。

它主要用于电路的建模和仿真,根据设计人员的需求进行电路拓扑结构和电路元件的选择和布局。

通过电路级CAD,设计人员可以通过仿真分析来验证设计的正确性,从而指导后续的制造和调试工作。

3.2 物理级CAD物理级CAD在集成电路CAD中扮演着重要的角色。

它主要用于IC设计的版图布局和电路布线。

通过物理级CAD,设计人员可以对集成电路的布线进行优化,提高信号传输的速度和稳定性。

此外,物理级CAD也可以进行光罩的设计和制作,用于制造工艺的控制。

3.3 系统级CAD此外,在集成电路CAD中还存在着系统级CAD的应用。

系统级CAD主要用于对整个系统进行建模和仿真,包括电路、器件和模块等。

通过系统级CAD,设计人员可以对整个系统的性能进行评估和调整,从而优化系统的设计和布局。

系统级CAD的应用在复杂的集成电路系统中尤为重要。

4. CAD的发展趋势随着科技的不断进步,集成电路CAD也在不断发展。

以下是几个集成电路CAD发展的趋势:4.1 三维设计随着集成电路的不断密集和复杂化,传统的二维设计已经无法满足需求。

集成电路的现状及其发展趋势

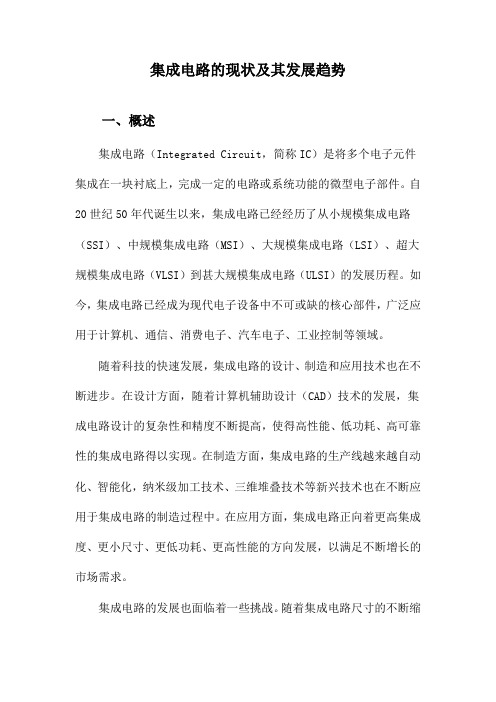

集成电路的现状及其发展趋势一、概述集成电路(Integrated Circuit,简称IC)是将多个电子元件集成在一块衬底上,完成一定的电路或系统功能的微型电子部件。

自20世纪50年代诞生以来,集成电路已经经历了从小规模集成电路(SSI)、中规模集成电路(MSI)、大规模集成电路(LSI)、超大规模集成电路(VLSI)到甚大规模集成电路(ULSI)的发展历程。

如今,集成电路已经成为现代电子设备中不可或缺的核心部件,广泛应用于计算机、通信、消费电子、汽车电子、工业控制等领域。

随着科技的快速发展,集成电路的设计、制造和应用技术也在不断进步。

在设计方面,随着计算机辅助设计(CAD)技术的发展,集成电路设计的复杂性和精度不断提高,使得高性能、低功耗、高可靠性的集成电路得以实现。

在制造方面,集成电路的生产线越来越自动化、智能化,纳米级加工技术、三维堆叠技术等新兴技术也在不断应用于集成电路的制造过程中。

在应用方面,集成电路正向着更高集成度、更小尺寸、更低功耗、更高性能的方向发展,以满足不断增长的市场需求。

集成电路的发展也面临着一些挑战。

随着集成电路尺寸的不断缩小,传统的制造方法已经接近物理极限,这使得集成电路的进一步发展变得更为困难。

同时,随着全球经济的不断发展和市场竞争的加剧,集成电路产业也面临着巨大的竞争压力。

探索新的制造技术、开发新的应用领域、提高产业竞争力成为集成电路产业未来的重要发展方向。

总体来说,集成电路作为现代电子技术的核心,其发展现状和趋势直接影响着整个电子产业的发展。

未来,随着技术的不断进步和市场的不断变化,集成电路产业将继续保持快速发展的势头,为全球经济和社会的发展做出更大的贡献。

1. 集成电路的定义与重要性集成电路(Integrated Circuit,简称IC)是一种微型电子器件或部件,采用一定的工艺,把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构。

集成电路CAD综合设计与验证

实验四十四集成电路CAD综合设计与验证实验名称:集成电路CAD综合设计与验证实验项目性质:综合训练所属课程名称:VHDL与集成电路CAD实验计划学时:6学时一、设计目的1.熟练掌握MAX+PLUSⅡ的使用;2.学习VHDL硬件描述语言描述电路的原理;3.学会使用VHDL进行大规模集成电路设计;4.学习用CPLD/FPGA实验系统硬件验证电路设计的正确性。

二.预习与参考1.VHDL相关教程;2.电子技术基础;3.CPLD/FPGA实验开发系统实验指导书。

三.设计要求1.用VHDL进行大规模集成电路设计;2.层次化设计;3.分模块设计,有子程序的调用。

四.设计内容及步骤1.以自己学号的后两位数字(00~09则加上100)为模的计数器或自选大规模集成器件或控制电路,如数字钟、数字频率计、数字电压表、多位乘法器等,进行功能分析与设计;2.建立VHDL模型;3.在MAX+PLUSⅡ软件平台上进行VHDL编辑,编译,综合,仿真,定时分析,适配、配置;4.在CPLD/FPGA实验系统上下载,进行硬件验证电路设计的正确性;5.写出设计报告。

五.设计所用仪器设备和材料清单PC机,MAX+PLUSⅡ软件,KHF-3型CPLD/FPGA实验开发系统,打印机,墨盒,打印纸。

六.考核型式书面报告和通过硬件验证情况相结合。

七.报告内容1.设计目的;2.设计要求;3.所选择的设计器件或电路的功能要求与分析;4.设计思路,设计方案分析与确定;5.VHDL源程序;6.在MAX+PLUSⅡ软件平台上进行VHDL编辑、编译、综合、仿真、定时分析、适配和配置的情况;7.在CPLD/FPGA实验系统上下载,进行硬件验证情况;8.总结设计收获与体会。

八.思考题1.有哪些VHDL设计平台?2.用VHDL进行集成电路设计有哪些优势?3.在VHDL设计中,分模块、层次化设计有什么好处?4.如何进行自顶向下的系统设计?5.CPLD/FPGA 有什么优势?附:KHF-3型CPLD/FPGA实验开发系统资料1.所用芯片:ACEX1K系列的EP1K30QC208-3,引脚为208个,集成度为3万门。

器件名词翻译

abrupt junction:突变结;Accumulation :积累Aging:老化alignment:校准Anneal:退火avalanche breakdown:雪崩击穿back-gate:背栅ballistic transport:弹道输运;body Effect:体效应,衬底偏置效应,衬偏效应Bonding:键合breakdown:击穿Buried channels:埋沟cat’s whisker detector:触须式检波器channel length modulation:沟道长度调制;chip: 芯片computer-aided design (CAD):计算机辅助设计CVD (chemical vapor deposition) :化学气相淀积Dangling bond: 悬挂键dangling silicon bond :悬挂键;deep submicrometer:深亚微米;degradation:退化;Degrade:退化dehydration:脱水Depletion-mode:耗尽型器件deposited uniformly:均匀淀积deposited uniformly:均匀淀积;development:显影DIBL (drain-induced barrier lowering):漏至势垒降低效应;die: 裸片dielectric constant:介电常数dielectric constant:介电常数;Dielectric:电介质Diffusion:扩散DMOS (double-diffused MOS) :双扩散MOSdopant:掺杂剂doping fluctuations:掺杂工艺的波动Drain:漏(区)Electrode:电极Electron affinity :电子亲和能electron beam lithographic:电子束光刻Energy-bands:能带图Enhancement-mode:增强型EOT(equivalent oxide thickness):等效氧化层厚度;epitaxial:外延;epitaxially grown 外延生长;etch stencil :刻蚀模板etch:刻蚀Field oxide :场氧化层Field oxide:场氧化层Flat-Band V oltage :平带电压Flat-Band V oltage 平带电压floating body:体区浮置gate dielectric:栅介质gate stack:栅叠层GIDL (gate-induced drain leakage):栅感应漏电效应;gradual-channel approximation:渐近沟道近似Hot Carriers Effect:热载流子效应hot-carrier effects: 热载流子效应;impact ionization:碰撞电离;induced electric field:感生电场Interconnection:互联interface state:表面态;-1interface states:界面态intrinsic Fermi level:本征费米能级inversion layer:反型层Ion Implantation:离子注入kinetic energy:动能;latch-up :闩锁;latch-up:闩锁lattice vibration:晶格振动;LDD(lightly doped drain):轻掺杂漏;leakage current:泄漏电流lithographic mask:光刻版;LOCOS(Local Oxidation of Silicon):硅的局部氧化Mask:掩模Metallization:金属化Metallurgical junction:冶金结momentum:动量;MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor):场效应晶体管nano-scale:纳米级;nonvolatile devices:非挥发性器件nonvolatile devices:非挥发性器件oxidation furnace :氧化炉Oxidation:氧化oxide charges:氧化层电荷Pattern: 样式,图形,集成电路设计中指版图phonons:声子;photolithography:光刻Photomasks:光学掩模photoresist strip:剥离光刻胶Photoresist:光刻胶,光致抗蚀剂Pinched-off :夹断planar technology:平面工艺plasma etch :等离子刻蚀Plasma:等离子Polysilicon:多晶硅Process :工艺(过程)punch-through : 穿通PVD (physical vapor deposition):金属物理气相淀积quantum confinement effect:量子限制效应;retrograde channel doping profile:retrograde channel doping profile:具有逆向(峰值不在表面处的)沟道掺杂分布salicide:自对准金属硅化物工艺scaling limit:按比例缩小的极限self-aligned:自对准SEM:扫瞄式电子显微镜(scanning electron microscope)series resistance:串联电阻sheet-resistance:薄层电阻,方块电阻short-channel effects:短沟道效应;short-channel effects:短沟效应silicide:金属硅化物SIMOX (separation by implantation of oxygen):注氧隔离single-crystal ingot:单晶锭single-crystalline silicon:单晶硅;SOI ( Silicon On Insulator):绝缘层上的硅Source:源(区)space charge region:空间电荷区Spacer:侧墙Specification : 规格,规范Sputtering:溅射stepper : 专用步进曝光机Substrate :衬底Subthreshold :亚阈值subthreshold swing:亚阈摆幅subthreshold swing:亚阈值摆动;-2Surface scattering :表面散射Technology :技术,工艺thermal equilibrium:热平衡thermal oxidation process:热氧化工艺Threshold voltage:阈值电压tunnel:遂穿ULSI:甚大规模集成电路ultraviolet light: 紫外光Vacuum level :真空能级vertical furnace :井式炉VLSI:超大规模集成电路V olume charge:体电荷wafer:晶片Work function :功函数abrupt junction:突变结;Accumulation :积累Aging:老化alignment:校准Anneal:退火avalanche breakdown:雪崩击穿back-gate:背栅ballistic transport:弹道输运;body Effect:体效应,衬底偏置效应,衬偏效应Bonding:键合breakdown:击穿Buried channels:埋沟cat’s whisker detector:触须式检波器channel length modulation:沟道长度调制;chip: 芯片computer-aided design (CAD):计算机辅助设计CVD (chemical vapor deposition) :化学气相淀积Dangling bond: 悬挂键dangling silicon bond :悬挂键;deep submicrometer:深亚微米;degradation:退化;Degrade:退化dehydration:脱水Depletion-mode:耗尽型器件deposited uniformly:均匀淀积deposited uniformly:均匀淀积;development:显影DIBL (drain-induced barrier lowering):漏至势垒降低效应;die: 裸片dielectric constant:介电常数dielectric constant:介电常数;Dielectric:电介质Diffusion:扩散DMOS (double-diffused MOS) :双扩散MOSdopant:掺杂剂doping fluctuations:掺杂工艺的波动Drain:漏(区)Electrode:电极Electron affinity :电子亲和能electron beam lithographic:电子束光刻Energy-bands:能带图Enhancement-mode:增强型EOT(equivalent oxide thickness):等效氧化层厚度;epitaxial:外延;epitaxially grown 外延生长;etch stencil :刻蚀模板etch:刻蚀Field oxide :场氧化层Field oxide:场氧化层-3Flat-Band Voltage :平带电压Flat-Band Voltage 平带电压floating body:体区浮置gate dielectric:栅介质gate stack:栅叠层GIDL (gate-induced drain leakage):栅感应漏电效应;gradual-channel approximation:渐近沟道近似Hot Carriers Effect:热载流子效应hot-carrier effects: 热载流子效应;impact ionization:碰撞电离;induced electric field:感生电场Interconnection:互联interface state:表面态;interface states:界面态intrinsic Fermi level:本征费米能级inversion layer:反型层Ion Implantation:离子注入kinetic energy:动能;latch-up :闩锁;latch-up:闩锁lattice vibration:晶格振动;LDD(lightly doped drain):轻掺杂漏;leakage current:泄漏电流lithographic mask:光刻版;LOCOS(Local Oxidation of Silicon):硅的局部氧化Mask:掩模Metallization:金属化Metallurgical junction:冶金结momentum:动量;MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor):场效应晶体管nano-scale:纳米级;nonvolatile devices:非挥发性器件nonvolatile devices:非挥发性器件oxidation furnace :氧化炉Oxidation:氧化oxide charges:氧化层电荷Pattern: 样式,图形,集成电路设计中指版图phonons:声子;photolithography:光刻Photomasks:光学掩模photoresist strip:剥离光刻胶Photoresist:光刻胶,光致抗蚀剂Pinched-off :夹断planar technology:平面工艺plasma etch :等离子刻蚀Plasma:等离子Polysilicon:多晶硅Process :工艺(过程)punch-through : 穿通PVD (physical vapor deposition):金属物理气相淀积quantum confinement effect:量子限制效应;retrograde channel doping profile:retrograde channel doping profile:具有逆向(峰值不在表面处的)沟道掺杂分布salicide:自对准金属硅化物工艺scaling limit:按比例缩小的极限self-aligned:自对准SEM:扫瞄式电子显微镜(scanning electron microscope)series resistance:串联电阻sheet-resistance:薄层电阻,方块电阻short-channel effects:短沟道效应;short-channel effects:短沟效应silicide:金属硅化物-4SIMOX (separation by implantation of oxygen):注氧隔离single-crystal ingot:单晶锭single-crystalline silicon:单晶硅;SOI ( Silicon On Insulator):绝缘层上的硅Source:源(区)space charge region:空间电荷区Spacer:侧墙Specification : 规格,规范Sputtering:溅射stepper : 专用步进曝光机Substrate :衬底Subthreshold :亚阈值subthreshold swing:亚阈摆幅subthreshold swing:亚阈值摆动;Surface scattering :表面散射Technology :技术,工艺thermal equilibrium:热平衡thermal oxidation process:热氧化工艺Threshold voltage:阈值电压tunnel:遂穿ULSI:甚大规模集成电路ultraviolet light: 紫外光Vacuum level :真空能级vertical furnace :井式炉VLSI:超大规模集成电路V olume charge:体电荷wafer:晶片Work function :功函数abrupt junction:突变结;Accumulation :积累Aging:老化alignment:校准Anneal:退火avalanche breakdown:雪崩击穿back-gate:背栅ballistic transport:弹道输运;body Effect:体效应,衬底偏置效应,衬偏效应Bonding:键合breakdown:击穿Buried channels:埋沟cat’s whisker detector:触须式检波器channel length modulation:沟道长度调制;chip: 芯片computer-aided design (CAD):计算机辅助设计CVD (chemical vapor deposition) :化学气相淀积Dangling bond: 悬挂键dangling silicon bond :悬挂键;deep submicrometer:深亚微米;degradation:退化;Degrade:退化dehydration:脱水Depletion-mode:耗尽型器件deposited uniformly:均匀淀积deposited uniformly:均匀淀积;development:显影DIBL (drain-induced barrier lowering):漏至势垒降低效应;die: 裸片dielectric constant:介电常数dielectric constant:介电常数;Dielectric:电介质Diffusion:扩散DMOS (double-diffused MOS) :双扩散MOSdopant:掺杂剂-5doping fluctuations:掺杂工艺的波动Drain:漏(区)Electrode:电极Electron affinity :电子亲和能electron beam lithographic:电子束光刻Energy-bands:能带图Enhancement-mode:增强型EOT(equivalent oxide thickness):等效氧化层厚度;epitaxial:外延;epitaxially grown 外延生长;etch stencil :刻蚀模板etch:刻蚀Field oxide :场氧化层Field oxide:场氧化层Flat-Band Voltage :平带电压Flat-Band Voltage 平带电压floating body:体区浮置gate dielectric:栅介质gate stack:栅叠层GIDL (gate-induced drain leakage):栅感应漏电效应;gradual-channel approximation:渐近沟道近似Hot Carriers Effect:热载流子效应hot-carrier effects: 热载流子效应;impact ionization:碰撞电离;induced electric field:感生电场Interconnection:互联interface state:表面态;interface states:界面态intrinsic Fermi level:本征费米能级inversion layer:反型层Ion Implantation:离子注入kinetic energy:动能;latch-up :闩锁;latch-up:闩锁lattice vibration:晶格振动;LDD(lightly doped drain):轻掺杂漏;leakage current:泄漏电流lithographic mask:光刻版;LOCOS(Local Oxidation of Silicon):硅的局部氧化Mask:掩模Metallization:金属化Metallurgical junction:冶金结momentum:动量;MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor):场效应晶体管nano-scale:纳米级;nonvolatile devices:非挥发性器件nonvolatile devices:非挥发性器件oxidation furnace :氧化炉Oxidation:氧化oxide charges:氧化层电荷Pattern: 样式,图形,集成电路设计中指版图phonons:声子;photolithography:光刻Photomasks:光学掩模photoresist strip:剥离光刻胶Photoresist:光刻胶,光致抗蚀剂Pinched-off :夹断planar technology:平面工艺plasma etch :等离子刻蚀Plasma:等离子Polysilicon:多晶硅Process :工艺(过程)punch-through : 穿通PVD (physical vapor deposition):金属物理-6气相淀积quantum confinement effect:量子限制效应;retrograde channel doping profile:retrograde channel doping profile:具有逆向(峰值不在表面处的)沟道掺杂分布salicide:自对准金属硅化物工艺scaling limit:按比例缩小的极限self-aligned:自对准SEM:扫瞄式电子显微镜(scanning electron microscope)series resistance:串联电阻sheet-resistance:薄层电阻,方块电阻short-channel effects:短沟道效应;short-channel effects:短沟效应silicide:金属硅化物SIMOX (separation by implantation of oxygen):注氧隔离single-crystal ingot:单晶锭single-crystalline silicon:单晶硅;SOI ( Silicon On Insulator):绝缘层上的硅Source:源(区)space charge region:空间电荷区Spacer:侧墙Specification : 规格,规范Sputtering:溅射stepper : 专用步进曝光机Substrate :衬底Subthreshold :亚阈值subthreshold swing:亚阈摆幅subthreshold swing:亚阈值摆动;Surface scattering :表面散射Technology :技术,工艺thermal equilibrium:热平衡thermal oxidation process:热氧化工艺Threshold voltage:阈值电压tunnel:遂穿ULSI:甚大规模集成电路ultraviolet light: 紫外光Vacuum level :真空能级vertical furnace :井式炉VLSI:超大规模集成电路Volume charge:体电荷wafer:晶片Work function :功函数abrupt junction:突变结;Accumulation :积累Aging:老化alignment:校准Anneal:退火avalanche breakdown:雪崩击穿back-gate:背栅ballistic transport:弹道输运;body Effect:体效应,衬底偏置效应,衬偏效应Bonding:键合breakdown:击穿Buried channels:埋沟cat’s whisker detector:触须式检波器channel length modulation:沟道长度调制;chip: 芯片computer-aided design (CAD):计算机辅助设计CVD (chemical vapor deposition) :化学气相淀积Dangling bond: 悬挂键dangling silicon bond :悬挂键;deep submicrometer:深亚微米;degradation:退化;Degrade:退化-7dehydration:脱水Depletion-mode:耗尽型器件deposited uniformly:均匀淀积deposited uniformly:均匀淀积;development:显影DIBL (drain-induced barrier lowering):漏至势垒降低效应;die: 裸片dielectric constant:介电常数dielectric constant:介电常数;Dielectric:电介质Diffusion:扩散DMOS (double-diffused MOS) :双扩散MOSdopant:掺杂剂doping fluctuations:掺杂工艺的波动Drain:漏(区)Electrode:电极Electron affinity :电子亲和能electron beam lithographic:电子束光刻Energy-bands:能带图Enhancement-mode:增强型EOT(equivalent oxide thickness):等效氧化层厚度;epitaxial:外延;epitaxially grown 外延生长;etch stencil :刻蚀模板etch:刻蚀Field oxide :场氧化层Field oxide:场氧化层Flat-Band Voltage :平带电压Flat-Band Voltage 平带电压floating body:体区浮置gate dielectric:栅介质gate stack:栅叠层GIDL (gate-induced drain leakage):栅感应漏电效应;gradual-channel approximation:渐近沟道近似Hot Carriers Effect:热载流子效应hot-carrier effects: 热载流子效应;impact ionization:碰撞电离;induced electric field:感生电场Interconnection:互联interface state:表面态;interface states:界面态intrinsic Fermi level:本征费米能级inversion layer:反型层Ion Implantation:离子注入kinetic energy:动能;latch-up :闩锁;latch-up:闩锁lattice vibration:晶格振动;LDD(lightly doped drain):轻掺杂漏;leakage current:泄漏电流lithographic mask:光刻版;LOCOS(Local Oxidation of Silicon):硅的局部氧化Mask:掩模Metallization:金属化Metallurgical junction:冶金结momentum:动量;MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor):场效应晶体管nano-scale:纳米级;nonvolatile devices:非挥发性器件nonvolatile devices:非挥发性器件oxidation furnace :氧化炉Oxidation:氧化oxide charges:氧化层电荷-8Pattern: 样式,图形,集成电路设计中指版图phonons:声子;photolithography:光刻Photomasks:光学掩模photoresist strip:剥离光刻胶Photoresist:光刻胶,光致抗蚀剂Pinched-off :夹断planar technology:平面工艺plasma etch :等离子刻蚀Plasma:等离子Polysilicon:多晶硅Process :工艺(过程)punch-through : 穿通PVD (physical vapor deposition):金属物理气相淀积quantum confinement effect:量子限制效应;retrograde channel doping profile:retrograde channel doping profile:具有逆向(峰值不在表面处的)沟道掺杂分布salicide:自对准金属硅化物工艺scaling limit:按比例缩小的极限self-aligned:自对准SEM:扫瞄式电子显微镜(scanning electron microscope)series resistance:串联电阻sheet-resistance:薄层电阻,方块电阻short-channel effects:短沟道效应;short-channel effects:短沟效应silicide:金属硅化物SIMOX (separation by implantation of oxygen):注氧隔离single-crystal ingot:单晶锭single-crystalline silicon:单晶硅;SOI ( Silicon On Insulator):绝缘层上的硅Source:源(区)space charge region:空间电荷区Spacer:侧墙Specification : 规格,规范Sputtering:溅射stepper : 专用步进曝光机Substrate :衬底Subthreshold :亚阈值subthreshold swing:亚阈摆幅subthreshold swing:亚阈值摆动;Surface scattering :表面散射Technology :技术,工艺thermal equilibrium:热平衡thermal oxidation process:热氧化工艺Threshold voltage:阈值电压tunnel:遂穿ULSI:甚大规模集成电路ultraviolet light: 紫外光Vacuum level :真空能级vertical furnace :井式炉VLSI:超大规模集成电路Volume charge:体电荷wafer:晶片Work function :功函数-9。

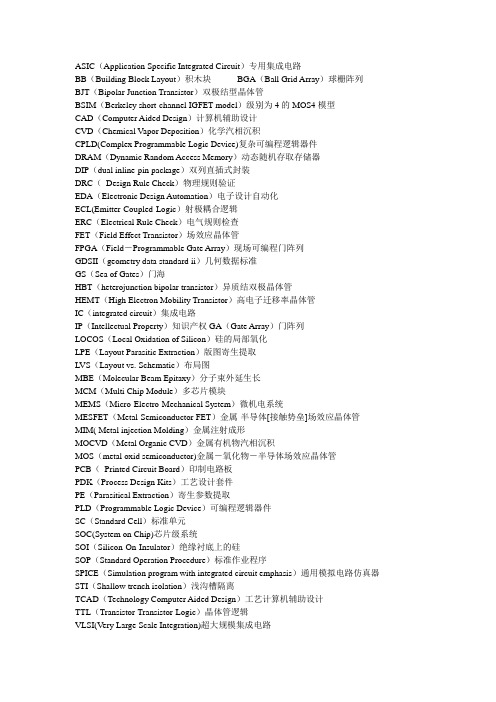

CAD缩写

ASIC(Application Specific Integrated Circuit)专用集成电路BB(Building Block Layout)积木块BGA(Ball Grid Array)球栅阵列BJT(Bipolar Junction Transistor)双极结型晶体管BSIM(Berkeley short-channel IGFET model)级别为4的MOS4模型CAD(Computer Aided Design)计算机辅助设计CVD(Chemical Vapor Deposition)化学汽相沉积CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件DRAM(Dynamic Random Access Memory)动态随机存取存储器DIP(dual inline-pin package)双列直插式封装DRC(Design Rule Check)物理规则验证EDA(Electronic Design Automation)电子设计自动化ECL(Emitter-Coupled-Logic)射极耦合逻辑ERC(Electrical Rule Check)电气规则检查FET(Field Effect Transistor)场效应晶体管FPGA(Field-Programmable Gate Array)现场可编程门阵列GDSII(geometry data standard ii)几何数据标准GS(Sea of Gates)门海HBT(heterojunction bipolar transistor)异质结双极晶体管HEMT(High Electron Mobility Transistor)高电子迁移率晶体管IC(integrated circuit)集成电路IP(Intellectual Property)知识产权GA(Gate Array)门阵列LOCOS(Local Oxidation of Silicon)硅的局部氧化LPE(Layout Parasitic Extraction)版图寄生提取LVS(Layout vs. Schematic)布局图MBE(Molecular Beam Epitaxy)分子束外延生长MCM(Multi Chip Module)多芯片模块MEMS(Micro-Electro-Mechanical System)微机电系统MESFET(Metal-Semiconductor FET)金属-半导体[接触势垒]场效应晶体管MIM( Metal injection Molding)金属注射成形MOCVD(Metal Organic CVD)金属有机物汽相沉积MOS(metal oxid semiconductor)金属-氧化物-半导体场效应晶体管PCB(Printed Circuit Board)印制电路板PDK(Process Design Kits)工艺设计套件PE(Parasitical Extraction)寄生参数提取PLD(Programmable Logic Device)可编程逻辑器件SC(Standard Cell)标准单元SOC(System on Chip)芯片级系统SOI(Silicon-On-Insulator)绝缘衬底上的硅SOP(Standard Operation Procedure)标准作业程序SPICE(Simulation program with integrated circuit emphasis)通用模拟电路仿真器STI(Shallow trench isolation)浅沟槽隔离TCAD(Technology Computer Aided Design)工艺计算机辅助设计TTL(Transistor-Transistor-Logic)晶体管逻辑VLSI(Very Large Scale Integration)超大规模集成电路。

集成电路CAD第一章概述资料

集成电路CAD第一章概述资料1.集成电路(Integrated Circuit,IC)是现代电子技术的重要组成部分。

在电子产品中,IC扮演着控制、存储和处理信号的关键角色。

而集成电路的设计和制造需要借助计算机辅助设计(Computerded Design,CAD)技术。

本章将介绍集成电路CAD的概念、发展历程以及其在电子设计领域的应用。

2. 集成电路CAD的定义集成电路CAD是指通过计算机辅助设计工具和方法,对集成电路进行设计、验证、优化和制造的过程。

它是利用计算机技术来提高集成电路设计与制造效率的一种方法。

集成电路CAD主要包括:•电子设计自动化(Electronic Design Automation,EDA)工具:用于辅助设计和验证集成电路的软件工具,包括原理图设计工具、布局设计工具、电路模拟工具、时序分析工具等。

•集成电路制造自动化(Integrated Circuit Manufacturing Automation,ICMA)工具:用于辅助集成电路制造的软件工具,包括掩膜制作工具、曝光工艺模拟工具、电子束曝光工具、湿法刻蚀工艺模拟工具等。

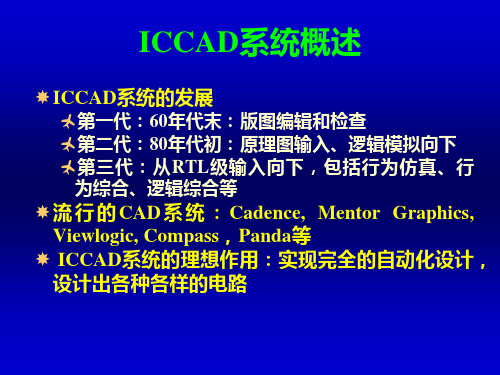

3. 集成电路CAD的发展历程集成电路CAD起源于20世纪60年代,当时主要使用通过硬线连接的离散器件来设计电路。

随着集成电路技术的发展,人们意识到需要更高效、更可靠的设计方法来实现复杂的电路功能。

,集成电路CAD技术应运而生。

•早期阶段(1960年代1970年代):集成电路CAD 主要用于辅助原理图设计和电路模拟。

主要工具是计算器和电路仿真软件。

•发展阶段(1980年代1990年代):随着计算机性能的提升和EDA工具的发展,集成电路CAD技术逐渐成熟并广泛应用。

电路布局、布线和时序分析等功能逐步引入。

•现代阶段(2000年至今):随着集成度和复杂度的增加,集成电路CAD技术也在不断进化。

高级EDA工具和集成电路制造自动化工具成为主流,实现更高效、更精确的电路设计与制造。

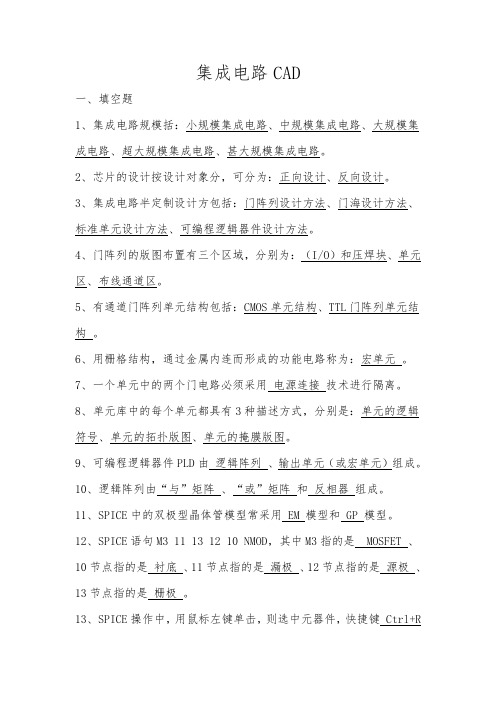

集成电路CAD复习

集成电路CAD一、填空题1、集成电路规模括:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路、甚大规模集成电路。

2、芯片的设计按设计对象分,可分为:正向设计、反向设计。

3、集成电路半定制设计方包括:门阵列设计方法、门海设计方法、标准单元设计方法、可编程逻辑器件设计方法。

4、门阵列的版图布置有三个区域,分别为:(I/O)和压焊块、单元区、布线通道区。

5、有通道门阵列单元结构包括:CMOS单元结构、TTL门阵列单元结构。

6、用栅格结构,通过金属内连而形成的功能电路称为:宏单元。

7、一个单元中的两个门电路必须采用电源连接技术进行隔离。

8、单元库中的每个单元都具有3种描述方式,分别是:单元的逻辑符号、单元的拓扑版图、单元的掩膜版图。

9、可编程逻辑器件PLD由逻辑阵列、输出单元(或宏单元)组成。

10、逻辑阵列由“与”矩阵、“或”矩阵和反相器组成。

11、SPICE中的双极型晶体管模型常采用 EM 模型和 GP 模型。

12、SPICE语句M3 11 13 12 10 NMOD,其中M3指的是 MOSFET 、10节点指的是衬底、11节点指的是漏极、12节点指的是源极、13节点指的是栅极。

13、SPICE操作中,用鼠标左键单击,则选中元器件,快捷键 Ctrl+R可以对该元器件进行旋转,快捷键 Ctrl+F 可以对该元器件进行镜像。

14、在PSPICE中Analysis菜单的Setup对话框中,DC Sweep意思是直流扫描分析,Transient...功能是瞬态分析。

15、电路模拟的三个步骤是:建立电路关系,列电路基本方程,求解电路基本方程。

二、选择题1、要求获得最高速度、最低功耗和最小芯片面积的设计,选择哪种设计方法最合适。

( C )A、半定制设计B、可编程逻辑设计C、全定制设计D、门海设计2、哪种设计方法取消常规门阵列的布线通道,宏单元之间的连线将在无用的器件区上进行。

( C )A、全定制设计B、可编程逻辑设计C、门海设计D、标准单元设计3、以下哪个器件的“与”矩阵和“或”矩阵都可以编程。

超大规模集成电路2017年秋段成华老师第一次作业

Assignment 1:冉文浩2017180136260161.Give a formal or descriptive definition for each of the following terms.●ITRS,1●Gate-Equivalent,1●Technology Nodes,1●Feature size,1●IC design complexity sources,1 ●Behavioral representation,1●Abstraction hierarchy,1●IC design,1●Synthesis,1●Refinement,1●System-level synthesis,1●Logic synthesis,1●Layout synthesis,1●Partial design tree,●Design window,1●Digital design space,1●Static timing analysis,1●Behavioral simulation,1●Post place and routesimulation,1●Composition-based approach.12.Access the Internet for information about Daniel D. Gajski’s “Y-c hart”methodology for integrated circuits design. According to your investigation of the related research papers and/or technical reports, please summarize the “Y-c hart”theory, including (1) design representation domains, (2) design abstraction hierarchy and (3) design activities. References must be listed at the end of your report.3.Write a summary in Chinese of the paper “A New Ear in Advanced IC Design” (inless than 200 characters).1. Give a formal or descriptive definition for each of the following terms.ITRS:International Technology Roadmap for Semiconductor(国际半导体技术发展路线图)Gate-Equivalent:A gate equivalent (GE) stands for a unit of measure which allows to specify manufacturing-technology-independent complexity of digital electronic circuits. It corresponds to a two input NAND gateTechnology Nodes:DRAM 结构里第一层金属的金属间距(pitch)的一半Feature size:roughly half the length of the smallest transistor(芯片上的最小物理尺寸)IC design complexity sources: It includes four main metrics:reliability、cost、performance and power consumption. It also includes four complexity sources:large size、variability and reliability、power dissipation and heterogeneity.Behavioral representation: Represents a design as a black box and its outputs in terms of its input and time. Indicates no geometrical information or structure information. Tables the form of text, math or algorithm.Abstraction hierarchy:Abstraction hierarchies are a human invention designed to assist people in engineering every complex systems by ignoring unnecessary details.A set of interrelated representation levels that allow a system to be represented in varying amounts of details. It includes six levels:system level、chip/algorithm level、RTL、logic gate level、circuit level、layout/silicon levelIC design: An integrated circuit is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material, normally silicon.(在以小片半导体材料上面设计大量的集成电路)Synthesis:将高层次的信息转换成低层次的描述,具体是指将行为域的信息转换成结构域的信息。

eda是什么

eda是什么EDA:电子设计自动化(英语:Electronic design automation,缩写:EDA)是指利用计算机辅助设计(CAD)软件,来完成超大规模集成电路(VLSI)芯片的功能设计、综合、验证、物理设计(包括布局、布线、版图、设计规则检查等)等流程的设计方式。

芯片设计分为前端设计和后端设计,前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及到与工艺有关的设计就是后端设计。

三巨头三足鼎立,合计市场份额超60%,目前,全球EDA软件供应者主要是国际三巨头Synopsys、Cadence和Mentor Graphic,三大EDA企业占全球市场的份额超过60%。

2018年,Synopsys全球市场份额领先,占比达到32.1%;Cadence次之,占比为22.0%。

而从提供的服务和产品上看,三家公司基本都能提供全套的芯片设计EDA解决方案。

其中,Synopsys(新思科技,美国)一直致力于复杂芯片系统(SoCs)的开发。

Synopsys的逻辑综合工具DC(design compiler)和时序分析工具PT(Prime Time)在全球EDA市场几乎一统江山。

Cadence(楷登电子科技,美国)产品涵盖了电子设计的整个流程。

全球知名半导体与电子系统公司均将Cadence软件作为其全球设计的标准。

Mentor Graphics(明导国际,2016年被德国西门子收购)工具虽没有前两家全面,但在某些领域,如PCB(印刷电路板)设计工具等方面有可圈可点的独到之处。

由于EDA行业入门门槛高,成本弹性大,对性能依赖性强,因此行业进入壁垒较高,我国本土有实力的EDA企业并不多。

目前,我国市场上主要EDA 软件供给企业包括华大九天、芯禾科技、广立微、九同方微、博达微、概伦电子、创联智软等。

这些企业虽然在全流程产品上和海外巨头还有不小的差距,但在具体工具上各有所长。

北大微电子

清华大学微电子所研究生课程一、简介我所研究生一级学科名称为电子科学与技术,二级学科名称为微电子学与固体电子学。

研究方向有以下四个方面:微/纳电子器件及微系统;系统的芯片集成;微/纳米工艺学;微/纳器件和系统的CAD方法。

我所现有博士生导师13名;研究生课程共设置19门;目前在校学生数:博士生77人;硕士生:235人(包括工程硕士125人)。

2005年度录取人数:博士生14人;硕士生102人。

2005年度毕业人数:博士生8人;硕士生33人。

二、博士生导师情况介绍姓名职称研究方向李志坚院士教授半导体新器件、器件物理和器件模型、微电子机械系统陈弘毅教授超大规模集成电路设计技术(多媒体数字信号处理、算法的VLSI实现和系统的芯片集成技术)周润德教授超大规模集成电路设计技术(微处理器与嵌埋式系统设计,加密算法,低压,低功耗电路设计)许军教授SiGe/Si微波功率HBT器件与集成电路以及超高速应变硅MOS器件刘理天教授半导体新器件、器件物理和器件模型、微电子机械系统魏少军教授超大规模集成电路设计技术(多媒体数字信号处理、算法的VLSI实现和系统的芯片集成技术)陈炜教授纳米加工、纳米电子器件、超导量子器件和量子计算实现孙义和教授超大规模集成电路设计技术(多媒体DSP技术、VLSI测试方法和可测性设计、网络安全)陈培毅教授半导体新器件、器件物理和器件模型、新型半导体材料余志平教授半导体器件和电路计算机模拟(包括亚100nm硅CMOS器件模型;纳电子器件量子输运模型;基于版图和衬底耦合的RF(射频)电路分析,验证软件和电路单元自动生成。

王志华教授模拟与数模混合集成电路设计,生物与医疗微系统芯片设计,射频电子标签电路技术,集成电路设计方法学任天令教授新型微电子器件、微电子机械系统(MEMS)、新型半导体存储器、纳电子与自旋电子学王燕教授纳电子器件的量子输运模型,化合物半导体器件和电路计算机模拟三、课程设置本年度共开设研究生课程23门,新开课4门。

集成电路cad发展历程

集成电路CAD发展历程一、简介集成电路CAD(Computer-Aided Design)是指利用计算机辅助设计技术来进行集成电路设计的过程。

它通过将设计流程数字化、自动化和可视化,提高了集成电路设计的效率和精度。

本文将从最早的集成电路CAD工具的出现开始,对其发展历程进行全面、详细、完整地探讨。

二、早期集成电路CAD工具1. 历史背景20世纪60年代,随着集成电路(Integrated Circuit,IC)技术的快速发展,人们开始感受到手工设计集成电路的困难,需要寻找更高效的设计方法。

于是,集成电路CAD工具应运而生。

2. 原理图设计工具最早的集成电路CAD工具是基于原理图的设计工具。

设计师通过在计算机上绘制电路的原理图,然后通过模拟和验算来验证电路的正确性。

早期的工具功能简单,但已经为集成电路设计带来了极大的便利。

3. 电路模拟工具随着计算机处理能力的提升,集成电路CAD工具开始提供更强大的电路模拟功能。

设计师可以在计算机上对电路进行仿真分析,以验证电路的性能和稳定性。

这为设计中的错误修正提供了便利,节省了大量时间和资源。

4. 物理布局工具随着集成电路的规模不断扩大,设计师面临着更大规模的布局和布线问题。

为了解决这一问题,物理布局工具应运而生。

设计师可以通过计算机绘制电路的物理布局和布线图,并进行智能布局和布线优化。

这使得设计师可以在保证性能的前提下,尽量减少芯片的面积和功耗。

三、现代集成电路CAD工具1. 逻辑综合工具逻辑综合工具是现代集成电路设计流程中不可或缺的一环。

逻辑综合工具可以将高级语言或者逻辑图转化为电路网表,为后续的优化和物理布局提供基础。

逻辑综合工具可以通过优化逻辑门的选择和布局,来提高电路的性能和功耗。

2. 物理综合工具物理综合工具是集成电路CAD工具中的关键环节。

物理综合工具可以将逻辑网表转换为物理规则满足的布局和布线结果。

物理综合工具充分利用资源利用率、时序特性等约束条件,通过优化和迭代,得到最优的物理布局和布线方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

超大规模集成电路CAD

学时:32 学分:2

电子科学技术与微电子教研室

授课教师: 鲁 迎 春

Luyingc2000@

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

☆ 课程关键词

IC:Integrated Circuit

Hale Waihona Puke 中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

☆ 课程的内容与学时分配

章节 一 内 容 学 时 讲课学时数

3 3

实验学时数

VLSI设计的概述

二

三 四

VLSI设计方法;VLSI设计流程

中国.中学政治教学网崇尚互联共享

硬件描述语言的基本概念和用法; 逻辑仿真软件介绍 逻辑综合的一般概念和方法;逻辑综 合软件介绍

4

7 6

4

5 4 2(Modelsim) 2(Synplify/Pro)

五

可编程逻辑器件基本知识和开发环境 QuartusⅡ介绍

SoC基本概念,自动布局布线的基本概 念,VLSI设计的发展方向 总 学 时 数

10

6

4(QuartusⅡ)

六

2 32

2 24 8

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

☆ 课程的基本要求

掌握VLSI设计的基本概念 掌握VLSI设计方法及相关设计流程

掌握硬件描述语言在VLSI设计中的使用

掌握可编程逻辑器件基本知识和开发环境 掌握SOC的基本概念与自动布局、布线的基本流程

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

☆ 选用教材和参考书目

选用教材:

电子工业出版社

《VLSI设计》,王志功、朱恩编著

主要参考书目:

《电子设计自动化与IC设计》 李东生编著 高等教育出版社 《VLSI设计基础》 李伟华编著 电子工业出版社 《VISL设计导论》 沈绪榜,杜敏著 高等教育出版社 《Altera FPGA/CPLD设计》吴继华,王诚编著 人民邮电出版社 《FPGA系统设计与实践》 黄智伟编 电子工业出版社 《Verilog HDL实用教程》 张明编 电子科技大学出版社 中国.中学政治教学网崇尚互联共享

① 是将系统逻辑与性能的设计要求转化为具体物理版图的过程。 ② 具体是指通过一系列特定的加工工艺,将晶体管等有源器件、电容 和电阻等无源器件,按照一定的电路互连,“集成”在一块半导体 单晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或 系统功能。

VLSI:Very Large Scale Integrated Circuit(万门以上) EDA: Electronic Design Automation SOC: System on chip SOPC:System on programmmable chip VDSM:Very Deep Sub-micron FPGA:Field Programmmable Gate array Top-down :自顶向下

超大规模集成电路CAD

☆ 考

试

平时成绩30% 出勤、实验(上机、试验)、课后练习 授课方式:多媒体教学 上课地点、时间:西二410,14~19周 实验地点、时间:逸夫楼10楼机房 12月24日下午连四节(2:00~6:00) 1月8日下午连四节(7:30~11:30) 试验内容:Modelsim、Synplify/Pro、QuartusII 考试时间:约课程结束后2~3周

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

专业词汇(掌握)

★.IC-Integrated Circuit:集成电路 ★.VDSM-Very Deep Sub-Micron :超深亚微米 (<=0.25um) ★.ASIC-Application Specific Integrated Circuit:专用集成电路 ★.ASSP-Application Specific Standard Parts: 专用标准部件 ★.VLSI-very Large-Scale Integration :超大规模集成电路 ★.EDA-Electronic Design Automation:电子设计自化 ★.SOC-system on a chip:片上系统 ★.SOPC-system on programmable chip:可编程片上系统 ★.IP-Intellectual Property:指知识产权、著作权 ★.CPLD- complex Programmable Logic Device:复杂可编程逻辑器件 ★.FPGA-Field Programmable Gate Array:现场可编程门阵列 ★.BGA-Ball Grid Array:球栅阵列 ★.GAL-Generic Array Logic:通用阵列逻辑 ★.GA-Gate Array:门阵列 ★.LUT-Look-Up Table:查找表 ★.EDIF-Electronic Design Interchange Format:电子设计网表格式 ★.NRE-NonRecurring Engineering:非重复性工程成本或一次性工程成本 ★.P&R-place and route:布局布线

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

★.Verilog HDL:一个专用的、高级的、基于文本的设计输入语言 ★.VHDL:VHSIC 硬件描述语言,高级的基于文本的设计输入语言 ★.DRC-Design rule check:设计规则检查 ★.ERC-Electric rule check:电路规则检查 ★.RTL-Regeister transfer Level :寄存器传输级 ★.LVS-Layout Vs Schematic check :网表一致性检查

考核成绩70%:闭卷笔试

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

应用领域

民用通信 学习娱乐 军用领域

生物科技

VLSI

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

集成电路世界15强

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

集成电路中国15强

中国.中学政治教学网崇尚互联共享

超大规模集成电路CAD

著名EDA软件供应商

Cadence

Synopsys Mentor

Graphics Altera EDA工具 MathWorks-Matlab synplify 华大Panda系统-Zeni系列