义隆单片机EM78P153使用

74HC164应用实例:驱动数码管两例(电路图和源程序)

74HC164应用实例:驱动数码管两例(电路图和源程序)————————————————————————————————作者:————————————————————————————————日期:4HC164应用实例:驱动数码管两例(电路图和源程序) 文章编号:100816210758 文章分类: 电路 > 电子元件 点击:... 关键词: 74HC164文章来源:百合电子工作室收集整理 摘要: 74HC164应用实例:驱动数码管的两个实例分别提供了汇编源程序和C 源程序...实例174HC164是串行输入,并行输出接口器件,可用在单向的并行输出/并行地址锁存等. 74HC164因为价格便宜,容易使用特别适合使用在在需要用到数码管显示IO 口又比较紧张的电子产品中,下面浅谈使用方法:1. 首先先了解他的引脚功能和逻辑图,如下图:图1 引脚名称和用途图2 真值表通过真值表我们可以了解到,A,B两个输入端是互锁的,CLK上升沿时数据移入移位寄存器中,CLEAR为清零用的,接低电平时所有端口都输出低电平,了解了真值表之后开始运用了,先给出如下原理图:图3 原理图图中,采用义隆的EM78P153作为控制芯片,P50作为CLK时钟信号,注意平时数据不传输时,时钟信号是不发送的应一直保持低电平或者高电平,数据需要传输的时候才输出时钟信号^_^ ,继续P51作为移位数据输出端,接到74HC164的B端,A端接高电平,当然也可以AB端短路,然后连接到DATA移位数据端,P52作为数码管的选通信号(也可以叫消隐^_^), 作用是使数据传输过程暂时关闭显示,以免显示出不需要的数据,原因是应为164不带锁存功能,数据传输过程是一位一位的向高位移位输出的,所以要等数据全部移入后才打开始点亮数码管.注意了哦,通过查看164的规格书发现,164输出高电平电流比输出低电平电流要小,亦称灌电流大,扇出电流弱,所以适合选用共阳数码管,如图,本人偷懒没有画出那个数码管的8字该介绍的介绍的差不多了,废话少说,该开始干活了,任务是: 显示0-9 每秒+1 ,到9后又返回0,一直循环显示,根据任务得到如下流程图:1. 显示部分:将需要显示的数值送入A ==>查表求得显示段码==>将段码逐位移入164==>8位移完后点亮数码管==>延时==>返回第一步执行2. 中断部分:进入中断==>保存现场(以备调查取证,送你入狱^_^)==>重置TCC==>够1秒钟将需要显示的数据+1,并重置,不够就退出;根据以上要求就开始写代码调试了,要注意一点,数据移位时一定要记得高位在前哦,否则显示错误别怪我没有说清楚,我当年实验时就因为这个数据移位方向反了排查了半天,甚至以为是时钟频率不对,又以为时许不对.....搞了半天,NND后来重看DATASHEET才发现,原来是低级错误啊,呜呼哀哉.......,希望你不要重蹈我覆辙,哎哟!! 谁! 谁! 谁扔砖头上来? 啥? 你扔的? 我废话太多.........,那俺少来两句,继续上菜, 咦好像没啥可说的了,上源程序吧1.;中断部分:2.3.;;;;;;;;;;中断;;;;;;;;4.INTPUT:5.MOV TEMPA, A;6.MOV A,@130;7.MOV TCC,A;255-130=1258.CLR RF;9.;;;;;此处填写250Us处理程序10. BS WKREG,T500US11.;;;;;;;;;;;;;;;;;;;;;;;;;12. DJZ R1MS13.JMP INTEXT;14.MOV A,@415.MOV R1MS,A;重置16. BS WKREG,T1MS17.;;;;;;;此处填写1ms处理程序18.19.;;;;;;;;;;;;;;;;;;;;;;;;;;20. DJZ R20MS21.JMP INTEXT;22.MOV A,@2023.MOV R20MS,A;重置24.;;;此处填写1秒处理程序25. BS WKREG,T20MS26.;;;;;;;;;;;;;;27. DJZ R1S28.JMP INTEXT;29.MOV A,@5030.MOV R1S,A;31.;;;;;;;;;32.INC NUMBER33.MOV A,NUMBER34. SUB A,@1035. JBS SR,236.JMP INTEXT37.MOV A,@038.MOV NUMBER,A39.40.41. INTEXT:42.MOV A,TEMPA;43.RETI;;;;;;;;;;;;;;;;;;;;;44.45.46.47.48.49.;显示部分:50.51.;==============TXDATA==============52.TXDATA:53. BS P5,CC154.MOV A,@855.MOV DATALOP,A;56.TXLOP:57. BC WKREG,T500US58. BS P5,CLK;clk=高59.NOP;60.NOP61. JBS DATA_BUF,762.JMP $+363. BS P5,DATA;64.JMP $+265. BC P5,DATA66.DD1MS: JBS WKREG,T500US67.JMP $-168. BC P5,CLK69. BC WKREG,T500US70. JBS WKREG,T500US71.JMP $-1;72.RLC DATA_BUF73. DJZ DATALOP74.JMP TXLOP75.;;;;;;;;;;76. BC WKREG,T500US77. BS P5,CLK;clk=高78. BC WKREG,T500US79. JBS WKREG,T500US80.JMP $-1;81. BC P5,CLK82.;;;;;;;;83. BC P5,CC184.85.RET;;;;;;;86.87.;数据查表88.;===============DSPTBL============89.DSPTBL: ADD PC,A90. RETL @0B01000000;091. RETL @0B01111001;192. RETL @0B00100100;293. RETL @0B00110000;394. RETL @0B00011001;495. RETL @0B00010010;596. RETL @0B00000010;697. RETL @0B01111000;798. RETL @0B00000000;899. RETL @0B00010000;9100.101.102.;循环体部分;103.104.;;;;;;;;;;主程序;;;;;;;;;;;105.MLOOP:106.MOV A,NUMBER107.CALL DSPTBL108.MOV DATA_BUF,A109.CALL TXDATA110. BC WKREG,T1MS111. JBS WKREG,T1MS112.JMP $-1113.NOP;114.115.JMP MLOOP;;;;;;;;;;;;;;;;;;;;实例2在实际应用中驱动数码管常用的方式分动态扫描和静态驱动。

78P153

78P153S资料1、一般描述EM78P153S是采用低耗高速CMOS工艺制造的8位单片机,它内部包含一个1024*13-bit的一次性可编程只读电存储器(OTP-ROM)。

有15位选项位可满足用户要求,其中的保护位可用来防止程序被读出由于有OTP-ROM,EM78P153S提供给用户一个方便的开发和检验他们的程序的环境。

而且,程序代码可用ELAN编程器写入芯片。

2、特征14个引线封装:EM78P153S 、工作电压范围:2.3V~5.5V 、适用温度范围:0 ℃~70℃工作频率范围(基于2个Clock):晶振模式:DC-20MHZ at 5V,DC-8MHZ at 3V,DC-4MHZ at 2.3VERC模式:DC-4MHZ at 5V,DC-4MHZ at 3V,DC-4MHZ at 2.3V低功耗: * 在5V/4MHz时低于1.5mA 、* 在3V/32KHz时为15uA、 * 在休眠模式时为1uA 1024x13位片内ROM 、内置4个校准IRC振荡器(8MHZ,4MHZ,1MHZZ,455KHZ)振荡器起振时间预分频系数可编程、一个安全位(代码寄存器中)保护程序不被读出一个结构寄存器满足用户要求、32x8bits片内寄存器组(SRAM,一般寄存器)2组双向I/O端口、 5级用于子程序嵌套的堆栈8位实时计时/计数器(TCC),其信号源、触发边沿可编程选择,溢出时产生中断节能模式(SLEEP模式)三种可用的中断: * TCC溢出中断 * 输入引脚变化中断(从休眠模式唤醒) * 外部中断可编程自由运行看门狗定时器(WDT)、7个可编程上拉I/O引脚7个可编程漏极开路 I/O引脚、 6个可编程下拉I/O引脚每个指令周期为两个时钟周期:99.9%的指令为单周期指令封装类型:14脚SOP、DIP ,14管脚DIP 300mil:EM78P153SP、 14管脚SOP 150mil:EM78P153SN 系统高低频率的变化点是400KHZ3、管脚分配管脚说明:4.1 操作寄存器1、R0(间接地址寄存器)R0并非实际存在的寄存器。

义隆单片机EM78P153使用讲解

基于EM78P153S的应用设计(V1.0)目录第一章EM78P153S的初识 (1)1.1 EM78P152/3S特性 (1)1.2 EM78P152/3S引脚 (2)1.3 功能寄存器 (2)1.3.1 累加器与端口控制寄存器 (2)1.3.2中断状态寄存器与中断使能寄存器 (3)1.3.3 操作寄存器 (4)1.3.4 特殊功能寄存器 (6)1.4 数据存储器的配置 (7)1.5 休眠与唤醒 (7)1.6 分频器 (9)1.7 定时器/计数器TCC (9)第二章EM78系列单片机应用软件的编辑与仿真 (11)2.1 Simulator的下载与安装 (11)2.2 Simulator的使用方法 (11)2.3 Simulator系统常用命令汇总 (14)2.4 Simulator仿真中的常见问题 (15)第三章EM78系列单片机的汇编指令 (17)3.1 寻址方式 (17)3.2 伪指令 (18)3.3 指令速查表 (18)第四章EM78P153S应用软件设计 (20)4.1 外部中断程序 (20)4.2 花样灯程序 (22)4.2.1 设计需求 (22)4.2.2 软件设计 (23)4.2.3 硬件设计 (37)4.2.4 元器件明细表 (38)第五章EM78系列单片机应用程序的烧录 (39)5.1 程序的转换过程 (39)5.2 烧录器与烧录软件 (40)5.3 烧录步骤 (41)第一章 EM78P153S的初识EM78P152/3S是采用低功耗高速CMOS工艺设计开发的8位微控制器,它的内部有一个1024×13位一次性可编程只读存储器(OTP_ROM) ,可见1k的只读存储器(ROM)决定了应用程序不能够太多,否则应用程序机器码将无法烧录到芯片中。

硬件设计中,EM78P152/3S可以通过设置代码选项寄存器使微处理器工作在内部RC 振荡模式(IRC)下,此模式下采用上电复位模式而不需要外接时钟电路;同时利用上电自动复位而不需要外接复位电路,P63复位引脚可以直接作为输入脚使用,充分提高了微处理器端口的利用率,这样硬件应用电路极为简化,节省了硬件成本。

ELAN义隆系列单片机解密

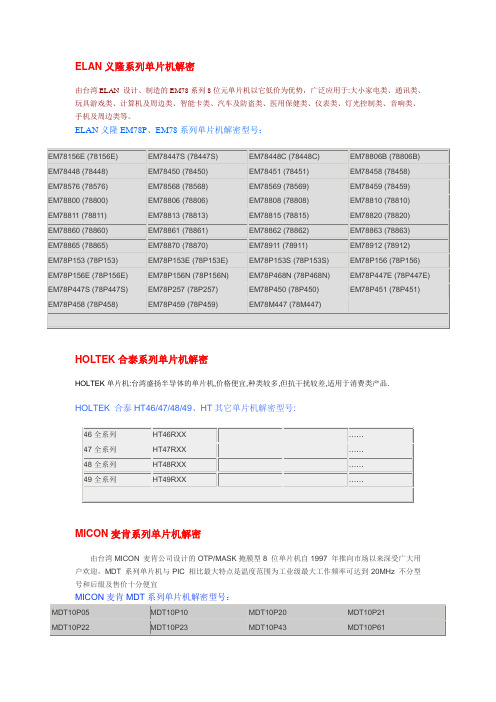

ELAN义隆系列单片机解密由台湾ELAN 设计、制造的EM78系列8位元单片机以它低价为优势,广泛应用于:大小家电类、通讯类、玩具游戏类、计算机及周边类、智能卡类、汽车及防盗类、医用保健类、仪表类、灯光控制类、音响类、手机及周边类等。

ELAN义隆EM78P、EM78系列单片机解密型号:HOLTEK合泰系列单片机解密HOLTEK单片机:台湾盛扬半导体的单片机,价格便宜,种类较多,但抗干扰较差,适用于消费类产品. HOLTEK 合泰HT46/47/48/49、HT其它单片机解密型号:MICON麦肯系列单片机解密由台湾MICON 麦肯公司设计的OTP/MASK掩膜型8 位单片机自1997 年推向市场以来深受广大用户欢迎,MDT 系列单片机与PIC 相比最大特点是温度范围为工业级最大工作频率可达到20MHz 不分型号和后缀及售价十分便宜SONIX松翰系列单片机解密应用领域:电子玩具产品:发声玩具、遥控玩具、音乐玩具、早教机、电子词典、电子故事书等小家电产品:电风扇、电暖器、消毒柜、微波炉、电磁炉、电饭煲、电子炖盅等遥控器:电视、空调、VCD、DVD、机顶盒遥控器充电器:锂电、镍氢、镍铬等智能充电器电子称:厨房称、人体称、口袋称、脂肪称松翰(SONIX)SN8P全系列单片机解密型号:PORTEK普泰系列单片机解密普泰半导体凭借着对产业趋势的掌握及卓越技术之极致深耕,在半导体产业界占一席之地。

从各项消费性电子产品的研发设计,兼顾客户多样化不同的需求;普泰提供了长期及稳定的产品,让客户快速进入市场以确保产品竞争优势,更降低了客户生产成本。

普泰(PORTEK)PTK87XX全系列单片机解密型号:TENX十速系列单片机解密八位单片机可兼容PIC/EMC等芯片,其具备相等或更优越抗干扰功能,适用于频道选择器、天线控制系统、功率放大器、智能型芳香机、超声波测距仪、遥控风扇、负离子风扇、遥控器、电卷发器、电动窗帘、按摩器、按摩椅、按摩鞋、按摩棒、雾化器、豆浆机、打蛋机、咖啡壶、小家电、密码锁、定时器等消费产品应用;四位单片机可实现定时、时钟、温度、湿度、倒计时等不同功能及组合,具标准芯片及依客户所需选择最佳性价比之四位单片机母体设计;USB控制芯片可兼容赛普拉斯( Cypress )系列芯片,适用于游戏机、跳舞毯、功夫机、手柄、鼠标、个人音箱等USB产品,具备优越之性价比。

义隆EM78P153S中文规格书

• iii

Contents

目录

目录 ...........................................................................................................................IV

1 综述······························································································································· 6

The contents of this specification are subject to change without further notice. ELAN Microelectronics assumes no responsibility concerning the accuracy, adequacy, or completeness of this specification. ELAN Microelectronics makes no commitment to update, or to keep current the information and material contained in this specification. Such information and material may change to conform to each confirmed order.

ELAN and ELAN logo

are trademarks of ELAN Microelectronics Corporation.

EM78系列单片机简介

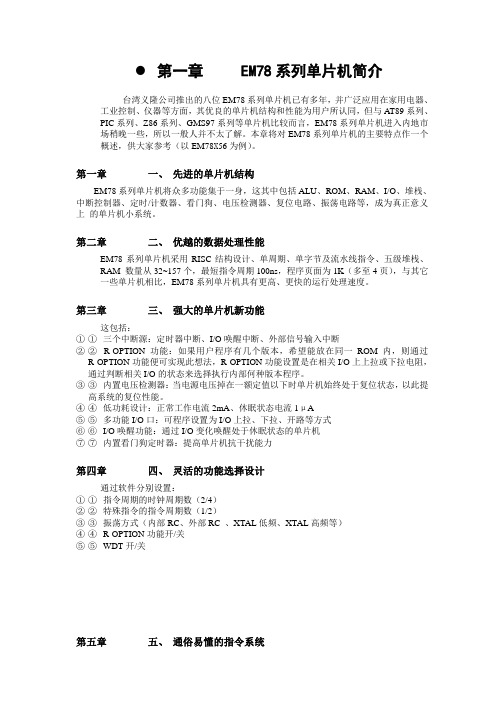

第一章EM78系列单片机简介台湾义隆公司推出的八位EM78系列单片机已有多年,并广泛应用在家用电器、工业控制、仪器等方面,其优良的单片机结构和性能为用户所认同,但与AT89系列、PIC系列、Z86系列、GMS97系列等单片机比较而言,EM78系列单片机进入内地市场稍晚一些,所以一般人并不太了解。

本章将对EM78系列单片机的主要特点作一个概述,供大家参考(以EM78X56为例)。

第一章一、先进的单片机结构EM78系列单片机将众多功能集于一身,这其中包括ALU、ROM、RAM、I/O、堆栈、中断控制器、定时/计数器、看门狗、电压检测器、复位电路、振荡电路等,成为真正意义上的单片机小系统。

第二章二、优越的数据处理性能EM78系列单片机采用RISC结构设计、单周期、单字节及流水线指令、五级堆栈、RAM数量从32~157个,最短指令周期100ns,程序页面为1K(多至4页),与其它一些单片机相比,EM78系列单片机具有更高、更快的运行处理速度。

第三章三、强大的单片机新功能这包括:①①三个中断源:定时器中断、I/O唤醒中断、外部信号输入中断②②R-OPTION功能:如果用户程序有几个版本,希望能放在同一ROM内,则通过R-OPTION功能便可实现此想法,R-OPTION功能设置是在相关I/O上上拉或下拉电阻,通过判断相关I/O的状态来选择执行内部何种版本程序。

③③内置电压检测器:当电源电压掉在一额定值以下时单片机始终处于复位状态,以此提高系统的复位性能。

④④低功耗设计:正常工作电流2mA、休眠状态电流1μA⑤⑤多功能I/O口:可程序设置为I/O上拉、下拉、开路等方式⑥⑥I/O唤醒功能:通过I/O变化唤醒处于休眠状态的单片机⑦⑦内置看门狗定时器:提高单片机抗干扰能力第四章四、灵活的功能选择设计通过软件分别设置:①①指令周期的时钟周期数(2/4)②②特殊指令的指令周期数(1/2)③③振荡方式(内部RC、外部RC、XTAL低频、XTAL高频等)④④R-OPTION功能开/关⑤⑤WDT开/关第五章五、通俗易懂的指令系统EM78系列单片机指令系统采用与大家熟知的MCS-51指令风格设计,共计58条指令,大家通过较短的时间便能掌握运用。

EMC(义隆)8K烧写器 说明书

EMC(义隆)8K 烧写器使用手册书 EMC(义隆)烧写器 DWTR 8K 使用手册(V.HUSOON20100817) 前言 我们做过很多义隆(EMC)的芯片解密和破解,样片客户确认正确后,到客户自己 烧写芯片的时候,我们发现很多客户不怎么会使用 EMC 的编程器。

针对 EM78 系 列单片机一次性烧写 (OTP) 芯片, 义隆公司推出了高性能带液晶显示介面的 EM78 全系列烧录器:DWRITER。

它可以烧入目前义隆公司生产的 EM78 系列 OTP 单片 机:EM78P153/156/447/458/459/451 等。

但由于 EMC 的专用烧录器“DWTR 8K” 说明书不详细,并且都是英文的,界面不是很友好,客户使用比较困难,比 5K ,经常会出现一些问题,所以下面我 的还难用(DWTR 5K 使用说明下载地址) 们以图文形式讲解一下 EMC 的 8K 专用烧录器“DWTR 8K”的使用流程. 单片机解密热线:021-******** 56311936 企业 QQ:800015035沪生电子 陈金林 2010.8.18上海沪生电子-单片机解密专家 021-******** 021-******** EMC(义隆)8K 烧写器使用手册书 DWTR 8K 是在 5K 的基础上升级的一款专业用于 EMC 系列单片机烧写的编程 器。

相对于 5K,8K 编程器支持的功能和型号更多,运用更广泛,检测性能更 强大。

目前我们解密 EMC 系列单片机提供的也都是 DWTR 8K 的熔丝配置位 (5K 编程器于 2010 年已经停产) 。

DWTR 8K 分为工规和商规两种规格(工规和商规两种主控芯片不同,通过更换 主芯片来实现工规和商规的变换,不需要换编程器) ,分别用于工业级和商业级 单片机的烧写;商业级和工业级的单片机的区别简单的理解为就是工业级的后 面带有 N 字样,例如:EM78P156E 的是商业级,EM78P156N 就是工业级的。

红外遥控解码(EM78P153)程序范例

红外遥控解码(EM78P153)程序范例红外遥控解码(EM78P153)程序范例--------------------------------------------------------------------------------发布时间:2007年1月4日 16时38分;芯片为EM78P153 (ST码);P64,P65接晶振,振荡模式为4MHz晶振;看门狗关,指令周期为2个CLOCK,P63为复位脚;*******************IO口的定义*********************PORT6 EQU 0X06IOC60 EQU 0X06;**************特殊功能寄存器的定义******************TCC EQU 0X01PC EQU 0X02PSW EQU 0X03IOCD0 EQU 0X0DIOCE0 EQU 0X0EIOCF0 EQU 0X0FRF EQU 0X0F;***************用户自定义的寄存器*******************COUNTER EQU 0X10CODE1 EQU 0X11CODE2 EQU 0X12CODE3 EQU 0X13CODE4 EQU 0X14LP_CNT0 EQU 0X15LP_CNT1 EQU 0X16TEMP EQU 0X17TEMPCODE EQU 0X18REPEAT_COUNTER EQU 0X19SEND_DATA EQU 0X1AUSER_CODE EQU 0X1BFLAG EQU 0X1C;*******************FLAG位定义**********************C EQU 0Z EQU 2TCIF EQU 0LEAD EQU 0REPEAT EQU 1INPUT EQU 1OUTPUT EQU 0ORG 0X000NOPNOPNOPNOPJMP 0X50;********************表格转换子程序程序****************** TABLE_CONVER:CLR TEMPTABLE_CONVER_1:MOV A,TEMPCALL TABLE_CONVERSION_INBC PSW,ZXOR A,CODE3JBC PSW,ZJMP EXIT_5INC TEMPJMP TABLE_CONVER_1EXIT_5:CALL TABLE_CONVERSION_OUTRET;**********************表格转换程序IN********************* TABLE_CONVERSION_IN:ADD PC,ARETL 0XD0 ;KEY_1RETL 0X58 ;KEY_2RETL 0XD8 ;KEY_3RETL 0X90 ;KEY_4RETL 0X18 ;KEY_5RETL 0X98 ;KEY_6RETL 0XE0 ;KEY_7RETL 0X68 ;KEY_8RETL 0XE8 ;KEY_9RETL 0X28 ;KEY_0RETL 0X20 ;KEY_3DRETL 0XA0 ;KEY_MUTERETL 0X40 ;KEY_VOCALRETL 0XE2 ;KEY_VOL+RETL 0XA2 ;KEY_VOL-RETL 0X52 ;KEY_TUNE FWDRETL 0X22 ;KEY_TUNE REVRETL 0X12 ;KEY_STOPRETL 0X80 ;KEY_<|RETL 0X82 ;KEY_|>RETL 0X02 ;KEY_OKRETL 0XF0 ;KEY_TUNERRETL 0X78 ;KEY_AM/FMRETL 0XF8 ;KEY_SAVERETL 0X50 ;KEY_AUDIO;**********************表格转换程序OUT********************* TABLE_CONVERSION_OUT:MOV A,TEMPADD PC,ARETL 0X35 ;KEY_1RETL 0X2D ;KEY_2RETL 0X25 ;KEY_3RETL 0X1D ;KEY_4RETL 0X34 ;KEY_5RETL 0X2C ;KEY_6RETL 0X24 ;KEY_7RETL 0X1C ;KEY_8RETL 0X33 ;KEY_9RETL 0X2B ;KEY_0RETL 0X10 ;KEY_3DRETL 0X18 ;KEY_MUTERETL 0X11 ;KEY_VOCALRETL 0X16 ;KEY_VOL+RETL 0X15 ;KEY_VOL-RETL 0X28 ;KEY_TUNE FWDRETL 0X2A ;KEY_TUNE REVRETL 0X22 ;KEY_STOPRETL 0X31 ;KEY_<|RETL 0X21 ;KEY_|>RETL 0X29 ;KEY_OKRETL 0X2E ;KEY_TUNERRETL 0X20 ;KEY_AUX-1RETL 0X23 ;KEY_AUX-2RETL 0X17 ;KEY_DVDORG 0X050MAIN:;*********************初始化寄存器********************** MOV A,@0B00000000IOW IOCE0MOV A,@0B11111101IOW IOCD0MOV A,@0B00000010IOW IOC60MOV A,@0B00000001MOV PORT6,AMOV A,@0B00000001IOW IOCF0CLR FLAGCLR TEMPCODECLR COUNTERCLR CODE1CLR CODE2CLR CODE3CLR CODE4MOV A,@0B10010000MOV USER_CODE,A;*********************扫描引导码********************** SCAN_LEAD_CODE:JBC PORT6,INPUTJMP SCAN_LEAD_CODECLR FLAGCLR REPEAT_COUNTERCLR TEMPCODECALL JUDGE_START_CODEJBS FLAG,LEADJMP SCAN_LEAD_CODE;*********************接收数据********************** RECEIVE_DATA_PROCEE:CLR TEMPCODECALL RECEIVE_DATAMOV A,TEMPCODEMOV CODE1,AMOV A,@0 ;判断用户码是否是00BC PSW,ZXOR A,CODE1JBS PSW,ZJMP SCAN_LEAD_CODECLR TEMPCODECALL RECEIVE_DATAMOV A,TEMPCODEMOV CODE2,AMOV A,@0XFF ;判断用户码是否是FFBC PSW,ZXOR A,CODE2JBS PSW,ZJMP SCAN_LEAD_CODECLR TEMPCODECALL RECEIVE_DATAMOV A,TEMPCODEMOV CODE3,ACLR TEMPCODECALL RECEIVE_DATAMOV A,TEMPCODEMOV CODE4,ACLR FLAG;*********************发送数据********************** SEND_DATA_PROCEE:JBS USER_CODE,6 ;ST码的次高位反相JMP COM_1 ;=0JMP COM_2 ;=1COM_1:BS USER_CODE,6JMP VVVCOM_2:BC USER_CODE,6JMP VVVVVV:CALL TABLE_CONVER ;调用码表转换子程序MOV CODE3,AREP:CALL TRANSMIT_DATABS PORT6,OUTPUTCALL JUDGE_REPEAT_CODE ;扫描引导码是否在重复? JBS FLAG,LEADJMP SCAN_LEAD_CODEJBC FLAG,REPEATJMP REP ;引导码是重复,继续扫描JMP RECEIVE_DATA_PROCEE ;引导码不重复,去接收新数据;****************引导码的检测子程序***************** JUDGE_START_CODE:CLR COUNTER ;清计数器JUDGE_START_CODE_0:JBC PORT6,INPUTJMP NO_HIGHCALL DELAY0.5MSJBC PORT6,INPUTJMP NO_HIGHINC COUNTERJMP JUDGE_START_CODE_0NO_HIGH:MOV A,COUNTERBC PSW,CSUB A,@20 ;20-AJBS PSW,CJMP EXIT_0 ;C=1,COUNTER>20MOV A,COUNTERBC PSW,CSUB A,@16 ;16-AJBC PSW,CJMP EXIT_0 ;C=0,COUNTER<16BS FLAG,LEADEXIT_0:JBC PORT6,INPUTJMP EXIT_0INC REPEAT_COUNTERRET;****************接收数据子程序********************** RECEIVE_DATA:MOV A,@8MOV COUNTER,AMOV A,@0B00100000CONTW ;停止记数CONTINUE_1:JBS PORT6,INPUTJMP CONTINUE_1CLR TCCMOV A,@0B00000100CONTW ;TCC开始记数CONTINUE_2:MOV A,TCCMOV TEMP,ABC PSW,CSUB A,@250JBS PSW,CJMP SCAN_LEAD_CODE ;C=0,TCC>250JBC PORT6,INPUTJMP CONTINUE_2MOV A,TCCMOV TEMP,ABC PSW,CSUB A,@60;142JBC PSW,CJMP X1 ;C=1,TCC<60JMP X2 ;C=0,TCC>60X1:BC TEMPCODE,0JMP EXIT_1X2:BS TEMPCODE,0JMP EXIT_1EXIT_1:DJZ COUNTERJMP HHMOV A,@0B00100000CONTW ;停止记数RETHH:BC PSW,CRLC TEMPCODEJMP CONTINUE_1;****************发送数据子程序********************** TRANSMIT_DATA:MOV A,@4MOV COUNTER,AMOV A,USER_CODE ;@0B10010000 ;发送ST的用户码MOV SEND_DATA,ACYCLE_1:JBS SEND_DATA,7JMP SEND_P_0JMP SEND_P_1SEND_P_1:CALL SEND_CODE_1 JMP EXIT_3SEND_P_0:CALL SEND_CODE_0 JMP EXIT_3EXIT_3:RLC SEND_DATA DJZ COUNTER JMP CYCLE_1MOV A,@8MOV COUNTER,AMOV A,CODE3 MOV SEND_DATA,A RLC SEND_DATA CYCLE_2:JBS SEND_DATA,7 JMP SEND_Q_0 JMP SEND_Q_1 SEND_Q_1:CALL SEND_CODE_1 JMP EXIT_4SEND_Q_0:CALL SEND_CODE_0 JMP EXIT_4EXIT_4:RLC SEND_DATA DJZ COUNTERJMP CYCLE_2RET;***************发送数据"1"子程序******************** SEND_CODE_1:MOV A,@0B00100000CONTW ;停止记数MOV A,@0B00000001 ;允许TCC中断IOW IOCF0MOV A,@35 ;引导脉冲的预置值MOV TCC,AMOV A,@0B00000001 ;选择预分频比为1:4 CONTWBC PORT6,OUTPUTWAIT_1:JBS RF,TCIFJMP WAIT_1MOV A,@0B00100000CONTW ;停止记数BC RF,TCIFMOV A,@32 ;代码"1"的预置值MOV TCC,AMOV A,@0B00000101 ;选择预分频比为1:64 CONTWBS PORT6,OUTPUTWAIT_2:JBS RF,TCIFJMP WAIT_2BC RF,TCIFMOV A,@0B00100000CONTW ;停止记数RET;***************发送数据"0"子程序******************** SEND_CODE_0:MOV A,@0B00100000CONTW ;停止记数MOV A,@0B00000001 ;允许TCC中断IOW IOCF0MOV A,@35 ;引导脉冲的预置值MOV TCC,AMOV A,@0B00000001 ;选择预分频比为1:4 CONTWBC PORT6,OUTPUTWAIT_3:JBS RF,TCIFJMP WAIT_3MOV A,@0B00100000CONTW ;停止记数BC RF,TCIFMOV A,@114 ;代码"0"的预置值MOV TCC,AMOV A,@0B00000101 ;选择预分频比为1:64 CONTWBS PORT6,OUTPUTWAIT_4:JBS RF,TCIFJMP WAIT_4NOPBC RF,TCIFMOV A,@0B00100000CONTW ;停止记数RET;****************重复码的检测子程序****************** JUDGE_REPEAT_CODE:CLR COUNTER ;清计数器CLR FLAGJUDGE_REPEAT_CODE_0:JBC PORT6,INPUTJMP JUDGE_REPEAT_CODE_0SS:JBC PORT6,INPUTJMP JUDGE_REPEAT_CODE_1CALL DELAY0.5MSJBC PORT6,INPUTJMP JUDGE_REPEAT_CODE_1INC COUNTERJMP SSJUDGE_REPEAT_CODE_1:MOV A,COUNTERBC PSW,CSUB A,@20 ;20-AJBS PSW,CJMP EXIT_2 ;C=1,COUNTER>20MOV A,COUNTERBC PSW,CSUB A,@16 ;16-AJBC PSW,CJMP EXIT_2 ;C=0,COUNTER<16BS FLAG,LEADJMP JUDGE_REPEAT_CODE_2EXIT_2:RETJUDGE_REPEAT_CODE_2:CLR COUNTER ;清计数器JUDGE_REPEAT_CODE_3:JBS PORT6,INPUTJMP JUDGE_REPEAT_CODE_4CALL DELAY0.5MSJBS PORT6,INPUTJMP JUDGE_REPEAT_CODE_4INC COUNTERJMP JUDGE_REPEAT_CODE_3JUDGE_REPEAT_CODE_4:MOV A,COUNTERBC PSW,CSUB A,@7 ;7-AJBS PSW,CJMP NO_REPEAT ;C=0,COUNTER>7JMP YES_REPEAT ;C=1,COUNTER<7NO_REPEAT:BC FLAG,REPEATCLR REPEAT_COUNTERRETYES_REPEAT:BS FLAG,REPEATINC REPEAT_COUNTERRET;****************延时0.5mS子程序********************* DELAY0.5MS:MOV A,@2MOV LP_CNT0,A DELAY0.5MS_1: MOV A,@82 MOV LP_CNT1,A DELAY0.5MS_2: NOPNOPNOPDJZ LP_CNT1JMP DELAY0.5MS_2 DJZ LP_CNT0JMP DELAY0.5MS_1。

EM78P153中文资料

z |} 512×13 OTP ROM *¥'½¾³¿/012c/0À 512 Á Â

z ÃÄ R2 ´ÅÆ 0

元器件交易网

uÔÕvC

^_O4

³ß TCC ð WDT c 8 UV4^_O4©Ð\]ª#¬_>($ $ CONT UV4 PAB %qPSR0~PSR2 &q_O`aä_ TCC$! 5 TCC ¤GÅÎ^_O4Æ 0ä_ WDT$! WDT ^_O4Å©ï WDTC SLEP \Æ 0TCC/WDT '»º» 5 ´¼

z Ü 3v7 ûü z Ü 0~2 P50~P52$Ü 4~6 P60~P620 ü¬$1 C z IOCB UV4&E5

5) IOCC UV4

7

6

5

4

3

2

1

0

OD7

OD6

OD5

OD4

-

OD2

OD1

OD0

z Ü 3 ûü z í_ P60~P62vP64~P67 R¬0 ü¬$1 C z IOCC UV4&E5

元器件交易网

EM78P153 CMOS 8 512*13 ! ROM OTPROM "#$%&'()*+,-./0/012& EMC 3/4567 13 89&:;%<=$>?@&ABC/0DEF

y 1$¸Æ 0 z Ü 3~7 ûü$EF 0 z RF &¸Æ 0$Ûf& 1 z IOCF0 >~ UV4 注意:读 RF 的结果为 RF 和 IOCF0 相与的结果。

义隆单片机应用笔记

义隆单片机应用应用笔记义隆EM78PXXX系列单片机价格低廉,在一些要求不高的应用场合经常被选用。

对于刚接触这个系列单片机的朋友,事先了解一些应用中可能遇到的问题,可能可以减少一些走弯路的时间。

一、关于义隆单片机抗静电放电问题。

EM78PXXX系列单片机也有商规和工规之分,商规的价格还会更低廉一些,但经一次偶然的事件提醒,笔者对商规芯片的应用开始谨慎起来。

那是做一个与安防有关的项目,无意中使用电蚊拍对装有EM78P447的控制器外壳拍打一只苍蝇,随着电蚊拍“啪啪”两声放电声响,苍蝇死了,控制器的LED数码管也熄灭了。

经检查控制器其他逻辑器件无恙,而EM78P447早已一命呜呼。

通过这个事件说明,商规芯片的应用需充分考虑环境因素的影响,否则,在辛辛苦苦做完一个项目之后发生这样的情况,岂不是很尴尬。

二、关于义隆仿真器抗干扰问题。

EM78PXXX系列单片机都是OTP 型的,没有硬件仿真器就干不了活。

但别指望仿真器能完美再现单片机的的特性。

当你的仿真器电源与工作台灯或电烙铁共用一个电源插座时,问题就来了。

在运行仿真器进行模拟时,不论是开关台灯或是拔插电烙铁,保准让仿真器跑飞,不信试试。

话说回来,那些廉价的诸如JTAG,ISP,IAP接口的防真器也有同样的问题,但它们与义隆1千多元的仿真器相比相比毕竟廉价呀。

笔者曾用过一款力浦WICE-PIC 的PIC单片机仿真器,那才真叫芯片特性的“完美再现”用起来真爽。

三、关于TBL指令的使用。

EMP78系列单片机在使用TBL指令时必须经常检查TBL的地址范围,模拟器界面的主菜单中有此选项供参考。

四、内存中的09H(R9)和3FH(R3F)的地址是重叠的,EM78P447S 的09H这个空闲内存单元不能使用,否则将改变3FH的内容。

义隆78P153模拟2262接收

JBC P6,2

JMP JS1_SJ_9

CALL JS_DELAY

MOV A,R13

ADD A,@120

JBS R3,0

JMP JS1_SJ_8

JMP JS_OVER

JS1_SJ_9:

NOP

JBS P6,2

JMP JS1_SJ_8

MOV A,R13

;信号检测

;===========================================

JS:

BC R14,0 ;清14H.0

NOP

JBC P6,4

JMP JS1

NOP

JBC P6,4

JMP JS1

CLR R13 ;延时后的计数存储器

ADD A,@253

JBS R3,0

JMP JS_OVER

DJZ R16

JMP JS1_SJ_0

MOV A,R20

XOR A,R23

JBS R3,2

JMP JS_SJ_10

MOV A,R21

XOR A,R24

JBS R3,2

JMP JS_SJ_10

BC R22,7

JMP JS_SJ_7

JS_SJ_6:

RRC R22

RRC R21

RRC R20

BS R22,7

JS_SJ_7:

CLR R13

JS_SJ_8:

NOP

JBC P6,4

JMP JS_SJ_9

CALL JS_DELAY

MOV A,R13

JS_SJ_10:

MOV A,R20

EM78指令说明

串口基础

串口编程

电力线通信

蓝牙技术

Modem技术

2. AND 与

语法AND A,R

编码0 0010 10rr rrrr

操作A&R®A

对标志位影响Z

说明无

举例P6口和R10寄存器相与,结果输出至P6口:

综合技术

|

计算机应用

|

您现在的位置: 中国单片机在线网 >> 文章中心 >> 单 片 机 >> EMC >> 正文 用户登录 新用户注册

操作A+K®A

对标志位影响Z,C,DC

说明无

举例实现A=0X01+0X01:

MOV A,@0X01

ADD A,@0X01

充电器设计

电池

另类电源

变压器

稳压技术

广电技术

安防监控

AGAIN:

CLR 0

INC 0X04

MOV A, 0X04

XOR A, 0X3F

JBS 0X03, 2

JMP AGAIN

END:

2.4. 位寻址

ADD Reg_B, A ; add Reg_B with A, and

; save in Reg_B

... 等等。

(3)位操作型指令( bit oriented ): 如

BC,JBS...等等。

EM78指令说明 【字体:小 大】

EM78指令说明

作者:程序匠人 文章来源:不详 点击数:1156 更新时间:2004-11-26

义隆单片机EM78P153使用讲解

基于EM78P153S的应用设计(V1.0)目录第一章EM78P153S的初识 (1)1.1 EM78P152/3S特性 (1)1.2 EM78P152/3S引脚 (2)1.3 功能寄存器 (2)1.3.1 累加器与端口控制寄存器 (2)1.3.2中断状态寄存器与中断使能寄存器 (3)1.3.3 操作寄存器 (4)1.3.4 特殊功能寄存器 (6)1.4 数据存储器的配置 (7)1.5 休眠与唤醒 (7)1.6 分频器 (9)1.7 定时器/计数器TCC (9)第二章EM78系列单片机应用软件的编辑与仿真 (11)2.1 Simulator的下载与安装 (11)2.2 Simulator的使用方法 (11)2.3 Simulator系统常用命令汇总 (14)2.4 Simulator仿真中的常见问题 (15)第三章EM78系列单片机的汇编指令 (17)3.1 寻址方式 (17)3.2 伪指令 (18)3.3 指令速查表 (18)第四章EM78P153S应用软件设计 (20)4.1 外部中断程序 (20)4.2 花样灯程序 (22)4.2.1 设计需求 (22)4.2.2 软件设计 (23)4.2.3 硬件设计 (37)4.2.4 元器件明细表 (38)第五章EM78系列单片机应用程序的烧录 (39)5.1 程序的转换过程 (39)5.2 烧录器与烧录软件 (40)5.3 烧录步骤 (41)第一章 EM78P153S的初识EM78P152/3S是采用低功耗高速CMOS工艺设计开发的8位微控制器,它的内部有一个1024×13位一次性可编程只读存储器(OTP_ROM) ,可见1k的只读存储器(ROM)决定了应用程序不能够太多,否则应用程序机器码将无法烧录到芯片中。

硬件设计中,EM78P152/3S可以通过设置代码选项寄存器使微处理器工作在内部RC 振荡模式(IRC)下,此模式下采用上电复位模式而不需要外接时钟电路;同时利用上电自动复位而不需要外接复位电路,P63复位引脚可以直接作为输入脚使用,充分提高了微处理器端口的利用率,这样硬件应用电路极为简化,节省了硬件成本。

5.1.EM78 系列八位微控器特色指令用法

"BS","BC" 等指令会先有 "读" 再 "写" 的动作,例如 "bc 0x06,3" 指令是將整个 Port 6 (8 pin) 读進 CPU,执行位运算后再写至 Port 6 上。假如 Port 6 有一些 pin 是双向 I/O pin (如 P65) 時,假設当执行 "bc 0x06,3" 時P65 是输入 pin,則 P65 pin 上的内容会被读入再写至 Latch 上,覆蓋原先 Latch 上的内容。因此只要 P65 一直是输入 pin 將不会有問題,一旦 P65 切換为输出,則 Latch 上的内容將是不可預知的。

注意:

此例中 "05,假如沒有 "052" 这行指令,则程序将跳转至"050" 的位址 (在 PAGE 0中),如此將沒有达到預期的目的。

2. 不同 PAGE 子程序呼叫的方法:

如第 1 项所述,当程序超过 1K 時,执行 "call" 指令时,"PAGE 选择位" 的设定就必须加以考虑。下面將以 EM78256 为例来说明呼叫不同 PAGE 子程序的方法。

MOV 0X10, A ;设定计数值。计数寄存器

LOOP: ;为0X10。

;

;

;

DJZ 0X10 ;递減计数寄存器,若计数

JMP LOOP ;值为0,则跳出循环。

JMP FLAG_1 ;THEN

JMP FLAG_0 ;ELSE

FLAG_0:

深圳市瑞丰汇 EM78 系列单片机仿真系统说明书

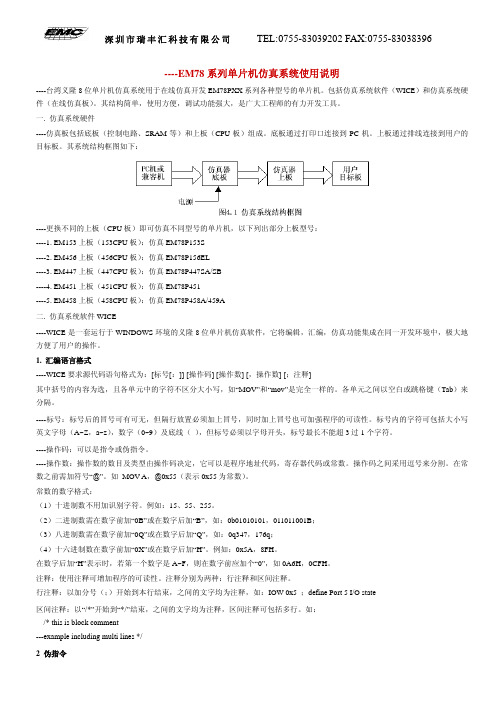

----EM78系列单片机仿真系统使用说明----台湾义隆8位单片机仿真系统用于在线仿真开发EM78PXX系列各种型号的单片机。

包括仿真系统软件(WICE)和仿真系统硬件(在线仿真板)。

其结构简单,使用方便,调试功能强大,是广大工程师的有力开发工具。

一. 仿真系统硬件----仿真板包括底板(控制电路、SRAM等)和上板(CPU板)组成。

底板通过打印口连接到PC机。

上板通过排线连接到用户的目标板。

其系统结构框图如下:----更换不同的上板(CPU板)即可仿真不同型号的单片机,以下列出部分上板型号:----1. EM153上板(153CPU板):仿真EM78P153S----2. EM456上板(456CPU板):仿真EM78P156EL----3. EM447上板(447CPU板):仿真EM78P447SA/SB----4. EM451上板(451CPU板):仿真EM78P451----5. EM458上板(458CPU板):仿真EM78P458A/459A二. 仿真系统软件WICE----WICE是一套运行于WINDOWS环境的义隆8位单片机仿真软件,它将编辑,汇编,仿真功能集成在同一开发环境中,极大地方便了用户的操作。

1. 汇编语言格式----WICE要求源代码语句格式为:[标号[:]] [操作码] [操作数] [,操作数] [;注释]其中括号的内容为选,且各单元中的字符不区分大小写,如“MOV”和“mov”是完全一样的。

各单元之间以空白或跳格键(Tab)来分隔。

----标号:标号后的冒号可有可无,但隔行放置必须加上冒号,同时加上冒号也可加强程序的可读性。

标号内的字符可包括大小写英文字母(A~Z,a~z),数字(0~9)及底线(_),但标号必须以字母开头,标号最长不能超3过1个字符。

----操作码:可以是指令或伪指令。

----操作数:操作数的数目及类型由操作码决定,它可以是程序地址代码,寄存器代码或常数。

义隆中文资料EM78P153S中文

8位OTP 微控制器产品规格书1.8义隆电子股份有限公司2009.09本文内容是由英文规格书翻译而来,目的是为了您的阅读更加方便。

它无法跟随原稿的更新,文中可能存在翻译上的错误,请您参考英文规格书以获得更准确的信息。

商标告知:IBM 为一个注册商标,PS/2是IBM 的商标之ㄧ.。

Windows 是微软公司的商标。

ELAN 和ELAN 标志 是义隆电子股份有限公司的商标。

版权所有 © 2003~2009 义隆电子股份有限公司所有权利保留台湾印制本规格书内容如有变动恕不另作通知。

关于该规格书的准确性、适当性或者完整性,义隆电子股份有限公司不承担任何责任。

义隆电子股份有限公司不承诺对本规格书之内容及信息有更新及校正之义务。

本规格书的内容及信息将为符合确认之指示而变更。

在任何情况下,义隆电子股份有限公司对本规格书中的信息或内容的错误、遗漏,或者其它不准确性不承担任何责任。

由于使用本规格书中的信息或内容而导致的直接,间接,特别附随的或结果的损害, 义隆电子股份有限公司没有义务负责。

本规格书中提到的软件(如果有),都是依据授权或保密合约所合法提供的,并且只能在这些合约的许可条件下使用或者复制。

义隆电子股份有限公司的产品不是专门设计来应用于生命维持的用具,装置或者系统。

义隆电子股份有限公司的产品不支持而且禁止在这些方面的应用。

未经义隆电子股份有限公司书面同意,任何个人或公司不得以任何形式或方式对本规格书的内容之任一部分进行复制或传输。

义隆电子股份有限公司 总公司:地址:台湾新竹科学园区创新一路12号电话:+886 3 563-9977 传真:+886 3 563-9966 webmaster@ http ://香港分公司:义隆电子(香港)有限公司九龙观塘巧明街95号世达中心19楼A 室电话:+852 2723-3376 传真:+852 2723-7780USA:Elan InformationTechnology Group (USA) P .O. Box 601Cupertino, CA 95015 USATel : +1 408 366-8225 Fax : +1 408 366-8225 Korea:Elan Korea ElectronicsCompany, Ltd. 301 Dong-A Building 632 Kojan-Dong, Namdong-kuIncheon City, KOREA Tel : +82 32 814-7730 Fax : +82 32 813-7730深圳分公司:义隆电子(深圳)有限公司地址:深圳市高新技术产业园南区高新南一道国微大厦3F 邮编:518057电话:+86 755 2601-0565 传真:+86 755 2601-0500 elan-sz@上海分公司:义隆电子(上海)有限公司地址:上海市浦東新區張江高科畢升路289弄3號101室 邮编:201203电话:+86 21 5080-3866 传真:+86 21 5080-0273 elan-sh@Contents目录1综述 (1)2 产品特性 (1)3 引脚分配 (2)4 引脚描述 (3)4.1 EM78P153S (3)4.2 EM78P152S (4)5 功能描述 (5)5.1操作寄存器 (5)5.1.1 R0 (间接寻址寄存器) (5)5.1.2 R1 (定时/计数器) (5)5.1.3 R2 (程序计数器) & 堆栈 (5)5.1.4 R3 (状态寄存器) (7)5.1.5 R4 (RAM 选择寄存器) (8)5.1.6 R5 ~ R6 (Port 5 ~ Port 6) (8)5.1.7 RF (中断状态寄存器) (8)5.1.8 R10 ~ R2F (8)5.2特殊功能寄存器 (9)5.2.1 A (累加器) (9)5.2.2 CONT (控制寄存器) (9)5.2.3 IOC5 ~ IOC6 (I/O 端口控制寄存器) (9)5.2.4 IOCB (下拉控制寄存器) (10)5.2.5 IOCC (漏极开路控制寄存器) (10)5.2.6 IOCD (上拉控制寄存器) (10)5.2.7 IOCE (看门狗定时器控制寄存器) (11)5.2.8 IOCF (中断屏蔽寄存器) (11)5.3 TCC/WDT & 预分频器 (12)5.4 I/O 端口 (12)5.5 复位和唤醒 (15)5.5.1 复位 (15)5.5.2 寄存器初始值总结 (17)5.5.3 状态寄存器的RST,T和 P的状态 (19)5.6 中断 (20)5.7 振荡器 (21)5.7.1 振荡模式 (21)5.7.2 晶体振荡器/陶瓷谐振器 (晶体) (22)5.7.3 外部 RC 振荡模式 (23)5.7.4 内部 RC 振荡模式 (24)5.8 代码选项寄存器 (25)Contents5.8.1 代码选项寄存器(Word 0) (25)5.9 上电探讨 (27)5.10 编程设置振荡器启动时间 (27)5.11 外部上电复位电路 (27)5.12 残留电压保护 (28)5.13 指令集 (28)6最大绝对值 (31)7 电气特性 (32)7.1 直流电气特性( Ta= 0°C ~ 70 °C, VDD= 5.0V±5%, VSS= 0V ) (32)7.2 交流电气特性(Ta=0°C ~ 70 °C, VDD=5V±5%, VSS=0V) (33)8 时序图 (34)附录A 封装类型 (35)B 封装信息 (36)C 器件特性 (39)数据手册修订历史1.1 初版1.2 修改初始寄存器值、内部RC偏移率、DC和AC电气特性2003/05/021.3 修改上电复位部分内容2003/06/251.4 在6.3节增加器件特性2003/12/311.5 在产品特性中增加IRC偏移率2006/01/161.6 增加EM78P152S SSOP 10引脚封装类型2007/03/051.7 1.修改EM78P152S 10-pin SSOP封装名称;2.在振荡器章节里面增加陶瓷振荡器;3.修改程序计数器章节内容;4.修改特殊功能寄存器IOCC。

义隆单片机 EM78P153_C语言范例

static io unsigned int IMR

@0x0F:iopage 0; //Interrupt Mask Register

/*======================================================;

; Special Purpose Registers Define

@0x05:iopage 0; @0x06:iopage 0; @0x0B:iopage 0; //Push-down Control Register @0x0C:iopage 0; //Open-drain Control Register @0x0D:iopage 0; //Push-high Control Register @0x0E:iopage 0; //WDT Control Register @0x0F:iopage 0; //Interrupt Mask Register

;

; ======================================================;

;

; A: Accumulator

; It can't be addressed.

;

; CONT: Control Register

;

;{

mINT == 0x40 ; Interrupt enable flag

static io unsigned int P5CR @0x05:iopage 0;//Port5 Control Register static io unsigned int P6CR @0x06:iopage 0;//Port6 Control Register static io unsigned int PDCR @0x0B:iopage 0; //Push-down Control Register

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于EM78P153S的应用设计(V1.0)目录第一章EM78P153S的初识 (1)1.1 EM78P152/3S特性 (1)1.2 EM78P152/3S引脚 (2)1.3 功能寄存器 (2)1.3.1 累加器与端口控制寄存器 (2)1.3.2中断状态寄存器与中断使能寄存器 (3)1.3.3 操作寄存器 (4)1.3.4 特殊功能寄存器 (6)1.4 数据存储器的配置 (7)1.5 休眠与唤醒 (7)1.6 分频器 (9)1.7 定时器/计数器TCC (9)第二章EM78系列单片机应用软件的编辑与仿真 (11)2.1 Simulator的下载与安装 (11)2.2 Simulator的使用方法 (11)2.3 Simulator系统常用命令汇总 (14)2.4 Simulator仿真中的常见问题 (15)第三章EM78系列单片机的汇编指令 (17)3.1 寻址方式 (17)3.2 伪指令 (18)3.3 指令速查表 (18)第四章EM78P153S应用软件设计 (20)4.1 外部中断程序 (20)4.2 花样灯程序 (22)4.2.1 设计需求 (22)4.2.2 软件设计 (23)4.2.3 硬件设计 (37)4.2.4 元器件明细表 (38)第五章EM78系列单片机应用程序的烧录 (39)5.1 程序的转换过程 (39)5.2 烧录器与烧录软件 (40)5.3 烧录步骤 (41)第一章 EM78P153S的初识EM78P152/3S是采用低功耗高速CMOS工艺设计开发的8位微控制器,它的内部有一个1024×13位一次性可编程只读存储器(OTP_ROM) ,可见1k的只读存储器(ROM)决定了应用程序不能够太多,否则应用程序机器码将无法烧录到芯片中。

硬件设计中,EM78P152/3S可以通过设置代码选项寄存器使微处理器工作在内部RC 振荡模式(IRC)下,此模式下采用上电复位模式而不需要外接时钟电路;同时利用上电自动复位而不需要外接复位电路,P63复位引脚可以直接作为输入脚使用,充分提高了微处理器端口的利用率,这样硬件应用电路极为简化,节省了硬件成本。

此外,EM78P153S单片机具有休眠模式,在一些不需要微处理器实时工作的应用场合,可以节省用电量,特别是在使用电池供电时,应用此模式可以延长电池的使用时间;另外在休眠模式下避免了微处理器在运行时受到来自外在杂波信号的干扰而导致程序跑飞。

1.1 EM78P152/3S特性EM78P152/3S的性能如表1.1所示。

1.2 EM78P152/3S 引脚EM78P152/3S 的引脚图如图1.1,引脚功能如表1.2所示。

表1.2 EM78P152/3S 引脚功能表引脚名称 序号类型 功能备注 P50~P53 1、12、13、14 I/O *通用的I/O 引脚P60~P62 P64~P67 2、3、5 6、8、9、10I/O *通用的I/O 引脚*引脚状态发生改变时,从休眠模式唤醒 *可以设置为上拉P60/INT 10 I/O *下降沿触发的外部中断引脚 P62/TCC 8 I/O *外部定时/ 计数器信号输入引脚 P63/RESET 7 I *若设置/RESET 引脚并使其保持逻辑低,器件将产生复位 *引脚状态改变时,从休眠模式唤醒 * P63 仅用作输入引脚 P64、P65 5、6 I/O *外部时钟信号输入*晶体振荡器的输入引脚VDD 4 — *电源正极 VSS11—*电源地1.3 功能寄存器期望微处理器按预期的性能工作,就需要对功能寄存器进行有效的定义,这也是汇编编程初始化的基本任务。

针对EM78P153单片机,在汇编程序编写中,使用频率相对较高的寄存器有累加器A 、I/O 端口控制寄存器IOC5~IOC6、中断状态寄存器(RF )、中断使能寄存器(IOCF)。

1.3.1 累加器与端口控制寄存器[示例1]端口数值的传送(读取一个端口的值送给另一个端口)。

源程序如下:;*****************************************************;DIP 输入,LED 输出;*****************************************************图1.1 EM78P152/3S 引脚图 EM78P153SP/N/S/J EM78P152SP/N/S/Jled==6 ;定义显示端口的地址为6org 0x00 ;定义程序存放区的起始地址jmp main ;跳转到主程序org 0x50 ;声明主程序开始地址main: mov a,@0x00;iow led ;设定显示端口引脚全部输出mov a,@0xff;iow dip ;设定dip端口全部为输入loopcoma dip ;读取dip状态并取反送amov led,a ;传送到端口6上面显示jmp loop ;循环回去;*****************************************************end ;告知汇编器源程序结束1、累加器A累加器A用于内部数据传送或指令操作数暂存,它不可被寻址。

寄存器之间的数据传递需要通过累加器A来过渡,即寄存器先传送给A再由A传送给另一个寄存器。

2、I/O 端口控制寄存器IOC5 ~ IOC6I/O 端口控制寄存器IOC5 ~ IOC6:为“1”时,相关I/O 引脚置为高阻态(输入);为“0”时,相关I/O 引脚置为输出。

IOC5 寄存器仅低4 位可被有效定义,IOC5 和IOC6 均为可读/写寄存器。

1.3.2中断状态寄存器与中断使能寄存器[示例2]將寄存器0x20当做计数器,每当外部中断产生,就自动加1。

源程序如下:;*****************************************************;P60/INT外部中断;將寄存器0x20当做计数器,每当外部中断产生,就自动加1;*****************************************************ORG 0x00 ;定义程序存放区的起始地址CLR 0x20 ;清除计数器JMP EXT_PRO ;跳转到主程序ORG 0x08 ;中断的入口地址INT_EXT:DISI ;使能中断CLR 0x0F ;清除中断状态寄存器的标志位INC 0x20 ;计数器加1RETI ;返回主程序ORG 0x50 ;主程序的开始地址EXT_PRO: CLR 0x0F ;清除标志位MOV A,@0x04 ;使能外部中断信号产生IOW 0x0F ;把A的内容送给0x0FMOV A,@0x40 ;定义P60为外部中断引脚IOW 0x0EENI ;开总中断EXT_WAIT: N OPNOPJMP EXT_WAIT ;循环等待外部中断END ;汇编器源程序结束1、中断状态寄存器(RF)中断状态寄存器(RF)地址0x0F,它反映三种中断标志情形,硬件自动置1,均需要通过软件的方式清0,以清除中断标志。

RF各位的含义如表1.3所示。

其中:Bit 2(EXIF) :外部中断标志位,/INT管脚输入下降沿时置“1”,由软件清“0”;Bit 1(ICIF):端口6输入状态改变标志位,输入状态改变时置“1”,由软件清“0”;Bit 0(TCIF):TCC 溢出中断标志位,TCC 溢出时置“1”,由软件清“0”。

2、中断使能寄存器(IOCF)中断使能寄存器(IOCF)地址0x0F,与中断状态寄存器共用一个地址,它反映三种中断的开启与关闭,在程序运行每个指令周期中,硬件自身判断中断使能位,当中断使能位为1时响应相应中断,同时在中断服务程序中务必清中断状态寄存器的相应标志位为0。

IOCF各位的含义如表1.4所示。

中断ICIF使能位;Bit 0 (TCIE)是定时溢出中断TCIF使能位。

1.3.3 操作寄存器1、间接寻址寄存器R0R0 并非实际存在的寄存器,它的主要功能是作为间接寻址指针,任何以R0为指针的指令,实际上是对RAM选择寄存器R4所指向地址的数据内容进行操作。

2、定时/计数器R1(1)TCC引脚的外部信号边沿或内部指令周期时钟触发( 由CONT寄存器的TE位设定) ,会使TCC寄存器加1;(2)像其它寄存器一样可读/写;(3)通过复位PAB 位(CONT-3) 设定;(4)如果PAB bit (CONT-3) 被复位,预分频器分配给TCC;(5)写入一个值到TCC寄存器后,TCC计数器的内容会被刷新。

3、程序计数器R2&堆栈一个程序页为1024字长。

在程序编译调试时,可以通过查看R2的值,判断程序是否跳转正常,或者通过对比某个程序的入口判断是否进入某个函数。

“JMP”指令直接加载程序计数器的低10位,因此,“JMP”允许PC跳转到一个程序页的任何位置。

“CALL”指令首先加载PC的低10位,然后将PC+1推入堆栈,因此,子程序的入口地址可位于一个程序页的任何位置。

正常情况下,所有指令均是单指令周期(一个指令周期包含2个振荡周期) ,但改变程序计数器(R2寄存器)内容的指令,均为2个指令周期。

EM78P153S有五级堆栈,这就决定了在程序编写的时候,子程序的嵌套调用不能够超过5次,否则编译会出错。

4、状态寄存器R3(程序)状态寄存器R3的地址为0x03,如表1.5所示。

5、RAM 选择寄存器R4:I/O 寄存器,仅低4位可用。

6、端口5寄存器R5:I/O 寄存器,引脚都为I/O口。

7、端口6寄存器R6:I/O 寄存器,除P63仅用作输入引脚外,其它引脚都为I/O口。

8、R10—R2F:所有这些寄存器均为8 位通用寄存器。

1、控制寄存器CONT控制寄存器CONT各位定义如表1.6所示。

2、下拉控制寄存器IOCB、漏极开路控制寄存器IOCC、上拉控制寄存器IOCD下拉控制寄存器IOCB各位定义如表1.7所示。

入口使用时,只需要考虑是否上拉或者下拉;当某端口作为输出口使用时,则考虑是否开漏极输出。

端口采用内部上拉,可以减少外部对引脚电平的干扰,如果要实现检测某端口是否为低电平的功能,则必须设置为内部上拉,若该端口没有上拉功能,则需要外部加上拉电阻。

端口采用内部下拉,理论上可以减少外部对引脚电平的干扰,但是实际的测试效果不明显,和没有设置下拉的效果一样。

所以如果端口设置为内部下拉,该端口只可以用于检测高电平,但是在没有输入的情况下,该引脚的电平并没有变为1V以下,不能看作真正的低电平。

合,输出的高电平将达不到VDD电压值。

5、看门狗定时器控制寄存器IOCE看门狗定时器控制寄存器IOCE各位定义如表1.10所示。

1.4 数据存储器的配置通过了解数据存储器的分布,可以在仿真时直接了解各个寄存器的状态以及程序运行情况,数据存储器的配置如表1.11所示。