集成电路封装设计的可靠性提高方法研究

集成电路制造中的可靠性设计与测试研究

集成电路制造中的可靠性设计与测试研究一、背景介绍随着电子技术的不断发展,集成电路已成为现代电子产品中的核心部件,集成电路的可靠性是保证电子产品正常运行的关键因素之一。

因此,在集成电路制造过程中,可靠性设计与测试是极为重要的工作之一。

二、可靠性设计1、产品设计阶段中的可靠性设计在产品设计阶段,可靠性设计包括确定可靠性指标、进行可靠性分析、制定可靠性设计规范等。

可靠性指标包括寿命、故障率、可靠度等。

通过可靠性分析,可以确定关键部件和系统的故障模式,进而通过设计保证其可靠性。

可靠性设计规范则是保证产品可靠性的重要手段之一,规范包括环境适应性、可靠性测试、可靠性分析等方面。

2、工艺流程中的可靠性设计在工艺流程中,可靠性设计包括选择适合的工艺和材料、制订可靠性工艺规范等。

要确保产品在制造过程中不会出现缺陷,需要采用裂解工艺、新型生长材料等技术,并制定标准的工艺流程,以确保产品可靠性。

三、可靠性测试1、可靠性检测技术集成电路制造中的可靠性测试技术包括环境应力测试、加速试验、可靠性评估等。

其中,环境应力测试是常见的可靠性测试方法,其目的是通过模拟极端条件来评估产品在使用过程中的可靠性。

加速试验则是在限定时间内模拟产品的寿命,以评估产品的可靠性。

可靠性评估则通过不同的数据收集、分析方法来评估产品的可靠性水平。

2、测试流程与系统设计在测试流程中,需要综合考虑各个阶段的测试数据和分析结果,对产品的可靠性水平进行评估。

同时,测试系统的设计也是非常关键的,在设计中需要考虑测试设备的精度、可靠性、稳定性等因素,同时还需要将产品应力状态的监测和数据采集等功能纳入到测试系统中。

四、结论在集成电路制造过程中,可靠性设计与测试是确保产品质量和可靠性的重要手段,可以减少产品故障率,提高产品稳定性和寿命。

因此,随着电子产品市场的不断扩大,集成电路制造中的可靠性设计与测试也会变得越来越重要。

超大规模集成电路可靠性设计与分析

超大规模集成电路可靠性设计与分析随着现代社会科技的不断发展,尤其是先进的制造工艺和设计方法的出现,超大规模集成电路(Very Large Scale Integration,VLSI)已经成为了当今电子信息领域的主流。

现代电子产品中的大多数电路都是通过将海量的晶体管等离子器件集成在一个小小的芯片上实现的。

然而,这种紧密的集成也带来了一个非常重要的问题:芯片的可靠性。

在过去的几年中,芯片的可靠性一直是材料科学和微电子工程领域的重要研究课题。

芯片可靠性的影响因素主要包括环境因素、使用条件、制造工艺等多个方面。

这些因素一旦引起芯片的失效,就会严重影响电子产品的工作效率并导致相关故障。

因此,越来越多的研究者开始关注如何提高芯片的可靠性,以保证电子产品的稳定性。

芯片失效机理超大规模集成电路的失效机理主要分为三类:电学失效、热失效和机械失效。

其中,电学失效包括场效应管击穿、介质击穿和极化强度等,通常是芯片的电气参数超过了其最大值或最小值而导致。

热失效则是由于芯片长时间运行过程中所产生的热失效,其中最常见的故障是封装和散热系统的失效以及氧化等,这些故障使得芯片的温度升高,从而引起芯片零部件的物理或化学变化,最终导致失效。

机械失效则是由于芯片本身结构的反复变形和应力过大等原因所引起的。

另外,也存在其他的失效模式,如磨损、腐蚀、放电和辐射等。

质量原则为了提高超大规模集成电路的可靠性,研究者们制定了一系列的质量原则。

这些原则主要包括以下三个方面:1.设计原则:设计人员应从芯片的可靠性角度去考虑设计方案。

他们应该遵循设计规范并避免潜在的失效机制。

例如,考虑到减小芯片的散热、优化电路结构、按规范进行封装等措施都应该采取。

2.质量控制原则:在芯片制造过程中,应该建立严密的质量控制系统,尽可能地避免缺陷扩散和标准的失效机制。

同时,在制造前应该对制造工艺进行严密的质量管理和检测,以保证每一批芯片的质量。

3.可靠性测试原则:对于新设计的芯片,应该进行可靠性测试以评估其可靠性,以防止潜在的问题。

集成电路可靠性设计方法与技巧

集成电路可靠性设计方法与技巧随着科技的不断进步,集成电路可靠性设计成为一个备受关注的话题。

集成电路可靠性是指电子元器件工作在设备使用环境下,能够在一定的时间内保持指定的性能指标的能力。

集成电路可靠性设计可以提高电路的寿命和可靠性,降低故障率。

集成电路可靠性设计方法与技巧有很多,下面将逐一进行探讨。

首先,选用合适的工艺是关键。

不同工艺的封装会对电路的使用寿命和可靠性产生很大的影响。

因此,在进行可靠性设计时,需要充分了解不同工艺的特点,选用适合的工艺。

其次,保证电路的制造质量。

良好的制造质量是提高电路可靠性的关键因素之一。

在生产过程中,需要对每一道工序进行严格的控制,做到全流程监控。

在生产完毕后,需要对产品进行全面的测试,确保产品的质量符合要求。

再次,优化电路设计。

电路设计的思路和方法直接影响电路的可靠性和使用寿命。

合理的电路结构能够最大化地降低电路的故障率。

要做到这一点,需要对电路进行全面的分析和优化设计。

在设计过程中,应尽可能考虑电路的可靠性,避免过多的冗余、复杂的设计方案,从而提高电路的稳定性和可靠性。

此外,可靠性测试也是一项重要的工作。

在测试中,需要对电路的各项指标进行全面的检测和评估,如温度、湿度、振动等。

通过建立可靠性模型和进行仿真模拟,可以尽可能地模拟各种极端环境下电路的使用情况,从而提高电路的可靠性和寿命。

最后,及时进行维护和保养。

无论是工业设备还是普通家电,使用过程中难免会出现一些故障,需要及时进行维护和保养。

在进行维护和保养时,需要对电路进行全面的检查和维修,确保电路运行稳定、可靠。

同时,应制定科学合理的保养计划,对电路进行定期维护和检查,延长电路的使用寿命。

在进行集成电路可靠性设计时,需要综合运用各种方法和技巧,从多个方面进行优化,提高电路的可靠性和使用寿命。

需要强调的是,可靠性设计需要贯穿整个开发过程,需要在设计、生产、测试、维护等各个环节加以实施,同时需要注重电路制造质量的控制,确保设计、生产、测试等各个环节的质量达到最佳水平。

微电子封装中的可靠性设计与优化研究

微电子封装中的可靠性设计与优化研究微电子封装是现代电子技术中重要的环节,可靠性是该领域研究的关键问题。

本文将从可靠性设计与优化的角度出发,探讨微电子封装中的可靠性问题,并提出相应的研究方向和优化策略。

一、微电子封装中的可靠性问题微电子封装是将微电子芯片、集成电路与外部介质进行物理连接和保护的过程。

在封装过程中,由于温度、湿度、机械应力等外部环境因素的影响,以及封装材料的特性限制,微电子封装可能存在以下可靠性问题:1. 焊接可靠性:封装过程中,焊接是连接芯片和外部引脚的重要方式。

焊点的质量直接影响到整个封装的可靠性。

焊点可能出现冷焊、开裂、疏松等问题,从而引起芯片与引脚的断裂,甚至导致器件失效。

2. 热传导问题:微电子封装中,芯片产生的大量热量需要通过封装材料传导和散热。

若散热不良,会导致芯片温度过高,降低器件的可靠性和寿命。

3. 封装材料的降解:封装材料因长期暴露在恶劣环境下,可能会出现老化、腐蚀、电学性能下降等问题,进而影响封装的可靠性和性能。

4. 微结构效应:微电子封装中,芯片和封装材料之间存在微结构效应,如针对封装材料的热膨胀系数不匹配,可能引起应力集中,导致微裂纹的产生和扩展,最终导致器件失效。

二、可靠性设计与优化的研究方向针对微电子封装中的可靠性问题,需要进行可靠性设计与优化的研究。

以下是几个研究方向的介绍:1. 封装材料的选择与设计:选择合适的封装材料对于提高微电子封装的可靠性至关重要。

研究人员需要综合考虑材料的热导率、机械强度、阻尼特性等因素,设计出能够满足封装要求并具备良好可靠性的材料。

2. 计算机辅助工程与模拟仿真:借助计算机辅助工程软件和模拟仿真技术,可以对微电子封装进行虚拟建模和仿真分析。

通过分析封装过程中的热传导、应力分布等问题,提前发现潜在的可靠性问题,并采取相应措施进行改进。

3. 焊接工艺的优化:焊接是微电子封装过程中容易产生可靠性问题的环节之一。

优化焊接工艺参数,控制熔化焊料的温度、时间、流动性等因素,能够降低焊接过程中的应力和热应变,提高焊接的可靠性。

集成电路tsv三维封装可靠性试验方法指南

集成电路tsv三维封装可靠性试验方法指南下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!集成电路TSV三维封装可靠性试验方法指南1.前言在当今集成电路领域,TSV(ThroughSilicon Via)三维封装技术已经成为一种重要的封装方式。

集成电路封装测试工艺流程优化研究

集成电路封装测试工艺流程优化研究集成电路封装测试工艺是电子制造行业中的一项重要环节,主要涉及封装测试过程中的工艺流程与优化方法。

本文将对集成电路封装测试工艺流程进行详细研究与分析,探讨如何优化该工艺流程,以提高封装测试的效率和质量。

一、集成电路封装测试工艺流程概述集成电路封装测试工艺流程是指将芯片封装至封装器件中,并进行测试的过程。

其主要包括以下几个环节:芯片封装准备、封装器件制备、封装器件测试、封装器件封装和封装器件测试。

1. 芯片封装准备:将芯片准备好,包括对芯片进行清洗、切割、打磨和测试等工艺过程。

2. 封装器件制备:将芯片封装至封装器件中。

这一过程主要包括粘贴芯片、焊接引线、封装胶固化等步骤。

3. 封装器件测试:对封装好的器件进行测试,包括电性能测试、温度测试、可靠性测试等。

4. 封装器件封装:将封装好的器件进行封装,包括封装胶固化、器件封装排列等。

5. 封装器件测试:对封装好的器件进行再次测试,以验证封装质量和性能。

二、集成电路封装测试工艺流程优化方法1. 工艺流程优化:通过优化封装测试工艺流程,可以提高生产效率和降低成本。

例如,合理安排工艺顺序,减少重复操作和不必要的环节;采用自动化设备和智能化系统,提高生产线的自动化程度和生产效率。

2. 设备优化:选择合适的封装测试设备,提高设备的稳定性和精度。

同时,对设备进行定期维护和保养,确保设备处于良好的工作状态。

3. 工艺参数优化:通过调整工艺参数,优化封装测试过程中的温度、湿度、压力等参数,以保证良好的工艺控制和产品质量。

4. 质量控制优化:建立完善的质量控制体系,严格按照质量标准进行检验,及时发现和纠正工艺中的问题,确保封装测试的产品质量。

5. 数据分析优化:通过对封装测试过程中的数据进行分析,及时发现异常和问题,并采取相应的措施进行调整和改进。

三、集成电路封装测试工艺流程优化的意义优化集成电路封装测试工艺流程的意义主要体现在以下几个方面:1. 提高生产效率:通过优化工艺流程,减少重复操作和不必要的环节,提高生产效率,降低生产成本。

高性能集成电路设计与优化技术研究

高性能集成电路设计与优化技术研究高性能集成电路(High Performance Integrated Circuit,简称HPIC)是在半导体技术和电子智能化技术的基础上发展起来的,具有强大的功能、高精度、高效能、高可靠性等特点,被广泛应用于计算机、通信、消费电子等领域。

随着信息技术的不断发展,HPIC的设计和优化技术也越来越受到人们的关注。

本文就HPIC设计和优化技术进行探讨。

一、HPIC的设计技术1. CMOS工艺CMOS工艺是当前最常用的集成电路制造工艺,它具有低功耗、高速度和高可靠性的特点。

在CMOS工艺的基础上,可以制造出大规模集成电路(Large Scale Integrated,简称LSI)和超大规模集成电路(Very Large Scale Integrated,简称VLSI),实现集成度的不断提高。

同时,CMOS工艺还具有可控工艺和低成本的特点,这使得CMOS工艺被广泛应用于HPIC的制造中。

2. 电路设计电路设计是HPIC设计的核心部分。

其中包括模拟电路设计、数字电路设计、混合信号电路设计等方面。

在电路设计的过程中,需要考虑诸多因素,如电路结构、电路参数、电路噪声等等。

为了保证电路设计的准确性和高性能,需要使用电路仿真软件对电路进行仿真分析,从而找出电路存在的问题,并进行优化改进。

3. 物理设计物理设计是HPIC设计中的重要环节,它主要涉及到电路布局和电路布线。

物理设计的目的是使电路的布局和布线尽可能紧凑,从而提高电路的性能和可靠性。

在物理设计的过程中,需要考虑电路信号传输的时延、电路功率消耗、电路噪声等等因素。

二、HPIC的优化技术1. 时钟优化时钟优化是HPIC优化中的一个重要部分,它可以提高HPIC电路的性能和可靠性。

时钟优化的基本思想是降低时钟延迟和时钟抖动,从而使电路的时钟频率提高,从而提高电路的运行速度和可靠性。

时钟优化需要结合多种优化方法,如时钟缓冲器设计、时钟树设计等等。

微电子封装技术中的可靠性设计与分析

微电子封装技术中的可靠性设计与分析第一章:引言随着微电子技术的迅猛发展,封装技术作为微电子技术中至关重要的一环,对于保证芯片的可靠性和稳定性起着关键作用。

本文将对微电子封装技术中的可靠性设计与分析进行探讨和研究。

第二章:微电子封装技术概述微电子封装技术是将芯片与外部环境隔离,并提供保护和连接功能的一种技术。

该技术可以分为无源封装和有源封装两大类,其中无源封装主要用于电子元器件或被动元件,有源封装主要用于集成电路芯片等。

第三章:微电子封装技术中的可靠性设计在微电子封装技术中,可靠性是至关重要的设计指标。

可靠性设计需要从以下几个方面考虑:1. 热管理:合理设计散热结构,保证芯片工作温度的稳定和可控;采用热传导材料和散热装置,有效地降低芯片温度,提高其可靠性。

2. 电磁兼容性:合理设计封装结构,以减少电磁干扰对芯片性能的影响;采用电磁屏蔽措施,提高封装结构对电磁波的屏蔽能力。

3. 机械可靠性:针对不同的应用场景和环境,选择合适的封装材料和结构,以提高封装的机械强度和抗震性能。

4. 寿命预测:通过可靠性测试和模拟,对封装结构进行寿命预测和分析,以预测其在实际使用中的可靠性水平。

第四章:微电子封装技术中的可靠性分析方法对于微电子封装技术中的可靠性分析,可以采用以下几种方法:1. 应力分析:通过应力分析软件模拟封装结构在不同工作状态下的应力分布情况,以评估其结构的强度和稳定性。

2. 可靠性测试:采用加速寿命测试方法,对封装结构进行长时间高负荷的可靠性测试,以评估其在实际使用中的寿命和可靠性水平。

3. 故障分析:对实际使用中出现的封装结构失效进行系统的故障分析,找出导致失效的原因,并采取相应的改进措施。

第五章:案例研究通过对几个典型的微电子封装技术案例进行研究,分析其可靠性设计和分析方法的应用效果,以及相应的问题和改进措施。

第六章:总结与展望本文对微电子封装技术中的可靠性设计与分析进行了系统的探讨和研究。

通过合理的设计和分析方法,可以提高微电子封装技术的可靠性和稳定性,为微电子工程提供更可靠的基础。

集成电路设计的可靠性研究

集成电路设计的可靠性研究随着科技不断进步,人们对电子产品的需求越来越大,而集成电路作为电子产品中的核心组件,其可靠性更是备受重视。

在集成电路设计中,可靠性是指电路在正常运行中不会出现故障,具有一定的寿命和稳定性。

而如何提高集成电路的可靠性,一直是电子工程领域研究的重点。

一、集成电路设计的主要问题在集成电路设计中,主要存在以下几个问题:1. 氧化层缺陷:氧化层是集成电路中的重要层之一,作为隔离层,可减少晶体管之间的干扰。

但是当氧化层存在缺陷时,会导致集成电路的漏电流不稳定,从而影响其可靠性。

2. 热应力问题:在集成电路的制造过程中,由于原始材料的热膨胀系数不同,不同部分的温度变化也不同,从而产生热应力。

这种热应力会导致晶体管上的氧化层被拉伸,最终导致氧化层剥离与漏电。

3. 磁性问题:磁场可以影响到集成电路中的晶体管与其他元件,从而导致数据误差或者设备不稳定。

4. 随机波动:由于电子元件本身会存在随机的波动,如输入噪声等,因此集成电路也会存在一定程度的随机波动,这种波动同样也会对集成电路的可靠性产生影响。

二、提高集成电路设计的可靠性为了提高集成电路的可靠性,可以从以下几个方面入手:1. 优化设计:在集成电路的设计过程中,需要采用优质的材料,尽量减少内部的缺陷与不平衡现象,并严格控制加工过程中的温度与时间,来保证器件的稳定性。

2. 强化封装:为了保护集成电路中的晶体管与其他元件,需要采用符合要求的包装材料来封装集成电路,以增加其抗热、防震、防湿的能力。

3. 优化工艺:为了减少磁场干扰以及随机波动,可以采用优化的加工工艺,如减少磁性材料的使用、加强屏蔽性能、优化底片制造等方式来提高集成电路的可靠性。

4. 加强检测:为了保证集成电路设计的可靠性,需要在制造的各个环节进行严格的检测与测试,以确保产品的合格率与稳定性。

以上这些方法虽然在实际操作中存在一定的难度,但是随着人们对电子产品可靠性要求的提高,集成电路设计的可靠性必将得到更为广泛的关注和重视。

集成电路封装工艺(毕业学术论文设计)

集成电路封装工艺(毕业学术论文设计)本文旨在介绍集成电路封装工艺的重要性和研究背景,以及阐述本论文的目的和结构安排。

集成电路是现代电子技术中的关键组成部分,其封装工艺对于保护集成电路的完整性和性能至关重要。

随着集成电路的不断发展,封装工艺的研究和优化变得越发重要。

本论文旨在研究集成电路封装工艺的相关技术和方法,以提高封装工艺的效率和可靠性。

本论文的结构安排如下:引言:介绍集成电路封装工艺的重要性和研究背景,说明本论文的目的和结构安排。

相关工艺:介绍集成电路封装工艺的基本概念和技术,包括封装材料、封装方法等。

封装工艺优化:探讨封装工艺中存在的问题和挑战,并提出相应的优化策略和方法。

实验与结果:介绍针对集成电路封装工艺的实验设计和实验结果分析,验证优化策略的有效性。

结论:总结论文的主要研究内容、取得的成果以及未来可能的研究方向。

希望通过本论文的研究,能够对集成电路封装工艺的优化和发展提供有益的参考和指导。

本文详细介绍集成电路封装工艺的定义、组成和基本流程,包括设计、布局、封装材料选择、封装技术等内容。

集成电路封装工艺是将裸露的集成电路芯片封装在一个外部封装材料中,以提供保护和连接功能的一种技术。

它是集成电路制造过程中不可或缺的一环。

封装工艺的组成部分包括设计、布局、封装材料选择和封装技术。

设计集成电路封装工艺的设计阶段涉及到确定芯片封装的物理特性和封装类型。

封装设计需要考虑到芯片的尺寸、引脚数量、电气性能、散热需求等因素。

布局封装布局是将芯片和周围器件的引脚连接起来的过程。

在布局阶段,需要精确安排引脚的位置和间距,以确保信号传输效果和封装可靠性。

封装材料选择在选择封装材料时,需要考虑到材料的导热性能、机械强度、耐化学性等因素。

常用的封装材料包括塑料、陶瓷和金属等。

封装技术封装技术涉及到将芯片与封装材料进行物理连接的过程。

常见的封装技术包括焊接、黏贴、球栅阵列(BGA)等。

集成电路封装工艺的基本流程包括设计、布局、材料选择和封装技术。

工艺技术集成电路可靠性

工艺技术集成电路可靠性一、引言工艺技术集成电路(Process Technology Integrated Circuit,简称PTIC)是指通过先进的工艺技术制造的电路芯片。

在现代社会中,PTIC已经广泛应用于电子设备和计算机系统中,因其体积小、功耗低、性能高等优势而成为不可或缺的组成部分。

然而,随着电子设备应用的不断扩大和电路复杂度的增加,PTIC的可靠性问题也日益凸显。

本文将深入探讨工艺技术集成电路可靠性的重要性、挑战以及解决方法。

二、工艺技术集成电路可靠性的重要性工艺技术集成电路的可靠性是指其在设计规定的环境和使用寿命内能够正常工作的能力。

PTIC的可靠性对于电子设备的正常运作至关重要。

一旦PTIC出现失效,将导致电子设备无法使用,严重影响用户体验和产品质量。

因此,保证PTIC的可靠性是电子设备制造商的首要任务。

工艺技术集成电路的可靠性问题主要体现在以下几个方面:1. 温度问题温度是导致PTIC失效的主要因素之一。

当PTIC工作时,会产生大量的热量,如果温度超过了PTIC所能承受的范围,将导致电路失效。

因此,合理的散热设计是提高PTIC可靠性的重要手段之一。

2. 电压问题电压过高或过低都会对PTIC的可靠性造成影响。

电压过高可能导致PTIC元件损坏或击穿;而电压过低可能导致PTIC无法正常工作。

因此,保持适宜的电压是确保PTIC可靠性的关键因素。

3. 电磁干扰问题电磁干扰是指外部电磁场对PTIC正常工作的干扰。

现代社会中,电子设备密集,电磁场干扰问题日益凸显。

电磁干扰可能导致PTIC数据丢失、性能降低甚至损坏。

4. 级联效应问题PTIC中的各个子电路相互连接,当其中一个子电路出现问题时,可能会引起级联效应,从而导致整个PTIC失效。

因此,降低级联效应对于提高PTIC可靠性至关重要。

三、工艺技术集成电路可靠性的挑战工艺技术集成电路的可靠性问题受到多方面因素的影响,带来了相应的挑战。

1. 设计复杂性随着电子设备的发展,PTIC的设计变得越来越复杂。

集成电路的工作原理及可靠性分析

集成电路的工作原理及可靠性分析摘要:集成电路是现代电子技术中的重要组成部分,其工作原理涉及到多种物理原理和技术方法。

本文将对集成电路的工作原理进行深入分析,并探讨其可靠性问题。

首先,本文将简要介绍集成电路的基本结构和分类,并详细介绍CMOS技术在集成电路中的应用。

然后,本文将分析集成电路的工作原理,包括数字电路和模拟电路两个方面,并介绍集成电路中常见的逻辑门和模拟电路。

最后,本文将探讨集成电路的可靠性问题,包括热稳定性、电子迁移效应、辐射效应等,以及集成电路的可靠性评估方法。

关键词:集成电路,工作原理,可靠性评估方法。

引言:集成电路是现代电子技术的核心之一,其广泛应用于计算机、通信、娱乐等各个领域。

集成电路的发展经历了数十年的探索和实践,逐步从简单的门电路发展到了复杂的微处理器和存储芯片。

在集成电路的发展过程中,CMOS技术成为了最为成熟和广泛应用的技术之一。

与此同时,随着集成电路规模的不断增大和工艺的不断进步,集成电路的可靠性问题也逐渐引起人们的关注。

因此,本文将深入分析集成电路的工作原理和可靠性问题,以期为相关研究提供参考。

一、集成电路的基本结构和分类集成电路是指将多个电子器件(晶体管、电容、电阻等)以一定的规律和方法集成到一块半导体晶片上,形成一个完整的电路系统。

根据功能和结构的不同,集成电路可以分为数字电路和模拟电路两种类型。

数字电路主要用于数字信号的处理和计算,包括逻辑门、存储器、微处理器等;模拟电路主要用于模拟信号的处理和放大,包括放大器、滤波器、电源管理芯片等。

此外,根据集成度的不同,集成电路还可以分为SSI(小规模集成电路)、MSI(中规模集成电路)、LSI(大规模集成电路)和VLSI(超大规模集成电路)等不同类型。

二、集成电路的工作原理1.数字电路的工作原理数字电路主要是处理离散的数字信号,其中最基本的逻辑门包括与门、或门、非门等。

这些逻辑门的输出取决于其输入信号的状态,可以用真值表来描述其逻辑功能。

英语作文-集成电路设计行业中的测试与可靠性验证方法解析

英语作文-集成电路设计行业中的测试与可靠性验证方法解析The testing and reliability verification methods in the integrated circuit design industry play a crucial role in ensuring the functionality and durability of electronic devices. In this article, we will analyze the various techniques used in the field to guarantee the quality and performance of integrated circuits.First and foremost, one of the most common testing methods in the industry is known as "design for testability" (DFT). This approach involves incorporating test features into the design of the integrated circuit itself, making it easier to detect and diagnose potential faults during the testing phase. By implementing DFT techniques such as scan chains, built-in self-test (BIST) circuits, and boundary scan, designers can improve the efficiency and accuracy of the testing process.In addition to DFT, another essential aspect of testing in the integrated circuit design industry is the use of simulation tools. These tools allow designers to model the behavior of the circuit under various conditions, helping to identify potential issues before the physical implementation. By simulating the circuit's performance in different scenarios, designers can optimize the design and ensure its reliability under real-world operating conditions.Furthermore, reliability verification is a critical step in the integrated circuit design process, as it ensures that the final product meets the required quality standards. One common method used for reliability verification is accelerated life testing, where the circuit is subjected to extreme conditions to simulate years of use in a short period. By analyzing the circuit's performance under stress, designers can identify weak points and improve the overall reliability of the design.Moreover, fault injection testing is another effective technique used in the industry to evaluate the reliability of integrated circuits. By intentionally introducing faults into the circuit and observing its response, designers can assess the robustness of the design andidentify potential vulnerabilities. This method helps to ensure that the circuit can withstand unexpected events and maintain its functionality under adverse conditions.In conclusion, the testing and reliability verification methods in the integrated circuit design industry are essential for ensuring the quality and performance of electronic devices. By incorporating DFT techniques, using simulation tools, conducting reliability verification tests, and performing fault injection testing, designers can enhance the reliability and durability of integrated circuits. These methods play a crucial role in the development of high-quality electronic products that meet the demands of modern technology.。

集成电路封装技术的研究与改进

集成电路封装技术的研究与改进随着科技的发展,人们对于电子产品的需求越来越高。

而集成电路作为电子产品的核心部件,其封装技术也越来越受到关注。

本文将从集成电路封装技术的历史发展、现今面临的问题和研究方向、技术改进等方面进行探讨。

一、集成电路封装技术的历史发展集成电路封装技术的发展可以追溯到上世纪70年代初期。

当时,大多数芯片都采用金属腿封装。

这种封装技术主要通过焊接的方式连接芯片和引脚,但是其成本高、制作量小、高温热膨胀系数等问题也引发了人们对其改进的迫切需求。

于是,人们开始研究新的封装技术,以提高电子产品的可靠性和性能。

在此之后,多种新型封装技术相继诞生,如微波封装、无引脚封装、BGA封装、QFN封装等。

这些新技术的出现,不仅将集成电路封装技术推向了新的高峰,也极大地促进了电子产品的市场发展。

二、集成电路封装技术面临的问题和研究方向但是封装技术不断进步的同时,也需要面对一些挑战和问题。

尤其是大规模集成电路封装技术,需要更加高效和可靠的解决方案。

首先,大规模集成电路封装需要充分考虑重构设计问题。

如果能够在集成电路设计的早期确定需要使用的封装类型,那么可以有效地减少封装设计过程中出现的问题,并节约设计时间。

其次,对于大规模的集成电路,需要封装技术在保证产品性能和可靠性的前提下,能够实现更高的集成度和更小尺寸的封装。

另外,由于晶体管的封装密度越来越高,对于热敏性和热稳定性的要求也越来越高。

因此,近年来,人们开始关注基于纳米孔阵列的散热材料的研究。

这种散热材料通过纳米孔的结构设计,在实现高性能的同时,还能够充分提高集成电路的稳定性和耐久性。

三、技术改进除了研究方向之外,技术改进也是封装技术不断提升的重要方式。

目前集成电路封装技术的改进主要有以下几个方面:1、采用新型材料和技术。

近年来,不断有新的封装材料和技术出现,如纳米氧化铝、柔性电路板等。

这些新型材料和技术的出现,不仅提高了封装的性能和稳定性,还能够满足更加个性化的设计需求。

集成电路可靠性试验及其分析与评估

集成电路可靠性试验及其分析与评估集成电路(Integrated Circuit, IC)是现代电子领域的核心技术之一,它被广泛应用于通讯、计算机、家用电器、汽车等各个领域,为人类社会的科技进步做出了重要贡献。

然而,随着芯片制造工艺的不断发展和集成度的提高,IC可靠性问题也愈加复杂和严峻。

为了确保IC在使用过程中能够稳定可靠地运行,科学家和工程师们对IC可靠性问题进行了数十年的研究与试验。

本文将着重介绍集成电路可靠性试验及其分析与评估方法。

一、IC可靠性指标:IC可靠性是指其在一定的工作条件下,能够在规定的时间和区间内完成其设计任务的程度。

IC的可靠性主要包括以下几个方面:1.寿命:IC在特定的实际工作条件下,运行至失效的时间。

2.失效率:IC在特定的实际工作条件下,单位时间内实际失效的概率。

3.可修复性:IC的失效后,是否能够通过修复方式恢复其原有功能。

4.鲁棒性:IC在受到外界干扰或异常工作条件下,能否保持其正常的工作状态。

以上指标是评估IC可靠性的主要参考指标,一般情况下,寿命和失效率是评估IC可靠性的重要指标,下面我们将介绍IC可靠性试验的主要内容。

二、IC可靠性试验内容:IC可靠性试验是指对IC进行一系列实验,以评估其可靠性及寿命等参数的试验。

其主要包括以下几个方面:1.温度试验:对IC进行高温和低温试验,以评估IC在极端温度条件下的可靠性。

2.湿度试验:对IC进行潮湿试验,以评估IC在高湿环境下的可靠性。

3.热应力试验:对IC进行热应力试验,以评估IC在温度梯度环境下的可靠性。

4.振动试验:对IC进行振动试验,以评估IC在机械振动等异常工作条件下的可靠性。

5.电学试验:对IC进行电学试验,以评估IC在电学参数变化时的可靠性。

以上试验是IC可靠性试验的主要内容,每一项试验都需要严格的操作规范和数据记录流程,下面我们将着重介绍IC可靠性试验数据分析与评估方法。

三、IC可靠性试验数据分析与评估方法:IC可靠性试验所得的试验数据一般包括失效时间、失效率、可修复性等参数,下面我们将介绍常用的IC可靠性数据分析与评估方法。

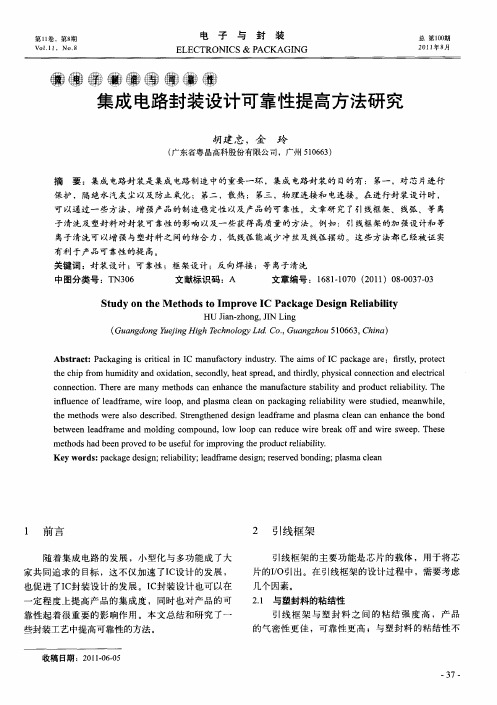

集成电路封装设计可靠性提高方法研究

刖 舌

2 引线 框 架

引线框 架 的主要 功能 是芯 片的载 体 ,用于 将芯

随 着集成 电路 的 发展 ,小 型化 与 多功 能 成 了大

家共 同追 求的 目标 ,这 不仅加 速 了I 设计 的发 展 , C

片 的I / 出。在 引线 框架的 设计过程 中 ,需要 考虑 0引

也促 进 了I 封 装设 计 的发展 。I 封 装设计 也 可以在 c C

一

几个 因素 。 21 与塑封料的粘结性 .

引 线 框 架 与 塑 封 料 之 间的 粘 结 强 度 高 ,产 品 的 气密性 更 佳 ,可靠性 更 高 ;与塑封 料的粘 结性 不

定 程度 上提 高产 品的 集成 度பைடு நூலகம்,同时 也对 产 品的可

靠性 起着 很重 要 的影 响作 用 。本 文 总结和 研 究 了一

St y o heM e ho st m pr veI Pa ka eDe i n Rei biiy ud n t t d o I o C c g sg la l t

HU in z o g JN n Ja — h n , I Li g

( u n d n u i G a g o gYe n g ehooyLd C . u n zo 1 6 3 C i ) j gHi Tcn l h g t. o, a gh u5 0 6 , hn G a

圆形钉孔三角形凹槽方形凸台一l图3bbosn于叠晶及芯片与芯片之间焊接的情况方形凹凸钉组合圆形凹槽及通孔图1各种增强型框架22芯片与引脚之间的连接引线框架的最重要的功能是芯片与外界之间的载体因此引线框架应设计得利于芯片与引脚之间的连接要考虑线弧的长度以及弧度

第 1卷 ,第8 1 期

V . 1 NO 8 o1 1 . .

集成电路中的可靠性设计与测试

集成电路中的可靠性设计与测试随着科技的不断发展,集成电路已经成为现代智能电子产品中不可或缺的组成部分。

然而,由于电子产品的高度复杂性和高密度的电路设计,集成电路的可靠性设计与测试成为一项至关重要的任务。

本文将探讨在集成电路中的可靠性设计与测试。

一、可靠性设计在集成电路中的重要性集成电路作为现代电子产品的核心技术,它的可靠性成为保障产品正常运行和长期使用的重要因素。

因此,集成电路的设计和测试必须要充分考虑到可靠性问题。

集成电路设计的可靠性包括电路设计的稳定性、噪声、温度和时间等多方面的因素。

对于电路设计的稳定性,可在设计阶段中采用合适的电磁兼容技术和稳定电源等方法,降低电路噪声和抖动等问题。

而对于温度和时间等因素,则需要设计具有较高实验稳定性和可重复性的电路。

另一方面,可靠性测试是集成电路生产过程中的重要环节之一。

通过对集成电路进行可靠性测试可以有效评估电路的稳定性和可靠性,及早发现存在的问题,并对测试数据进行动态分析和优化改进。

因此,在集成电路的设计和生产中,可靠性测试应该被认为是对电路可靠性进行验证和监控的重要手段。

二、集成电路的可靠性测试方法为了测试集成电路的可靠性,需要采用合适的测试方法和技术。

下面介绍几种常见的集成电路可靠性测试方法。

1. 温度加速测试温度加速测试是一种重要的集成电路可靠性测试方法,它通过将被测试芯片置于高温环境下,模拟电路使用寿命,并测量芯片的可靠性和寿命。

此测试方法可以有效发现电路中的潜在问题,对设计进行改进和优化。

温度加速测试也可以结合其他测试方法,如电性能测试和可靠性老化测试,实现综合性能评估。

2. 电性能测试电性能测试是另一种重要的集成电路可靠性测试方法。

它通过测试芯片的电气特性,包括电压、电流、功耗、输入输出电阻和逻辑门延时等指标来评估芯片的可靠性和性能。

此测试方法适用于评估芯片较低层次的性能指标和实现电路测试。

3. 可靠性老化测试可靠性老化测试是一种长时间测试芯片的可靠性的测试方法。

集成电路封装材料可靠性评估技术研究

集成电路封装材料可靠性评估技术研究随着集成电路技术的不断发展,封装材料的可靠性评估成为了重要的研究方向。

对于集成电路制造商和封装材料供应商来说,提高封装材料的可靠性是确保产品质量和可靠性的关键。

因此,研究和发展封装材料可靠性评估技术对于促进集成电路产业的发展具有重要的意义。

首先,我们需要了解集成电路封装材料的可靠性评估技术是如何进行的。

当集成电路封装材料在实际工作环境中受到温度、湿度、机械应力等外部因素的影响时,封装材料可能会出现热膨胀、应力集中、裂纹扩展等问题。

因此,评估封装材料的可靠性需要考虑这些因素,并通过实验和模拟等手段进行研究。

一种常用的封装材料可靠性评估技术是可靠性试验。

通过将封装材料置于特定的环境条件下进行长时间稳定性测试,如高温老化试验、湿热试验等,观察材料在不同条件下的性能退化情况,从而评估材料的可靠性。

在试验过程中,可以通过测量材料的物理性质、电性能等指标来得到相应的数据。

同时,还可以采用加速寿命试验的方法,通过增加环境条件的严酷程度来加速材料的老化过程,以便更快地得到可靠性评估结果。

除了试验方法外,模拟和数值计算方法也是封装材料可靠性评估的重要手段。

通过建立封装材料的数学模型,研究材料在特定环境下的热力学、力学响应等特性,预测材料的可靠性。

模拟方法可以减少试验时间和成本,并能提供更全面的材料性能信息。

例如,有限元分析是一种常用的数值计算方法,可以模拟材料在不同外部加载条件下的应力分布情况,从而评估材料的可靠性。

此外,还可以通过建立可靠性评估模型,将试验数据与模拟结果进行综合分析,提高可靠性评估的准确性。

另外,材料表征技术也是封装材料可靠性评估的重要组成部分。

通过对材料的物理性质、微观结构等进行表征,可以获得关于材料的详细信息。

例如,扫描电子显微镜、透射电子显微镜等技术可以观察材料的表面形貌和内部结构,从而了解材料的微观缺陷情况。

热分析技术可以测量材料的热性能,包括热导率、热膨胀系数等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图1 各种增强型框架

2.2 芯片与引脚之间的连接

引线框架的最重要的功能是芯片与外界之间的载体,因此,引线框架应设计得利于芯片与引脚之间的连接,要考虑线弧的长度以及弧度。

2.3 考虑塑封料在型腔内的流动

对于多芯片类的复杂设计,还应考虑塑封时塑封料在芯片与芯片或芯片与模具之间的流动性。

集成电路封装设计的可靠性提高方法研究

1 前言

随着集成电路的发展,小型化与多功能成了大家共同追求的目标,这不仅加速了IC设计的发展,也促进了IC封装设计的发展。IC封装设计也可以在一定程度上提高产品的集成度,同时也对产品的可靠性起着很重要的影响作用。本文总结和研究了一些封装工艺中提高可靠性的方法。

3.3 等离子清洗

提高焊接可靠性的一个重要方法是使用等离子清洗。等离子清洗除能清洁掉芯片及引线框架表面的沾污和氧化物之外,还能激活表面,使结合面更加牢固。等离子清洗需要保证气体在产品各个表面均匀的流动,因此需要使用有孔料盒,。

图6 等离子清洗使用的料盒

等离子清洗的几个关键影响因素有:

表1 等离子清洗前后样品焊球推力测试结果比较

由此可见,等离子清洗对金线的结合力有一定程度的提高,同时也提高了品质稳定性。

4 塑封

影响塑封效果的主要因素有以下几个方面。

4.1 模具和框架设计

前文中提到一些加强框架与塑封料之间结合力的设计方法,当需要用到大面积的基岛时,就需要考虑用到加强型的设计;同时,接近塑封体边缘的部分也是脆弱点,也需要一些加强结合力的方法。

图3 BBOS用于叠晶及芯片与芯片之间焊接的情况

3.2 降低线弧高度

现在的封装都向更薄更小发展,对芯片厚度、胶水厚度和线弧高度都有严格控制。一般弧度的线弧,弧高(芯片表面至线弧最高点的距离)一般不低于100μm,要形成更低的线弧,有以下两种方法。RB(Reverse BONding反向焊接)和FFB(FoldedForward Bonding折叠焊接 ),。

评估等离子清洗效果的另一方法为比较PpK或CpK,这也是使用等离子清洗的最终目标。为了获得稳定的高质量控制,我们做了PpK的比较试验,结果证明,等离子清洗能够在一定程度上提高产品的质量稳定性。试验内容如下:

试验设备:EUROPLASMA;气体:Ar+H2(氩气+氢气);线径:30μm金线;焊球直径:82.5μm;等离子清洗机RF功率:300W;清洗时间:180s。

3 焊线

3.1 增强焊线强度

焊线强度除了焊点处的结合强度外,线弧的形状也会对焊线强度有一定的影响。

增强焊线强度的方法之一是在焊线第二点种球,有BSOB和BBOS两种方式。。

图2 BSOB和BBOS的示意图

BSOB的方法是先在焊线的第二点种球,然后再将第二点压在焊球上;BBOS的方法是在焊线的第二点上再压一个焊球。两种方法均能增强焊线强度,经试验,BBOS略强于BSOB。BBOS还应用于die todie(芯片与芯片)之间的焊接,。

5 总结

在进行封装设计时,除了考虑电性能方面的稳定性之外,封装工艺的可靠性设计也是重要的环节。封装工艺需要依靠行业标准和各个公司总结出的经验,同时,封装工艺设计和可靠性测试与失效分析是密不可分的,它们具有相辅相成的关系。封装工艺需要通过可靠性试验来衡量,需要失效分析来寻找问题的原因,需要经验与技术来得出改进的方法。

框架和塑封模具之间关系密切,它们互补互足,设计模具时需要综合考量框架、内部芯片摆放位置、走线方向以及塑封料的物理化学性能。

4.2 塑封料

塑封料性能的好坏也直接影响可靠性。一般判断塑封料等级的首要因素为MSL(潮湿敏感度等级),MSL等级越高,其对芯片的保护越好。其次,热硬度即热转化温度及与不同金属面之间的粘结性能也是需要考虑的重要因素。

2 引线框架

引线框架的主要功能是芯片的载体,用于将芯片的I/O引出。在引线框架的设计过程中,需要考虑几个因素。

2.1 与塑封料的粘结性

引线框架与塑封料之间的粘结强度高,产品的气密性更佳,可靠性更高;与塑封料的粘结性不好,会导致分层及其他形式的失效。影响粘结强度的因素除了塑封料的性能之外,引线框架的设计也可以起到增强粘结强度的作用,如在引脚和基岛边缘或背面设计图案,。

图4 反向焊接(RB)

图5 折叠正向焊接(FFB)

反向焊接虽然可以形成低的线弧,但是种球形成了大的焊球,使得焊线间距受到限制。折叠正向焊接方法是继反向焊接之后开发的用于低线弧的焊接方法,。

低线弧不仅能够满足塑封体厚度更薄的要求,还能减少塑封时的冲丝以及线弧的摆动(wiresweep),对增加封装可靠性有一定的帮助。

(3)功率和时间。对不同厂家制造的等离子清洗机以及不同类型的产品,都要通过DOE实验方法,找出最合适的设定范围。

(4)评定方法。最直观的评定等离子清洗效果的方法是滴水试验,通过观浸湿示意图

浸湿角在20°~40°之间是合适状态,16h后浸湿角会大于40°。因此,等离子清洗后的延迟时间建议为8h。

(1)气体成分。等离子清洗使用的气体一般为氩气、氧气和氢气,也可以使用混合气体。氩气和氧气用来清洗有机残留,氢气用来清洗氧化物。

(2)料盒和产品排布。清洗效果的一致性是很重要的,有利于获得封装组装工艺的高质量控制 [3]。对于射频型等离子清洗机而言,应该让料盒的排布顺应气体的流向,让气体均匀流通在料盒的各个位置。