时钟门控技术(Clock Gating)

ClockGatingMethodology

7

Agenda

• Objective • Introduction to clock gating • Clock gating methodology

– – – – – Overview RTL synthesis Physical synthesis Clock tree synthesis Summary of Recommendations

• Area savings

– Eliminating multiplexers saves area

• Easy to implement

– No RTL code change is required – Clock gating is automatically inserted by the tool – Technology independent

• Clock Gate Styles • Enable signal timing

– Ensure that you meet setup time on the enable pin of clock gate

• Impact of clock gate fanout on

– Power and enable pin timing – Clock tree structure

RTL Synthesis

Insert Clock Gating during RTL Synthesis

• Use the insert_clock_gating command

12

– The global option looks across hierarchical boundaries for the common enable Extra ports

set_clock_gating_check用法 -回复

set_clock_gating_check用法-回复set_clock_gating_check是一种在数字电路设计中使用的时钟门控检查方法。

在这篇文章中,我们将一步一步地介绍set_clock_gating_check的用法,以及它在电路设计中的重要作用。

1. 什么是时钟门控?在数字电路中,时钟信号用于同步电路的操作。

时钟门控是一种优化技术,用于在某些特定情况下关闭不必要的时钟信号,从而降低功耗和提高性能。

当某个电路模块在没有活动输入时,可以通过关闭与该模块相关的时钟信号来停用该模块,以节省功耗。

2. set_clock_gating_check的作用是什么?set_clock_gating_check是一种在静态时序分析中使用的方法,用于检查时钟门控的正确性。

它可以帮助设计工程师找出在时钟门控逻辑中可能存在的故障,并确保时钟门控的正确性,以避免在实际电路运行时遇到时序问题。

3. 如何使用set_clock_gating_check?使用set_clock_gating_check需要进行以下几个步骤:步骤一:定义时钟门控单元首先,设计工程师需要在电路设计中使用特定的时钟门控单元。

这个单元将负责控制特定模块的时钟信号,以便在没有活动输入时关闭该模块的时钟。

根据不同的设计需求和设计约束,可以选择不同的时钟门控单元类型。

步骤二:设置时钟门控约束在设计中,设计工程师需要为时钟门控单元定义约束。

这些约束描述了时钟门控的行为和逻辑关系,以及单元和其他模块之间的相互作用。

约束文件可以使用特定的语言(如SystemVerilog的设置约束语言)编写。

步骤三:运行set_clock_gating_check工具一旦约束文件定义完成,设计工程师就可以使用相应的set_clock_gating_check工具来对设计进行时钟门控检查。

这些工具通常包括一些静态时序分析工具,可以检查设计中的时钟门控逻辑是否满足约束条件,并找出可能的错误。

fpga 门控时钟 功耗

fpga 门控时钟功耗FPGA(可编程逻辑门阵列)是一种灵活的集成电路芯片,其门控时钟和功耗是在设计和应用FPGA时需要考虑的重要因素。

下面将介绍FPGA的门控时钟和功耗的相关概念和影响因素:1.门控时钟:FPGA中的门控时钟(Clock Gating)技术是一种用来减小功耗的技术。

它基于时钟信号,通过控制特定部分的电路时钟使能信号,实现对电路的部分停止或冻结。

通过精确控制时钟信号的分配,可以降低那些不需要运行或处于空闲状态的部分的功耗。

2.功耗:FPGA的功耗是指FPGA芯片在工作中消耗的电能。

FPGA的功耗由多个因素决定,包括运行的电路逻辑、时钟频率、输入输出功耗、时钟和数据冲突等。

功耗的高低直接影响到芯片的工作稳定性、散热需求和电池寿命等。

影响FPGA功耗的因素包括:•逻辑电路:芯片中运行的逻辑电路数量和复杂度直接影响功耗。

•时钟频率:时钟频率越高,功耗也越高。

高时钟频率可能需要更多的功率来驱动逻辑和开关电容。

•输入输出功耗:与外部设备的通信和I/O电路相关的功耗。

•激活逻辑:即芯片中具体逻辑的使用情况,未使用或未激活的逻辑不会消耗功耗。

•工艺制程:不同的工艺制程也会影响功耗,先进的工艺通常具有更低的功耗。

减小FPGA的功耗可以通过以下策略实施:•优化逻辑设计:减少逻辑元件的数量和复杂度,精简逻辑电路。

•优化时钟频率:选择适当的时钟频率,以平衡性能和功耗。

•使用门控时钟技术:通过控制部分电路的时钟使能信号,降低空闲电路的功耗。

•合理布局和布线:减少布线的长度和电容负载,优化功耗表现。

在设计和实现FPGA时,需要综合考虑门控时钟和功耗,根据实际需求进行优化和权衡。

同时,对于特定的应用场景,还可以选择适合的低功耗模式、电源管理和时钟路由等技术,以进一步减小FPGA的功耗。

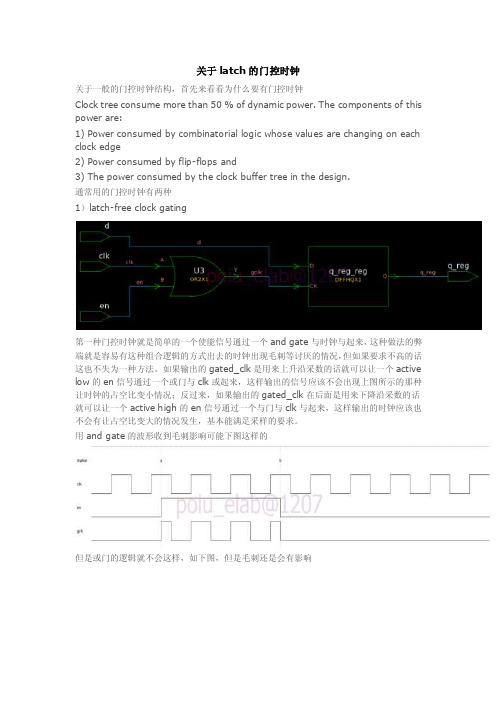

关于latch的门控时钟综合

关于latch的门控时钟关于一般的门控时钟结构,首先来看看为什么要有门控时钟Clock tree consume more than 50 % of dynamic power. The components of this power are:1) Power consumed by combinatorial logic whose values are changing on each clock edge2) Power consumed by flip-flops and3) The power consumed by the clock buffer tree in the design.通常用的门控时钟有两种1)latch-free clock gating第一种门控时钟就是简单的一个使能信号通过一个and gate与时钟与起来,这种做法的弊端就是容易有这种组合逻辑的方式出去的时钟出现毛刺等讨厌的情况,但如果要求不高的话这也不失为一种方法。

如果输出的gated_clk是用来上升沿采数的话就可以让一个active low的en信号通过一个或门与clk或起来,这样输出的信号应该不会出现上图所示的那种让时钟的占空比变小情况;反过来,如果输出的gated_clk在后面是用来下降沿采数的话就可以让一个active high的en信号通过一个与门与clk与起来,这样输出的时钟应该也不会有让占空比变大的情况发生,基本能满足采样的要求。

用and gate的波形收到毛刺影响可能下图这样的但是或门的逻辑就不会这样,如下图,但是毛刺还是会有影响2)latch-based clock gatinglatch的这种gating的结构比较特殊,如图这个东西还是基于synopsys的自己的gating clock的逻辑处理出现的一种方式这个同学的仿真波形图是这样的(只注意en clk q 和gclk)latch这里为低有效,即latch 的en端(即clk)为低的时候,latch的q端是可以变化的,但是高的时候就会被latch 住。

低功耗设计中的时钟门控技术

低功耗设计中的时钟门控技术

时钟门控技术是低功耗设计中非常重要的一项技术。

在数字电路中,时钟信号

的频率越高,功耗也就越大。

因此,在设计低功耗的数字电路时,需要采用一些技术手段来降低时钟信号的频率以达到降低功耗的目的。

时钟门控技术就是一种有效的降低功耗的方法之一。

它通过控制时钟信号的开

关来实现对电路的时钟信号进行控制。

在时钟门控技术中,当电路不需要进行运算时,可以通过控制时钟门控信号来使时钟信号停止,从而降低功耗。

时钟门控技术的实现方法有很多种,其中比较常见的是利用时钟门控信号对寄

存器、触发器以及各种逻辑门进行控制。

通过合理的设计,可以实现在保证电路正常功能的前提下,尽可能地减少功耗。

时钟门控技术在数字集成电路设计中有着广泛的应用。

特别是在移动设备、智

能传感器等对功耗要求较高的领域中,时钟门控技术更是必不可少的一项技术。

通过合理地应用时钟门控技术,可以大幅降低电路的功耗,延长设备的使用时间,提高设备的稳定性。

总的来说,时钟门控技术在低功耗设计中扮演着非常重要的角色。

它通过控制

时钟信号的开关来实现对电路功耗的有效控制,是实现低功耗设计的一种重要手段。

在未来的数字集成电路设计中,时钟门控技术将继续发挥着重要的作用,为我们提供更加节能高效的数字电路设计方案。

门控时钟检查(clock gating check)的理解和设计应用

门控时钟检查 (Clock Gating Check) 的理解和设计应用本文旨在介绍门控时钟检查 (Clock Gating Check) 的定义、作用以及在数字电路设计中的应用,并提供一些设计技巧。

门控时钟检查 (Clock Gating Check) 是一种用于数字电路中的时序分析技术,它的主要作用是检查门控时钟网络 (Clock Gating Network) 的正确性。

门控时钟网络通常用于降低功耗和减少时序约束,它可以根据某些条件来控制时钟信号的传输。

门控时钟检查的核心思想是,通过对门控时钟网络进行分析,检查所有可能的时序路径是否满足时序约束条件。

具体来说,门控时钟检查器会检查每个时钟周期是否被正确地门控,以及每个门是否在正确的时序状态下工作。

如果检查器发现任何错误,它将报告这些错误并提供有关如何修复它们的建议。

在数字电路设计中,门控时钟检查通常是必不可少的,因为它可以帮助设计人员在设计过程中检测和纠正时序错误,从而提高电路的性能和可靠性。

门控时钟检查可以在 RTL 代码层面进行实现,也可以在门级网表层面进行实现。

在设计门控时钟检查时,需要考虑以下几个方面:

1. 确定门控时钟网络的时序约束条件,包括时钟周期、时钟门控信号、时钟网络拓扑结构等。

2. 选择合适的门控时钟检查算法,例如基于状态的检查算法或

基于推断的检查算法。

3. 实现门控时钟检查器,通常可以使用硬件描述语言 (HDL) 来实现。

4. 验证门控时钟检查器的正确性和性能,通常可以使用仿真工具来验证。

门控时钟检查是数字电路设计中一个非常重要的技术,它可以帮助设计人员检测和纠正时序错误,提高电路的性能和可靠性。

门控时钟技术在RTL功耗优化上的应用

优化设计

9 8 . 1 4 %

9 1 . 6 4 %

优化效果

3 . 5 6 %

5 . 8 1 %

逻 辑 门控 技 术 我 们 还 是l o c k — g a t i n g 效率得到 5 . 8 1 %的

提升, 寄存 器 功耗 得 到 1 3 . 5 9 %的节 省 。

当 然 , 由于 引 入 了 额 外 的 控 制 逻

8 5

8 3 %

组 合 电 路 功 耗 寄存 器 电路 功耗

面 积

3 5 0 6 4 . 0 u W 1 7 5 4 1 . 3 u W

6 6 9 8 4 6 6

3 4 6 8 2 . 7 u W l 5 l 5 6 . 9 u W

表 1模 块 A 功 耗 优 化 结 果

例和 c l o c k — g a t i n g 效 率 不 是很 高 ,经 过

优化效果

1 3 。 0 5 %

2 7 . O 1 %

对 比项

实现 c l o c k — g a t i n g 插 入 的 寄存 器 比例

( 4) 利用 形 式验 证工 具 S L E C完 成 原始 设 计 和

优 化设 计 在功 能 上的一 致性 验证 ; ( 5) 对 优化 的 R T L代 码 进行 功 能仿 真 , 得到 新 的仿真 波形 文件 ;

参考文献

[ 1 ] P o w e r P r o U s e r Ma n u a l , C l a y p t o , V e r s i o n 6 . 1

设计 中

原始设 计

7 5

.

优化设计

8 8 . 8 9 %

fpga内部时钟门控单元

fpga内部时钟门控单元英文回答:Clock gating is a technique used in FPGA design to reduce power consumption by selectively stopping the clock signal to certain parts of the circuit when they are not in use. This is achieved by using clock gating cells, which are special logic gates that control the clock signal to specific parts of the design.For example, let's say I have a circuit that includes a counter and a comparator. The counter increments every clock cycle, while the comparator only needs to be active when the counter reaches a certain value. By using a clock gating cell, I can disable the clock signal to the comparator when it is not needed, saving power in the process.Clock gating cells are typically implemented usingflip-flops and AND gates. The flip-flop stores the enablesignal, while the AND gate controls the clock signal based on the enable signal. When the enable signal is high, the clock signal passes through the AND gate to the flip-flop, allowing the circuit to operate normally. When the enable signal is low, the clock signal is blocked, effectively stopping the circuit.In FPGA design, it is important to carefully consider where to place clock gating cells to maximize power savings without compromising performance. Over-gating can lead to timing issues, while under-gating may not providesignificant power savings. It's a delicate balance that requires thorough testing and optimization.中文回答:时钟门控是一种在FPGA设计中使用的技术,通过在某些部分不使用时选择性地停止时钟信号来减少功耗。

clock gating verilog写法

clock gating verilog写法Clock gating是一种广泛用于减少功耗和提高芯片性能的技术。

简单来说,它是通过控制时钟信号的流动来实现减少功耗和提高性能的目的。

在这篇文章中,我们将探讨如何使用Verilog语言来实现Clock gating的设计。

第一步:定义时钟及其控制信号首先,我们需要定义时钟信号和时钟控制信号。

这可以通过在Verilog代码中定义一个clock变量和一个enable变量来实现。

例如:reg clock;reg enable;在这里,我们使用了reg关键字来定义时钟和控制信号。

clock变量用于存储时钟信号的值,而enable变量用于存储时钟控制信号的值。

第二步:实现Clock gating功能接下来,我们需要实现Clock gating的功能。

这可以通过使用always块来实现。

例如:always @ (posedge clock) beginif (enable) begin// 对时钟进行操作endend在这里,我们使用了always块来定义一个与时钟相关的过程。

当时钟的上升沿到来时,if语句对控制信号进行检查。

如果控制信号为高电平,则执行语句块中的代码。

否则,时钟信号将被屏蔽,不执行任何操作。

第三步:测试Clock gating设计最后,我们需要测试我们的Clock gating设计是否正常工作。

一种测试方法是通过手动设置时钟和控制信号的值来检查输出结果。

例如:initial begin// 设置控制信号为1enable = 1;// 设置时钟信号clock = 0;#10 clock = 1;#10 clock = 0;#10 clock = 1;#10 clock = 0;// 设置控制信号为0enable = 0;#10 clock = 1;#10 clock = 0;#10 clock = 1;#10 clock = 0;end在这里,我们使用了initial块来设置时钟和控制信号的值,并检查输出结果。

芯片设计中的功耗优化技术研究

芯片设计中的功耗优化技术研究芯片设计中的功耗优化技术是为了降低芯片的功耗而进行的一系列研究和优化工作。

功耗优化技术在芯片设计过程中起到了至关重要的作用,能够提高芯片的性能、延长电池寿命以及减少能源消耗。

本文将介绍和探讨一些常用的功耗优化技术。

1.系统级功耗优化技术:系统级功耗优化技术主要通过优化芯片的整体结构和电源管理来降低功耗。

其中包括:-动态电压调整(DVM):根据当前芯片的工作负载,动态地调整电压,以达到节能的目的。

-动态频率调整(DPM):根据芯片的工作负载以及功耗需求,实时调整芯片的工作频率,以控制功耗。

-休眠模式:在空闲时,可以将芯片进入低功耗或休眠状态,以减少功耗。

-分频:通过降低芯片各个模块的工作频率,来节约功耗。

2.电源管理技术:电源管理技术是降低芯片功耗的关键技术之一,主要包括以下几个方面:- 电压频率调整(VF Scaling):调整电压和频率,以实现在给定电压下的最低功耗。

-电源噪声抑制:通过优化供电网络,减少电源噪声,以提高芯片的功耗效率。

- 电源降压(Undervolting):降低芯片的工作电压,以减少功耗。

-功率管理单元(PMU):通过对芯片中的各个模块进行电源管理,实现精确的功耗控制。

3.逻辑级功耗优化技术:逻辑级功耗优化技术主要通过对芯片逻辑电路进行优化来降低功耗。

常见的逻辑级功耗优化技术包括:- 时钟门控(Clock gating):对不需要时钟的电路模块进行控制,以减少功耗。

- 动态逻辑(Dynamic logic):通过优化逻辑电路的传输门和开关门,减少功耗。

-逻辑重编码:通过对逻辑电路进行重编码,减少开关翻转,降低功耗。

4.物理级功耗优化技术:物理级功耗优化技术主要通过对芯片的物理结构进行优化,降低功耗。

常见的物理级功耗优化技术包括:-布局优化:通过优化芯片的布局,减少导线的长度和电容,降低功耗。

- 时钟树优化(Clock tree optimization):通过优化时钟树的设计,减少时钟信号的延迟和功耗。

芯片设计中的功耗管理技术有哪些

芯片设计中的功耗管理技术有哪些在当今的科技时代,芯片作为各种电子设备的核心组件,其性能和功耗管理至关重要。

随着芯片的集成度越来越高,功能越来越强大,功耗管理成为了芯片设计中一个不可忽视的关键问题。

有效的功耗管理技术不仅能够延长设备的电池续航时间,还能降低芯片的发热,提高系统的稳定性和可靠性。

那么,在芯片设计中,都有哪些常见的功耗管理技术呢?动态电压频率调整(DVFS)是一种被广泛应用的功耗管理技术。

简单来说,就是根据芯片的工作负载动态地调整其电压和频率。

当芯片处理的任务较为简单,负载较轻时,降低工作电压和频率,从而减少功耗;而当处理复杂任务,负载较重时,相应地提高电压和频率,以保证性能。

这种技术就像是给芯片安装了一个智能的“油门”,根据实际需求灵活调节“动力输出”。

时钟门控(Clock Gating)也是一项重要的技术。

在芯片中,时钟信号是控制各个模块工作的“节拍器”。

但是,并非所有模块在任何时候都需要工作。

通过时钟门控技术,可以在不需要某些模块工作的时候,关闭其时钟信号,使其停止工作,从而避免不必要的功耗。

这就好比在一个工厂里,当某个生产线不需要运转时,就把它的电源关掉,节省能源。

电源门控(Power Gating)则是在芯片不工作的部分直接切断电源供应。

与时钟门控不同,电源门控是从根本上杜绝了漏电等功耗的产生。

但这种技术在重新启用被关闭的部分时,可能会有一定的延迟,所以需要在功耗节省和性能之间进行权衡。

多阈值电压(MultiThreshold Voltage)技术也是降低功耗的有效手段。

在芯片制造过程中,可以采用不同阈值电压的晶体管。

低阈值电压的晶体管速度快,但漏电功耗大;高阈值电压的晶体管速度较慢,但漏电功耗小。

通过合理地搭配使用不同阈值电压的晶体管,在保证性能的前提下降低整体功耗。

睡眠模式(Sleep Mode)和待机模式(Standby Mode)也是常见的功耗管理策略。

当芯片在一段时间内没有操作或处于空闲状态时,自动进入低功耗的睡眠或待机模式。

set_clock_gating_style用法

set_clock_gating_style用法

set_clock_gating_style是一种用于时钟门控的技术,它可以根据特定需求来控制时钟信号的输出,从而降低功耗和提高性能。

二、set_clock_gating技术的原理

set_clock_gating技术通过在不需要时钟信号时关闭时钟门,以减少时钟信号的输出,从而达到降低功耗的目的。

这种技术通常应用于需要周期性唤醒和睡眠的设备,如移动设备、服务器等。

1. 了解需求:在使用set_clock_gating之前,需要了解设备的具体需求,确定需要控制的时钟信号以及控制方式。

2. 查找支持:在设备中查找是否有支持set_clock_gating的软件或工具,这些工具通常会提供相应的API或配置选项。

3. 配置设置:根据工具或API的要求,进行相应的配置设置,包括控制方式、触发条件等。

4. 测试验证:在实施set_clock_gating后,需要进行测试验证,确保设备的性能和功耗得到改善。

四、注意事项

1. 实施set_clock_gating时,需要充分了解设备的具体需求和时钟信号的特性和影响,避免出现不良后果。

2. 在实施set_clock_gating时,需要确保配置设置正确,并经过充分的测试验证,以确保设备的稳定性和性能。

3. 在实施set_clock_gating时,需要遵守相关法律法规和安全标准,避免侵犯他人合法权益或违反相关规定。

总的来说,set_clock_gating是一种非常实用的技术,能够有效地降低功耗和提高性能。

正确使用和配置设置,就能够发挥出它的优势和特点。

芯片设计中的低功耗时钟技术研究

芯片设计中的低功耗时钟技术研究随着移动设备、物联网和智能家居等领域的快速发展,对低功耗芯片的需求也越来越大。

而在芯片设计中,时钟技术是重要的一部分,它对芯片的功耗和性能有着直接的影响。

因此,研究和应用低功耗时钟技术成为了现代芯片设计中的一个热门方向。

一、低功耗时钟技术的意义时钟信号在芯片中起到同步和驱动的作用,它控制了芯片内各个功能部件的工作状态。

在低功耗芯片设计中,优化时钟技术可以帮助降低功耗、提高芯片性能,并延长电池寿命。

此外,低功耗时钟技术还能减少由于时钟信号传输引起的功耗损耗和噪音干扰,提高芯片的可靠性和稳定性。

二、低功耗时钟技术的研究方向1. 时钟频率调节技术在低功耗芯片设计中,时钟频率调节技术是一种常用的手段。

通过动态地调整时钟频率,可以根据芯片当前的工作状态来灵活地改变时钟频率。

例如,在芯片处于空闲状态时,可以降低时钟频率以减少功耗;而在需要高性能的场景下,可以提高时钟频率以提升芯片运算能力。

2. 时钟门控技术时钟门控技术是低功耗芯片设计中的另一种重要手段。

它通过在芯片中插入可控的时钟门,实现对芯片内部功能单元的时钟供应进行精确控制。

当某个功能单元不需要工作时,可以关闭对其的时钟供应,从而实现功耗的降低。

3. 功耗感知时钟树设计时钟树是芯片中时钟信号传输的重要组成部分,它的设计对芯片功耗有着直接的影响。

为了降低时钟树的功耗,可以采用功耗感知的时钟树设计方法。

这种方法通常包括时钟树的分级设计、时钟缓冲的优化以及时钟信号的容错机制等,以实现低功耗的时钟信号传输。

4. 时钟域划分与管理在复杂的芯片设计中,常常存在多个时钟域。

合理地进行时钟域划分与管理可以有效地降低功耗。

通过将芯片划分为不同的时钟域,并采用适当的互联方式和时钟同步策略,可以减少时钟信号的功耗消耗和传输延迟,提高芯片性能和可靠性。

三、低功耗时钟技术的挑战与前景低功耗时钟技术在芯片设计中具有重要的意义,但同时也面临着一些挑战。

clock gating原理和应用场景

clock gating原理和应用场景

Clock gating是一种低功耗设计技术,它通过控制时钟信号的传输来减少电路的功耗。

其原理是根据电路的工作逻辑,在不需要时将时钟信号屏蔽或关闭,从而减少了电路的开关功耗。

在一个电路中,只有当需要执行某个特定功能时,才需要时钟信号来驱动电路的操作。

而在其他情况下,比如当电路处于空闲状态、待机状态或者无效操作时,时钟信号可以被关闭或屏蔽,这样就可以减少电路的功耗。

Clock gating主要应用于以下场景:

1. 空闲状态:当电路处于空闲状态时,没有需要执行的任务,可以通过关闭时钟信号来降低功耗。

例如,在处理器中,当空闲时可以关闭某个功能模块的时钟信号。

2. 待机状态:当电路处于待机状态时,处于节能模式或者等待外部事件的触发,可以关闭不必要的模块电源或者关闭整个电路的时钟信号,以减少功耗。

3. 无效操作:在一些指令流水线等场景中,存在一些无效操作,不需要时钟信号的驱动。

可以通过根据指令类型或者条件判断来关闭不必要的时钟信号,从而减少功耗。

总之,Clock gating技术可以根据电路的工作状态来动态地控制时钟信号的传输,从而实现功耗的降低。

它在现代集成电路设计中广泛应用,可以有效地提高电路的能效和性能。

clock gating的验证方法

clock gating的验证方法Clock gating是一种常用的功耗优化技术,其原理是在时钟信号到达时钟门控器件之前将时钟信号屏蔽,以达到降低功耗的目的。

而针对这种技术,需要进行验证以保证其正确性和可靠性。

本文将介绍clock gating的验证方法。

1.功能仿真功能仿真是验证clock gating的最基本方法。

通常使用的是基于RTL级别的仿真工具,通过对设计的时钟门控电路进行仿真,验证电路在激励下的输出是否符合预期。

仿真测试包括了针对时钟门控器件的开启和关闭信号的测试,以及对整个时钟域的时序分析等。

2.时序仿真时序仿真是对时序电路进行验证的一种方法。

在clock gating设计中,时序仿真可以帮助验证时钟门控电路的时序逻辑是否正确。

时序仿真的过程是通过输入激励来模拟电路的时序行为,以检查电路的时序逻辑是否正确。

3.静态分析静态分析是验证clock gating的一种方法。

它可以被用来检查设计中的一些潜在错误,比如说时钟门控器件的开启和关闭信号的正确性。

静态分析可以通过在设计中检查时钟门控器件的状态、时钟域的分析和时序逻辑的检查等方法来实现。

4.形式化验证形式化验证是一种验证方法,它可以对设计进行形式上的证明,以证明设计的正确性。

在clock gating设计中,形式化验证可以对时钟门控电路的逻辑进行证明,以证明其正确性。

形式化验证的过程是通过形式化建模、状态探索和证明等步骤来实现。

5.物理验证物理验证是对设计进行布局和布线,以验证电路的物理特性是否符合预期的一种方法。

在clock gating设计中,物理验证可以通过对时钟门控电路的布局和布线进行验证,以验证电路的物理特性是否符合设计要求。

6.模拟验证模拟验证是对设计进行模拟和分析,以验证电路的性能和可靠性的一种方法。

在clock gating设计中,模拟验证可以用来验证时钟门控电路的性能和可靠性。

模拟验证的过程是通过激励输入和电路响应的分析来实现。

基于数据驱动的时钟门控技术的物理实现

基于数据驱动的时钟门控技术的物理实现在高性能微处理器和SoC中,时钟树功耗占总功耗很大比重,时钟门控技术是有效降低时钟树功耗的方法。

基于综合的时钟门控技术遗留了大量冗余的时钟脉冲,时钟门控效率低,时钟树功耗优化效果不理想。

采用基于数据驱动的时钟门控(Data-driven Clock Gating, DDCG)技术能够有效关断冗余时钟脉冲,提高时钟门控效率,进一步降低时钟树功耗。

本文以基于数据驱动的时钟门控技术为研究重点,综合考虑寄存器翻转矢量之间的相关性和每个寄存器的物理位置,实现寄存器群组最优化。

本文将寄存器群组过程抽象为最小成本完美匹配(MCPM)问题,采用DDCG寄存器群组算法获取最优化的寄存器群组方式。

该算法主要包括三部分:1) Edmonds算法实现一般图加权最优匹配;2)状态矢量处理算法获取寄存器群组冗余时钟脉冲数量,用以表征寄存器翻转矢量之间的相关性;3)最小覆盖圆算法确定寄存器群组最小覆盖圆直径,用以表征寄存器物理位置的影响。

针对传统的DDCG技术面积开销大的问题,本文给出了门控效率排序与筛选、组合式群组和异或逻辑近似等改进方法,实现功耗优化和面积开销的平衡。

本文基于SMIC 40nm LOGIC工艺,首先在ISCAS89基准电路上进行了物理实现和仿真实验,并分析了该技术的适用条件,然后以DW8051和Cortex-M3处理器作为案例进行了详细的数据分析和对比。

结果表明,与基于综合的时钟门控技术相比,采用改进的DDCG技术时,时钟树功耗分别降低了33.13%和35.34%,总功耗分别降低了20.65%和16.42%,面积分别增加了12.5%和9.67%。

与传统的DDCG技术相比,采用改进的DDCG技术时,时钟树功耗分别降低了17.01%和31.92%,总功耗分别降低了14.3%和13.08%,面积分别降低了11.41%和11.74%。

clock gating结构

clock gating结构

Clock gating是一种降低功耗的常用技术,主要由与门(或或门)和LATCH组合而成。

这种结构可以在整个CLK为低的半个周期期间锁存EN

信号,只要保证EN信号在下一个CLK的上升沿来临之前稳定,就能将正确的EN信号锁存进去。

随着技术的发展,现在的clock gating结构可能会基于LATCH+OR形式,其中LATCH需要换成clock high-active,并根据EN信号的高低电平有效不同,决定图中inverter CELL是否存在。

这种基于LATCH+OR的clock gating电路形式,能够为EN信号稳定争取到一个CLK cycle的时间。

以上内容仅供参考,如需了解更多信息,建议查阅相关文献或咨询专业人士。

scanchain的原理和实现——7.ClockGatingCellConnection

scanchain的原理和实现——7.ClockGatingCellConnection Clock Gating Cell Connectionset_dft_configuration -connect_clock_gating enable 默认enableset_clock_gating_style -control_signal test_model | scan_enable -sequential_cell latch -positive_edge_logic {integrated } -control_point before -control_signal test_mode] -observation_point trueset_dft_clock_gating_configuration -exclude_elements [list] ⽤于At speed中control point :before VS after基于latch的clock gating要求使能信号始终在时钟的下降沿之后到达。

如果控制点在latch前,则不会违反要求、故障不会损坏时钟输出。

如果测试⼯具不⽀持将控制点在clock gating latch之前,则使⽤-control_point after将控制点插⼊clock gating latch之后。

Scan Enable VS Test ModeScan enable仅在scan mode下active;Test mode在整个test期间activeScan enable通常⽐Test mode带来更⾼的故障覆盖率。

Scan enable的故障覆盖率与没有clock gating的电路差不多。

但在某些情况下,必须使⽤Test mode。

例如,如果将point放在latch之前,并且测试⼯具不⽀持Scan enable控制点位置,则可能需要使⽤Test mode。

clock gating的验证方法

clock gating的验证方法Clock gating技术是一种用于减少数字电路功耗的有效方案。

它利用了时钟信号在数字电路中的控制作用,并对不活动的模块或者电路进行时钟屏蔽,从而避免了无用功耗的产生。

因此,验证Clock gating功能的正确性是至关重要的,下面将介绍几种验证方法。

首先,常用的验证方法是静态验证,它利用工具来模拟代码行为,并通过形式化推理或证明来验证其功能正确性。

这些工具包括面向模型的归纳法、反演技术以及有界模型检测等。

在静态验证中,可以使用Cadence Encounter RTL Compiler、Synopsys Design Compiler以及TSMC Power Compiler等工具来实现。

然后,模拟验证是另一种重要的验证方法,其采用仿真器来模拟电路行为,并通过观察仿真结果来验证其功能正确性和总体性能。

在Clock gating的模拟验证中,需要考虑多种情况,如多种工作状态、电源噪声等。

在模拟验证中,可以使用Cadence NC-Verilog、Synopsys VCS以及Mentor Graphics Questa等仿真器来实现。

此外,硬件测试是一种必要的验证方法,它通过实现设计并在实际硬件平台上进行测试来验证其功能正确性和性能。

硬件测试包括逻辑BIST、存储器BIST以及ATPG等,可以使用Altera Quartus II、Xilinx ISE以及Cadence Encounter Test等工具来实现。

最后,形式化验证也是一种越来越重要的验证方法,在形式化验证中,需要使用模型检验工具或基于定理证明工具来推导出设计的正确性证明。

形式化验证可以通过NuSMV、Cadence JasperGold以及Synopsys IC-Verify等工具来实现。

总之,Clock gating的验证方法是多种多样的,不同的验证方法在不同阶段都有其优缺点。

因此,在进行Clock gating的验证时,需要根据具体情况综合考虑,选择合适的验证方法。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

时钟门控技术(Clock Gating)

随着能源的日益短缺和地球的变暖,对电子产品的功耗要求越来越重要,如何降低电子产品的功耗是每一个电子工程师所要思考的问题。

对于半导体产品来说,一个数字电路的功耗有2部分构成,其一是静态功耗,通常表现为电子线路的漏电流,控制这部分功耗主要决定于生产工艺和所用的材料;其二是动态工作电流,而影响这部分功耗的因素很多,如电路设计的方式,线路的复杂程度,工作时时钟频率等。

本文谈的时钟门控技术就是一种非常简单和有效的功耗控制方法,它的基本原理就是通过关闭芯片上暂时用不到的功能和它的时钟,从而实现节省电流消耗的目的。

STM32中使用了这种时钟门控技术,请看下图是STM32的时钟分配示意图:图中以橙色标注的那些与门就是用于控制不同模块的时钟,用户可以在程序中通过适当的寄存器位,打开或关闭对应模块的时钟,以达到减低功耗的目的。

tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。