控制寄存器

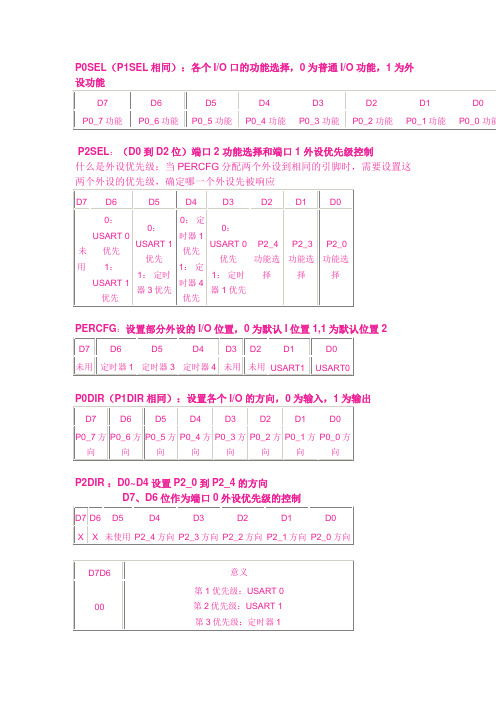

常用控制寄存器详解

P2IFG:D0~D4为P2_0~P2_4的中断标志位

D5为USD D+中断状态标志,当D+线有一个中断请求未决时设置该标志,用于检测USB挂起状态下的USB恢复事件。

当USB控制器没有挂起时不设

置该标志。

IEN2:中断使能2,0为中断禁止,1为中断使能

T1STAT:定时器1的状态寄存器,D4~D0为通道4~通道0的中断标志,D5为溢出标志位,当计数到最终技术值是自动置1。

T1CCTL0~T1CCTL4:定时器1通道0~通道4的工作方式设置。

D1D0为捕捉模式选择:00为不捕捉,01为上升沿捕获,10为下降沿捕获,11为上升或下降沿都捕获。

D2位为捕获或比较的选择,0为捕获模式,1为比较模式。

D5D4D3为比较模式的选择:000为发生比较式输出端置1,001为发生比较时输出端清0,010为比较时输出翻转,其他模式较少使用。

4MHZ,100为2MHZ,101为1MHZ,110为500KHZ,111为250KHZ。

当D6为1时,系统主时钟最高可采用频率为16MHZ。

U0GCR:USART0通用控制寄存器;。

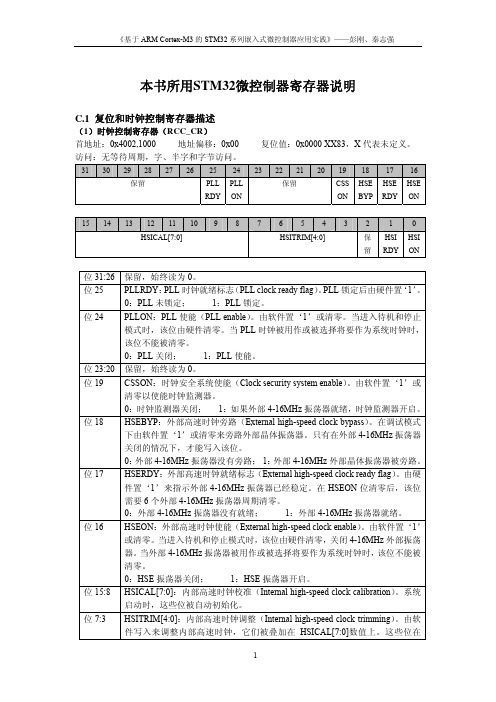

STM32微控制器寄存器说明

PLLXTPRE:HSE 分频器作为 PLL 输入(HSE divider for PLL entry)。由软件

置‘1’或清‘0’来分频 HSE 后作为 PLL 输入时钟。只能在关闭 PLL 时才能

写入此位。

0:HSE 不分频; 1:HSE 2 分频

PLLSRC:PLL 输入时钟源(PLL entry clock source)。由软件置‘1’或清‘0’

保 HSI HSI

留 RDY ON

位 31:26 位 25 位 24

位 23:20 位 19 位 18

位 17

位 16

位 15:8 位 7:3

保留,始终读为 0。 PLLRDY:PLL 时钟就绪标志(PLL clock ready flag)。PLL 锁定后由硬件置‘1’。 0:PLL 未锁定; 1:PLL 锁定。 PLLON:PLL 使能(PLL enable)。由软件置‘1’或清零。当进入待机和停止 模式时,该位由硬件清零。当 PLL 时钟被用作或被选择将要作为系统时钟时, 该位不能被清零。 0:PLL 关闭; 1:PLL 使能。 保留,始终读为 0。 CSSON:时钟安全系统使能(Clock security system enable)。由软件置‘1’或 清零以使能时钟监测器。 0:时钟监测器关闭; 1:如果外部 4-16MHz 振荡器就绪,时钟监测器开启。 HSEBYP:外部高速时钟旁路(External high-speed clock bypass)。在调试模式 下由软件置‘1’或清零来旁路外部晶体振荡器。只有在外部 4-16MHz 振荡器 关闭的情况下,才能写入该位。 0:外部 4-16MHz 振荡器没有旁路; 1:外部 4-16MHz 外部晶体振荡器被旁路。 HSERDY:外部高速时钟就绪标志(External high-speed clock ready flag)。由硬 件置‘1’来指示外部 4-16MHz 振荡器已经稳定。在 HSEON 位清零后,该位 需要 6 个外部 4-16MHz 振荡器周期清零。 0:外部 4-16MHz 振荡器没有就绪; 1:外部 4-16MHz 振荡器就绪。 HSEON:外部高速时钟使能(External high-speed clock enable)。由软件置‘1’ 或清零。当进入待机和停止模式时,该位由硬件清零,关闭 4-16MHz 外部振荡 器。当外部 4-16MHz 振荡器被用作或被选择将要作为系统时钟时,该位不能被 清零。 0:HSE 振荡器关闭; 1:HSE 振荡器开启。 HSICAL[7:0]:内部高速时钟校准(Internal high-speed clock calibration)。系统 启动时,这些位被自动初始化。 HSITRIM[4:0]:内部高速时钟调整(Internal high-speed clock trimming)。由软 件写入来调整内部高速时钟,它们被叠加在 HSICAL[7:0]数值上。这些位在

控制器和寄存器

控制器负责协调和控制CPU 内部各个部件的工作,确保 计算机指令的正确执行。

寄存器作为CPU内部的高速存 储单元,用于存储运算数据、 地址和状态信息,提高数据传

输和处理的速度。

嵌入式系统的应用

控制器和寄存器在嵌入式系统中也具有广泛的 应用,用于实现各种智能化控制功能。

嵌入式系统中的控制器根据预设的算法和程序 ,对输入信号进行处理并输出控制信号,以驱 动执行机构实现特定的动作或功能。

控制器与寄存器的协同工作

数据传输

控制器通过读写寄存器实现与硬件设备的数据传输。

控制逻辑

控制器通过配置和操作寄存器实现控制逻辑,的操作可以是同步或异步的,以 满足不同的应用需求。

04

CATALOGUE

控制器和寄存器的应用场景

工业控制系统的应用

控制器和寄存器在物联 网领域的应用将促进各 行业的数字化转型,提 升产业的整体竞争力。

控制器和寄存器在人工智能领域的应用

人工智能技术的快速发展为控制器和寄存器提供了新 的应用场景。

控制器和寄存器在人工智能领域的应用将有助于提高 机器的学习能力和数据处理能力,加速人工智能技术

的商业化进程。

控制器和寄存器在人工智能领域的应用将促进人工智 能技术的普及和应用,为各行业带来更多的商业机会

寄存器在嵌入式系统中用于存储程序代码、配 置参数、实时数据等信息,支持控制器的快速 响应和控制。

05

CATALOGUE

控制器和寄存器的未来发展

控制器和寄存器技术的创新

01

控制器和寄存器技术的持续创新将推动相关产业的发展,提高 生产效率和产品质量。

02

技术创新将带来更高效、更可靠的控制器和寄存器,以满足不

STM32f103寄存器说明书

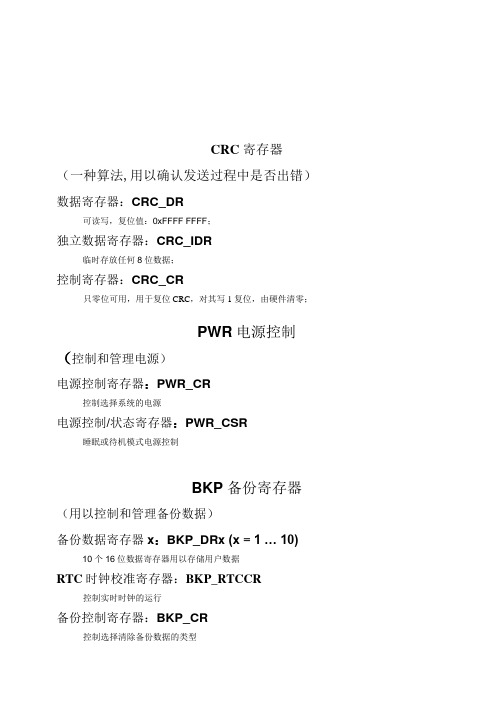

CRC寄存器(一种算法,用以确认发送过程中是否出错)数据寄存器:CRC_DR可读写,复位值:0xFFFF FFFF;独立数据寄存器:CRC_IDR临时存放任何8位数据;控制寄存器:CRC_CR只零位可用,用于复位CRC,对其写1复位,由硬件清零;PWR电源控制(控制和管理电源)电源控制寄存器:PWR_CR控制选择系统的电源电源控制/状态寄存器:PWR_CSR睡眠或待机模式电源控制BKP备份寄存器(用以控制和管理备份数据)备份数据寄存器x:BKP_DRx (x = 1 … 10) 10个16位数据寄存器用以存储用户数据RTC时钟校准寄存器:BKP_RTCCR控制实时时钟的运行备份控制寄存器:BKP_CR控制选择清除备份数据的类型备份控制/状态寄存器:BKP_CSR对侵入事件的控制RCC寄存器(时钟的选择、复位、分频)时钟控制寄存器(RCC_CR)各时钟状态显示时钟配置寄存器(RCC_CFGR)时钟分频时钟中断寄存器(RCC_CIR)控制就绪中断使能与否APB2外设复位寄存器(RCC_APB2RSTR) APB1外设复位寄存器(RCC_APB1RSTR) 复位APB各功能寄存器AHB外设时钟使能寄存器(RCC_AHBENR) AHB时钟使能控制APB2外设时钟使能寄存器(RCC_APB2ENR) APB1外设时钟使能寄存器(RCC_APB1ENR) APB1时钟使能控制备份域控制寄存器(RCC_BDCR)备份域时钟控制控制/状态寄存器(RCC_CSR)复位标志寄存器AHB外设时钟复位寄存器(RCC_AHBRSTR) 复位以太网MAC模块时钟配置寄存器2(RCC_CFGR2)时钟选择与分频GPIO寄存器(设置端口的功能)端口配置低寄存器(GPIOx_CRL) (x=A..E)端口配置高寄存器(GPIOx_CRH) (x=A..E)端口输入数据寄存器(GPIOx_IDR) (x=A..E)只读数据,读出IO口的状态端口输出数据寄存器(GPIOx_ODR) (x=A..E) 可读可写端口位设置/清除寄存器(GPIOx_BSRR) (x=A..E)端口位清除寄存器(GPIOx_BRR) (x=A..E)将某一端口清零端口配置锁定寄存器(GPIOx_LCKR) (x=A..E) 用于保护端口配值AFIO寄存器(将端口重映射到其它端口用以端口的第二功能)事件控制寄存器(AFIO_EVCR)选择时间输出端口与引脚复用重映射和调试I/O配置寄存器(AFIO_MAPR) 各寄存器功能引脚重映射选择外部中断配置寄存器1(AFIO_EXTICR1)外部中断配置寄存器2(AFIO_EXTICR2)外部中断配置寄存器3(AFIO_EXTICR3) 外部中断配置寄存器4(AFIO_EXTICR4) 外部中断引脚重映射选择EXTI 寄存器(外部中断控制器)中断屏蔽寄存器(EXTI_IMR)用于屏蔽或开放某一引脚的中断请求事件屏蔽寄存器(EXTI_EMR)用于屏蔽或开放某一引脚的事件上升沿触发选择寄存器(EXTI_RTSR) 禁止或允许某一引脚的上升沿触发下降沿触发选择寄存器(EXTI_FTSR) 禁止或允许某一引脚的下降沿触发软件中断事件寄存器(EXTI_SWIER) 控制某引脚的软件中断挂起寄存器(EXTI_PR)显示某线的引脚有无触发请求DMA寄存器(脱离cpu的传输模式)DMA中断状态寄存器(DMA_ISR)中断情况标志器DMA中断标志清除寄存器(DMA_IFCR) 手动清除标志位DMA通道x配置寄存器(DMA_CCRx)(x = 1…7)传输控制寄存器DMA通道x传输数量寄存器(DMA_CNDTRx)(x = 1…7)数据传输剩余数量存储器DMA通道x外设地址寄存器(DMA_CPARx)(x = 1…7)设置数据传输外设源或目标地址DMA通道x存储器地址寄存器(DMA_CMARx)(x = 1…7)设置存储器地址ADC寄存器(模数转换器)ADC状态寄存器(ADC_SR)AD转换标志寄存器ADC控制寄存器1(ADC_CR1)ADC控制寄存器2(ADC_CR2)设置AD转换的各种功能ADC采样时间寄存器1(ADC_SMPR1)ADC采样时间寄存器2(ADC_SMPR2)某通道选择固定的采样时间ADC注入通道数据偏移寄存器x (ADC_JOFRx)(x=1..4) 设置数据偏移量ADC看门狗高阀值寄存器(ADC_HTR)设置模拟看门狗的阀值高限ADC看门狗低阀值寄存器(ADC_LRT)设置模拟看门狗的阀值低限ADC规则序列寄存器1(ADC_SQR1)ADC规则序列寄存器2(ADC_SQR2)ADC规则序列寄存器3(ADC_SQR3)设置ADC顺序ADC注入序列寄存器(ADC_JSQR)ADC 注入数据寄存器x (ADC_JDRx) (x= 1..4)ADC数据结果寄存器ADC规则数据寄存器(ADC_DR)DAC寄存器(数模转换器)DAC控制寄存器(DAC_CR)DAC软件触发寄存器(DAC_SWTRIGR)DAC通道1的12位右对齐数据保持寄存器(DAC_DHR12R1) DAC通道1的12位左对齐数据保持寄存器(DAC_DHR12L1) DAC通道1的8位右对齐数据保持寄存器(DAC_DHR8R1) DAC通道2的12位右对齐数据保持寄存器(DAC_DHR12R2) DAC通道2的12位左对齐数据保持寄存器(DAC_DHR12L2) DAC通道2的8位右对齐数据保持寄存器(DAC_DHR8R2)双DAC的12位右对齐数据保持寄存器(DAC_DHR12RD)双DAC的12位左对齐数据保持寄存器(DAC_DHR12LD)双DAC的8位右对齐数据保持寄存器(DAC_DHR8RD) DAC通道1数据输出寄存器(DAC_DOR1)DAC通道2数据输出寄存器(DAC_DOR2)TIM1和TIM8寄存器(高级的定时计数寄存器)TIM1和TIM8控制寄存器1(TIMx_CR1)TIM1和TIM8控制寄存器2(TIMx_CR2)TIM1和TIM8从模式控制寄存器(TIMx_SMCR)TIM1和TIM8 DMA/中断使能寄存器(TIMx_DIER) TIM1和TIM8状态寄存器(TIMx_SR)TIM1和TIM8事件产生寄存器(TIMx_EGR)TIM1和TIM8捕获/比较模式寄存器1(TIMx_CCMR1) TIM1和TIM8捕获/比较模式寄存器2(TIMx_CCMR2) TIM1和TIM8捕获/比较使能寄存器(TIMx_CCER) TIM1和TIM8计数器(TIMx_CNT)TIM1和TIM8预分频器(TIMx_PSC)TIM1和TIM8自动重装载寄存器(TIMx_ARR)TIM1和TIM8重复计数寄存器(TIMx_RCR)TIM1和TIM8捕获/比较寄存器1(TIMx_CCR1)TIM1和TIM8捕获/比较寄存器2(TIMx_CCR2)TIM1和TIM8捕获/比较寄存器3(TIMx_CCR3)TIM1和TIM8捕获/比较寄存器(TIMx_CCR4)TIM1和TIM8刹车和死区寄存器(TIMx_BDTR)TIM1和TIM8 DMA控制寄存器(TIMx_DCR)TIM1和TIM8连续模式的DMA地址(TIMx_DMAR)TIMx寄存器(控制定时器)控制寄存器1(TIMx_CR1)控制寄存器2(TIMx_CR2)从模式控制寄存器(TIMx_SMCR)DMA/中断使能寄存器(TIMx_DIER)状态寄存器(TIMx_SR)事件产生寄存器(TIMx_EGR)捕获/比较模式寄存器1(TIMx_CCMR1)捕获/比较模式寄存器2(TIMx_CCMR2)捕获/比较使能寄存器(TIMx_CCER)计数器(TIMx_CNT)预分频器(TIMx_PSC)自动重装载寄存器(TIMx_ARR)捕获/比较寄存器1(TIMx_CCR1)捕获/比较寄存器2(TIMx_CCR2)捕获/比较寄存器3(TIMx_CCR3)捕获/比较寄存器4(TIMx_CCR4)DMA控制寄存器(TIMx_DCR)连续模式的DMA地址(TIMx_DMAR)TIM6和TIM7寄存器(基本定时计数器)TIM6和TIM7控制寄存器1(TIMx_CR1)TIM6和TIM7控制寄存器2(TIMx_CR2)TIM6和TIM7 DMA/中断使能寄存器(TIMx_DIER)TIM6和TIM7状态寄存器(TIMx_SR)TIM6和TIM7事件产生寄存器(TIMx_EGR)TIM6和TIM7计数器(TIMx_CNT)TIM6和TIM7预分频器(TIMx_PSC)TIM6和TIM7自动重装载寄存器(TIMx_ARR)RTC寄存器(实时时钟)RTC控制寄存器高位(RTC_CRH)RTC控制寄存器低位(RTC_CRL)16.4.3 RTC预分频装载寄存器(RTC_PRLH/RTC_PRLL) 16.4.4 RTC预分频器余数寄存器(RTC_DIVH / RTC_DIVL)RTC计数器寄存器(RTC_CNTH / RTC_CNTL) 16.4.6 RTC闹钟寄存器(RTC_ALRH/RTC_ALRL)IWDG寄存器(独立看门狗,用以监督系统硬件的正常运行)键寄存器(IWDG_KR)预分频寄存器(IWDG_PR)重装载寄存器(IWDG_RLR)状态寄存器(IWDG_SR)窗口看门狗(WWDG)寄存器(用以监督软件的正常运行)控制寄存器(WWDG_CR)配置寄存器(WWDG_CFR)状态寄存器(WWDG_SR)FSMC寄存器(可变静态存储控制器)NOR闪存和PSRAM控制器寄存器SRAM/NOR闪存片选控制寄存器1…4 (FSMC_BCR1…4)SRAM/NOR闪存片选时序寄存器1…4 (FSMC_BTR1…4) SRAM/NOR闪存写时序寄存器1…4 (FSMC_BWTR1…4)NAND闪存和PC卡控制器寄存器PC卡/NAND闪存控制寄存器2..4 (FSMC_PCR2..4) FIFO状态和中断寄存器2..4 (FSMC_SR2..4)通用存储空间时序寄存器 2..4 (FSMC_PMEM2..4)属性存储空间时序寄存器 2..4 (FSMC_PATT2..4)I/O空间时序寄存器4 (FSMC_PIO4)ECC结果寄存器2/3 (FSMC_ECCR2/3)SDIO寄存器(数据传输控制器)SDIO电源控制寄存器(SDIO_POWER) SDIO时钟控制寄存器(SDIO_CLKCR) SDIO参数寄存器(SDIO_ARG)SDIO命令寄存器(SDIO_CMD)SDIO命令响应寄存器(SDIO_RESPCMD) SDIO响应1..4寄存器(SDIO_RESPx) SDIO数据定时器寄存器(SDIO_DTIMER) SDIO数据长度寄存器(SDIO_DLEN)SDIO数据控制寄存器(SDIO_DCTRL SDIO数据计数器寄存器(SDIO_DCOUNT) SDIO状态寄存器(SDIO_STA)SDIO清除中断寄存器(SDIO_ICR)SDIO中断屏蔽寄存器(SDIO_MASK)SDIO FIFO计数器寄存器(SDIO_FIFOCNT) SDIO数据FIFO寄存器(SDIO_FIFO)USB寄存器(usb传输控制器)通用寄存器USB控制寄存器(USB_CNTR)USB中断状态寄存器(USB_ISTR)USB帧编号寄存器(USB_FNR)USB设备地址寄存器(USB_DADDR)USB分组缓冲区描述表地址寄存器(USB_BTABLE)端点寄存器USB 端点n寄存器(USB_EPnR), n=[0..7]缓冲区寄存器发送缓冲区地址寄存器n(USB_ADDRn_TX)发送数据字节数寄存器n(USB_COUNTn_TX)接收缓冲区地址寄存器n(USB_ADDRn_RX)接收数据字节数寄存器n(USB_COUNTn_RX)CAN 寄存器(控制寄存器)CAN控制和状态寄存器CAN主控制寄存器(CAN_MCR)CAN主状态寄存器(CAN_MSR)CAN发送状态寄存器(CAN_TSR)CAN接收FIFO 0寄存器(CAN_RF0R)CAN接收FIFO 1寄存器(CAN_RF1R)CAN中断使能寄存器(CAN_IER)CAN错误状态寄存器(CAN_ESR)CAN位时序寄存器(CAN_BTR)CAN寄存器发送标识符寄存器(CAN_TIxR) (x=0..2)发送数据长度和时间戳寄存器(CAN_TDTxR) (x=0..2)发送低字节数据寄存器(CAN_TDLxR) (x=0..2)发送高字节数据寄存器(CAN_TDHxR) (x=0..2)接收FIFO标识符寄存器(CAN_RIxR) (x=0..1)接收FIFO数据长度和时间戳寄存器(CAN_RDTxR) (x=0..1)接收FIFO低字节数据寄存器(CAN_RDLxR) (x=0..1)接收FIFO高字节数据寄存器(CAN_RDHxR) (x=0..1)CAN过滤器寄存器CAN 过滤器主控寄存器(CAN_FMR)CAN 过滤器模式寄存器(CAN_FM1R)CAN 过滤器位宽寄存器(CAN_FS1R)CAN 过滤器FIFO关联寄存器(CAN_FFA1R)CAN 过滤器激活寄存器(CAN_FA1R)CAN 过滤器组i的寄存器x (CAN_FiRx) (互联产品中i=0..27,其它产品中i=0..13;x=1..2)SPI和I2S寄存器(串行外设接口控制器)SPI控制寄存器1(SPI_CR1)SPI控制寄存器2(SPI_CR2)SPI 状态寄存器(SPI_SR)SPI 数据寄存器(SPI_DR)SPI CRC多项式寄存器(SPI_CRCPR)SPI Rx CRC寄存器(SPI_RXCRCR)SPI Tx CRC寄存器(SPI_TXCRCR)SPI_I2S配置寄存器(SPI_I2S_CFGR)SPI_I2S预分频寄存器(SPI_I2SPR)I2C寄存器(数据传输寄存器)控制寄存器1(I2C_CR1)控制寄存器2(I2C_CR2)自身地址寄存器1(I2C_OAR1)自身地址寄存器2(I2C_OAR2)数据寄存器(I2C_DR)状态寄存器1(I2C_SR1)状态寄存器2 (I2C_SR2)时钟控制寄存器(I2C_CCR)TRISE寄存器(I2C_TRISE)USART寄存器(通用同步异步收发器)状态寄存器(USART_SR)数据寄存器(USART_DR)波特比率寄存器(USART_BRR)控制寄存器1(USART_CR1)控制寄存器2(USART_CR2)控制寄存器3(USART_CR3)保护时间和预分频寄存器(USART_GTPR)OTG_FS控制和状态寄存器(数据传输控制器)OTG_FS全局寄存器OTG_FS控制和状态寄存器(OTG_FS_GOTGCTL)OTG_FS中断寄存器(OTG_FS_GOTGINT)OTG_FS AHB配置寄存器(OTG_FS_GAHBCFG)OTG_FS_USB配置寄存器(OTG_FS_GUSBCFG)OTG_FS复位寄存器(OTG_FS_GRSTCTL)OTG_FS控制器中断寄存器(OTG_FS_GINTSTS)OTG_FS中断屏蔽寄存器(OTG_FS_GINTMSK)OTG_FS接收状态调试读/OTG状态读和POP寄存器(OTG_FS_GRXSTSR / OTG_FS_GRXSTSP)OTG_FS接收FIFO长度寄存器(OTG_FS_GRXFSIZ)OTG_FS非周期性TX FIFO长度寄存器(OTG_FS_GNPTXFSIZ)OTG_FS非周期性TX FIFO/请求队列状态寄存器(OTG_FS_GNPTXSTS)OTG_FS通用控制器配置寄存器(OTG_FS_GCCFG)OTG_FS控制器ID寄存器(OTG_FS_CID)OTG_FS主机周期性发送FIFO长度寄存器(OTG_FS_HPTXFSIZ)OTG_FS设备IN端点发送FIFO长度寄存器(OTG_FS_DIEPTXFx)(其中x是FIFO的编号,x=1…4)主机模式下的寄存器OTG_FS主机模式配置寄存器(OTG_FS_HCFG)OTG_FS主机帧间隔寄存器(OTG_FS_HFIR)OTG_FS主机帧号/帧时间剩余寄存器(OTG_FS_HFNUM)OTG_FS主机周期性发送FIFO/请求队列寄存器(OTG_FS_HPTXSTS)OTG_FS主机所有通道中断寄存器(OTG_FS_HAINT)OTG_FS主机所有通道中断屏蔽寄存器(OTG_FS_HAINTMSK)OTG_FS主机端口控制和状态寄存器(OTG_FS_HPRT)OTG_FS主机通道x特性寄存器(OTG_FS_HCCHARx)(此处x代码通道号,x = 0...7)OTG_FS主机通道x中断寄存器(OTG_FS_HCINTx)(其中x代表通道号,x=0...7,)OTG_FS主机通道x中断屏蔽寄存器(OTG_FS_HCINTMSKx)(其中x为通道号,x=0...7) OTG_FS主机通道x传输长度寄存器(OTG_FS_HCTSIZx)(其中x为通道号,x=0...7)设备模式下的寄存器OTG_FS设备配置寄存器(OTG_FS_DCFG)OTG_FS设备控制寄存器(OTG_FS_DCTL)OTG_FS设备状态寄存器(OTG_FS_DSTS)OTG_FS设备IN端点通用中断屏蔽寄存器(OTG_FS_DIEPMSK)OTG_FS设备OUT端点通用中断屏蔽寄存器(OTG_FS_DOEPMSK)OTG_FS设备所有端点中断寄存器(OTG_FS_DAINT)OTG_FS所有端点中断屏蔽寄存器(OTG_FS_DAINTMSK)OTG_FS设备V BUS放电时间寄存器(OTG_FS_DVBUSDIS)OTG_FS设备V BUS脉冲时间寄存器(OTG_FS_DVBUSPULSE)OTG_FS设备IN端点FIFO空中断屏蔽寄存器(OTG_FS_DIEPEMPMSK)OTG_FS设备控制IN端点0控制寄存器(OTG_FS_DIEPCTL0)OTG设备端点x控制寄存器(OTG_FS_DIEPCTLx)(其中x为端点号,x=1…3)OTG_FS设备控制OUT端点0控制寄存器(OTG_FS_DOEPCTL0)OTG_FS设备OUT端点x控制寄存器(OTG_FS_DOEPCTLx)(其中x为端点号,x=1…3) OTG_FS设备端点x中断寄存器(OTG_FS_DIEPINTx)(其中x为端点号,x=0…3)OTG_FS设备端点x中断寄存器(OTG_FS_DOEPINTx)(其中x为端点号,x=0…3)OTG_FS设备IN端点0传输长度寄存器(OTG_FS_DIEPTSIZ0)OTG_FS设备OUT端点0传输长度寄存器(OTG_FS_DOEPTSIZ0)OTG_FS设备端点x传输长度寄存器(OTG_FS_DIEPTSIZx)(其中x为端点号,x=1…3) OTG_FS设备IN端点传输FIFO状态寄存器(OTG-FS_DTXFSTSx)(其中x为端点号,x=0…3)OTG_FS设备端点x传输长度寄存器(OTG_FS_DOEPTSIZx)(其中x为端点号,x=1…3) OTG_FS电源和时钟门控寄存器(OTG_FS_PCGCCTL)以太网寄存器(通信传输控制器)MAC寄存器以太网MAC设置寄存器(ETH_MACCR)以太网MAC帧过滤器寄存器(ETH_MACFFR)以太网MAC Hash列表高寄存器(ETH_MACHTHR)以太网MAC Hash列表低寄存器(ETH_MACHTLR)以太网MAC MII地址寄存器(ETH_MACMIIAR)以太网MAC MII数据寄存器(ETH_MACMIIDR)以太网MAC流控寄存器(ETH_MACFCR)以太网MAC VLAN标签寄存器(ETH_MACVLANTR)以太网MAC远程唤醒帧过滤器寄存器(ETH_MACRWUFFR)以太网MAC PMT控制和状态寄存器(ETH_MACPMTCSR)以太网MAC中断状态寄存器(ETH_MACSR)以太网MAC中断屏蔽寄存器(ETH_MAIMR)以太网MAC地址0高寄存器(ETH_MACA0HR)以太网MAC地址0低寄存器(ETH_MACA0LR)以太网MAC地址1高寄存器(ETH_MACA1HR)以太网MAC地址1低寄存器(ETH_MACA1LR)以太网MAC地址2高寄存器(ETH_MACA2HR)以太网MAC地址2低寄存器(ETH_MACA2LR)以太网MAC地址3高寄存器(ETH_MACA3HR)以太网MAC地址3低寄存器(ETH_MACA3LR)MMC寄存器以太网MMC控制寄存器(ETH_MMCCR)以太网MMC接收中断寄存器(ETH_MMCRIR)以太网MMC发送中断寄存器(ETH_MMCTIR)以太网MMC接收中断屏蔽寄存器(ETH_MMCRIMR)以太网MMC发送中断屏蔽寄存器(ETH_MMCTIMR)以太网MMC1次冲突后发送”好”帧的计数器寄存器(ETH_MMCTGFSCCR)以太网MMC1次以上冲突后发送”好”帧的计数器寄存器(ETH_MMCTGFMSCCR)以太网MMC发送”好”帧的计数器寄存器(ETH_MMCTGFCR)以太网MMC CRC错误接收帧计数器寄存器(ETH_ MMCRFCECR)以太网MMC对齐错误接收帧计数器寄存器(ETH_ MMCRFAECR)以太网MMC接收帧”好”单播帧计数器寄存器(ETH_ MMCRGUFCR)27.8.3。

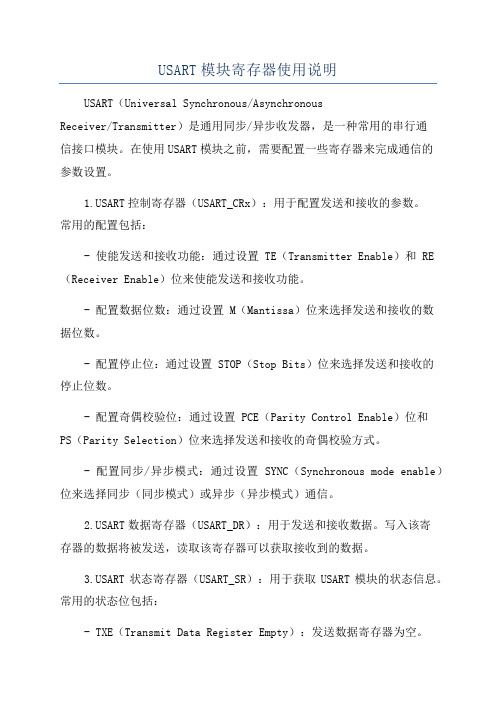

USART模块寄存器使用说明

USART模块寄存器使用说明USART(Universal Synchronous/AsynchronousReceiver/Transmitter)是通用同步/异步收发器,是一种常用的串行通信接口模块。

在使用USART模块之前,需要配置一些寄存器来完成通信的参数设置。

ART控制寄存器(USART_CRx):用于配置发送和接收的参数。

常用的配置包括:- 使能发送和接收功能:通过设置 TE(Transmitter Enable)和 RE (Receiver Enable)位来使能发送和接收功能。

- 配置数据位数:通过设置 M(Mantissa)位来选择发送和接收的数据位数。

- 配置停止位:通过设置 STOP(Stop Bits)位来选择发送和接收的停止位数。

- 配置奇偶校验位:通过设置 PCE(Parity Control Enable)位和PS(Parity Selection)位来选择发送和接收的奇偶校验方式。

- 配置同步/异步模式:通过设置 SYNC(Synchronous mode enable)位来选择同步(同步模式)或异步(异步模式)通信。

ART数据寄存器(USART_DR):用于发送和接收数据。

写入该寄存器的数据将被发送,读取该寄存器可以获取接收到的数据。

ART状态寄存器(USART_SR):用于获取USART模块的状态信息。

常用的状态位包括:- TXE(Transmit Data Register Empty):发送数据寄存器为空。

- RXNE(Read Data Register Not Empty):接收数据寄存器非空。

- FE(Framing Error):帧错误。

- ORE(Overrun Error):溢出错误。

- NE(Noise Error):噪声错误。

ART波特率寄存器(USART_BRR):用于配置通信的波特率。

波特率=时钟频率/(16*USARTDIV)。

ART控制寄存器2(USART_CR2)和寄存器3(USART_CR3):用于配置流控制、硬件流控制、DMA接口等其他功能。

UART寄存器介绍

UART寄存器介绍UART(Universal Asynchronous Receiver/Transmitter)是一种串行通信协议,常用于各种微控制器和外围设备之间的通信。

UART寄存器是用来配置和控制UART模块的寄存器,包括数据传输、波特率、中断、状态等方面。

本文将从这几个方面详细介绍UART寄存器。

1.数据传输寄存器:数据传输寄存器用来存储和传输数据。

在发送数据时,将要发送的数据写入数据寄存器,发送完毕后,数据寄存器将被清空准备接收下一个数据。

在接收数据时,接收到的数据会存储在数据寄存器中,供读取或进一步处理。

2.波特率寄存器:波特率寄存器用来设置UART通信的波特率,它决定了数据传输的速率。

波特率寄存器通常是一个16位寄存器,低8位用来表示分频器的分频值,高8位用来表示分频器的倍频值。

通过设置不同的分频值和倍频值,可以实现不同的波特率。

具体的计算公式如下:波特率=时钟频率/(分频值*倍频值)3.中断寄存器:中断寄存器用来配置和控制UART模块的中断。

通过设置中断使能位和中断标志位,可以实现在特定事件发生时触发相应的中断处理程序。

常见的中断包括接收到数据中断、发送数据完成中断、数据溢出中断等。

4.状态寄存器:状态寄存器用来提供UART模块的状态信息。

常见的状态包括发送缓冲区为空、接收缓冲区不为空、接收缓冲区溢出、发送完成等。

通过读取状态寄存器的值,可以了解UART模块的当前状态,并进行相应的处理。

5.控制寄存器:控制寄存器用来配置和控制UART模块的行为。

它可以设置UART模块的工作方式、数据位数、停止位数、校验方式等。

通过写入控制寄存器的不同值,可以改变UART的工作模式,并对数据进行校验等处理。

6.波特率发生器寄存器:波特率发生器寄存器用来配置UART模块的波特率发生器。

波特率发生器根据设置的时钟频率和波特率,产生传输数据时所需要的时钟信号。

通过修改波特率发生器寄存器的值,可以调整UART模块的波特率。

寄存器结构、存储器管理

08

例: MOV AX, [BX+03H]

CX——Count可以作计数寄存器使用。 在循环LOOP指令和串处理指令中用作隐含计数器。 例: MOV CX , 200H AGAIN: …… …… LOOP AGAIN ;(CX)-1(CX),结果0转AGAIN DX——Data可以作为数据寄存器使用。 一般在双字长乘除法运算时, 把DX和AX组合在一起存放一个双字长(32位)数,DX用来存放高16位; 对某些I/O操作DX可用来存放I/O的端口地址(口地址 256)。 例: MUL BX ; (AX)(BX)(DX)(AX) 例: IN AL , DX

奇偶标志PF(Parity Flag)

若算术运算的结果有溢出,则OF=1;

否则 OF=0

3AH + 7CH=B6H,产生溢出:OF=1 AAH + 7CH=(1)26H,没有溢出:OF=0

溢出标志OF(Overflow Flag)

3AH+7CH=B6H,就是58+124=182,

什么是溢出

处理器内部以补码表示有符号数 8位表达的整数范围是:+127 ~ -128 16位表达的范围是:+32767 ~ -32768 如果运算结果超出这个范围,就产生了溢出 有溢出,说明有符号数的运算结果不正确

01

AX——(Accumulator)作为累加器。

02

它是算术运算的主要寄存器,

03

所有I/O指令都使用这一寄存器与外部设备交换数据。

04

例: IN AL , 20H

05

OUT 30H , AX

06

BX——Base用作基址寄存器使用。

07

在计算内存储器地址时,经常用来存放基址。

0

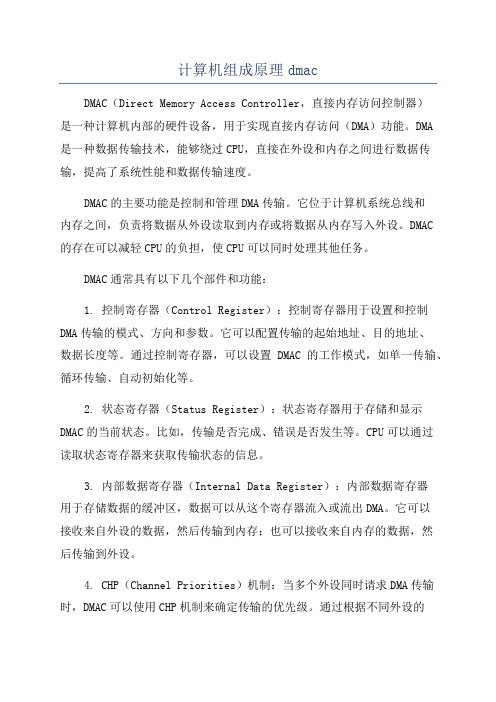

计算机组成原理dmac

计算机组成原理dmacDMAC(Direct Memory Access Controller,直接内存访问控制器)是一种计算机内部的硬件设备,用于实现直接内存访问(DMA)功能。

DMA是一种数据传输技术,能够绕过CPU,直接在外设和内存之间进行数据传输,提高了系统性能和数据传输速度。

DMAC的主要功能是控制和管理DMA传输。

它位于计算机系统总线和内存之间,负责将数据从外设读取到内存或将数据从内存写入外设。

DMAC的存在可以减轻CPU的负担,使CPU可以同时处理其他任务。

DMAC通常具有以下几个部件和功能:1. 控制寄存器(Control Register):控制寄存器用于设置和控制DMA传输的模式、方向和参数。

它可以配置传输的起始地址、目的地址、数据长度等。

通过控制寄存器,可以设置DMAC的工作模式,如单一传输、循环传输、自动初始化等。

2. 状态寄存器(Status Register):状态寄存器用于存储和显示DMAC的当前状态。

比如,传输是否完成、错误是否发生等。

CPU可以通过读取状态寄存器来获取传输状态的信息。

3. 内部数据寄存器(Internal Data Register):内部数据寄存器用于存储数据的缓冲区,数据可以从这个寄存器流入或流出DMA。

它可以接收来自外设的数据,然后传输到内存;也可以接收来自内存的数据,然后传输到外设。

4. CHP(Channel Priorities)机制:当多个外设同时请求DMA传输时,DMAC可以使用CHP机制来确定传输的优先级。

通过根据不同外设的优先级,DMAC可以优先处理最高优先级的传输请求,提高数据传输的效率。

5. 描述符(Descriptor):描述符是一种数据结构,用于描述DMA传输的一些重要信息,如源和目的地址、传输长度等。

在传输过程中,DMAC可以根据描述符中的信息进行数据传输。

多个描述符可以连接在一起,构成一个传输链表,从而实现复杂的数据传输操作。

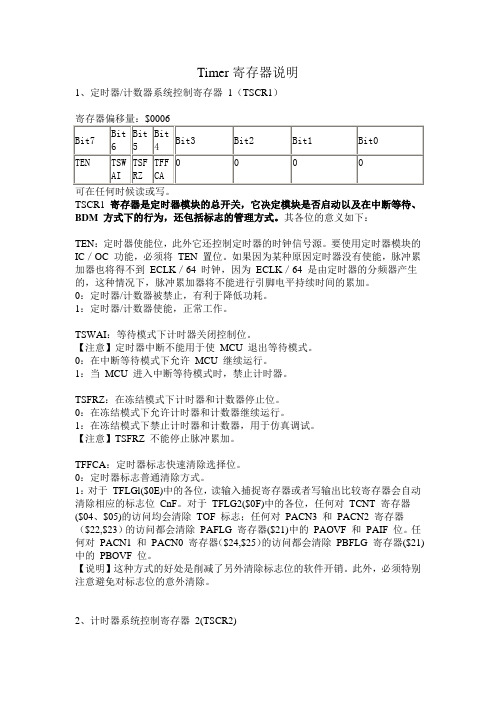

Timer寄存器说明

Timer寄存器说明1、定时器/计数器系统控制寄存器1(TSCR1)TSCR1 寄存器是定时器模块的总开关,它决定模块是否启动以及在中断等待、BDM 方式下的行为,还包括标志的管理方式。

其各位的意义如下:TEN:定时器使能位,此外它还控制定时器的时钟信号源。

要使用定时器模块的IC/OC 功能,必须将TEN 置位。

如果因为某种原因定时器没有使能,脉冲累加器也将得不到ECLK/64 时钟,因为ECLK/64 是由定时器的分频器产生的,这种情况下,脉冲累加器将不能进行引脚电平持续时间的累加。

0:定时器/计数器被禁止,有利于降低功耗。

1:定时器/计数器使能,正常工作。

TSWAI:等待模式下计时器关闭控制位。

【注意】定时器中断不能用于使MCU 退出等待模式。

0:在中断等待模式下允许MCU 继续运行。

1:当MCU 进入中断等待模式时,禁止计时器。

TSFRZ:在冻结模式下计时器和计数器停止位。

0:在冻结模式下允许计时器和计数器继续运行。

1:在冻结模式下禁止计时器和计数器,用于仿真调试。

【注意】TSFRZ 不能停止脉冲累加。

TFFCA:定时器标志快速清除选择位。

0:定时器标志普通清除方式。

1:对于TFLGl($0E)中的各位,读输入捕捉寄存器或者写输出比较寄存器会自动清除相应的标志位CnF。

对于TFLG2($0F)中的各位,任何对TCNT 寄存器($04、$05)的访问均会清除TOF 标志;任何对PACN3 和PACN2 寄存器($22,$23)的访问都会清除PAFLG 寄存器($21)中的PAOVF 和PAIF 位。

任何对PACN1 和PACN0 寄存器($24,$25)的访问都会清除PBFLG 寄存器($21)中的PBOVF 位。

【说明】这种方式的好处是削减了另外清除标志位的软件开销。

此外,必须特别注意避免对标志位的意外清除。

2、计时器系统控制寄存器2(TSCR2)寄存器偏移量:$000DTOI:定时器/计时器溢出中断使能。

单片机笔记-寄存器、引脚及其英文名称缩写

单片机笔记-寄存器、引脚及其英文名称缩写在单片机开发过程中,我们常常会涉及到寄存器和引脚的使用。

寄存器是用于存储和处理数据的重要组成部分,而引脚则是用于连接外部设备和单片机的接口。

了解寄存器、引脚及其英文名称缩写是学习和理解单片机编程的重要一步。

一、寄存器寄存器是单片机中的一种特殊功能寄存器,它们用来存储特定的信息,如状态、控制和数据等。

寄存器的使用是通过对其地址进行读/写操作来实现的。

在单片机中,存在着许多不同的寄存器,下面是一些常见的寄存器及其英文名称缩写:1. 状态寄存器(Status Register) - SR状态寄存器用于存储和显示一些跟运算或处理结果有关的标志位,如进位标志位、溢出标志位、零标志位等。

通过对状态寄存器的读写,可以获取或设置这些标志位的值。

2. 数据寄存器(Data Register) - DR数据寄存器用于存储临时数据,如中间计算结果或输入/输出数据等。

读写数据寄存器时,可以进行数据的读取或写入操作。

3. 控制寄存器(Control Register) - CR控制寄存器用于控制某些外设或特定功能的工作方式,如时钟控制寄存器、中断控制寄存器等。

写入或读取控制寄存器可以实现对相应功能的配置和控制。

4. 地址寄存器(Address Register) - AR地址寄存器用于存储指令和数据的地址信息。

在程序执行过程中,地址寄存器可以用于指示当前要执行的指令或要读取/写入数据的地址。

二、引脚引脚是单片机的外部接口,通过引脚可以与其他电子元件或设备进行连接和通信。

引脚的使用通常包括输入输出、中断触发、时钟输入等功能。

下面是一些常见的引脚及其英文名称缩写:1. 电源引脚(Power Pin) - VCC、GND电源引脚用于提供单片机的供电电源。

其中,VCC用于给单片机提供正电源,而GND则是单片机的接地端。

2. 输入引脚(Input Pin) - IN输入引脚用于接收外部信号。

SJA1000 CAN控制器 peil模式 寄存器

验收屏蔽1

22 RX数据4 RX数据2 TX数据4 TX数据2 验收屏蔽2

验收屏蔽2

23 RX数据5 RX数据3 TX数据5 TX数据3 验收屏蔽3

24 RX数据6 RX数据4 TX数据6 TX数据4 保留(00H)

25 RX数据7 RX数据5 TX数据7 TX数据5 保留(00H)

26 RX数据8 RX数据6 TX数据8 TX数据6 保留(00H)

IER.0 RIE

接收中断使能

BTR0.7 SJW.1

同步跳转宽度1

BTR0.6 SJW.0

同步跳转宽度0

BTR0.5 BRT.5

波特率预设值5

总线定时0

BTR0.4 BRT.4 BTR0.3 BRT.3

波特率预设值4 波特率预设值3

BTR0.2 BRT.2

波特率预设值2

BTR0.1 BRT.1

波特率预设值1

1

SR.3

TCS

发送完毕状态

1

SR.2

TBS

发送缓冲器状态

1

1

SR.1

DOS

数据溢出状态

0

0)

SR.0

RBS

接收缓冲器状态

0

0

IR.7

BEI

总线出错状态

0

0

IR.6

ALI

仲裁丢失中断

0

0

IR.5

EPI

错误消极中断

0

0

中断

IR.4

WUI

唤醒中断

0

0

IR.3

DOI

数据溢出中断

0

0

IR.2

EI

错误警报中断

4 RXFIFO 的内部读/写指针复位到初始化值 连续的读 RXB 口将会得到一些未定义的值 一部分是

PMM寄存器解析

PMMCTL0 电源管理系统控制寄存器PMMKEY 第15-8位PMM密码,通常读为096h;必须被写入0A5h否则引发PUC;PMMHPMRE 第7 位全局高电源模式请求位,PMMHPMRE位置1,任何模式都可以要求PMMv高电源模式;Reserved 第6-5位保留位,通常为0;PMMREGOFF第4位稳压器关闭,详见“禁用VCORE 稳压器-LPM5”章;PMMSWPOR 第3 位软件POR,此位置1会引发POR,此位自动清除;PMMSWBOR 第2 位软件BOR,此位置1会引发BOR,此位自动清除;PMMCOREV 第1-0位核心电压,细节参看器件特殊资料00 VCORE典型值为1.4 V.01 VCORE典型值为1.6 V.10 VCORE典型值为 1.8 V.11VCORE典型值为1.9 VPMMCLT1 电源管理系统控制寄存器Reserved 第15-6位保留位,通常为0;PMMCMD 第5-4位电压稳压器电流模式00 电压稳压器电流范围由低功耗模式定义01 电压稳压器电流范围由低功耗模式定义10 电压稳压器被强制进入低电流模式11 电压稳压器被强制进入全性能模式Reserved 第3-2位保留位,通常为0;PMMREFACC 第1位PMM 参考精度。

如果PMMREFACC 置1,电压基准的功耗被降低;电压基准的精确度尤其会在较高温度时降低。

PMMREFMD 第0 位PMM 参考模式。

如果电压稳压器在全性能模式下,那么电压参考就运行在连续(静态)模式下;如果PMMREFMD 置1 而且电压稳压器在全性能模式下,那么电压参考的电流消耗就被降低。

电压基准(参考)是的精度也会降低。

SVSMHCTL 高端供电电压监控与监视控制寄存器SVMHFP 第15 位SVM高电平全性能模式。

如果此位置1则SVMH 工作在全性能模式下;0 正常模式,延迟典型为150us,详见器件特殊手册。

1 全性能模式,典型延迟为1us,详见器件特殊手册。

单片机中常用寄存器的功能介绍

1.定时器/计数器控制寄存器TCON定时器/计数器控制寄存器TCON的地址为88H,可以位读写,控制T0、T1的启动和停止计数,同时包含了T0、T1是否溢出的状态。

其功能如下:TCON.7TCON.6TCON.5TCON.4TCON.3TCON.2TCON.1TCON.0TF1TR1TF0TR0IE1IT1IE0IT0⑴TF1是定时器T1的溢出申请位。

定时器T1被允许计数以后,从初值开始加1计数,当产生溢出时置TF1=1,向CPU请求中断。

到CPU响应该中断后才由硬件自动清0,也可以由查询程序清0(软件清零)。

⑵TF0是定时器T0的溢出申请位。

其作用类同于TF1。

TF0实际上是T0中断触发器的一个输出端。

⑶IE1是外部中断INT1请求标志位。

当CPU检测到在INT1管脚上出现低电平或脉冲下降沿的外部中断信号时,由硬件置位IE1=1,请求中断。

CPU响应中断并运行中断服务程序后,如脉冲边沿触发方式,则IE1位被硬件自动清0。

⑷IT1是外部中断INT1请求控制位,由程序来置1或清0。

IT1=0时,外部中断INT1被设置为电平触发方式,当INT1输入低电平时,置位IE1,申请中断,直到该中断被CPU响应。

同时,在该中断服务程序执行完之前,外部中断源有效电平必须被撤消,否则将产生另一次中断。

IT1=1时,外部中断1为边沿触发方式,CPU如果采样高电平到低电平跳变,则硬件自动对IE1置1,申请中断。

CPU响应中断后,IE1由硬件自动清0。

⑸IE0是外部中断INT0请求标志位。

⑹IT0是外部中断INT0触发方式控制位。

定时器计数器结构框图2.定时器/计数器方式寄存器TMOD选择定时器/计数器T0、T1的功能和工作方式,字节地址为89H。

TMOD D7D6D5D4D3D2D1D089H GATE C/T M1M0GATE C/T M1M0说明:M1、M0:工作方式选择位,用于对T0的四种工作方式,T1的三种工作方式进行选择。

单片机中寄存器的作用

单片机中寄存器的作用单片机中寄存器的作用1、寄存器的作用寄存器是单片机中最重要的部件之一,它可以保存信息(数据和指令),以及控制信号。

寄存器可以把数据存放在内部,以便处理器对其进行操作。

所有的电脑、控制系统中都要求有寄存器,它们可以依据操作系统、存储器或处理器的要求,在操作系统、存储器或处理器之间传递信息。

2、寄存器的功能(1)存储寄存器存储寄存器是一种用于存放控制指令、地址、数据等信息的存储器,可以把各种信息存放在内部,以便处理器对其进行操作。

(2)控制寄存器控制寄存器用来控制电路的运行,它可以把外部信号转换成内部控制信号。

(3)状态寄存器状态寄存器可以把外部信号转换成内部状态码,用来描述当前的状态,它可以用来检测、追踪和控制系统的运行状态,例如报警状态、可断电状态等。

(4)状态传感器状态传感器是一种特殊的寄存器,它能够检测电路中的状态,可以通过状态传感器确定电路的某个状态是否合法。

(5)常量存储器常量存储器是一种用于存储固定数据的存储器,它可以把特定的值存储下来,以便在日后使用。

例如,时钟时间、计算机参数或系统参数等。

3、寄存器的用途(1)控制存储器存储器可以把指令和数据存放在寄存器上,以便处理器读取它。

存储器可以将指令转换成控制信号,以便处理器能够控制其他电路的运行。

(2)状态检测状态寄存器可以用来检测系统的状态,比如有无故障,有无内存空间,有无电源等。

它可以帮助程序员更好的控制电路的运行,实现系统的自检和自动恢复。

(3)定时器定时器是一种特殊的寄存器,它能够定时记录系统的运行时间,也可以用来生成时钟信号,以便系统能够在合适的时间进行操作。

UART寄存器介绍

UART寄存器介绍UART(通用异步收发器)是一种常用的串行通信接口,可以实现计算机与外部设备之间的数据传输。

在UART的工作过程中,寄存器是起着重要作用的,它们用于控制和管理数据的收发、存储和传输。

本文将介绍常用的UART寄存器,并详细说明它们的功能和用途。

1.UART状态寄存器(USR):UART状态寄存器用于存储UART当前的状态信息,包括数据收发状态、错误标志等。

常见的状态标志位包括接收缓冲区满(RXF)标志、发送缓冲区空(TXE)标志、奇偶校验错误(PERR)标志、帧错误(FERR)标志等。

通过读取该寄存器的状态位,可以实时监测UART的状态。

2.数据寄存器(DR):数据寄存器用于存储UART接收和发送的数据。

当UART接收到数据时,数据将存储在该寄存器中;当UART发送数据时,数据将从该寄存器中传输出去。

通过读取和写入该寄存器,可以实现数据的收发操作。

3.波特率寄存器(BAUD):波特率寄存器用于设置UART的数据传输速率,即波特率。

波特率是指UART每秒钟发送或接收的数据位数。

通过修改该寄存器的值,可以调整UART的波特率,以适应不同的数据传输需求。

4.控制寄存器(CR):控制寄存器用于设置和控制UART的工作模式和功能。

常见的控制位包括发送使能(TXE)位、接收使能(RXE)位、奇偶校验使能(PAREN)位、奇偶校验选择(PSEL)位等。

通过设置和清除这些位的值,可以实现UART的各种功能配置。

5.时钟寄存器(CLK):时钟寄存器用于设置UART的时钟源和时钟分频系数,从而控制UART的时钟频率。

通过调整该寄存器的值,可以改变UART时钟的频率,以满足不同的通信需求。

6.中断使能寄存器(IER):中断使能寄存器用于设置UART的中断功能。

通过设置该寄存器的中断使能位,可以开启或关闭UART的中断功能。

常见的中断使能位包括接收中断使能(RXIE)位、发送中断使能(TXIE)位、错误中断使能(ERIE)位等。

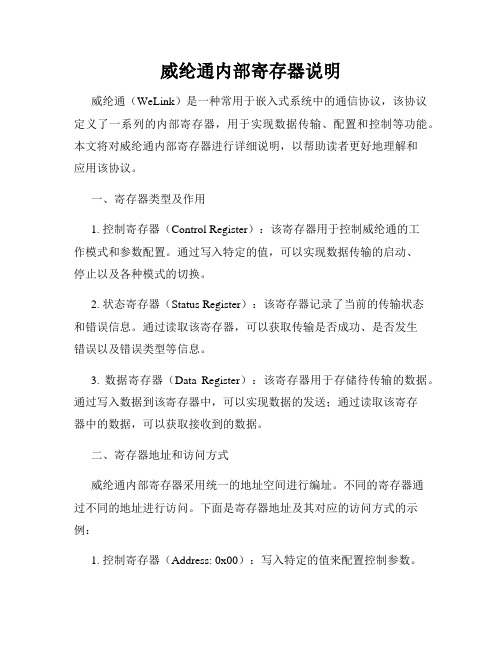

威纶通内部寄存器说明

威纶通内部寄存器说明威纶通(WeLink)是一种常用于嵌入式系统中的通信协议,该协议定义了一系列的内部寄存器,用于实现数据传输、配置和控制等功能。

本文将对威纶通内部寄存器进行详细说明,以帮助读者更好地理解和应用该协议。

一、寄存器类型及作用1. 控制寄存器(Control Register):该寄存器用于控制威纶通的工作模式和参数配置。

通过写入特定的值,可以实现数据传输的启动、停止以及各种模式的切换。

2. 状态寄存器(Status Register):该寄存器记录了当前的传输状态和错误信息。

通过读取该寄存器,可以获取传输是否成功、是否发生错误以及错误类型等信息。

3. 数据寄存器(Data Register):该寄存器用于存储待传输的数据。

通过写入数据到该寄存器中,可以实现数据的发送;通过读取该寄存器中的数据,可以获取接收到的数据。

二、寄存器地址和访问方式威纶通内部寄存器采用统一的地址空间进行编址。

不同的寄存器通过不同的地址进行访问。

下面是寄存器地址及其对应的访问方式的示例:1. 控制寄存器(Address: 0x00):写入特定的值来配置控制参数。

2. 状态寄存器(Address: 0x01):读取该寄存器来获取当前的传输状态和错误信息。

3. 数据寄存器(Address: 0x02):写入数据到该寄存器中进行发送;读取该寄存器中的数据来获取接收到的数据。

在使用威纶通协议时,通过访问相应的寄存器地址,可以实现对控制、状态和数据的读写操作,从而进行数据的传输和配置。

三、寄存器配置示例以下是一个基于威纶通协议的简单示例,用于演示如何通过寄存器配置实现数据传输:1. 设置传输模式:写入控制寄存器(Address: 0x00)的特定值,选择传输模式(如单向传输、双向传输等)。

2. 发送数据:将待发送的数据写入数据寄存器(Address: 0x02),通过特定的数据格式进行封装,以实现数据的发送。

3. 接收数据:读取数据寄存器(Address: 0x02)中的数据,通过解析特定的数据格式,获取接收到的数据。

串口控制寄存器SCON

串行口控制寄存器(SCON)SCON是 MCS-51 单片机的一个可位寻址的专用寄存器,用于串行数据通信的控制。

单元地点为 98H,位地点为98H~ 9FH。

寄存器的内容及位地点表示以下:位9FH 9EH 9DH 9CH 9BH 9AH 99H 98H地址位符SM0 SM1 SM2 REN TB8 RB8TI RI号各位的说明以下:1)SM0 、 SM1——串行口工作方式选择位其状态组合和对应工作方式为:SM0 SM1工作方式00方式001方式110方式211方式32)SM2——同意方式2、 3 的多机通信控制位在方式 2 和 3 中,若 SM2= 1 且接收到的第九位数据(RB8)为 1,才将接收到的前8位数据送入接收SBUF中,并置位RI 产生中止恳求;不然抛弃前8 位数据。

若SM2=0,则无论第九位数据(RB8)为 1 仍是为 0, 都将前8 位送入接收SBUF中,并产生中止恳求。

方式 0 时, SM2一定置 0。

3)REN——同意接收位REN= 0严禁接收数据REN= 1同意接收数据4)TB8 ——发送数据位8在方式 2、 3 时, TB8 的内容是要发送的第9 位数据,其值由用户经过软件来设置。

5)RB8——接收数据位8在方式 2、 3 时, RB8是接收的第 9 位数据。

在方式 1 时, RB8 是接收的停止位在方式 0 时,不使用RB86)TI ——发送中止标记位在方式 0 时,发送完第8 位数据后,该位由硬件置位在其余方式下,于发送停止位以后,由硬件置位。

所以, TI = 1 表示帧发送结束,其状态既可供软件查问使用,也可恳求中止。

TI 由软件清“0”。

7)RI ——接收中止标记位在方式 0 时,接收完第8 位数据后,该位由硬件置位。

在其余方式下,于接收到停止位之时,该位由硬件置位。

所以, RI = 1 表示帧接收结束,其状态既可供软件查问使用,也可恳求中止。

RI 由软件清“0”。

SPI寄存器配置说明

保留

1基于RXFFIVL匹配的RXFIFO中断将被使能

4-0

TXFFIL4-0

接收FIFO中断级别位

当FIFO状态位和FIFO级别位匹配时,接收FIFO将产生中断

SP1FFCTSP1 FIFO控制寄存器704CH

15-87-0

Reserved

FFTSDLY7--0

R-0R/W-0

位

名称

功能描述

15--8

SLAVE

SPI网络模式控制

1—从动模式

2—主动模式

1

TALK

主动/从动发送模式

0

SPI INT

ENA

SPI中断使能位

SP1ST状态寄存器7042H

7654-0

RECEIVER

OVERRUN

FLAG

SPI INT FLAG

TX BUF FULL FLAG

Reserved

R/C-0R/C-0R/C-0R-0

……

……

7

RXFF INT Flag

1RXFIFO未产生中断

2RXFIFO产生中断

6

RXFF INT CLR

写1清除RXFF INT中断位

5

RXFFI ENA

0基于TXFFIVL匹配的TXFIFO中断将被禁止

1基于TXFFIVL匹配的TXFIFO中断将被使能

4-0

TXFFIL4-0

发送FIFO中断级别位

00000接收FIFO是空

00001接收FIFO是1个字节

00010接收FIFO是2个字节

00011接收FIFO是3个字节

……

……

7

RXFF INT Flag

0 RXFIFO未产生中断

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

工作方式小结:

1.计数条件:0234置完数就可计数,15GATE 有一个上升沿才开始计数

2.连续性,23连续计数,0145单次计数

3.GATE电平影响:GATE=0时,0234停止计数, 15继续计数,不受影响,GATE恢复为1时, 0继续计数,12345重新计数

4.OUT波形:245计满后输出一个负脉冲,01 计数过程中为低电平,计满为高电平,3前半 周期为高电平,后半周期为低电平

3. 方式2 —— 周期性负脉冲输出 (比率发生器,计满后,连续计数)

计 数 期 间 , OUT 为 高 电 平 , 当 计 数 至 1 时 , OUT输出一个负脉冲,计满后继续计数

D0

D1

数

D2

据

D3

线

D4 D5

D6

D7

RD

控 WR

制 线

A1 A0

CS

电

源

VCC

线 GND

8 7

9

CLK0 计

数

6 5

11

GATE0 器

4

10

OUT0

0

3

2 1

15

CLK1 计

14

GATE1

数 器

22

13

OUT1

1

23

20

19

18

CLK2 计

21

16

GATE2

数 器

24 12

17

OUT2

2

图8-3 82图537的-3 引8脚25信3P号IT管脚图

(3)控制寄存器

接收从CPU来的控制字,并由控制字的D7、D6位的 编码决定该控制字写入哪个计数器的控制寄存器,控制 寄存器只能写入,不能读出。

(4)计数器

当8253用作计数器时,加在CLK引脚上脉冲的间隔 可以是不相等的;当它用作定时器时,则在CLK引脚应 输入精确的时钟脉冲,8253所能实现的定时时间,取决 于计数脉冲的频率和计数器的初值,即:定时时间=时 钟脉冲周期Tc×预置的计数初值n。

8253具有较好的通用性和使用灵活性,几乎适合于 任何一种微处理器组成的系统。

2. 8253的内部结构

8253的内部结构如图7.1所示,由数据总线缓冲器、 控制寄存器、读/写控制逻辑和计数器等部分组成。

图7.1 8253的内部结构示意图

7.2.2 8253的引脚信号

8253 是一片具 有3个独立 通道的16 位计数器/ 定时器芯 片,使用 单一+5V 电源,24 引脚双列 直插式封 装,如图 7.3所示

图7.6(a) 方式2 正常计数

CW = 14 LSB = 3 WR

CLK GATE

OUT 32 23 2 13

计数期间,若GAbT.E方为式低2 电GAT平E信,号停的止作用计数,若 GATE恢复高电平,重新开始计数

图7.6(b) 方式2时GATE信号的作用

计数值改变不影响正在进行的计数过程 改变的计数值是下次有效的

图7.7(b) 方式3 计数值为奇数时的波形

CW = 16 LSB = 4 WR

CLK GATE

OUT

4 3 2 1 4 4 4321

c. 方式3 GATE信号的作用

GATE信号使计数过程重新开始。若OUT为低期间, GATE=0,OUT将立即变高,停止计数。当GATE=1后 ,计数重新开始。

图7.7(c) 方式3 GATE信号的作用

计数期间,重新计数,下一次按新数计数 计数期间,若GATE为低电平,停止计数, 若GATE恢复高电平,重新开始计数 用途:作为脉冲速率发生器或用于产生实时 时钟中断

CW = 14 LSB = 3 WR

CLK GATE

OUT

321 321 3

a. 方式2 正常计数

•当写入CW控制字后,OUT输出为高。 •在写入计数值后,立即计数。 •计数器减到1时,输出变低,经过一个CLK周期,输 出恢复为高,计数器重新计数。输出固定频率的脉冲

4. 方式3 —— 方波发生器 (周期性方波输出)

方式3的工作过程同方式2,只是输出的脉宽不同

• 置完数,GATE为高电平时就开始计数,计数中, 前一半OUT为高电平,后一半OUT为低电平

• 置的数为奇数时,前一半〉后一半一个时钟周期

• 计满后,连续计数

• GATE信号使计数过程重新开始。若OUT为低期 间 , GATE=0,OUT 将 立 即 变 高 , 停 止 计 数 。 当 GATE=1后,计数重新开始。

图7.7(a) 方式3 计数值为偶数时的波形

CW = 16 WR

LSB = 5

CLK GATE

OUT

5 4 3 2 1 5 4 3 21

b. 方式3 计数值为奇数时的波形

若计数为奇数,第一个CLK脉冲使计数值减1,其后,每一个 CLK脉冲使计数器减2,当计到0时,输出改变状态,重新装入 计数值,这以后的第一个CLK脉冲使计数器减3,以后每个 CLK脉冲,计数器仍减2,直到计数器再次到0,输出恢复为高

图7.6(c) 方式2时计数过程中改变计数值

❖ 例:若要使计数器2工作于方式2,按二进制 计数,计数值为02F0H,则初始化程序:

MOV OUT MOV OUT MOV OUT

AL,0B4H

;写入控制字

07H,AL

AL,0F0H

06H,AL ;写计数值低8位

AL,02H

06H,AL ;写计数值高8位

CW = 16 WR

LSB = 4

CLK GATE

OUT

4 3 2 1 43 2 14 3

•写入CW后,输出a为. 方高式,3 计置数值数为后偶数 自时动的计波形数,计数到一半时, 输出变为低,直到计数为0,输出又变为高,重新开始计数

•若计数为偶数,每一个CLK脉冲使计数值减2,当计到0时, 输出改变状态,重新装入计数值开始新的计数。

CW = 16 WR

LSB = 5

LSB = 4

CLK GATE

OUT

543 21 4 3 d. 方式3 计数过程中改变计数值

计数期间写入一个新值,新值在现行半周期结束时装 入计数器。

对8253来讲,外部输入到CLK引脚上的时钟脉冲频 率不能大于2MHZ,否则需分频后才能送到CLK端。

7.2 Intel 8253可编程定时器/计数器

7.2.1 8253的基本功能和内部结构

1. 8253 的基本功能

(1)3个独立的16位计数器,最大计数范围为0~65535;

(2)每个计数器均可以按二进制或二—十进制计数; (3)计数器速率可达2MHz; (4)可编程6种不同的工作方式; (5)所有输入和输出都与TTL兼容。