集成电路第1章全解

集成电路分析与设计

第一章集成电路的发展1.何谓集成电路(Integrated Circuits)?集成电路:指通过一系列特定的加工工艺, 将晶体管,二极管等有源器件和电阻,电容,电感等无源器件,按照一定的电路互连,”集成”在一块半导体晶片上,封装在一个外壳内,执行特定电路或系统功能的一种器件.2.什么是摩尔定律(Moore’s Law)?它对集成电路的发展有什么作用?集成度:大约每三年翻两番,特征尺寸:每六年缩小近一倍事实上,摩尔定律并不是一个物理定律,而是一种预言,一张时间表。

它鞭策半导体产业界不断进步,并努力去实现它。

从根本上讲,摩尔定律是一种产业自我激励的机制,它让人们无法抗拒,并努力追赶,谁跟不上,谁就可能被残酷地淘汰。

摩尔定律已成为一盏照亮全球半导体产业前进方向的明灯。

3.IC发展水平的指标是什么?随着IC工业的发展,这些指标如何变化?集成规模(Integration scale)和特征尺寸(Feature size) 单个芯片上已经可以制作含有几百万个晶体管的一个完整的数字系统或数模混合的电子系统,集成电路的特征尺寸也已发展到深亚微米水平,0.18μm工艺已经走向规模化生产.4.什么是IDM、Fabless和Foundry?理解他们之间的关系。

IDM:集成电路发展的前三十年中,设计、制造和封装都是集中在半导体生产厂家内进行的,称之为一体化制造(IDM,Integrated Device Manufacturer)的集成电路实现模式。

无生产线(Fabless)集成电路设计提供了条件,为微电子领域发展知识经济提供了条件。

Fabless:1.设计公司拥有设计人才和设计技术,但不拥有生产线2.芯片设计公司不拥有生产线而存在和发展,而芯片制造单位致力于工艺实现(代客户加工,简称代工)3.设计单位与代工单位以信息流和物流的渠道建立联系Foundry:Foundry(代客户加工)第二章PN结的形成1.P型、N型半导体的形成及其能带结构图(EF与掺杂的关系)在纯净的硅晶体中掺入三价元素(如硼),使之取代晶格中硅原子的位置,此时自由电子和空穴浓度远远小于由于掺杂带来的空穴浓度,因此自由电子的导电基本可以忽略,这样的半导体叫做P型半导体。

超大规模集成电路CAD 第一章 VLSI设计的概述教材

差))

1952 年,英国皇家雷达研究所的达默第一次提出“集成电 路”的设想; 1958年美国德克萨斯仪器公司基尔比为首的小组研制出世 界上第一块集成电路了双极性晶体管(由12个器件组成的 相移振荡和触发器集成电路),并于1959年公布—这就是 世界上最早的集成电路,是现代集成电路的雏形或先驱 ; (基尔比于2000年获得诺贝尔物理学奖) 1960年成功制造出MOS管集成电路; 1965年戈登· 摩尔发表预测未来集成电路发展趋势的文章, 就是“摩尔定律”的前身; 1968年Intel公司诞生。

2019/4/12 4

第1章 VLSI概述

集成电路的发展除了物理原理外还得益于许多新工艺的 发明:

50年美国人奥尔和肖克莱发明的离子注入工艺; 56年美国人富勒发明的扩散工艺; 60年卢尔和克里斯坦森发明的外延生长工艺; 60年kang和Atalla研制出第一个硅MOS管; 70年斯皮勒和卡斯特兰尼发明的光刻工艺,使晶体管从点接触 结构向平面结构过渡并给集成电路工艺提供了基本的技术支持。 因此,从70年代开始,第一代集成电路才开始发展并迅速成熟。

图1 – 1 “点接晶体管放大器” 2019/4/12 3

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

第1章 VLSI概述

1948年,威廉· 肖克莱(William Shockley)—“晶体管之 父” ,提出结型晶体管的想法; 1951年,威廉· 肖克莱领导的研究小组成功研制出第一个可 靠的单晶锗NPN结型晶体管;(温度特性差、提纯度差、表面防护能力差(稳定性

路 漫 漫 其 修 远 兮 吾 将 上 下 而 求 索

第1章集成电路设计导论

1、微电子(集成电路)技术概述 2、集成电路设计步骤及方法

1

集成电路设计步骤

➢ “自底向上”(Bottom-up)

“自底向上”的设计路线,即自工艺开始,先进行单元设 计,在精心设计好各单元后逐步向上进行功能块、子系统 设计直至最终完成整个系统设计。在模拟IC和较简单的数 字IC设计中,大多仍采用“自底向上”的设计方法 。

5

半定制方法

半定制的设计方法分为: 门阵列(GA:Gate Array)法; 门海(GS:Sea of Gates)法; 标准单元(SC: Standard Cell)法; 积木块(BB:Building Block Layout); 可编程逻辑器件(PLD:Programmable Logic Device)设计法。

标准单元法也存在不足:பைடு நூலகம்

(1) 原始投资大:单元库的开发需要投入大量的人力物力;当工艺变化时, 单元的修改工作需要付出相当大的代价,因而如何建立一个在比较长的时 间内能适应技术发展的单元库是一个突出问题。 (2) 成本较高:由于掩膜版需要全部定制,芯片的加工也要经过全过程,因 而成本较高。只有芯片产量达到某一定额(几万至十几万),其成本才可接受。

不满足 后仿真

满足

VLS流I数片、字封I装C、的测设试 计流图

功能要求

系统建模 (Matlab等)

不满足 电路仿真

满足 手工设计

版图 不满足

后仿真 满足

模流拟片、IC封的装、设测计试 流图

3

集成电路设计方法

➢ 全定制方法(Full-Custom Design Approach) ➢ 半定制方法(Semi-Custom Design Approach)

集成电路制造工艺

集成电路制造工艺第1章绪论1.1 课题背景在过去的的几十年里,一个以计算机、互联网、无线通信和全球定位系统为组成部分的信息社会逐渐形成。

这个信息社会的核心部分是由众多内建于系统中的细小集成电路(IC)芯片支持和构成的。

集成电路广泛应用于生活中的各个领域—诸如消费类产品、家庭用品、汽车、信息技术、电信、媒体、军事和空间应用。

结合纳米技术,持续不断的研究和开发即将使得集成电路更小和更强有力。

在可见的未来,计算机的尺寸将缩小到指甲盖大小,达到集成电路在尺寸、速度、价格及功耗方面实际可能的极限。

1.2 集成电路制造工艺发展概况随着硅平面工艺技术的不断完善和发展,到1958年,诞生了第一块集成电路,也就是小规模集成电路(SSL);到了20世纪60年代中期,出现了中规模集成电路(MSL);20世纪70年代前期,出现了大规模集成电路(LSL);20世纪70年代后期又出现了超大规模集成电路(VLSL);到了20世纪90年代就出现了特大规模集成电路(ULSL)。

集成电路的制造工艺流程十分复杂,而且不同的种类、不同的功能、不同的结构的集成电路,其制造工艺的流程也不一样。

人们常常以最小线宽(特征尺寸)、硅晶圆片的直径和动态随机存取存储器(DRAM)的容量,来评价集成电路制造工艺的发展水平。

在表1-1中列出了从1995年到2010年集成电路的发展情况和展望。

表1-1 集成电路的发展情况和展望年代1995 1998 2001 2004 2007 2010 特征尺寸/um 0.35 0.25 0.18 0.13 0.09 0.065DRAM容量/bit 64M 256M 1G 4G 16G 64G微处理器尺寸/mm²250 300 360 430 520 620DRAM尺寸/mm²190 280 420 640 960 1400 逻辑电路晶体管密度(晶体管数)/个4M 7M 13M 25M 50M 90M 高速缓冲器/(bit/cm²)2M 6M 20M 50M 100M 300M最大硅晶圆片直径/mm 200 200 300 300 400 400第2章半导体集成电路制造工艺流程2.1 概括本章以大量精美的图片、图表及具体详实的数据详细描述了集成电路制造的全过程。

《基于Tanner的集成电路版图设计技术》课件第一章 集成电路设计前沿技术

1.2集成电路设计行业概况

1.2.3 我国集成电路设计行业发展情况

我国集成电路设计行业的起步较晚,但是发展速度很快,过去10年 的年复合增长率达到了29%。2004~2014年中国集成电路设计企业销售额 及增速,如图1.2所示。

1.2集成电路设计行业概况

1.2.1 集成电路设计行业概况

集成电路设计行业是集成电路行业的子行业,集成电路行业包括集 成电路设计业、集成电路制造业、集成电路封装业、集成电路测试业、 集成电路加工设备制造业、集成电路材料业等子行业。集成电路设计行 业处于产业链的上游,主要根据终端市场的需求设计开发各类芯片产品, 兼具技术密集型和资金密集型等特征,对企业的研发水平、技术积累、 研发投入、资金实力及产业链整合运作能力等均有较高的要求。

1.2集成电路设计行业概况

1.2.3 我国集成电路设计行业发展情况

2015年排名 1 2 3 4 5 6 7 8 9 10

厂商 Qualcomm OSR Avago/Broadcom

MTK Nvidia AMD Hisilicon(海思) Apple/TSMC Marvell Xilinx Spreadtrum(紫光展讯) 合计

1.2集成电路设计行业概况

1.2.2 集成电路设计行业的市场分类

集成电路按照应用领域大致分为标准通用集成电路和专用集成电路。 其中标准集成电路是指应用领域比较广泛、标准型的通用电路,如存储 器(DRAM)、微处理器(MPU)及微控制器(MCU)等;专用集成电 路是指某一领域会某一专门用途而设计的电路,系统集成电路(SoC) 属于专用集成电路。

集成电路芯片封装技术第1章

(50~90)%

封装效率

封装效率

=2-7%(1970-) =10-30%(1980-)

封装效率

=20-80%(1990-)

封装效率

=50-90%(1993-)

封装效率的改进

35

表2.封装厚度的变化

封装形式

封装厚度

(mm)

PQFP/PDIP TQFP/TSOP UTQFP/UTSOP

解决途径:

1、降低芯片功耗:双极型-PMOS-CMOS-???

2、增加材料的热导率:成本

微电子技术发展对封装的要求

三、集成度提高 适应大芯片要求

热膨胀系数(CTE)失配—热应力和热变形

解决途径:

1、采用低应力贴片材料:使大尺寸IC采用CTE接近

Si的陶瓷材料,但目前环氧树脂封装仍为主流

2、采用应力低传递模压树脂 消除封装过程中的热应

目的

使各种元器件、功能部件相组合形成功能电路

难易程度

依据电路结构、性能要求、封装类型而异

需考虑的问题

ห้องสมุดไป่ตู้保护

苛刻的工程条件(温度、湿度、振动、冲击、放射性等)

超高要求

超高性能 (3D IC)

超薄型、超小型

超多端子连接

超高功率(采用热冷、金属陶瓷复合基板等)

电子封装实现的四种功能

① 信号分配:

② 电源分配:

何将聚集的热量散出的问

题

封装保护

芯片封装可为芯片和其他连

接部件提供牢固可靠的机械

支撑,并能适应各种工作环

境和条件的变化

确定封装要求的影响因素

成本

电路在最佳

性能指标下

的最低价格

外形与结构

数字集成电路--电路、系统与设计(第二版)复习资料

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

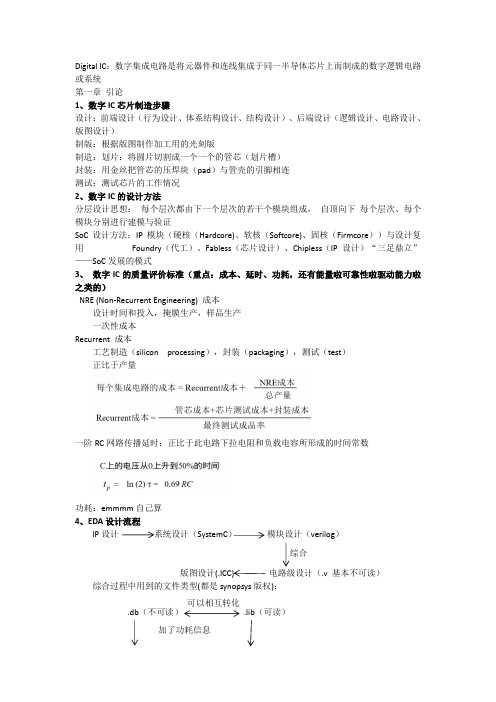

数字集成电路知识点整理

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm自己算4、EDA设计流程IP设计系统设计(SystemC)模块设计(verilog)综合版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys版权):可以相互转化.db(不可读).lib(可读)加了功耗信息.sdb .slib第二章器件基础1、保护IC的输入器件以抗静电荷(ESD保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

《集成电路制造工艺与工程应用》第一章课件

d) 功耗和散热成为限制芯片性能的瓶颈, 限制了NMOS工艺技术在超大规模集成电路的应用。(集成

度不断提高,每颗芯片可能含有上万门器件) 。

VDD

(a)NMOS反相器 (b)NMOS或非门 (c)NMOS与非门

VDD

VDD

输入

输出

A

B

VSS (a)

VSS

VSS

(b)

A 输出

B

输出

VSS

(c)

6

多晶硅栅工艺技术

NMOS和PMOS阈值电压的调节问题。

15

《集成电路制造工艺与工程应用》讲义 2018/09/28

栅极金属硅化物和漏端轻掺杂结构工艺技术

随着MOS器件的特征尺寸缩小到亚微米阶段: 1. 多晶硅栅的缺点: 电阻率高,严重影响了MOS器件的高频特性。(厚度3KÅ的多晶硅的方块电阻高达

36ohm/sq。 ) 2. 金属硅化物(polycide):

输出 PNP

p+

n+

Rp

n+

p+

p+

Rn P-sub

(a)

n+ NW Rp

输出 NPN

VSS (b)

输入

输出

Hale Waihona Puke VSS8SOS CMOS集成电路和硅CMOS集成电路

蓝宝石(Silicon-on-Sapphire SOS)是通过 外延生长技术把硅生长在蓝宝石上,SOS CMOS工艺集成电路被应用在人造卫星和导 弹等军事电子领域。

3. 20世纪60年代之前集成电路基本是双极型工艺集成电路,20世纪70年代NMOS和CMOS工艺集成电路 开始在逻辑运算领域逐步取代双极型工艺集成电路的统治地位。

集成电子学(第一、二章)

恒定电压等比例缩小规律(CV律)

– 保持电源电压Vds 和阈值电压Vth 不变,对其它 参数进行等比例缩小 – 按CV律缩小后对电路性能的提高远不如CE律, 而且采用CV律会使沟道内的电场大大增强 – CV律一般只适用于沟道长度大于1m的器件, 它不适用于沟道长度较短的器件。

准恒定电场等比例缩小规则(QCE律)

2 2 3 2

C V (恒 压 )律 1 / 1

2

Q C E (准 恒 场 )律 1 / / / / 1 /

2

1 1 / 1 /

3 2

1 / /

2 3 3 3 2

1 / 1 /

2 2

/ 1 /

2

2

四、微电子技术的发展方向

集成电子学

电子科技大学微固学院

课程介绍

教师:陈勇 83206779 yongchen@

计算机学院一楼东112

赵建民 83202193 jmzhao@

教材:《纳米CMOS器件》 甘学温 黄如 刘晓彦 张兴 编著 2004年 科学出版社出版 《超大规模集成物理学导论》童勤义编著 1989年 电子工业出版社

• 附图就是摩尔文章中所 给出的预测图形,据此, 摩尔明确预测, 1975年时集成电路上 的元件数将达到65 000。 果不其然,1975年64K RAM芯片问世,而所谓 64K的精确值正是65536, 即216。这使摩尔预言名 噪一时,并从此把它称 为摩尔定律。

Moore定律

描述 性能价格比

• 集成电路的集成度 • 在过去的20年中,改进 每三年增长四倍, 了1,000,000倍 • 特征尺寸每三年缩 • 在今后的20年中,还将 小 2 倍 改进1,000,000倍 • 很可能还将持续 10年

西南民族大学集成电路第1章集成运放的基础知识

差模电压增益: 共模电压增益: 总输出电压:

uo = uod uoc Aud uid Auc uic

1 u ic = (u i1 u i2 ) u i1 u i2 2 uod Aud = uid uoc Auc = uic

第1章 集成运放的基础知识

u i1 Rc

+VCC Rc

uo1

T1

uo2

T2 Re ui2

_

VCC

Auc 0

体现对共模信号的 抑止作用

共模半等效电路 b Ib + rbe

第1章 集成运放的基础知识

+VCC Rc

集成电路

第1章 集成运放的基础知识

期末总评成绩

期末考试成绩 70% 平时成绩 30%

集成电路原理及应用

1 集成运放的基础知识 2 模拟集成电路的线性应用 3 模拟集成电路的非线性应用 4 集成变换器及其应用 5 集成信号发生器 6 集成有源滤波器

第1章 集成运放的基础知识

第1章 集成运放的基础知识

第1章 集成运放的基础知识 1.1 集成运放的基本组成电路 1.2 集成运放的基本构成和表示符号 1.3 集成运放的主要参数和分类 1.4 集成运放的等效模型 1.5 实际运放与理想运放的误差 1.6 运放电路的稳定性及其判断 1.7 集成运放的相位补偿技术

第1章 集成运放的基础知识

1.1 集成运放的基本组成电路

差模输出电阻

RbR

u i1

Rc

b

Rc

uo12RL uo2

T1 Re T2

Rb

ui2

Rb

Rod 2 Rc

_

VCC

集成电路原理及应用第一章

2. 克服交越失真的互补推挽输出电路

VT4、R1、R2组成固定恒压偏置电路(称VBE 扩大电路),为VT2、VT3基极提供固定偏压, 克服了交越失真。

图1-1-19 克服交越失真的互补推挽输出电路

3. 具有过载保护的互补推挽输出电路

ห้องสมุดไป่ตู้

由Re2、Re3、 VD1、VD2 组成限流型

目前,集成运放还在向低漂移、低功耗、高速度、高输入阻抗、高放大倍数和高输出功率等高指标 的方向发展。

§1.1 集成运放的基本组成电路

1.1.1 差动输入电路 1.1.2 恒流源电路 1.1.3 有源负载电路 1.1.4 双端变单端电路 1.1.5 直流电平位移电路 1.1.6 互补推挽输出电路

1.1.1 差动输入电路

集成运放的发展从技术性能角度,大致可分为几个阶段: ⑴上世纪60年代初出现原始型 “单片集成”运放μA702。 ⑵1965年出现了第一代集成运放,如μA709。 ⑶1966年出现了第二代集成运放,如μA741。 ⑷1972年出现了第三代集成运放,如AD508。 ⑸1973年出现了第四代集成运放,如HA2900。

返回

3.集成运放的输入级

集成运放的许多性能指标主要取决于差动输入级。输入级的改进便成为各代集成运放的重要标 志。

(1)普通差动放大电路

普通差放电路作为集成运放的输入级时,其优点是电路结构简单,容易匹配,因此输 入失调电压小。它广泛用于早期产品和第一代集成运放中。

如国产的F001(5G922)、F004(5G23)以及国外的A709等。

缺点: 输入阻抗低,约为50k到300k; 失调电流,约为100nA; 最大差模输入电压低,不超过7V; 差模输入电压范围也较小,常为10V; 电压增益不高,约为30到100倍。

3篇1章习题解答浙大版集成电路课后答案

第一章 放大电路的动态和频响分析题 对于放大电路的性能指标,回答下列问题:(1) 已知某放大电路第一级的电压增益为40dB ,第二级的电压增益为20dB ,总的电压增益为多少dB(2) 某放大电路在负载开路时输出电压为4V ,接入3 k Ω的负载电阻后输出电压降为3V ,则该放大电路的输出电阻为多少(3) 为了测量某CE 放大电路的输出电压,是否可以用万用表的电阻档直接去测输出端对地的电阻解:(1) 60 dB ;(2) 1 k Ω;(3) 不可以。

题 一学生用交流电压表测得某放大电路的开路输出电压为,接上24 k Ω的负载电阻后测出的电压值为4V 。

已知电压表的内阻为120 k Ω。

求该放大电路的输出电阻R o 和实际的开路输出电压V oo 。

】解:由题意列方程组: 420208.4120120=+⋅=+⋅o DD o BB R V R V解得:V 5k 5=Ω=OO o V R ,题 在图题所示CS 放大电路中,已知静态工作点为V GSQ =,I DQ =2mA ,V DSQ =5V ,R s =3kΩ。

设电压放大倍数为vA =-20,发生截止失真时输出电压的正向幅值为5V ,发生饱和失真时输出电压的负向幅值为3V 。

(1) 当输入信号为v i =ωt (V)时,画出g 、d 点的电压波形v G 、v D ,并标出峰、谷电压的大小;(2) 当输入信号为v i =ωt (V)时,画出g 、d 点的电压波形v G 、v D ,并标出峰、谷电压的大小。

图题解:(1) 当v i =ωt (V)时,栅极的静态电压为:V 5.5325.0=⨯+-=+=s DQ GSQ GQ R I V V栅极的瞬态电压为:(V)t 0.1sin 5.5ω+=+=i GQ G v V v|漏极的瞬态电压为:(V) sin 211sin 1.0)20(325t t v A R I V v V v V v iv s DQ DSQ o DQ d DQ D ω-=ω⨯-+⨯+=++=+=+=因此,v G 、v D 电压波形如图(a )所示。

微电子与集成电路设计导论 第一章 概论

图1.5.4 国内集成电路的供求关系

图1.5.5 集成电路的进口量

➢ 我国的微电子技术的发展大致可以分为两个阶段:

第一个阶段:在2000年之前,1956年,北京大学、复旦大学、东北人民 大学、厦门大学、南京大学在北大联合创建半导体专业。1977年在北京 大学诞生了第一块大规模集成电路。而在1980年以后,初步形成了制造 业、设计业、封装业分离的状态。

➢ 膜集成电路:是在玻璃或陶瓷片等绝缘物体上,以膜的形式制作电阻、电 容等无源器件,并加以封装而成。

➢ 混合集成电路:在实际应用中,多半是在无源膜电路上外加半导体集成电 路或分立元件的二极管、三极管等有源器件,使之构成一个整体,这便是 混合集成电路。

图1.4.1 集成电路的分类

1.5 微电子产业的发展现状

ห้องสมุดไป่ตู้

3. 对信息社会的作用

图1.2.3 信息社会各应用产品市场领域的销售额

4. 对传统产业的带动作用

微电子对传统产业的渗透与带动作用。几乎所有的传统产业与微电子技术结 合,用集成电路芯片进行智能改造,都可以使传统产业重新焕发青春。

对风机、水泵采用变频调速等电子技术进行改造,每年即可节电500亿度以上. 和机械学科的结合,导致很多传统的机械产品逐步电子化。 和生物学结合,生物芯片的诞生得以实现对细胞、蛋白质、DNA以及其他生

图1.3.8 摩尔定律示意图

➢ 早期研制和生产的集成电路都是双极型的。 1930年,德国科学家Lilien-filed提出了关于MOS场效应晶体管的概念、工作原理 以及具体的实施方案。 1960年Kang和Atalla研制出第一个利用硅半导体材料制成的MOS晶体管。 1962年以后出现了由金属-氧化物-半导体(MOS)场效应晶体管组成的MOS集成 电路。

(完整版)1-1集成电路版图设计概述

二、按集成度分类

集成度:每块集成电路芯片中包含的元器件数目

类别

数字集成电路

模拟集成电路

MOS IC

双极IC

SSI

<102

<100

<30

MSI

102103

100500

30100

LSI

103105

5002000

100300

VLSI

105107

>2000

>300

ULSI

107109

GSI

❖ 专用集成电路 根据某种电子设备中特定的技术要求而专门设计的集成 电路简称ASIC,其特点是集成度较高功能较多,功耗较 小,封装形式多样。玩具狗芯片; 通信卫星芯片;计算 机工作站CPU中存储器与微处理器间的接口芯片

第一章 集成电路设计概述

1.3 无生产线集成电路设计技术 Fabless IC Design Technique

IDM与Fabless集成电路实现

• 集成电路发展的前三十年中,设计、制造和封装都 是集中在半导体生产厂家内进行的,称之为一体化 制造 (IDM,Integrated Device Manufacture)的集 成电路实现模式。

• 近十年以来,电路设计、工艺制造和封装开始分立 运行,这为发展无生产线(Fabless)集成电路设计 提供了条件,为微电子领域发展知识经济提供了条 件。

第一章 集成电路设计概述

1.1 集成电路(IC)的发展

芯片,现代社会的基石

内存条

PDA:掌上电脑

手机

数码相机

主板

计算机

集成电路

Integrated Circuit ,缩写IC IC是通过一系列特定的加工工艺,将晶体管 、二极管等有源器件和电阻、电容、电感等无源 器件,按照一定的电路互连,“集成”在一块半 导体晶片(如硅或砷化镓)上,封装在一个外壳 内,执行特定电路或系统功能的一种器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

其设计步骤与“自底向上”步骤相反。设计者首先进行行

为

设计;其次进行结构设计;接着把各子单元转换成逻辑图

或电路图;最后将电路图转换成版图。

15

功能要求

行为设计 (Verilog/VHDL)

不满足 行为仿真

满足 综合、优化

网表 不满足

时序仿真 满足

版图自动 布局、布线

不满足 后仿真

满足

流片、封装、测试

集成电路设计技术与工具

1

主要内容

集成电路简介 集成电路材料与器件物理基础 集成电路制造工艺 集成电路版图设计与工具 集成电路元器件及其SPICE模型 集成电路仿真软件SPICE 模拟集成电路晶体管级设计 数字集成电路晶体管级设计 集成电路模块级设计 集成电路系统级设计简介 集成电路封装 集成电路测试

表1 CMOS工艺特征尺寸发展进程

在新技术的推动下,集成电路自发明以来四十年,集成电路芯片

的集成度每三年翻两番 ,而加工特征尺寸缩小 2 倍。 这就是由Intel公司创始人之一Gordon E. Moore博士1965年总

结的规律,被称为摩尔定律。

8

1.2 集成电路的分类

器件结构类型 集成度 使用的基片材料 电路的功能 应用领域

14

1.3 集成电路设计步骤

❖ “自底向上”(Bottom-up)

“自底向上”的设计路线,即自工艺开始,先进行单元设

计,在精心设计好各单元后逐步向上进行功能块、子系统 设计直至最终完成整个系统设计。在模拟IC和较简单的数 字IC设计中,大多仍采用“自底向上”的设计方法 。

❖ “自顶向下”(Top-down)

4

集成电路芯片显微照片

集成电路芯片键合

5

各种封装好的集成电路

6

1.1 集成电路的发展

集成电路的历程:

1947-1948年: 世界上第一只晶体三极管面世 1950年: 成功研制出结型晶体管 1952年: 英国皇家雷达研究所第一次提出“集成电路”

的设想 1958年: 在美国德州仪器公司工作的Jacky Killby制造

按晶体管数目划分的集成电路规模

11

按使用的基片材料分类

• 单片集成电路:

它是指电路中所有的元器件都制作在同一块半 导体基片上的集成电路 在半导体集成电路中最常用的半导体材料是硅, 除此之外还有GaAs等

• 混合集成电路:

厚膜集成电路 薄膜集成电路

12

按电路的功能分类

➢ 数字集成电路(Digital IC): 它是指处理数字信号的集成电路,即采用二进制方式进 行数字计算和逻辑函数运算的一类集成电路。

10

按集成度分类

集成度:每块集成电路芯片中包含的元器件数目

类别

SSI MSI LSI VLSI ULSI GSI

数字集成电路

MOS IC 双极IC

<102

<100

102103 100500

103105 5002000

105107 >2000

107109

>109

模拟集成电路

<30 30100 100300 >300

17

一、全定制方法

全定制IC:硅片没有经过加工 ,其各掩模层都要 Байду номын сангаас特定电路的要求进行专门设计

适用于要求得到最高速度、最低功耗和最省面积 的芯片设计

版图设计时采用人工设计,对每个器件进行优化, 芯片性能获得最佳,芯片尺寸最小

设计周期长,设计成本高,适用于性能要求极高 或批量很大的产品,模拟电路

出世界上第一块集成电路—双极型晶体管集成 电路 1960年: 世界上成功制造出第一块MOS集成电路

7

1.1 集成电路的发展

年份 1989年 特征尺寸 1.0µm 水平标志 微米(M)

1993年

0.6µm

亚微米 (SM)

1997年

0.35µm

深亚微米 (DSM)

2001年

0.18µm

超深亚微米 (VDSM)

VLSI数字IC的设计流图

功能要求

系统建模 (Matlab等)

不满足 电路仿真

满足 手工设计

版图 不满足

后仿真 满足

流片、封装、测试

模拟IC的设计流图

16

1.4 集成电路设计方法

➢ 全 定 制 方 法 ( Full-Custom Design Approach)

➢ 半 定 制 方 法 ( Semi-Custom Design Approach)

2

集成电路设计与九天EDA工具应用 第1章 集成电路设计导论

1.1 集成电路的发展 1.2 集成电路的分类 1.3 集成电路设计步骤 1.4 集成电路设计方法 1.5 电子设计自动化技术概论

3

集成电路

Integrated Circuit ,缩写IC 通过一系列特定的加工工艺,将晶体管、二 极管等有源器件和电阻、电容、电感等无源 器件,按照一定的电路互连,“集成”在一 块 半导体晶片(如硅或砷化镓)上,封装在一 个外壳内,执行特定电路或系统功能的一种 器件。

9

按器件结构类型分类

双极集成电路:主要由双极晶体管构成

NPN型双极集成电路 PNP型双极集成电路

金属-氧化物-半导体(MOS)集成电路:主要由MOS 晶体管(单极晶体管)构成

NMOS PMOS

CMOS(互补MOS)

双 极 -MOS(BiMOS) 集 成 电 路 : 同 时 包 括 双 极 和 MOS晶体管的集成电路为BiMOS集成电路,综合 了双极和MOS器件两者的优点,但制作工艺复杂

➢ 模拟集成电路(Analog IC): 它是指处理模拟信号(连续变化的信号)的集成电路,通 常又可分为线性集成电路和非线性集成电路 : 线性集成电路:又叫做放大集成电路,如运算放大器、 电压比较器、跟随器等。 非线性集成电路:如振荡器、定时器等电路。

➢ 数模混合集成电路(Digital - Analog IC) : 例如数模(D/A)转换器和模数(A/D)转换器等。

13

按应用领域分类

❖ 标准通用集成电路: 通用集成电路是指不同厂家都在同时生产的用量极大的 标准系列产品。这类产品往往集成度不高,然而社会需 求量大,通用性强。

❖ 专用集成电路: 根据某种电子设备中特定的技术要求而专门设计的集成 电路简称ASIC,其特点是集成度较高功能较多,功耗较 小,封装形式多样。

18

二、半定制方法

半定制的设计方法分为门阵列(GA:Gate Array)法和门海(GS:Sea of Gates); 标准单元(SC: Standard Cell)法;积木 块(BB:Building Block Layout);可编 程逻辑器件(PLD:Programmable Logic Device)设计法。