版图设计实验报告剖析

两级运算放大器的版图设计(版图设计实验报告)

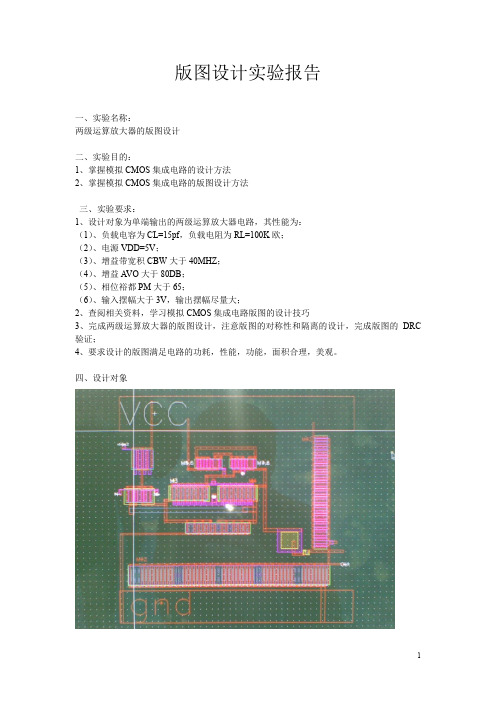

版图设计实验报告一、实验名称:两级运算放大器的版图设计二、实验目的:1、掌握模拟CMOS集成电路的设计方法2、掌握模拟CMOS集成电路的版图设计方法三、实验要求:1、设计对象为单端输出的两级运算放大器电路,其性能为:(1)、负载电容为CL=15pf,负载电阻为RL=100K欧;(2)、电源VDD=5V;(3)、增益带宽积CBW大于40MHZ;(4)、增益AVO大于80DB;(5)、相位裕都PM大于65;(6)、输入摆幅大于3V,输出摆幅尽量大;2、查阅相关资料,学习模拟CMOS集成电路版图的设计技巧3、完成两级运算放大器的版图设计,注意版图的对称性和隔离的设计,完成版图的DRC 验证;4、要求设计的版图满足电路的功耗,性能,功能,面积合理,美观。

四、设计对象仿真后MOS管的宽长比如下图:备注:电阻:R1为180欧电容:C1为2.62pf五、实验步骤1、观察模型文件(.SCS文件)或通过对CMOS管点单电路的DC分析并查看MOS管的直流工作点参数,得到PMOS,NMOS的基工艺参数(TOX,Cox,VthN,VthP等)2、确定具体的设计方案3、在schematic中画出电路图4、开始设计电路的版图5、修改版图,使之通过DRC验证6、优化版图使面积合理、美观六、实验结果面积:120*180=22680(um)七、实验心得第二次做版图设计,相较上次的实习难度提升了些许,最关键的是即将步入工作的我们重拾了那些被淡化和遗忘的知识,重新刷新脑子,和团队紧密合作,细致的分工,相互的监督和检验,我们一步步的完成脑中的想法,在有限的时间内完成老师的作业,这让我们感觉就是在工作间里。

然而每一步的前进总是让我们明白我们的不足和问题,知识的模糊,对版图设计的有限了解,粗糙的设计,迟钝的软件操作,这些都让我们反思了很久也想了很多,无论如何,经过了再一次的版图设计,我还是能够感到自己的进步,无论是对知识的理解还是对学习知识的渴求,而后者让我感到格外珍贵。

本科生课-集成电路版图设计-实验报告

西安邮电大学集成电路版图设计实验报告学号:XXX姓名:XX班级:微电子XX日期:20XX目录实验一、反相器电路的版图验证1)反相器电路2)反相器电路前仿真3)反相器电路版图说明4)反相器电路版图DRC验证5)反相器电路版图LVS验证6)反相器电路版图提取寄生参数7)反相器电路版图后仿真8)小结实验二、电阻负载共源放大器版图验证9)电阻负载共源放大器电路10)电阻负载共源放大器电路前仿真11)电阻负载共源放大器电路版图说明12)电阻负载共源放大器电路版图DRC验证13)电阻负载共源放大器电路版图LVS验证14)电阻负载共源放大器电路版图提取寄生参数15)电阻负载共源放大器电路版图后仿真16)小结实验一、反相器电路的版图验证1、反相器电路反相器电路由一个PMOS、NPOS管,输入输出端、地、电源端和SUB 端构成,其中VDD接PMOS管源端和衬底,地接NMOS管的漏端,输入端接两MOS管栅极,输出端接两MOS管漏端,SUB端单独引出,搭建好的反相器电路如图1所示。

图1 反相器原理图2、反相器电路前仿真通过工具栏的Design-Create Cellview-From Cellview将反相器电路转化为symbol,和schemetic保存在相同的cell中。

然后重新创建一个cell,插入之前创建好的反相器symbol,插入电感、电容、信号源、地等搭建一个前仿真电路,此处最好在输入输出网络上打上text,以便显示波形时方便观察,如图2所示。

图2 前仿真电路图反相器的输入端设置为方波信号,设置合适的高低电平、脉冲周期、上升时间、下降时间,将频率设置为参数变量F,选择瞬态分析,设置变量值为100KHZ,仿真时间为20u,然后进行仿真,如果仿真结果很密集而不清晰可以右键框选图形放大,如图3所示。

图3 前仿真结果3、反相器电路版图说明打开之前搭建好的反相器电路,通过Tools-Design Synthesis-Laout XL新建一个同cell目录下的Laout文件,在原理图上选中两个MOS管后在Laout中选择Create-Pick From Schematic从原理图中调入两个器件的版图模型。

(实习报告)集成电路版图设计的实习报告

(实习报告)集成电路版图设计的实习报告关于在深圳菲特数码技术有限公司成都分公司从事集成电路版图设计的实习报告一、实习单位及岗位简介(一)实习单位的简介深圳菲特数码技术有限公司成立于2005年1月,总部位于深圳高新技术产业园。

深圳市菲特数码技术有限公司成都分公司于2007年10月在成都设立研发中心,位于青羊工业集中发展区B区12栋2楼。

菲特数码技术有限公司员工总人数已超过50人,其中本科以上学历占90%。

菲特公司拥有一支集嵌入式系统、软件技术、集成电路设计于一体的综合研发团队,其核心人员均是来自各个领域的资深专家,拥有多年成功研发经验,已在手持多媒体,车载音响系统,视频监控等多个领域有所斩获。

菲特公司以自有芯片技术为核心原动力,开展自我创新能力,并于2006年申请两项技术专利,且获得国家对自主创新型中小企业扶持的专项资金。

主要项目电波钟芯片设计及方案开发;视频专用芯片设计及监控摄像头方案开发、监控DVR方案开发;车载音响系统方案开发;网络电视、网络电话方案开发。

(二)实习岗位的简介集成电路版图设计是连接设计与制造工厂的桥梁,主要从事芯片物理结构分析、版图编辑、逻辑分析、版图物理验证、联系代工厂、版图自动布局布线、建立后端设计流程等。

版图设计人员必须懂得集成电路设计与制造的流程、原理及相关知识,更要掌握芯片的物理结构分析、版图编辑、逻辑分析、版图物理验证等专业技能。

集成电路版图设计的职业定义为:通过EDA设计工具,进行集成电路后端的版图设计和验证,最终产生送交供集成电路制造用的GDSII数据。

通常由模拟电路设计者进行对模拟电路的设计,生成电路及网表文件,交由版图设计者进行绘制。

版图设计者在绘制过程中需要与模拟电路设计者进行大量的交流及讨论,这关系到电路最终的实现及最终芯片的性能。

这些讨论涉及到电流的走向,大小;需要匹配器件的摆放;模块的摆放与信号流的走向的关系;电路中MOS 管、电阻、电容对精度的要求;易受干扰的电压传输线、高频信号传输线的走线问题。

比较器的版图设计实验报告

实验报告:比较器的版图设计与实现1. 实验目的1.1 了解Schematic设计环境;1.2 掌握比较器电路原理图输入方法;1.3 掌握比较器电路的版图绘制方法;1.4 掌握版图DRC、LVS验证及仿真方法。

2. 实验内容:1)、比较器的电路及仿真:○1局部电路图:完整电路图○2激励信号(以表格的形式给出)Function DCvoltage/V Voltage1/VVoltage2/VPeriod/SPulsewidth/SVdd dc 1.8 \ \ \ \ gnd dc 0 \ \ \ \ INP sin \ 0.9 -0.9 1000n \ INN sin \ 0.9 -0.9 600n \ P1D pulse 1.8 0 \ 400n 200n ○3电路图的仿真结果。

2)、比较器的版图及仿真:○1版图(写出版图的面积)局部版图版图面积大约为:10*10=100 um2 完整版图版图面积大约为:25*35=875 um2 ○2版图的后仿提取网表○3激励信号(以表格的形式给出)Function DCvoltage/V Voltage1/VVoltage2/VPeriod/SPulsewidth/SVdd dc 1.8 \ \ \ \ gnd dc 0 \ \ \ \ INP sin \ 0.9 -0.9 1000n \ INN sin \ 0.9 -0.9 600n \ P1D pulse 1.8 0 \ 400n 200n○4版图的仿真结果。

3、收获与感悟:通过这次比较器的实验,我不仅能够熟练地使用软件进行layout,还能考虑电路的面积、器件的匹配等因素进行版图的绘制。

这次实验中,我这设计比较器时,考虑了P1、P2、P3、P4以及N5、N6的匹配问题,用了指装交叉的设计思路,大大缩小了版图的面积,并且减小了一些寄生参数的影响,使电路的性能得到了优化。

这次实验完成后,我在做整个比较器设计的时候,我再次对前两次设计的原件进行了一些修改,主要是优化了面积,改善了输入输出端的位置,使我能在布局比较器的时候更方便。

IC版图设计实训报告

集成电路版图设计一、实验目的1.熟悉cadence的基本操作2.学会搭建电路3.学会根据版图设计规则设计版图4.学会根据DRC,LVS检查并改正错误5.掌握版图设计的一些常用技巧二、实验内容①布局:安排各个晶体管、基本单元、复杂单元在芯片上的位置。

②布线:设计走线,实现管间、门间、单元间的互连。

③尺寸确定:确定晶体管尺寸(W、L)、互连尺寸(连线宽度)以及晶体管与互连之间的相对尺寸等。

④版图编辑(Layout Editor ):规定各个工艺层上图形的形状、尺寸和位⑤布局布线(Place and route ):给出版图的整体规划和各图形间的连接。

⑥版图检查(Layout Check ):设计规则检验(DRC,Design Rule Check)、电气规则检查(ERC,Electrical Rule Check)、版图与电路图一致性检验(LVS,Layout Versus Schematic )。

版图设计规则如下:三、实验要求版图(layout)是集成电路从设计走向制造的桥梁,它包含了集成电路尺寸、各层拓扑定义等器件相关的物理信息数据。

版图设计是创建工程制图(网表)的精确的物理描述过程,即定义各工艺层图形的形状、尺寸以及不同工艺层的相对位置的过程。

其设计目标有以下三方面:(1)满足电路功能、性能指标、质量要求;(2)尽可能节省面积,以提高集成度,降低成本;(3)尽可能缩短连线,以减少复杂度,缩短延时,改善可能性。

四、实验步骤(1)Linux中打开cadence注意要在lab 文件夹下打开(2)新建设计库并连接工艺库(3)新建电路图并搭建此次设计两个电路的版图BUF1 和AO121(4)新建版图(layout)文件,根据电路图布局布线画好版图BUF1版图AO121版图(5)DRC设计规则检查(6)LVS版图电路图一致性检查四、实验总结通过三天的版图培训学习,对IC版图设计有了更深的认识和了解,以下这三天的实验总结:1.Linux基本操作:基本指令:1.打开目录:cd 目录2.列出文件:ls3.复制文件:cp文件一文件二4.打开cadence : Icfb &5.移动文件:mv文件一文件一目录2. 版图绘制:(1)准备工作:option—display—最小精度选0.05;按F3—选择—orthogonal上下左右平行移动(2) PMOS版图绘制:a、有源区T0绘制:选中图层T0,按R,点击图层起点,松开鼠标拖动图层到终点,按K标尺选择图层上下宽度为4.2um。

版图实验报告(完美版)

图 1-9 带隙基准源的电路原理图 10、完成电路图后按 X 键检查和保存,无错误后退出;

第4页

11、回到 ic6151 界面,依次选择 File->Export->CDL,弹出 CDL Out 界面,个参数如图 1-10 所பைடு நூலகம்;

第8页

实验二: 带隙基准源电路的版图设计

一、实验目的: 1、熟悉 Linux 系统基本命令并学会使用同时熟练画 layout 的一些快捷方式; 2、掌握半导体集成电路的设计规则; 3、掌握半导体集成电路的布局布线; 4、掌握使用 Cadence Virtuoso 版图编辑软件进行模拟 IC 版图布局设计; 5、掌握如何根据电路图提取网表,从而进行 LVS 检查验证; 6、学会使用 cadence 工具对所画版图进行 DRC 验证,确保版图符合工艺设计规则; 7、学会如何看 DRC 和 LVS,以便对错误进行修改。 二、实验原理和内容: 1、设计规则: (1)同层金属之间的距离是 0.6us (2)不同电位的阱间距是 4us (3)在对差分对和电流镜的匹配时,用的共质心的原则 (4)对于电流镜和差分对这类敏感模块要用 guardring (5)对于电阻要加 dummy 2、原理:Virtuoso Layout Editor 是一种基于 LINUX 系统的 EDA 工具,用于集成电路版图 设计。该工具可以进行 DRC 和 LVS 检查验证,DRC(设计规则检查)即查看所画版图是否符 合工艺设计规则,只有通过 DRC 检查,版图才能在现有工艺条件下实现;LVS(版图和电路 图一致性比较)即查看版图是否和电路图一致,只有通过 LVS 检查,版图才能在电学特性和 电路所要实现的功能上和原电路保持完全一致。本实验利用 Cadence 画出电路原理图,然 后进行检查与验证; 3、内容:首先根据已经知道的电路原理图分析其那些器件需要匹配,将匹配的器件画在一 起,分成若干个版图模块。带隙基准源大致分为:电流镜模块,分压电阻模块,差分对模块 以及剩下的单个电阻; 4、需要用到的快捷键: F2 保存 C 键 复制 F 键 满屏 M 键 移动工具 Shift+M 合并工具 K 键 标尺工具 L 键 标签工具

(实习报告)集成电路版图设计的实习报告

(实习报告)集成电路版图设计的实习报告关于在深圳菲特数码技术有限公司成都分公司从事集成电路版图设计的实习报告一、实习单位及岗位简介(一)实习单位的简介深圳菲特数码技术有限公司成立于2005年1月,总部位于深圳高新技术产业园。

深圳市菲特数码技术有限公司成都分公司于2007年10月在成都设立研发中心,位于青羊工业集中发展区B区12栋2楼。

菲特数码技术有限公司员工总人数已超过50人,其中本科以上学历占90%。

菲特公司拥有一支集嵌入式系统、软件技术、集成电路设计于一体的综合研发团队,其核心人员均是来自各个领域的资深专家,拥有多年成功研发经验,已在手持多媒体,车载音响系统,视频监控等多个领域有所斩获。

菲特公司以自有芯片技术为核心原动力,开展自我创新能力,并于2006年申请两项技术专利,且获得国家对自主创新型中小企业扶持的专项资金。

主要项目电波钟芯片设计及方案开发;视频专用芯片设计及监控摄像头方案开发、监控DVR方案开发;车载音响系统方案开发;网络电视、网络电话方案开发。

(二)实习岗位的简介集成电路版图设计是连接设计与制造工厂的桥梁,主要从事芯片物理结构分析、版图编辑、逻辑分析、版图物理验证、联系代工厂、版图自动布局布线、建立后端设计流程等。

版图设计人员必须懂得集成电路设计与制造的流程、原理及相关知识,更要掌握芯片的物理结构分析、版图编辑、逻辑分析、版图物理验证等专业技能。

集成电路版图设计的职业定义为:通过EDA设计工具,进行集成电路后端的版图设计和验证,最终产生送交供集成电路制造用的GDSII数据。

通常由模拟电路设计者进行对模拟电路的设计,生成电路及网表文件,交由版图设计者进行绘制。

版图设计者在绘制过程中需要与模拟电路设计者进行大量的交流及讨论,这关系到电路最终的实现及最终芯片的性能。

这些讨论涉及到电流的走向,大小;需要匹配器件的摆放;模块的摆放与信号流的走向的关系;电路中MOS 管、电阻、电容对精度的要求;易受干扰的电压传输线、高频信号传输线的走线问题。

LDMOS版图设计实验_第三次实验报告

半导体功率器件与智能功率IC实验学生姓名:田瑞学号:201422030143指导教师:乔明一、实验室名称:211楼803 工作站二、实验项目名称:半导体功率器件与智能功率IC实验——LDMOS器件版图设计实验三、实验原理:首先,设计版图的基础便是电路的基本原理,以及电路的工作特性,硅加工工艺的基础、以及通用版图的设计流程,之后要根据不同的工艺对应不同的设计规则,一般来说通用的版图设计流程为:1.制定版图规划记住要制定可能会被遗忘的特殊要求清单2.设计实现考虑特殊要求及如何布线创建组元并对其进行布3.版图验证执行基于计算机的检查和目视检查,进行校正工作最终步骤工程核查以及版图核查版图参数提取与后仿真完成这些之后需要特别注意的是寄生参数噪声以及布局等的影响,具体是电路而定,在下面的实验步骤中会体现到这一点。

IC设计与制造的主要流程四、实验目的:掌握版图设计的基本理论。

掌握版图设计的常用技巧。

掌握定制集成电路的设计方法和流程。

熟悉Cadence Virtuoso Layout Edit软件的应用学会用Cadence软件设计版图、版图的验证以及后仿真熟悉Cadence软件和版图设计流程,减少版图设计过程中出现的错误。

五、实验内容:结合LDMOS的版图文件,完成LDMOS器件的版图绘制。

六、实验器材(设备、元器件):CADENCE软件七、实验步骤:LDMOS的版图文件nwell 16400 8000pwell1 10 7000pwell2 70 34003550 40504220 45204740 49905250 54705770 59206350 8000poly 20400 18005000 7400nimplant 20400 74007700 8000pimplant 10 7700omicont 20300 07000900 7600metal 20 20004800 8000nitride 20 06006300 8000八、实验数据及结果分析:整体版图版图下部分别为:源端pad,漏端pad以及栅极pad九、实验结论:通过实验,了解LDMOS器件的版图设计,熟悉CADENCE软件的使用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

版图设计实验报告课程名称:集成电路版图设计姓名:学号;专业;电子科学与技术教师;老师目录(一)实验目的 (3)(二)实验步骤 (4)1,搭建环境····································································································2,运用ic6151···························································································3,作图···········································································································4,Run DRC··························································································5,画原理图···························································································6,Run LVS········································································································(三)实验总结·················································································································(一)实验目的1、熟悉Linux系统基本命令并学会使用;2、掌握使用Cadence Virtuoso版图编辑软件进行模拟IC 版图布局设计;3、Cadence-Virtuoso Layout Editor是一种基于Linux系统的EDA工具;(1)熟练使用快捷键;R;画矩形, ESC;取消任务, delete;除去、U;撤销, shift + f;变繁体 k;测距离C;复制, s;改变形状 p;双沟道 L创建标识等等;(2) 画线和贴片;横----A2纵----A1M1-M24、学会用Cadence搭建网表即如何构建电路,并对电路图进行检查和验证;5、为了从电路图提取网表,用于后续layout的LVS检查验证做准备;6、学习对电路模块的认识。