超大规模集成电路第八次作业2016秋,段成华

段成华————第一次作业

第1题

解:20世纪60年代,英特尔公司的创始人摩尔预测集成电路中单位面积集成的晶体管数目大约每十八个月翻一番。

此后的三十多年,半导体工艺技术基本上按照摩尔定律的预测发展。

根据世界半导体行业共同制定的2005年国际半导体技术发展路线,2020年以前集成电路仍将按照摩尔定律持续高速发展。

根据世界半导体行业共同制定的2005年国际半导体技术发展路线图(ITRS)及其更新,2014年将采用22nm工艺,2017年将采用16nm工艺,2020年将采用11nm 工艺。

2013年高性能芯片上可集成的集体管数量突破8.8G,片上局部时钟频率达到22GHz;预计2020年将这些数据会分别突破超过35.3G和73GHz。

工艺的实现也存在很多制约的因素:晶体管特征尺寸达到nm量级,这使得物理设计的难度大大增加;微处理器芯片的功耗将超过封装功耗极限200W/mm2的5倍即1KW/mm2,功耗问题仍是一个不可规避的问题;而信号在一个时钟周期内传输的距离之相当于芯片尺寸的十分之一左右,导线延迟将会成为处理器主频提高的瓶颈;片内处理能力的进一步加强对封装能力提出了新的挑战,封装能力会成为系统性能提升的瓶颈。

在更遥远的未来,碳纳米管因其超常的能量及半导体性能而被认为是最有可能取代硅,成为未来信息革命的导火索。

第2题

解:表2-1所示。

表2-1 三极管数量和时钟频率

年代三极管数量时钟频率典型处理器(Inter) 70年代2300~60000.5MHz~2MHz 4004、8008、8080 80年代20000~134000 4MHz~20MHz 8086、8088、80286 00年代9500000~55000000 100MHz~1.6GHz Pentium II、III、4。

最新电大《高新技术基础》教学考一体化网考形考作业试题及答案

最新电大《高新技术基础》教学考一体化网考形考作业试题及答案100%通过2015年秋期河南电大把《高新技术基础》纳入到“教学考一体化”平台进行网考,针对这个平台,本人汇总了该科所有的题,形成一个完整的题库,内容包含了单选题、判断题,并且以后会不断更新,对考生的复习、作业和考试起着非常重要的作用,会给您节省大量的时间。

做考题时,利用本文档中的查找工具,把考题中的关键字输到查找工具的查找内容框内,就可迅速查找到该题答案。

本文库还有其他教学考一体化答案,敬请查看。

一单选题1.第二次技术革命是以()的应用为特征的技术革命。

A.电力2.高电子迁移率晶体管缩写是()。

D. HEMT3.现代通信技术是从20世纪()年代以来开始应用的。

A. 604.控制论的创始人是美国数学家()。

A.维纳5.第一次技术革命是以()为先导的。

B.纺织机6.信息处理技术的第一次飞跃是()的产生与使用。

D.文字7.双极型晶体管缩写是()。

D. HBT8.现代计算机系统结构被称为()结构。

B.冯.诺依曼9.算术逻辑运算单元的缩写是()。

D. ALU10.信息论的创始人是美国数学家()。

A.申农11.第一台电子数字计算机问世于()年。

C. 194612.第一次技术革命的代表是()。

D.蒸汽机13.运算器和控制器和在一起称为()。

C. CPU 14.微电子技术的核心是()。

B.集成电路技术15.()是所有高新技术的基础和核心。

A.信息技术16.计算机辅助设计的缩写是()。

B. CAD17.集成电路的缩写是()。

D. IC18.下列哪个不是按规模对计算机分类的类型()。

D.通用计算机19.集成电路封装技术中的四列扁平封装缩写是()。

B. QFP20.第一台电子数字计算机被命名为()。

A. ENIAC21.计算机网络使人们共享网络中的计算机硬件、软件和()等资源。

C.数据22. 1888年赫兹用气体火花放电实现了电磁波发射,意味着()的诞生。

B.电子学23.系统软件的核心是()。

超大规模集成电路秋段成华老师第三次作业精编版

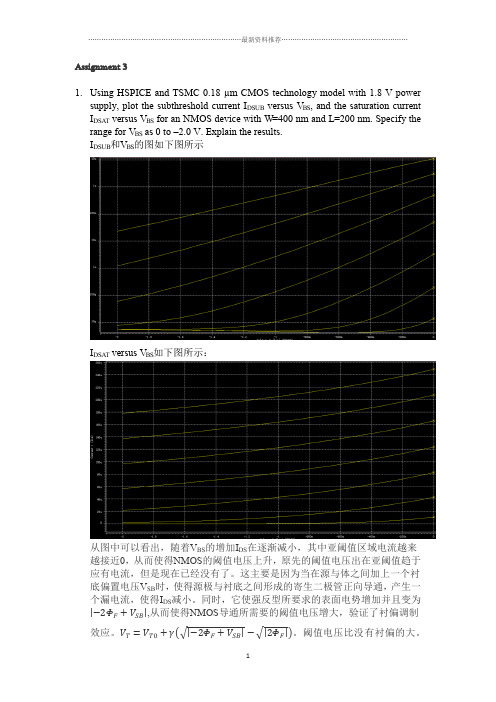

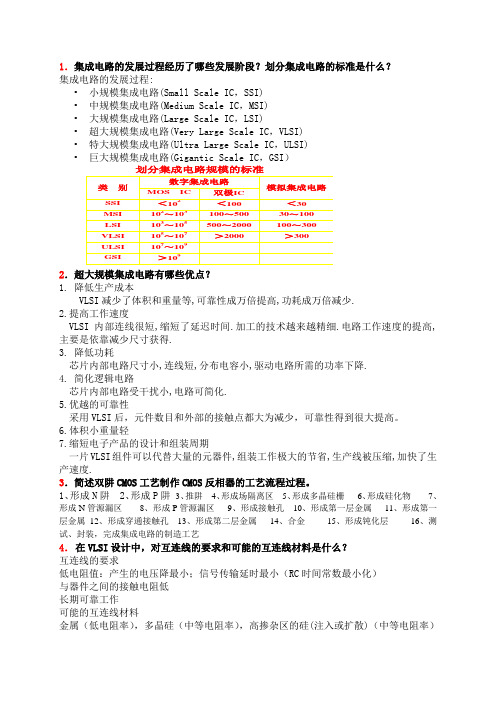

Assignment 3ing HSPICE and TSMC 0.18 µm CMOS technology model with 1.8 V powersupply, plot the subthreshold current I DSUB versus V BS, and the saturation currentI DSAT versus V BS for an NMOS device with W=400 nm and L=200 nm. Specify therange for V BS as 0 to –2.0 V. Explain the results.I DSUB和V BS的图如下图所示I DSAT versus V BS如下图所示:从图中可以看出,随着V BS的增加I DS在逐渐减小,其中亚阈值区域电流越来越接近0,从而使得NMOS的阈值电压上升,原先的阈值电压出在亚阈值趋于应有电流,但是现在已经没有了。

这主要是因为当在源与体之间加上一个衬底偏置电压V SB时,使得源极与衬底之间形成的寄生二极管正向导通,产生一个漏电流,使得I DS减小。

同时,它使强反型所要求的表面电势增加并且变为,从而使得NMOS导通所需要的阈值电压增大,验证了衬偏调制效应。

阈值电压比没有衬偏的大。

* SPICE INPUT FILE: problem.sp ID-VBS.param Supply=1.8 * Set value of Vdd.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT * Set 0.18um library .opt scale=0.1u * Set lambda*.model pch PMOS level=49 version=3.1*.model nch NMOS level=49 version=3.1mn Vdd gaten Gnd bn nch l=2 w=4 ad=20 pd=4 as=20 ps=4Vdd Vdd 0 'Supply'Vgsn gaten Gnd d cVbsn bn Gnd d c.dc Vbsn 0 -2 -0.05 Vgsn 0.6 1.8 0.2.print dc I1(mn).ending HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V powersupply, plot log I DS versus V GS while varying V DS for an NMOS device withL=200 nm, W=800 nm and a PMOS with L=200 nm, W= 2 µm. Explain theresults.图中红线表示NMOS的I DS对V GS的曲线,从图中可以看出,随着V GS的增大I DS 的电流先为0,到后来逐渐增大,最后I DS对V GS的关系接近一个线性变化,且NMOS的导通电压约为0.43V,当V GS=0.43V的时候NMOS导通。

《超大规模集成电路设计》考试习题(含答案)完整版分析

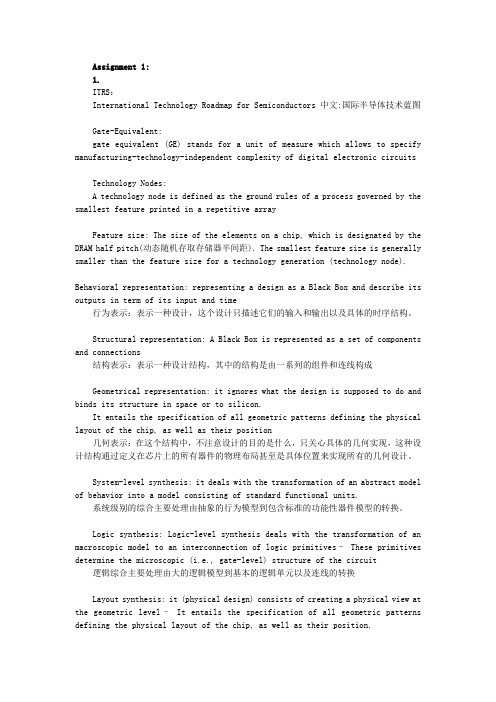

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么?集成电路的发展过程:•小规模集成电路(Small Scale IC,SSI)•中规模集成电路(Medium Scale IC,MSI)•大规模集成电路(Large Scale IC,LSI)•超大规模集成电路(Very Large Scale IC,VLSI)•特大规模集成电路(Ultra Large Scale IC,ULSI)•巨大规模集成电路(Gigantic Scale IC,GSI)划分集成电路规模的标准2.超大规模集成电路有哪些优点?1. 降低生产成本VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少.2.提高工作速度VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得.3. 降低功耗芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降.4. 简化逻辑电路芯片内部电路受干扰小,电路可简化.5.优越的可靠性采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。

6.体积小重量轻7.缩短电子产品的设计和组装周期一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度.3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。

1、形成N阱2、形成P阱3、推阱4、形成场隔离区5、形成多晶硅栅6、形成硅化物7、形成N管源漏区8、形成P管源漏区9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么?互连线的要求低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化)与器件之间的接触电阻低长期可靠工作可能的互连线材料金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)5.在进行版图设计时为什么要制定版图设计规则?—片集成电路上有成千上万个晶体管和电阻等元件以及大量的连线。

中科院数字集成系统设计(段成华)作业答案

Assignment 1:1.ITRS:International Technology Roadmap for Semiconductors 中文:国际半导体技术蓝图Gate-Equivalent:gate equivalent (GE) stands for a unit of measure which allows to specify manufacturing-technology-independent complexity of digital electronic circuitsTechnology Nodes:A technology node is defined as the ground rules of a process governed by the smallest feature printed in a repetitive arrayFeature size: The size of the elements on a chip, which is designated by the DRAM half pitch(动态随机存取存储器半间距). The smallest feature size is generally smaller than the feature size for a technology generation (technology node).Behavioral representation: representing a design as a Black Box and describe its outputs in term of its input and time行为表示:表示一种设计,这个设计只描述它们的输入和输出以及具体的时序结构。

Structural representation: A Black Box is represented as a set of components and connections结构表示:表示一种设计结构,其中的结构是由一系列的组件和连线构成Geometrical representation: it ignores what the design is supposed to do and binds its structure in space or to silicon.It entails the specification of all geometric patterns defining the physical layout of the chip, as well as their position几何表示:在这个结构中,不注意设计的目的是什么,只关心具体的几何实现,这种设计结构通过定义在芯片上的所有器件的物理布局甚至是具体位置来实现所有的几何设计。

中国科学院大学 段成华 VLSI 超大规模集成电路 期末复习笔记(1到10章)

MOS 管 耗尽区电荷以及宽度

阈值电压的定义,饱和区线性区等阶段的电流

阈值电压:强反型发生时

饱和区: 与 Vgs-Vt 平方成正比

线性区:

ID

n

(VGS

VT

)VDS

VDS 2

2

Vds 较小时忽略平方项,就是线性关系

沟调效应

增加 Vds 会使漏结的耗尽区变大,缩小了有效沟道长度。 影响为:Vds 会增大 ID

Vdd Vdd 0 'Supply' VgspVdd gatep dc='Supply' Vgsngaten Gnd dc='Supply'

.dc Vgsp0 'Supply' 'Supply/20' .dc Vgsn0 'Supply' 'Supply/20'

.print dc I1(mp) .print dc I1(mn)

* Set TSMC 0.18um library

*.model pch PMOS level=49 version = 3.1 *.model nch NMOS level=49 version = 3.1

.options list node post measout * Option List: Prints a list of netlist elements, node connections, and values for components, voltage and current sources, parameters, and more. * Option Node: Prints a node cross-reference table. * Option Post: Saves simulation results for viewing by an interactive waveform viewer. * Option Measout: Outputs .MEASURE statement values and sweep parameters into an ASCII file.

超大规模集成电路秋段成华老师第三次作业

超大规模集成电路2017年秋段成华老师第三次作业work Information Technology Company.2020YEARAssignment 3ing HSPICE and TSMC 0.18 µm CMOS technology model with 1.8 V powersupply, plot the subthreshold current I DSUB versus V BS, and the saturation currentI DSAT versus V BS for an NMOS device with W=400 nm and L=200 nm. Specify therange for V BS as 0 to –2.0 V. Explain the results.I DSUB和V BS的图如下图所示I DSAT versus V BS如下图所示:从图中可以看出,随着V BS的增加I DS在逐渐减小,其中亚阈值区域电流越来越接近0,从而使得NMOS的阈值电压上升,原先的阈值电压出在亚阈值趋于应有电流,但是现在已经没有了。

这主要是因为当在源与体之间加上一个衬底偏置电压V SB时,使得源极与衬底之间形成的寄生二极管正向导通,产生一个漏电流,使得I DS减小。

同时,它使强反型所要求的表面电势增加并且变为|−2ΦF+V SB|,从而使得NMOS导通所需要的阈值电压增大,验证了衬偏调制效应。

V T=V T0+γ(√|−2ΦF+V SB|−√|2ΦF|)。

阈值电压比没有衬偏的大。

* SPICE INPUT FILE: problem.sp ID-VBS.param Supply=1.8 * Set value of Vdd.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT * Set 0.18umlibrary.opt scale=0.1u * Set lambda*.model pch PMOS level=49 version=3.1*.model nch NMOS level=49 version=3.1mn Vdd gaten Gnd bn nch l=2 w=4 ad=20 pd=4 as=20 ps=4Vdd Vdd 0 'Supply'Vgsn gaten Gnd dcVbsn bn Gnd dc.dc Vbsn 0 -2 -0.05 Vgsn 0.6 1.8 0.2.print dc I1(mn).ending HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V powersupply, plot log I DS versus V GS while varying V DS for an NMOS device withL=200 nm, W=800 nm and a PMOS with L=200 nm, W= 2 µm. Explain the results.图中红线表示NMOS的I DS对V GS的曲线,从图中可以看出,随着V GS的增大I DS的电流先为0,到后来逐渐增大,最后I DS对V GS的关系接近一个线性变化,且NMOS的导通电压约为0.43V,当V GS=0.43V的时候NMOS导通。

超大规模集成电路第四次作业2016秋_段成华

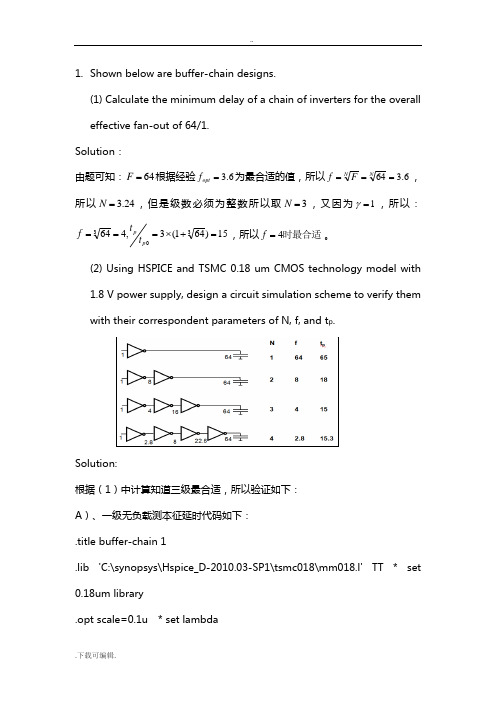

1. Shown below are buffer-chain designs.(1) Calculate the minimum delay of a chain of inverters for the overalleffective fan-out of 64/1.Solution :由题可知:64=F 根据经验6.3=opt f 为最合适的值,所以6.364===N N F f ,所以24.3=N ,但是级数必须为整数所以取3=N ,又因为1=γ,所以:15)641(3,464303=+⨯===p p t t f ,所以时最合适4=f 。

(2) Using HSPICE and TSMC 0.18 um CMOS technology model with1.8 V power supply, design a circuit simulation scheme to verify themwith their correspondent parameters of N, f, and t p .Solution:根据(1)中计算知道三级最合适,所以验证如下:A )、一级无负载测本征延时代码如下:.title buffer-chain 1.lib 'C:\synopsys\Hspice_D-2010.03-SP1\tsmc018\mm018.l' TT * set0.18um library.opt scale=0.1u * set lambda.options post=2 list.temp 27.global vddVdd vdd gnd 1.8vin vin 0 0.9 pulse 0 1.8 25n 5p 5p 49.99n 100n $频率为10MhzCl vout gnd 0f $Cg1=2.46fF,负载为CL=157.44fF.subckt inv in out wn=3.5 wp=10 t=7.5mn out in gnd gnd NCH l=2 w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mp out in vdd vdd PCH l=2 w=wp ad='wp*t' pd='wp+2*t' as='wp*t' ps='wp+2*t'.endsX1 vin vout inv wn=3.5 wp=10 t=7.5.op.tran 5p 5n.meas tran voutmax max v(vout) from=5p to=5n.meas tran voutmin min v(vout) from=5p to=5n$一级.meas tran tphl1+trig v(vin)+val=0.9+rise=1+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+fall=1.meas tran tplh1+trig v(vin)+val=0.9+fall=1+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+rise=1.end1)一级无负载测得本征延时约为17ps;2)带上64倍Cg1大小的负载测得延时为750.35ps,是本征延时的44倍B)、三级带负载测延时代码如下:.title buffer-chain 3.lib 'C:\synopsys\Hspice_D-2010.03-SP1\tsmc018\mm018.l' TT * set 0.18um library.opt scale=0.1u * set lambda.options post=2 list.temp 27.global vdd.param fan=4Vdd vdd gnd 1.8vin vin 0 0.9 pulse 0 1.8 25n 5p 5p 49.99n 100nCl vout gnd 0f $Cg1=2.46fF,负载为CL=157.44fF.subckt inv in out wn=3.5 wp=10 t=7.5mn out in gnd gnd NCH l=2 w=wn ad='wn*t' pd='wn+2*t' as='wn*t' ps='wn+2*t'mp out in vdd vdd PCH l=2 w=wp ad='wp*t' pd='wp+2*t' as='wp*t' ps='wp+2*t'.endsX1 vin 2 inv wn=3.5 wp=10 t=7.5X2 2 3 inv wn='fan*3.5' wp='fan*10' t=5X3 3 vout inv wn='fan*fan*3.5' wp='fan*fan*10' t=5.op.tran 50p 500n.meas tran voutmax max v(vout) from=50p to=500n.meas tran voutmin min v(vout) from=50p to=500n$三级.meas tran tphl3+trig v(vin)+val=0.9+rise=1+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+fall=1.meas tran tplh3+trig v(vin)+val=0.9+fall=1+targ v(vout)+val='0.5*(voutmax-voutmin)+voutmin'+rise=11)带上64倍Cg1大小的负载测得延时为174.6ps ,是本征延时的10.27倍总结如下:经过调整参数近似时每一级的1=γ,所以经过手工计算得到一级带负载和三级带负载的延时比值为:2344.065151300==p p t t tp tp ,而仿真得到的结果为2327.035.7506.174=,所以符合手工计算的比值,同理其他级的延时代码也是如上的写法,经过仿真得到三级延时最小。

中科院_段成华_专用集成电路设计_作业 3

UX:未知不定 U1:未知1 U0:未知0 为了定义决断函数如何工作用了几个简单规定: 1、最强的强度总是赢家 2、强度相同而值不同,返回强度同但值为X 先比较强度: F R Z F F R Z

1、在Design_Vision中可以看到设计原理图如下,和ench对其进行测试

3、通过观察仿真波形可以看出,如下图所示,当C=1时,Q的状态和D 输入的状态是始终同步的。当C=X时,Q=X,在t=10ns时,C=0,而Q依 然保持Q=X。

b、设立delta为1 ns ,比较两者之间的区别 ------------------------------------------delta延迟的门级设计--------------------------------library IEEE; use IEEE.STD_LOGIC_1164.ALL; entity dff1 is port( c,d:in std_logic; q:out std_logic); end dff1; -------------------------------- Assume all elements have 3ns delay-------------------------architecture Behavioral of dff1 is signal a,b,cn,qq:std_logic;

D 0 0 1 1 0 0 1 1

Q 0 1 0 1 0 1 0 1

q 0 1 0 1 0 0 1 1

布尔逻辑表达式:q =QC’D’+C’DQ+CDQ’+CDQ 卡诺图: Q CD 00 01 11 0 0 0 1 1 1 1 1 化简可得到布尔逻辑表达式:q =QC’ +CD

cbmjqaaa超大规模集成电路第八次作业秋-段成华

c b m j q A A A超大规模集成电路第八次作业2016秋-段成华Assignment 81. Access relevant reference books or technical data books and give accuratedefinitions for the following timing parameters:(1) design entity, (6) delta delay,(2) signal driver, (7) simulation time,(3)transaction,(8)simulation cycle,(4)event,(9)inertial time,(5)time queue,(10) transport time.(1)design entity: In VHDL a given logic circuit represented as a design entity. Adesign entity, in return , consists of two different types of description: the interface description and one or more architectural bodies. The interface description declares the entity and describes its inputs and outputs.(2)signal driver: If a process contains one or more signal assignmentstatement that schedule future values for some signal X, the VHDL simulator creates a single value holder called asignal driver .(3)transaction:A pair consisting of a value and time. The value part represents afuture value of the driver; the time part represents the time at which the value part becomes the current value of driver.(4)event: It’s a kind of signal property and presents signal jump. Such asif(clk'event and clk='1).(5)time queue: It’s used to keep some signal transactions in the simulator.Time queue entries are represented as a two-tuple of the form(SN,V), where SN is a signal name and V is the value the signal is scheduled to assume at the scheduled time. Each time queue entry is called a signal transaction.(6)delta delay: A period of time greater than 0, but less than any standardtime unit no number of delta delayadded together can cause simulation time toadvance.(7)simulation time: The elapsed time in standard time units during simulation.(8)simulation cycle: Every time simulation time advances, a simulation cycleoccurs, which we now define more formally. The execution of a model consists of an initialization phase followed by the repetitive execution of processesin the process network. Each repetition is said to be simulation cycle.(9)inertial time: Example: Z <= I after 10ns; The signal propagation willtake place if and only if input I persists at a given level for 10ns-the amount of time specified in the after clause.(10)transport time: Z <= transport I after 10ns; All changes on I willpropagate to Z, regardless of how long the value of I stays at the new level.2.Construct VHDL models for 74-139 dual 2-to-4-line decoders using threedescription types, ., behavioral, dataflow and structural descriptions.Synthesize andsimulate these models respectively in the environment of Xilinx ISE with the ModelSim simulator integrated. When simulating these models, testvector(s) are required to stimulate the units under test (UUT). Reasonable test vectors are designed and created by your own as sources added to your VHDLproject.Logic schematic of 74-139:Function table of one decoder of 74-139:INPUTSSELEC OUTPUTSENABLTEY Y Y YG B A0123H X X H H H HL L L L H H HL L H H L H HL H L H H L HL H H H H H L (1)、行为描述代码如下:-- Company:-- Engineer:-- Create Date:21:14:09 12/02/2016--D esign Name:--M odule Name: deceoder_beh - Behavioral--P roject Name:--T arget Devices:--T ool versions:--D escription:--D ependencies:--R evision:--R evision - File Created--A dditional Comments:library IEEE;----use the following library declaration if instantiating----any Xilinx primitives in this code.--library UNISIM;--use deceoder_beh isPort ( G1,G2 : in std_logic;A : in std_logic_vector(1 downto 0);end deceoder_beh;architecture Behavioral of deceoder_beh isbeginde1: process (A, G1)beginif G1 = '1' theny1 <= "1111"; -- sequential statement elsecase A iswhen "00"=>Y1 <= "1110";when "01"=>Y1 <= "1101";when "10"=>Y1 <= "1011";when "11"=>Y1 <= "0111";when others => Y1 <= "1111";end case;end if;end process;de2: process (B, G2)beginif G2 = '1' thenY2 <= "1111"; -- sequential statement elsecase B iswhen "00"=>Y2 <= "1110";when "01"=>Y2 <= "1101";when "10"=>Y2 <= "1011";when "11"=>Y2 <= "0111";when others => Y2 <= "1111";end case;end if;end process;end Behavioral;TestBench代码如下:--C ompany:--E ngineer:--C reate Date: 22:25:59 12/02/2016--D esign Name:--M odule Name: D:/decoder/--P roject Name: decoder--T arget Device:--T ool versions:--D escription:--V HDL Test Bench Created by ISE for module: deceoder_beh--D ependencies:--R evision:--R evision - File Created--A dditional Comments:--N otes:--T his testbench has been automatically generated using types std_logic and--s td_logic_vector for the ports of the unit under test. Xilinx recommends--t hat these types always be used for the top-level I/O of a design in order--t o guarantee that the testbench will bind correctly to the post-implementation --s imulation model.--C omponent Declaration for the Unit Under Test (UUT)COMPONENT deceoder_behPORT(G1 : IN std_logic;G2 : IN std_logic;A : IN std_logic_vector(1 downto 0);B : IN std_logic_vector(1 downto 0);Y1 : OUT std_logic_vector(3 downto 0);Y2 : OUT std_logic_vector(3 downto 0));END COMPONENT;--Inputssignal G1 : std_logic := '0';signal G2 : std_logic := '0';signal A : std_logic_vector(1 downto 0) := (others => '0');signal B : std_logic_vector(1 downto 0) := (others => '0'); --Outputssignal Y1 : std_logic_vector(3 downto 0);signal Y2 : std_logic_vector(3 downto 0);BEGIN--I nstantiate the Unit Under Test (UUT)uut: deceoder_beh PORT MAP (G1 => G1,G2 => G2,A=>A, B=>B,Y1 => Y1,Y2 => Y2);-- Stimulus processstim_proc: processbegin-- insert stimulus hereG1 <='1';WAIT FOR 100 ns;G1 <='0';A <= "00";B <= "00";-- --------------------------------------- -------------Current Time:200nsWAIT FOR 100 ns;G1 <='0';A <= "01";B <= "01";-- --------------------------------------- -------------Current Time:300nsWAIT FOR 100 ns;G1 <='0';A <= "10";B <= "10";-- --------------------------------------- -------------Current Time:400nsWAIT FOR 100 ns;G1 <='0';a <= "11";b <= "11";WAIT FOR 100 ns;end process;END;测试波形如下:可以看到当 G1=0 和 G2=0 可以正常的译码,当 G1=1 和 G2=1,则Y1 和 Y2 都输出”1111”。

《超大规模数字集成电路》试题B

《超大规模数字集成电路》试题B第 1 页共 2 页内蒙古科技大学2015/2016学年第二学期《超大规模数字集成电路》考试试题B课程号:671180800考试方式:闭卷使用专业、年级:电子信息工程、通信工程2013 任课教师:侯海鹏考试时间:2016年9月备注:一、选择题(共12题,每题2分,共24分)1.下面()不是硅材料在集成电路技术中起着举足轻重的作用的原因。

(A) 原材料来源丰富 (B) 技术成熟 (C) 价格低廉 (D) 硬度高2.下面()不是芯片电感的实现结构。

(A) 匝线圈 (B) 叉指金属结构 (C) 螺旋形多匝线圈 (D) 传输线结构3.P,Q,R 都是4bit 的输入矢量,下面()的表达形式是正确的。

(A)input [3:0]P,[3:0]Q,[0:3]R; (B) input P,Q,R[3:0]; (C) input P[3:0],Q[3:0],R[3:0]; (D) input [3:0] P,Q,R; 4.根据以下两条语句,下列选项中()是正确的。

reg [7:0] B; B=8'bZ0;(A) 8'0000_00Z0 (B) 8'bZZZZ_0000 (C) 8'b0000_ZZZ0 (D) 8'bZZZZ_ZZZ0 5.在Verilog HDL 中,下列语句中()不是分支语句。

(A) if-else (B) case(C) casez(D) repeat6.在下列标识符中,()是不合法的标识符。

(A) 9moon(B) State0(C) Not_Ack_0 (D) signall7.Verilog HDL 中并行块语句的关键字是()(A) module…endmoudle (B) begin …end (C) fork …join (D) if …else 8.已知“a =1b ’1; b=3b’100;”那么{a,b}=()(A)4b ’0100(B) 3b ’110(C) 4b ’1100(D) 3b ’1009.在下列表达式中,正确的是()。

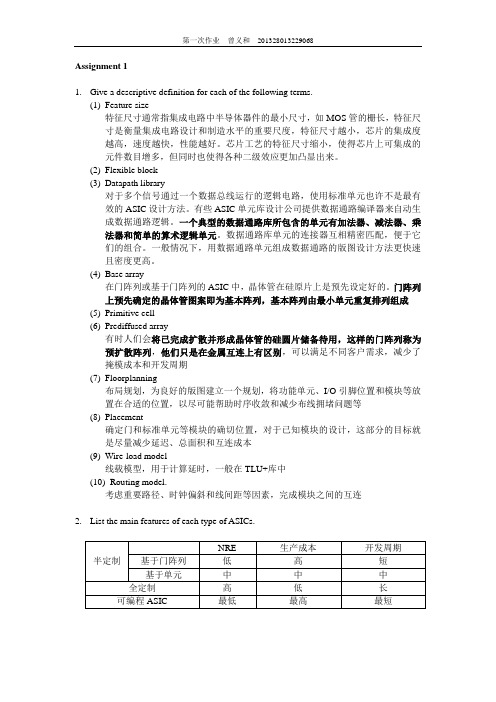

中科院_段成华_专用集成电路设计_作业 1

Assignment 11.Give a descriptive definition for each of the following terms.(1)Feature size特征尺寸通常指集成电路中半导体器件的最小尺寸,如MOS管的栅长,特征尺寸是衡量集成电路设计和制造水平的重要尺度,特征尺寸越小,芯片的集成度越高,速度越快,性能越好。

芯片工艺的特征尺寸缩小,使得芯片上可集成的元件数目增多,但同时也使得各种二级效应更加凸显出来。

(2)Flexible block(3)Datapath library对于多个信号通过一个数据总线运行的逻辑电路,使用标准单元也许不是最有效的ASIC设计方法。

有些ASIC单元库设计公司提供数据通路编译器来自动生成数据通路逻辑。

一个典型的数据通路库所包含的单元有加法器、减法器、乘法器和简单的算术逻辑单元。

数据通路库单元的连接器互相精密匹配,便于它们的组合。

一般情况下,用数据通路单元组成数据通路的版图设计方法更快速且密度更高。

(4)Base array在门阵列或基于门阵列的ASIC中,晶体管在硅原片上是预先设定好的。

门阵列上预先确定的晶体管图案即为基本阵列,基本阵列由最小单元重复排列组成(5)Primitive cell(6)Prediffused array有时人们会将已完成扩散并形成晶体管的硅圆片储备待用,这样的门阵列称为预扩散阵列,他们只是在金属互连上有区别,可以满足不同客户需求,减少了掩模成本和开发周期(7)Floorplanning布局规划,为良好的版图建立一个规划,将功能单元、I/O引脚位置和模块等放置在合适的位置,以尽可能帮助时序收敛和减少布线拥堵问题等(8)Placement确定门和标准单元等模块的确切位置,对于已知模块的设计,这部分的目标就是尽量减少延迟、总面积和互连成本(9)Wire-load model线载模型,用于计算延时,一般在TLU+库中(10)Routing model.考虑重要路径、时钟偏斜和线间距等因素,完成模块之间的互连2.List the main features of each type of ASICs.3.Write a summary of the paper “Silicon Design Chain C ooperation Enables NanometerChip Design” in Chinese (about 500 words).硅片设计链之间的合作使纳米芯片设计成为可能随着集成电路工艺水平的提升,越来越小的晶体管尺寸可以被设计出来,但同时由于短沟道效应等问题越来越明显,芯片的设计复杂度也越来越高,我们需要考虑的设计问题越来越多,同时更短的推向市场的应用需求也增加了SOC设计的难度。

超大规模集成电路2017年秋段成华老师第四次作业

超大规模集成电路2017年秋段成华老师第四次作业1.Shown below are buffer-chain designs.(1) Calculate the minimum delay of a chain of inverters for the overalleffective fan-out of 64/1.(2) Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 Vpower supply, design a circuit simulation scheme to verify them with their correspondent parameters of N, f, and t p.N=3.6 ∴N=3.246(1)γ=1 F=64∴f=√F所以最佳反相器数目约为3通过仿真可以得到tphl=1.3568E-11 tplh=1.7498E-11 tp0=1.5533E-11(2)N=1时,tphl= 5.2735E-10 tplh= 8.1605E-10 tpd= 6.7170E-10N=2时,tplh=2.2478E-10 tphl=2.5567E-10 tpd=2.4023E-10N=3时,tphl=2.0574E-10 tplh=2.1781E-10 tpd=2.1178E-10N=4时,tplh=2.1579E-10 tphl=2.2189E-10 tpd=2.1884E-10从仿真结果可以看出N=3或者N=4时延迟时间最优,且N=2、3、4得到的仿真延迟时间与理论推导的时间比较接近,比例基本上是18、15、15.3,而N=1时仿真得到的延迟时间远小于理论推导的时间,但是最优结果依旧是N=3,f=4,tp=15。

* SPICE INPUT FILE: Bsim3demo1.sp--a chain of inverters.param Supply=1.8.lib 'C:\synopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT.option captab.option list node post measout.tran 10p 6000p************************************************************.param tdval=10p.meas tran tplh trig v(in) val=0.9 td=tdval rise=2+targ v(out) val=0.9 rise=2.meas tran tphl trig v(in) val=0.9 td=tdval fall=2+targ v(out) val=0.9 fall=2.meas tpd param='(tphl+tplh)/2'*macro definitions**************************************************************pmos3*.subckt pmos3 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=6.4u ad=3.2p^2 pd=6.4u as=3.2p^2 ps=6.4u .ends pmos3*.subckt inv3 in outxmn out in Gnd nmos3xmp out in Vcc pmos3vcc Vcc Gnd Supply.ends inv3**nmos4*.subckt nmos4 n1 n2 n3mn n1 n2 n3 Gnd nch l=0.2u w=9.04u ad=4.52p^2 pd=9.04u as=4.52p^2 ps=9.04u .ends nmos4**pmos4*.subckt pmos4 p1 p2 p3mp p1 p2 p3 Vcc pch l=0.2u w=18.08u ad=9.04p^2 pd=18.08u as=9.04p^2 ps=18.08u.ends pmos4*.subckt inv4 in outxmn out in Gnd nmos4xmp out in Vcc pmos4vcc Vcc Gnd Supply.ends inv4*main circuit netlistxinv1 in out1 inv1xinv2 out1 out2 inv2xinv3 out2 out3 inv3xinv4 out3 out inv4cl out Gnd 154.24fVin in Gnd 0.9 pulse(0.0 1.8 219p 40p 40p 1100p 2400p).print tran v(in) v(out).end2.Consider the logic network below, which may represent the critical path of amore complex logic block. The output of the。

通信中的超大规模集成电路(VLSI)

通信中的超大规模集成电路(VLSI)

曹志刚

【期刊名称】《国际电子快讯》

【年(卷),期】1991(000)005

【总页数】3页(P6-8)

【作者】曹志刚

【作者单位】无

【正文语种】中文

【中图分类】TN47

【相关文献】

1.VLSI超大规模集成电路测试和验证的发展趋势 [J], 贾建革;段新安;李咏雪

2.超大规模集成电路(VLSI)制造技术 [J], 许晶华

3.神经元网络超大规模集成电路(VLSI)的实现 [J], 谭锡林

4.超大规模集成电路设计基础:第三讲 NMOS VLSI的结构特性 [J], 刘以皓;冯世琴

5.浅析超大规模集成电路(VLSI)的电路级设计 [J], 路庆东;梁蓓

因版权原因,仅展示原文概要,查看原文内容请购买。

超大规模集成电路2017年秋段成华老师第四次作业

超大规模集成电路2017年秋段成华老师第四次作业1.Shown below are buffer-chain designs.⑴ Calculate the minimum delay of a chain of inverters for the overalleffective fan-out of 64/1.(2) Using HSPICE and TSMC 0.18 um CMOS technology model with 1.8 V powersupply, design a circuit simulation schemeto verify them with theircorrespondent parameters of N, f, and p t64^18-----------------15.3⑴所以最佳反相器数目约为3通过仿真可以得到tphl=1.3568E-11 tplh=1.7498E-11 tpO=1.5533E-11(2)N=1 时,tphl= 5.2735E-10 tplh= 8.1605E-10 tpd= 6.7170E-10N=2时,tplh=2.2478E-10 tphl=2.5567E-10 tpd=2.4023E-10N=3时,tphl=2.0574E-10 tplh=2.1781E-10 tpd=2.1178E-10N=4时,tplh=2.1579E-10 tphl=2.2189E-10 tpd=2.1884E-10从仿真结果可以看出N=3或者N=4时延迟时间最优,且N=2 3、4得到的仿真延迟时间与理论推导的时间比较接近,比例基本上是18、15、15.3,而N=1时仿真得到的延迟时间远小于理论推导的时间,但是最优结果依旧是N=3,f=4,tp=15。

* SPICE INPUT FILE: Bsim3demo1.sp--a chain of inverters.param Supply=1.8.lib 'C:\sy nopsys\Hspice_A-2007.09\tsmc018\mm018.l' TT.optio n captab.optio n list node post measout.tran 10p 6000p************************************************************.param tdval=10p.meas tran tplh trig v(i n) val=0.9 td=tdval rise=2+targ v(out) val=0.9 rise=2.meas tran tphl trig v(i n) val=0.9 td=tdval fall=2+targ v(out) val=0.9 fall=2.meas tpd param='(tphl+tplh)/2'*macro defi niti ons*nmosl*•subckt nmosl nl n2 n3mn nl n2 n3 Gnd nch 1=0.2u w=0. 4u ad=0. 2p"2 pd=O. 4u as=0. 2p"2 ps=0.4u •ends nmosl• *pmosl*•subckt pmosl pl p2 p3mp pl p2 p3 Vcc pch 1=0. 2u w=0. 8u ad=0. 4p"2 pd=O. 8u as=0. 4p 2 ps=0.8u •ends pmosl*•subckt invl in out xmn out in Gnd nmosl xmp out in Vcc pmosl vcc Vcc Gnd Supply• ends invl**nmos2*•subckt nmos2 nl n2 n3mn nl n2 n3 Gnd nch 1=0. 2u w=l. 12u ad=0. 56p 2 pd=l. 12u as=0. 56p 2 ps=l. 12u •ends nmos2**pmos2*•subckt pmos2 pl p2 p3mp pl p2 p3 Vcc pch 1=0. 2u w=2. 24u ad=l. 12p"2 pd=2. 24u as=l. 12p"2 ps=2.24u•ends pmos2••subckt inv2 in outxmn out in Gnd nmos2xmp out in Vcc pmos2vcc Vcc Gnd Supply•ends inv2**nmos3*•subckt nmos3 nl n2 n3mn nl n2 n3 Gnd nch 1=0. 2u w=3. 2u ad=l. 6p^2 pd=3. 2u as=l. 6p 2 ps=3. 2u •ends nmos3*pmos3 .subckt pmos3 pl p2 p3mp pl p2 p3 Vcc pch l=0.2u w=6.4u ad=3.2p A2 pd=6.4u as=3.2p A2 ps=6.4u .ends pmos3*.subckt inv3 in outxmn out in Gnd nm os3xmp out in Vcc pmos3vcc Vcc Gnd Supply.ends inv3**nm os4*.subckt nmos4 n1 n2 n3mnnl n2 n3 Gndnch l=0.2u w=9.04u ad=4.52pA2 pd=9.04u as=4.52pA2 ps=9.04u .ends nm os4 **pmos4*.subckt pmos4 pl p2 p3mp pl p2 p3 Vcc pch l=0.2u w=18.08u ad=9.04pA2 pd=18.08u as=9.04pA2 ps=18.08u.ends pmos4*.subckt inv4 in outxmn out in Gnd nm os4xmp out in Vcc pmos4vcc Vcc Gnd Supply.ends inv4*ma in circuit n etlistxinvl in outl invlxinv2 outl out2 inv2xinv3 out2 out3 inv3xinv4 out3 out inv4cl out Gnd 154.24fVin in Gnd 0.9 pulse(0.0 1.8 219p 40p 40p 1100p 2400p).print tran v(i n) v(out).end2.Consider the logic network below, which may represent the critical path of a morecomplex logic block. The output of the。

中科院_段成华_专用集成电路设计_作业 2

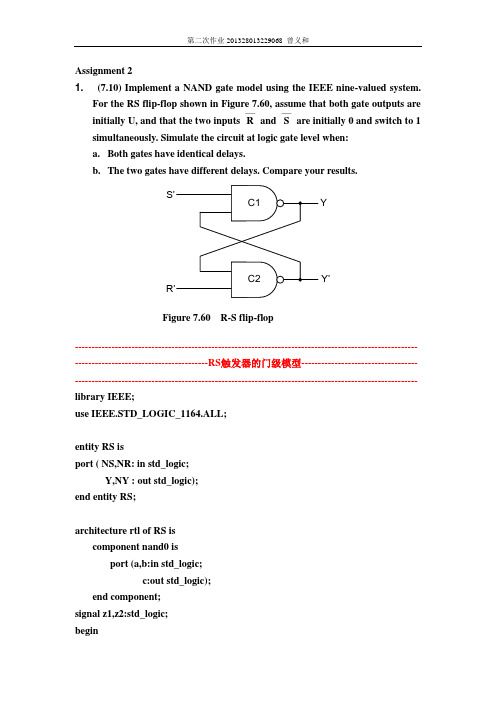

Assignment 21. (7.10)Implement a NAND gate model using the IEEE nine-valued system.For the RS flip-flop shown in Figure 7.60, assume that both gate outputs are initially U, and that the two inputs R——and S——are initially 0 and switch to 1 simultaneously. Simulate the circuit at logic gate level when:a.Both gates have identical delays.b.The two gates have different delays. Compare your results.YY’Figure 7.60 R-S flip-flop------------------------------------------------------------------------------------------------------- ----------------------------------------RS触发器的门级模型----------------------------------- ------------------------------------------------------------------------------------------------------- library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity RS isport ( NS,NR: in std_logic;Y,NY : out std_logic);end entity RS;architecture rtl of RS iscomponent nand0 isport (a,b:in std_logic;c:out std_logic);end component;signal z1,z2:std_logic;beginNY<=z2;Y<=z1;u1:nand0 port map(NS,z2,z1);u2:nand0 port map(NR,z1,z2);end architecture rtl;------------------------------------------------------------------------------------------------------- ----------------------------------RS触发器的门级模型测试激励----------------------------- ------------------------------------------------------------------------------------------------------- library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity RS_TB isend entity RS_TB;architecture RTL of RS_TB iscomponent RS isport ( NS,NR: in std_logic;Y,NY: out std_logic);end component;signal NY :std_logic:='1';signal Y :std_logic:='1';signal NS :std_logic:='0';signal NR :std_logic:='0';beginDUT:RS port map(NS => NS,NR => NR,y => y,NY => NY);processbeginNS <= '0';NR <= '0';wait for 0.1 us;NS <= '1';NR <= '1';wait for 0.1 us;end process;end architecture RTL;------------------------------------------------------------------------------------------------------- --------------共同延迟的RS电路门级仿真、此次采用的是VCS 2009.12--------------- -------------------------------------------------------------------------------------------------------一、建立和设置环境变量二、分析三、Elaboration四、仿真1、调用DVE2、查看仿真波形3、根据DVE检查波形,分析功能上图是VCS图形界面的DVE工具显示的波形图,从上面可以得到一下几个结论:1、初始状态输出端为‘U’,输入端均为‘0’;2、在1ns的反应延迟之后,输出端根据当前状态被置为‘1’;3、在100ns时,输入端同时置‘1’,此时输出端出现震荡状态。

超大规模集成电路2017年秋段成华老师第一次作业

Assignment 1:冉文浩2017180136260161.Give a formal or descriptive definition for each of the following terms.●ITRS,1●Gate-Equivalent,1●Technology Nodes,1●Feature size,1●IC design complexity sources,1 ●Behavioral representation,1●Abstraction hierarchy,1●IC design,1●Synthesis,1●Refinement,1●System-level synthesis,1●Logic synthesis,1●Layout synthesis,1●Partial design tree,●Design window,1●Digital design space,1●Static timing analysis,1●Behavioral simulation,1●Post place and routesimulation,1●Composition-based approach.12.Access the Internet for information about Daniel D. Gajski’s “Y-c hart”methodology for integrated circuits design. According to your investigation of the related research papers and/or technical reports, please summarize the “Y-c hart”theory, including (1) design representation domains, (2) design abstraction hierarchy and (3) design activities. References must be listed at the end of your report.3.Write a summary in Chinese of the paper “A New Ear in Advanced IC Design” (inless than 200 characters).1. Give a formal or descriptive definition for each of the following terms.ITRS:International Technology Roadmap for Semiconductor(国际半导体技术发展路线图)Gate-Equivalent:A gate equivalent (GE) stands for a unit of measure which allows to specify manufacturing-technology-independent complexity of digital electronic circuits. It corresponds to a two input NAND gateTechnology Nodes:DRAM 结构里第一层金属的金属间距(pitch)的一半Feature size:roughly half the length of the smallest transistor(芯片上的最小物理尺寸)IC design complexity sources: It includes four main metrics:reliability、cost、performance and power consumption. It also includes four complexity sources:large size、variability and reliability、power dissipation and heterogeneity.Behavioral representation: Represents a design as a black box and its outputs in terms of its input and time. Indicates no geometrical information or structure information. Tables the form of text, math or algorithm.Abstraction hierarchy:Abstraction hierarchies are a human invention designed to assist people in engineering every complex systems by ignoring unnecessary details.A set of interrelated representation levels that allow a system to be represented in varying amounts of details. It includes six levels:system level、chip/algorithm level、RTL、logic gate level、circuit level、layout/silicon levelIC design: An integrated circuit is a set of electronic circuits on one small flat piece (or "chip") of semiconductor material, normally silicon.(在以小片半导体材料上面设计大量的集成电路)Synthesis:将高层次的信息转换成低层次的描述,具体是指将行为域的信息转换成结构域的信息。

超大规模集成电路第七次作业2016秋,段成华

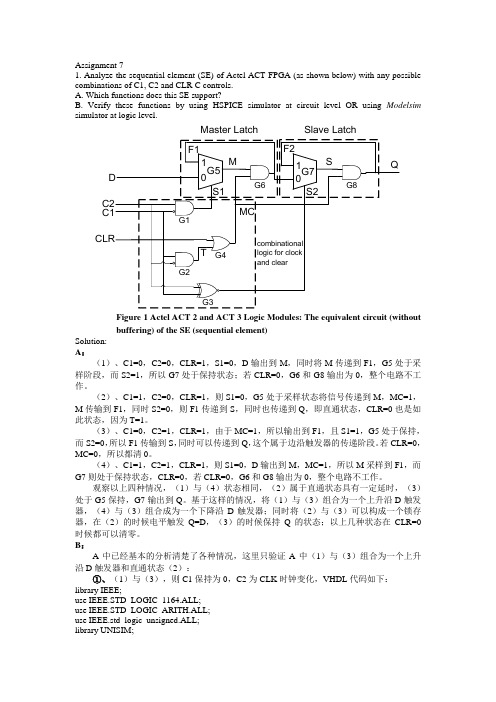

Assignment 71.Analyze the sequential element (SE) of Actel ACT FPGA (as shown below) with any possible combinations of C1, C2 and CLR C controls.A. Which functions does this SE support?B. Verify these functions by using HSPICE simulator at circuit level OR using Modelsim simulator at logic level.Master Latch Slave LatchFigure 1 Actel ACT 2 and ACT 3 Logic Modules: The equivalent circuit (withoutbuffering) of the SE (sequential element)Solution:A:(1)、C1=0,C2=0,CLR=1,S1=0,D输出到M,同时将M传递到F1,G5处于采样阶段,而S2=1,所以G7处于保持状态;若CLR=0,G6和G8输出为0,整个电路不工作。

(2)、C1=1,C2=0,CLR=1,则S1=0,G5处于采样状态将信号传递到M,MC=1,M传输到F1,同时S2=0,则F1传递到S,同时也传递到Q,即直通状态,CLR=0也是如此状态,因为T=1。

(3)、C1=0,C2=1,CLR=1,由于MC=1,所以输出到F1,且S1=1,G5处于保持,而S2=0,所以F1传输到S,同时可以传递到Q,这个属于边沿触发器的传递阶段。

若CLR=0,MC=0,所以都清0。

(4)、C1=1,C2=1,CLR=1,则S1=0,D输出到M,MC=1,所以M采样到F1,而G7则处于保持状态,CLR=0,若CLR=0,G6和G8输出为0,整个电路不工作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Assignment 81.Access relevant reference books or technical data books and give accuratedefinitions for the following timing parameters:(1)design entity,(2)signal driver,(3)transaction,(4)event,(5)time queue,(6)delta delay,(7)simulation time,(8)simulation cycle,(9)inertial time,(10)transport time.(1)design entity: In VHDL a given logic circuit represented as a design entity. Adesign entity, in return , consists of two different types of description: the interface description and one or more architectural bodies. The interface description declares the entity and describes its inputs and outputs.(2)signal driver: If a process contains one or more signal assignment statementthat schedule future values for some signal X, the VHDL simulator creates a single value holder called a signal driver.(3)transaction:A pair consisting of a value and time. The value part represents afuture value of the driver; the time part represents the time at which the value part becomes the current value of driver.(4)event: It’s a kind of signal property and presents signal jump. Such asif(clk'event and clk='1).(5)time queue: It’s used to keep some signal transactions in the simulator. Timequeue entries are represented as a two-tuple of the form(SN,V), where SN is a signal name and V is the value the signal is scheduled to assume at the scheduled time. Each time queue entry is called a signal transaction.(6)delta delay: A period of time greater than 0, but less than any standard time unitno number of delta delay added together can cause simulation time to advance.(7)simulation time: The elapsed time in standard time units during simulation.(8)simulation cycle: Every time simulation time advances, a simulation cycleoccurs, which we now define more formally. The execution of a model consists of an initialization phase followed by the repetitive execution of processes in the process network. Each repetition is said to be a simulation cycle.(9)inertial time: Example: Z <= I after 10ns; The signal propagation will takeplace if and only if input I persists at a given level for 10ns-the amount of time specified in the after clause.(10)transport time: Z <= transport I after 10ns; All changes on I will propagate toZ, regardless of how long the value of I stays at the new level.2.Construct VHDL models for 74-139 dual 2-to-4-line decoders using threedescription types, i.e., behavioral, dataflow and structural descriptions. Synthesize and simulate these models respectively in the environment of Xilinx ISE with the ModelSim simulator integrated. When simulating these models, test vector(s) are required to stimulate the units under test (UUT). Reasonable test vectors are designed and created by your own as sources added to your VHDL project.Logic schematic of 74-139:Function table of one decoder of 74-139:(1-- Company:-- Engineer:-- Create Date: 21:14:09 12/02/2016-- Design Name:-- Module Name: deceoder_beh - Behavioral -- Project Name:-- Target Devices:-- Tool versions:-- Description:-- Dependencies:-- Revision:-- Revision 0.01 - File Created-- Additional Comments:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;---- Uncomment the following library declaration if instantiating ---- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity deceoder_beh isPort ( G1,G2 : in std_logic;A : in std_logic_vector(1 downto 0);B : in std_logic_vector(1 downto 0);Y1 : out std_logic_vector(3 downto 0);Y2 : out std_logic_vector(3 downto 0));end deceoder_beh;architecture Behavioral of deceoder_beh isbeginde1: process (A, G1)beginif G1 = '1' theny1 <= "1111"; -- sequential statementelsecase A iswhen "00" => Y1 <= "1110";when "01" => Y1 <= "1101";when "10" => Y1 <= "1011";when "11" => Y1 <= "0111";when others => Y1 <= "1111";end case;end if;end process;de2: process (B, G2)beginif G2 = '1' thenY2 <= "1111"; -- sequential statementelsecase B iswhen "00" => Y2 <= "1110";when "01" => Y2 <= "1101";when "10" => Y2 <= "1011";when "11" => Y2 <= "0111";when others => Y2 <= "1111";end case;end if;end process;end Behavioral;TestBench代码如下:-- Company:-- Engineer:-- Create Date: 22:25:59 12/02/2016-- Design Name:-- Module Name: D:/ISE11.1_example/decoder/deconder_beh_tb.vhd-- Project Name: decoder-- Target Device:-- Tool versions:-- Description:-- VHDL Test Bench Created by ISE for module: deceoder_beh-- Dependencies:-- Revision:-- Revision 0.01 - File Created-- Additional Comments:-- Notes:-- This testbench has been automatically generated using types std_logic and -- std_logic_vector for the ports of the unit under test. Xilinx recommends-- that these types always be used for the top-level I/O of a design in order-- to guarantee that the testbench will bind correctly to the post-implementation -- simulation model.LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE ieee.std_logic_unsigned.all;USE ieee.numeric_std.ALL;ENTITY deconder_beh_tb ISEND deconder_beh_tb;ARCHITECTURE behavior OF deconder_beh_tb IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT deceoder_behPORT(G1 : IN std_logic;G2 : IN std_logic;A : IN std_logic_vector(1 downto 0);B : IN std_logic_vector(1 downto 0);Y1 : OUT std_logic_vector(3 downto 0);Y2 : OUT std_logic_vector(3 downto 0));END COMPONENT;--Inputssignal G1 : std_logic := '0';signal G2 : std_logic := '0';signal A : std_logic_vector(1 downto 0) := (others => '0');signal B : std_logic_vector(1 downto 0) := (others => '0');--Outputssignal Y1 : std_logic_vector(3 downto 0);signal Y2 : std_logic_vector(3 downto 0);BEGIN-- Instantiate the Unit Under Test (UUT)uut: deceoder_beh PORT MAP (G1 => G1,G2 => G2,A => A,B => B,Y1 => Y1,Y2 => Y2);-- Stimulus processstim_proc: processbegin-- insert stimulus hereG1 <='1';WAIT FOR 100 ns;G1 <='0';A <= "00";B <= "00";-- --------------------------------------- ------------- Current Time: 200nsWAIT FOR 100 ns;G1 <='0';A <= "01";B <= "01";-- --------------------------------------- ------------- Current Time: 300nsWAIT FOR 100 ns;G1 <='0';A <= "10";B <= "10";-- --------------------------------------- ------------- Current Time: 400nsWAIT FOR 100 ns;G1 <='0';a <= "11";b <= "11";WAIT FOR 100 ns;end process;END;测试波形如下:可以看到当G1=0和G2=0可以正常的译码,当G1=1和G2=1,则Y1和Y2都输出”1111”。