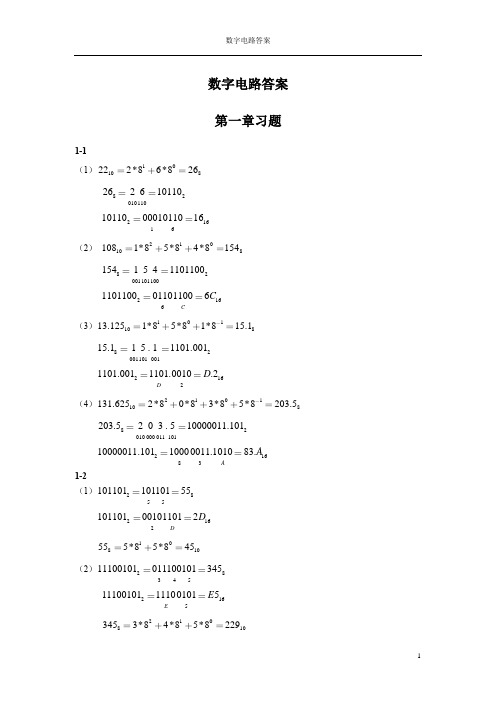

数字电路第02章习题答案

(完整版)数字电路与逻辑设计课后习题答案蔡良伟(第三版)

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

3-6

3-7

3-8

3-9

3-10

求减数的补码,然后与被减数相加即可。电路图如下:

3-11

3-12

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

3-13

(1)真值表:

(2)电路图

3-14

3-15

第四章习题

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

RSDRSJK RST

4-11

(1)转换真值表

1 1 0 1

1 1 1 0

1 1 1 1

1 0 1 0

0 0 0 0

0 0 0 1

0 0 1 0

00 11

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

××××

××××

××××

××××

××××

1×0×1×0×

0×0×0××1

0×0××1 1×

0×0××0×1

0××1 1×1×

数字集成电路分析与设计 第二章答案

CHAPTER 2P2.1. a) The solution for the NMOS case is based on Example 2.4: The equation for V T0 is: 02BT FB F OXQ V V C φ=-- Calculate each individual component.1710()1362OX 077200611196310ln 0.026ln 0.44 V 1.4100.440.550.99 V 4 3.510 F/cm1.610 F/cm 310310/0.188 V 1.610610 1.6100.1.610i FpA GC Fp G gate OXB B OX OX OX n kT q NC Q Q C cmC Q C φφφφεε-------⨯==-=-⨯=-=--=-==⨯=⨯⨯=⨯==⨯⨯⨯⨯==⨯TO 06 V V 0.99(0.88)(0.188)0.0600.018 V=------=+ For the PMOS device:1710()77200611196TO 310ln 0.026ln 0.44 V 1.4100.440.550.99 V 310310/0.188 V1.610610 1.6100.06 V 1.610V 0.99(0.88)(0.188)0.0600.138 D Fn i GC Fn G gate B B OX OX OX N kT q n Q Q C cmC Q C φφφφ-----⨯===⨯=-=+=+⨯=⨯==⨯⨯⨯⨯==⨯=---=-Vb) The magnitude of V T0 would be higher. Since the device is PMOS this means that V T0 islowered. Since the only thing that’s been changed is the doping of the gate, only G φ changes. The new V T0 then becomes:00.110.880.1880.6 1.24V T V =----=-c) Since V T0 will be adjusted with implanted charge (Q I ):60.40.0180.382(1.610)(0.382)IOXIOXI Q C Q V C Q V -=-==⨯To calculate the threshold implant level N I :I I I I qN Q Q N q==For the NMOS device from part(a):6122190.610 3.8210/1.610I I Q N ions cm q --⨯=-=-=⨯⨯ (p-type) For the PMOS device from part(a):612219(1.610)(0.40.138)2.6210/1.610I I Q N ions cm q --⨯-=-=-=⨯⨯ (n-type) For the PMOS device from part(b):612219(1.610)(1.240.4)8.410/1.610I I Q N ions cm q --⨯-=-=-=⨯⨯ (p-type)d) The advantage of having the gate doping be n + for NMOS and p + for PMOS could be seen from analysis above. Doping the gates in such a way leads to devices with lower threshold voltages, but enables the implant adjustment with the same kind of impurities that used in the bulk (p-type for NMOS and n-type for PMOS). If we were to use the same kind of doping in gate as in the body (i.e. n + for PMOS and p + for NMOS) that would lead to higher un-implanted threshold voltages. Adjusting them to the required lower threshold voltage would necessitate implantation of the impurities of the opposite type near the oxide-Si interface. This is not desirable. Also, the doping of the poly gate can be carried out at the same time as the source and drain and therefore does not require an extra step.P2.2. First, convert ox t to units of cm:810100cm222210cm 10ox t -=⨯=ÅÅNow, using the mobility equation:()()20 1.8568130/V70cm0.8114102210pep nGS T ox cm V s V V t μμθ--==≈⎛⎫⎛⎫-+ ⎪⎪+ ⎪⎝⎭⎝⎭P2.3. a) For each transistor, derive the region of operation. In our case, for 0V,0.4V GS V =, thetransistor is in the cutoff region and there is no current. For 0.8V,1.2V GS V =, firstcalculate the saturation voltage Dsat V using:()GS T C DSAT GS T C V V E L V V V E L-=-+For our transistors, this would be:Next, we derive the IV characteristics using the linear and saturation current equations,we get the graphs shown below.IV Characteristic of NMOS01020304050607000.20.40.60.811.2Volts (V)C u r r e n t (u A )IV Characteristic of PMOSVolts (V)C u r r e n t (u A )To plot DS I vs. GS V , first identify the region of operation of the transistor. For GS T V V <, the transistor is in the cutoff region, and there is negligible current. For GS T V V > and GS DS V V ≤, the transistor is in the saturation region and saturation current expression should be used. The graphis shown below. Clearly, it is closer to the linear model.Ids vs. Vgs of NMOS010********607000.20.40.60.811.21.4Vgs (V)I d s (V )P2.4. For each transistor, first determine if the transistor is in cutoff by checking to see if V GS isless than or greater than V T . V T may have to be recalculated if the source of the transistor isn’t grounded. If V GS is less than V T , then it is in cutoff, otherwise, it is in either triode or saturation.To determine if it is in the triode saturation region, check to see if V DS is less than or greater than V DSAT . If V DS is less than V DSAT , then it is in triode, otherwise, it is in saturation. a. Cutoff00.200.2V0.4V GS G S T T GS TV V V V V V V =-=-===∴<b. Cutoff01.2 1.20V0.4V GS G S T T GS TV V V V V V V =-=-===∴<c. Linear01.20 1.2V0.4V GS G S T T GS TV V V V V V V =-=-===∴>The transistor is not in the cutoff region.()()()()()()1.20.460.20.48V 1.20.460.20.2V GS T C DSATGS T C DS DS DSATV V E L V V V E L V V V --===-+-+=∴<d. Saturation: In this case, because D G V V > the transistor is in the saturation region. To see this, recognize that in a long-channel transistor if D G V V >, the transistor is in saturation. Since the saturation drain voltage Dsat V is smaller in a velocity-saturated transistor than in a long-channel transistor, if the long-channel saturation region equation produces a saturated transistor, than the velocity-saturated saturation region equation will also.P2.5. In both cases, the first step it to calculate the maximum value of X V given G V . If thevoltage at the drain is higher than this maximum value, then ,max X X V V =, otherwise,X D V V =. The maximum value of X V is G T V V - but 0T T V V ≠ because of body effect andwe consider its effect.(),max 0001.20.40.988X G T G T G T G T V V V V V V V V V γγγγ=-=-+=--=--+=--=-There are two ways to calculate this, either through iteration or through substitution. Iteration:For the iteration method, we need a starting value for V X,max . A good starting value would be 0 1.20.40.8V G T V V -=-=. We plug this value on the RHS of the equation, calculate a new V X,max and repeat until we reach a satisfactory converged value.Old Vx,max New Vx,max 0.800 0.728 0.728 0.734 0.734 0.734In this, only three iterations are needed to reach 0.734V. Substitution:The term makes things a bit tricky, we get around this by making the following substitution:2,max 2,max 0.880.88X X x V V x =+∴=-Therefore:,max 220.9880.880.98800.2 1.87X V x x x =--=-=+-2,max 1.27, 1.470.880.733,1.28X x V x ===-=-= We use the first value since second value is above V DD . a. Since ,max D X V V >, ,max 0.733V X X V V ==. b. Since ,max D X V V <, ,max 0.6V X X V V ==. P2.6.a. Initially, when 0V in V =, the transistor is in the cutoff region and 0V X V =. Thisvalue is constant until V in exceeds V t 0. From then, X in T V V V =- and body effect must be taken into account. This trend continues until 0.7V X D V V ==, and the value of V inat that point must be calculated. From then on, 0.7V X D V V ==. To plot V X in the second region, we first derive an expression for V X vs. V in.(),max 0000.40.212X G T G T in T in T in in V V V V V V V V V V V γγγγ=-=-+=---=--=--=--Substituting:2,max2,max 0.880.88X X x V V x =+∴=-Therefore:,max 220.2120.880.21200.20.66X in in in V V x V x x V =---=--=+--220.880.88XxV x====-=-⎝⎭Since this is a quadratic function, there will be two graphs of V X. Only one of thesegraphs intersects with V X in the first region. In this case, plug 0.4inV= and see which one gives 0V. In our case, it would be the ‘+’ version of the quadratic.To see where region 3 begins, we simply isolate V in:()()()22220.880.2 2.710.2 2.71440.2 2.711.16V4XinVV=-⎝⎭-+-==+-==The final graph is shown in Figure 错误!未找到引用源。

数字电子技术基础第三版第二章答案

第二章逻辑门电路第一节重点与难点一、重点:1.TTL与非门外特性(1)电压传输特性及输入噪声容限:由电压传输特性曲线可以得出与非门的输出信号随输入信号的变化情况,同时还可以得出反映与非门抗干扰能力的参数U on、U off、U NH和U NL。

开门电平U ON是保证输出电平为最高低电平时输入高电平的最小值。

关门电平U OFF是保证输出电平为最小高电平时,所允许的输入低电平的最大值。

(2)输入特性:描述与非门对信号源的负载效应。

根据输入端电平的高低,与非门呈现出不同的负载效应,当输入端为低电平U IL时,与非门对信号源是灌电流负载,输入低电平电流I IL通常为1~1.4mA.当输入端为高电平U IH时,与非门对信号源呈现拉电流负载,输入高电平电流I IH通常小于50μA。

(3)输入负载特性:实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况,电阻的取值不同,将影响相应输入端的电平取值。

当R≤关门电阻R OFF时,相应的输入端相当于输入低电平;当R≥ 开门电阻R ON时,相应的输入端相当于输入高电平。

2.其它类型的TTL门电路(1)集电极开路与非门(OC门)多个TTL与非门输出端不能直接并联使用,实现线与功能.而集电极开路与非门(OC门)输出端可以直接相连,实现线与的功能,它与普通的TTL与非门的差别在于用外接电阻代替复合管.(2)三态门TSL三态门即保持推拉式输出级的优点,又能实现线与功能。

它的输出除了具有一般与非门的两种状态外,还具有高输出阻抗的第三个状态,称为高阻态,又称禁止态.处于何种状态由使能端控制.3.CMOS逻辑门电路CMOS反相器和CMOS传输门是CMOS逻辑门电路的最基本单元电路,由此可以构成各种CMOS逻辑电路。

当CMOS反相器处于稳态时,无论输出高电平还是低电平,两管中总有一管导通,一管截止,电源仅向反相器提供nA级电流,功耗非常小。

CMOS器件门限电平U TH近似等于1/2U DD,可获得最大限度的输入端噪声容限U NH和U NL=1/2U DD。

数字电子技术第二章(逻辑门电路)作业及答案

数字电子技术第二章(逻辑门电路)作业及答案第二章(逻辑门电路)作业及答案1.逻辑门电路如下图所示:(1)电路均为TTL电路,试写出各个输出信号的表达式。

(2)电路若改为CMOS电路,试写出各个输出信号的表达式。

答案:(1),,,(2),,,2、已知TTL反相器的电压参数为V IL(max)=0.8V,V OH(min)=3V,V TH=1.4V,V IH(min)=1.8V,V OL(max)=03V,V CC=5V,试计算其高电平噪声容限V NH和低电平噪声容限V NL。

答案:V NL= V IL(max) - V OL(max)=0.5V,V NH= V OH(min) - V IH(min) =1.2V。

3、试写出图2-1、图2-2所示逻辑电路的逻辑函数表达式。

解:(1)(2)4、试分析图2-3所示MOS电路的逻辑功能,写出Y端的逻辑函数式,并画出逻辑图。

5、试简要回答下列问题。

(1)有源(图腾柱)输出与集电极开路(OC)输出之间有什么区别?解:OC门输出端只能输出低电平和开路状态,其输出级需要上拉电阻才能输出高电平,且上拉电源可以与芯片电源不同,因此常用于不同电源电压芯片之间实现信号电平变换,OC门输出端可以并联实现线与;有源输出可以输出低电平与高电平,两个有源输出端连接在一起时,若是一个输出端输出高电平,另外一个输出端输出低电平时,可引起较大电流损坏输出级。

(2)TTL逻辑电路输入端悬空时,可视为输入高电平信号处理,而CMOS逻辑电路输入端则不允许悬空使用,试说明其原因。

解:因为CMOS电路的输入端具有非常高的输入阻抗,容易受到干扰,一旦受到干扰后,会使输出电平发生转换,产生功耗,因此输入端不能悬空,应该连接确定的逻辑电平。

6.请查阅74LS00芯片手册(常规温度范围的),回答如下问题:(1)电源电压范围;(2)输出高电平电压范围;(3)输出低电平电压范围;(4)输入高电平电压范围;(5)输入低电平电压范围;(6)该芯片的电源电流;(7)典型传播延迟时间;(8)扇出系数。

数字电子技术课后习题答案

❖ 3.21 用8选1数据选择器74151设计一个组合 逻辑电路。该电路有3三个输入逻辑变量A、B、 C和一个工作状态控制变量M。当M=0时电路 实现“意见一致”功能( A、B、C状态一致 时输出为1,否则输出为0),而M=1时电路 实现“多数表决”功能,即输出与A、B、C中 多数的状态一致。

数字电子技术作业

第一章数字逻辑基础 第二章逻辑门电路 第三章组合逻辑电路 第四章触发器 第五章时序逻辑电路 第六章脉冲波形的产生与整形 第七章半导体存储器 第八章可编程逻辑器件 第九章数/模和模/数转换器

1.12 写出下图所示各逻辑图的输出函数表达式,列 出它们的真值表。

F1 F4

F2

F3

解: F1 AB F2 A B F3 BC

ABACBC

BC

A

00 01 11 10

00

1

0

1

11

0

1

0

Y ABC

❖ 3.13某医院有一、二、三、四号病室4间,每室设有 呼叫按钮,同时在护士值班室内对应的装有一号、 二号、三号、四号4个指示灯。

❖ 现要求当一号病室的按钮按下时,无论其它病室的 按钮是否按下,只有一号灯亮。当一号病室的按钮 没有按下而二号病室的按钮按下时,无论三、四号 病室的按钮是否按下,只有二号灯亮。当一、二号 病室的按钮都未按下而三号病室的按钮按下时,无 论四号病室的按钮是否按下,只有三号灯亮。只有 在一、二、三号病室的按钮均未按下四号病室的按 钮时,四号灯才亮。试用优先编码器74148和门电路 设计满足上述控制要求的逻辑电路,给出控制四个 指示灯状态的高、低电平信号。

Y CBA CB CA CBACB CA

《电子技术基础》第五版(数字部分)高教版课后答案

1.1 数字电路与数字信号第一章 数字逻辑习题1.1.2 图形代表的二进制数MSBLSB 0 1 211 12(ms )解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms 频率为周期的倒数,f=1/T=1/=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10% 数制1.2.2 将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于 2 (2)127 (4)解:(2)(127)D=27-1=()B-1=(1111111)B =(177)O=(7F )H (4)()D=B=O=H 二进制代码1.4.1 将下列十进制数转换为 8421BCD 码: (1)43 (3) 解:(43)D=(01000011)BCD1.4.3 试用十六进制写书下列字符繁荣 ASC Ⅱ码的表示:P28 (1)+ (2)@ (3)yo u (4)43解:首先查出每个字符所对应的二进制表示的 ASC Ⅱ码,然后将二进制码转换为十六进制 数表示。

(1)“+”的 ASC Ⅱ码为 0101011,则(00101011)B=(2B )H (2)@的 ASC Ⅱ码为 1000000,(01000000)B=(40)H(3)you 的 ASC Ⅱ码为本 1111001,1101111,1110101,对应的十六进制数分别为79,6F,75 (4)43 的 ASC Ⅱ码为 0110100,0110011,对应的十六紧张数分别为 34,33 逻辑函数及其表示方法解: (a)为与非, (b)为同或非,即异或第二章逻辑代数习题解答2.1.1 用真值表证明下列恒等式(3) A⊕B AB AB(A⊕B)=AB+AB解:真值表如下A B A⊕BAB AB A⊕BAB+AB0 0 1 11111111111A (1BC ) ACDCDEA ACDCDEACD CDEACD E2.1.4 用代数法化简下列各式(3) ABC B C)A⋅B A⋅B(A B)(A B)1BAB ABABBABAB(9) ABC DABD BC D ABCBD BC解: ABC DABDBC DABCBD BCB ( ACD )L D ( AC)2(3)(L AB)(C D)2.2.2 已知函数 L(A,B,C,D)的卡诺图如图所示,试写出函数 L 的最简与或表达式解:L( A, B, C, D) BC D BCD B C D ABD2.2.3 用卡诺图化简下列个式(1)ABCD ABCD AB AD ABC3解:ABCD ABCD AB AD ABCABCD ABCD AB CC DDAD B B CCABC D D)()()()()(ABCD ABCD ABC D ABCD ABC D ABC D ABC D(6)L( A, B, C, D ) ∑m解:(0, 2, 4, 6,9,13)∑d(1, 3, 5, 7,11,15)L AD(7)L( A, B, C , D )∑m 解: (0,13,14,15)∑d(1, 2, 3, 9,10,11)L AD AC AB42.2.4 已知逻辑函数L AB BC C A,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表A11112>由真值表画出卡诺图B1111C1111L1111113>由卡诺图,得逻辑表达式L AB BC AC 用摩根定理将与或化为与非表达式L AB BC AC AB⋅B C⋅AC4>由已知函数的与非-与非表达式画出逻辑图5第三章习题MOS逻辑门电路3.1.1 根据表题所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。

数字电子技术基础第三版第二章答案

第二章逻辑门电路第一节重点与难点一、重点:1.TTL与非门外特性(1)电压传输特性及输入噪声容限:由电压传输特性曲线可以得出与非门的输出信号随输入信号的变化情况,同时还可以得出反映与非门抗干扰能力的参数U on、U off、U NH和U NL。

开门电平U ON是保证输出电平为最高低电平时输入高电平的最小值。

关门电平U OFF 是保证输出电平为最小高电平时,所允许的输入低电平的最大值。

(2)输入特性:描述与非门对信号源的负载效应。

根据输入端电平的高低,与非门呈现出不同的负载效应,当输入端为低电平U IL时,与非门对信号源是灌电流负载,输入低电平电流I IL通常为1~1.4mA。

当输入端为高电平U IH时,与非门对信号源呈现拉电流负载,输入高电平电流I IH通常小于50μA。

(3)输入负载特性:实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况,电阻的取值不同,将影响相应输入端的电平取值。

当R≤关门电阻R OFF时,相应的输入端相当于输入低电平;当R≥ 开门电阻R ON时,相应的输入端相当于输入高电平。

2.其它类型的TTL门电路(1)集电极开路与非门(OC门)多个TTL与非门输出端不能直接并联使用,实现线与功能。

而集电极开路与非门(OC 门)输出端可以直接相连,实现线与的功能,它与普通的TTL与非门的差别在于用外接电阻代替复合管。

(2)三态门TSL三态门即保持推拉式输出级的优点,又能实现线与功能。

它的输出除了具有一般与非门的两种状态外,还具有高输出阻抗的第三个状态,称为高阻态,又称禁止态。

处于何种状态由使能端控制。

3.CMOS逻辑门电路CMOS反相器和CMOS传输门是CMOS逻辑门电路的最基本单元电路,由此可以构成各种CMOS逻辑电路。

当CMOS反相器处于稳态时,无论输出高电平还是低电平,两管中总有一管导通,一管截止,电源仅向反相器提供nA级电流,功耗非常小。

CMOS器件门限电平U TH近似等于1/2U DD,可获得最大限度的输入端噪声容限U NH和U NL=1/2U DD。

数字电路课后习题答案第二章

2.8

(a)

(b)

2.9

(a)

(b)

2.10 (a)

(b)

(c)

2.11 decimal signed-magnitude two’s-magnitude one’s-complement 2.12 (a)

11010100 (b) 101110011 (c) 01011101 (d) 00100110 + 10101011 + 11010110 + 00100001 + 01011010 ------------------------------------------------------------------------------------------------------------------------01111111 10001111 01111101 10000000 yes no no yes

2.6

(a) (c) (e) (g) (i)

125 10 = 1111101 2 209 10 = 11010001 2 132 10 = 1000100 2 727 10 = 10402 5 1435 10 = 2633 8 1100010 110101 + 11001 ------------------------1001110 110000 110101 - 11001 -----------------------011100 1372 + 4631 ------------------6223 1372 + 4631 ------------------59A3 (b)

2.7

(a)

111111110 (d) 11000000 1011000 (c) 11011101 101110 1110010 + 1100011 + 100101 + 1101101 ------------------------------------------------------------------------------------101000000 1010011 11011111 0011010 000010 (c) 11000100 (d) 1110010 11011101 101110 - 1101101 - 1100011 - 100101 ------------------------------------------------------------------------------------0000101 01111010 001001 47135 + 5125 ------------------54262 4F1A5 + B8D5 ---------------------5AA7A + 18 00010010 00010010 00010010 (c) 175214 (d) 110321 + 152405 + 56573 ---------------------------------------------347621 167114 F35B + 27E6 -------------------11B41 + 115 01110011 01110011 01110011 (d) 1B90F + C44E --------------------27D5D +79 01001111 01001111 01001111 –49 10110001 11001111 11001110 –3 10000011 11111101 11111100 –100 11100100 10011100 10011011

数字电子技术基础课后习题答案第2章习题答案

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

数字电路_第二章答案

(A)

(B)

图 T2.19

(C)

(D)

[ T2.20 ] 设图 T2.20 所示 电路 均 为 LSTTL 门电路,能 实现 F = A 功能的电路

PDF 文件使用 "pdfFactory Pro" 试用版本创建

2 集成门电路习题解答

3

是

。

EN

(A)

(B)

图 T2.20

8

解:电路为 OC 输出的同或门 [P2.6] 图 P3.6 中 G1、G2、G3 为 LSTTL 门电路,G4、G5、G6 为 CMOS 门电路。 试指出各门的输出状态(高电平、低电平、高阻态?) 。

G1 5V & 20Ω Y1 5V 0.3V 3.6V G2 & EN Y2 5V G3 & 10kΩ Y3

PDF 文件使用 "pdfFactory Pro" 试用版本创建

2 集成门电路习题解答

10

图 P2.9

解: F1 = A + B

F2 = A + BC

F3 = AB CD

F4 = AB EN + CD EN

[P2.1功能?如能的在括号内写 “Y” ,错的写“N” 。

+ 5V

0.2kΩ

RC

G1

A B

≥1

VD

RB

10kΩ

T2

&

G2

C D

图 P2.8

解: (1)要使发光二极管 VD 发光必须使 T 管饱和导通,要使 T 管饱和导通,必须使 G1 输出高电平,G2 输出低电平,即 A=B=0,C=D=1,因此,当且仅当 ABCD=0011 时,VD 才可能发光。 (2)为使三极管导通时进入饱和状态,三极管β的选择必须满足 IB≥IBS,式中

数字电路课后题参考答案

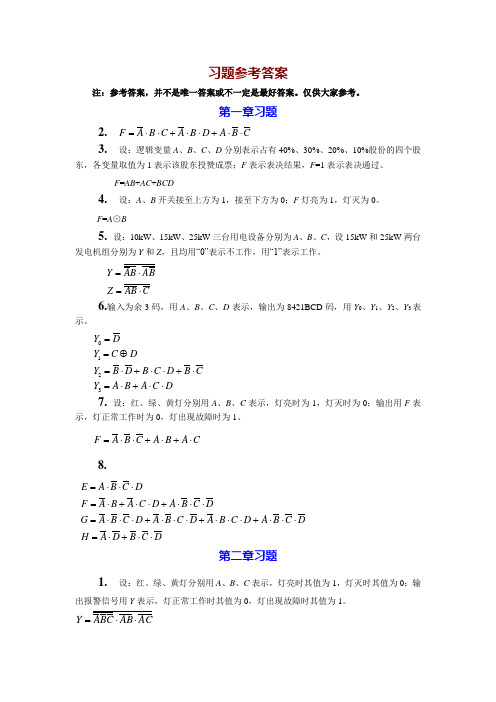

习题参考答案注:参考答案,并不是唯一答案或不一定是最好答案。

仅供大家参考。

第一章习题2. C B A D B A C B A F ⋅⋅+⋅⋅+⋅⋅=3. 设:逻辑变量A 、B 、C 、D 分别表示占有40%、30%、20%、10%股份的四个股东,各变量取值为1表示该股东投赞成票;F 表示表决结果,F =1表示表决通过。

F =AB +AC +BCD4. 设:A 、B 开关接至上方为1,接至下方为0;F 灯亮为1,灯灭为0。

F =A ⊙B5. 设:10kW 、15kW 、25kW 三台用电设备分别为A 、B 、C ,设15kW 和25kW 两台发电机组分别为Y 和Z ,且均用“0”表示不工作,用“1”表示工作。

C AB Z BA B A Y ⋅=⋅=6.输入为余3码,用A 、B 、C 、D 表示,输出为8421BCD 码,用Y 0、Y 1、Y 2、Y 3表示。

D C A B A Y CB DC BD B Y DC Y DY ⋅⋅+⋅=⋅+⋅⋅+⋅=⊕==32107. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时为1,灯灭时为0;输出用F 表示,灯正常工作时为0,灯出现故障时为1。

C A B A C B A F ⋅+⋅+⋅⋅=8. D C B D A H DC B AD C B A D C B A D C B A G DC B AD C A B A F DC B A E ⋅⋅+⋅=⋅⋅⋅+⋅⋅⋅+⋅⋅⋅+⋅⋅⋅=⋅⋅⋅+⋅⋅+⋅=⋅⋅⋅=第二章习题1. 设:红、绿、黄灯分别用A 、B 、C 表示,灯亮时其值为1,灯灭时其值为0;输出报警信号用Y 表示,灯正常工作时其值为0,灯出现故障时其值为1。

AC AB C B A Y ⋅⋅=2. 设:烟、温度和有害气体三种不同类型的探测器的输出信号用A 、B 、C 表示,作为报警信号电路的输入,有火灾探测信号时用1表示,没有时用0表示。

报警信号电路的书躇用Y 表示,有报警信号时用1表示,没有时用0表示。

数字电路第二章答案

第二章 组合逻辑电路习题参考答案2-1 写出图2-29所示各逻辑电路输出的逻辑表达式,列出真值表。

解:(a) BC AB Z +=1(b) D C B A D C B A Z =+⋅+=2 真值表:(3) E D C B A E D C B A Z +++++++=)(3 E D C B A E D C B A +++⋅+++= ))((E D C B A E D C B A ++++++++=++BCD⋅+]=++EA+])A()([[EBCDA+BA++C=++A(E)(DD)BEBCBECA+A+D=++BEDEEBCAE真值表:2-2分析图2-30所示的各逻辑电路,写出输出的逻辑表达式,列出真值表。

解:(a) )()(AC C B A C B A Z ⋅+⋅⊕+⊕= C B A C A B A C B A ⊕++=)(C B A C A B A C B A C B A C A B A C B A +++++=)( C B A A C B A C B A C A B A C B A +=+=+++= 真值表:(b) C B A ABC C B A C B A C B C B A C B A X +++=+⊕=⊕⊕=)()( C A BC B A Y ++=2-3分析图2-31所示的逻辑电路,画出电路输出的波形图。

解:由逻辑图可以得到其输出表达式C AD D BC B AD C AD D BC B AD Z +++==)( C AD D C B B D A +++++=)()( C AD D C D B D B B A +++++= C AD D B D B B A ++++=波形图如下:ABCD Z2-4用与门、或门和非门实现下列逻辑函数。

(1)AB F =1 (2)B A F +=2 (3)BD AC F +=3 (4)))((4D C B A F ++= (5)CD B A F +=5 (6)E B A D C B F ++=)(6略。

数电各章复习题及答案.

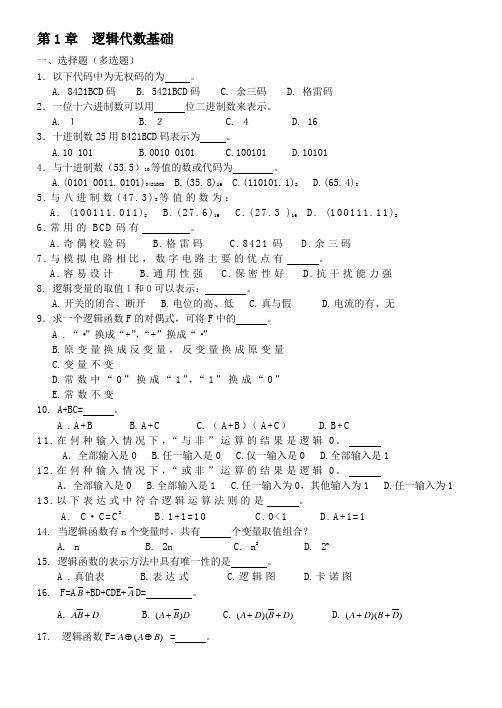

第1章逻辑代数基础一、选择题(多选题)1.以下代码中为无权码的为。

A. 8421BCD码B. 5421BCD码C. 余三码D. 格雷码2.一位十六进制数可以用位二进制数来表示。

A. 1B. 2C. 4D. 163.十进制数25用8421BCD码表示为。

A.10 101B.0010 0101C.100101D.101014.与十进制数(53.5)10等值的数或代码为。

A.(0101 0011.0101)8421BCDB.(35.8)16C.(110101.1)2D.(65.4)85.与八进制数(47.3)8等值的数为:A. (100111.011)2B.(27.6)16C.(27.3 )16D. (100111.11)26.常用的B C D码有。

A.奇偶校验码B.格雷码C.8421码D.余三码7.与模拟电路相比,数字电路主要的优点有。

A.容易设计B.通用性强C.保密性好D.抗干扰能力强8. 逻辑变量的取值1和0可以表示:。

A.开关的闭合、断开B.电位的高、低C.真与假D.电流的有、无9.求一个逻辑函数F的对偶式,可将F中的。

A .“·”换成“+”,“+”换成“·”B.原变量换成反变量,反变量换成原变量C.变量不变D.常数中“0”换成“1”,“1”换成“0”E.常数不变10. A+BC= 。

A .A+B B.A+C C.(A+B)(A+C) D.B+C11.在何种输入情况下,“与非”运算的结果是逻辑0。

A.全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是112.在何种输入情况下,“或非”运算的结果是逻辑0。

A.全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为113.以下表达式中符合逻辑运算法则的是。

A.C·C=C2B.1+1=10C.0<1D.A+1=114. 当逻辑函数有n个变量时,共有个变量取值组合?A. nB. 2nC. n2D. 2n15. 逻辑函数的表示方法中具有唯一性的是。

数字电路简明教程习题

第一章 ∙问题 1∙得2 分,满分2 分∙八进制数100对应的十进制数是()。

答案所选答案: B.64正确答案: B.64∙∙问题 2∙得0 分,满分2 分∙逻辑函数F=AB+C写成最小项表达式是。

A 的指定答案:m(1,3,5,6,7)A 的正确答案:F=m1+m3+m5+m6+m7∙∙问题 3∙得2 分,满分2 分∙十六进制数16用二进制表示为()。

答案所选答案: D.10110正确答案: D.10110∙∙问题 4∙得10 分,满分10 分∙按照数制的构成原理,四进制数一共有个数码,分别是、、、。

A 的指定答案:4B 的指定答案:C 的指定答案:1A 的正确答案:4B 的正确答案:C 的正确答案:1D 的正确答案:2E 的正确答案:3∙∙问题 5∙得2 分,满分2 分∙逻辑函数的取值有种。

A 的指定答案:2A 的正确答案:2∙∙问题 6∙得2 分,满分2 分∙用8421BCD码对十进制数68进行编码,则编码为。

A 的指定答案:01101000A 的正确答案:01101000∙∙问题 7∙得2 分,满分2 分∙关于逻辑函数化简的说法,错误的是()。

答案所选答案:C.如果采用公式法化简过程中使用不同的公式得到不同的结果,则只有一个结果是正确的,必须还要做辨别的工作。

正确答案:C.如果采用公式法化简过程中使用不同的公式得到不同的结果,则只有一个结果是正确的,必须还要做辨别的工作。

∙∙问题 8∙得6 分,满分6 分∙基本的逻辑运算主要有、、等。

C 的指定答案:非A 的正确答案:与B 的正确答案:或C 的正确答案:非∙∙问题 9∙得2 分,满分2 分∙六进制数50对应的十进制数是()。

答案所选答案: C.30正确答案: C.30∙∙问题 10∙得2 分,满分2 分∙逻辑函数F(A,B,C,D)的卡诺图中有7个方格填有1,其他都填的是0,则其最小项表达式有项。

A 的指定答案:7A 的正确答案:7∙∙问题 11∙得2 分,满分2 分∙八进制数70对应转换为十六进制数为。

数字电路第二章习题答案

第二章答案1.2.(1) v 0=0.6V(2) v 0=3.6V(3) v 0=3.6V ,v A =3V(4) V V V v B 2.2,8.20==3.(1) V V R V V R V V I cB I 2.27.02.160129.8601.097.0≈+⨯⨯≥⨯-≥-5. 与非门,采用多发射极三极管可以加快门电路速度6.可以,与非或非输入端接在一起即可,异或门将输入端之一接1。

7.8.9.()Ω=Ω-Ω≤≥+⨯⨯-∴≤≥Ω=Ω≤≤⨯⨯∴≤≤K M R VR R A I V V K R VR m AI V V IH IH IL IL 8.920001.04520520,42002.04.054.04.0,4.022122μ10.10G 10V 100404106.116M IL =∴====个与非门。

可以驱动图是连接的输入时每个门算一路,又与非门A mA G mA mA G MH ML μ 11.个个则只能驱动如果每个的输入端改为个二输入或非门。

可以驱动图是连接的路,输入时每个输入端算一又或非门245V IL ∴ 12.()()Ω=Ω=≤∴-≤⨯+⨯Ω=Ω≈≥∴-≥⨯-⨯K M R R K R R L L L L 5005.03608.12.3520310037007.08.66.44.054.038 13.14.CB AC AB C B A Y C AB Y A C Y +=+⊕==⎩⎨⎧==321,,)1高阻(15.CMOS 输入端悬空时栅极积累电荷极性不定,造成逻辑值不定甚至引起振荡。

16.(2)、(3)、(5)17. (1),(2)18. (a )AB Y =2, (b)异或门。

(c )CD AB Y +=319.(a )C B A C B A Y ++=∙∙=, (b )AB C Y ∙=。

数字电路第01-04章在线测试答案

数字电路第01-04章在线测试答案(共14页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--《数字电路》第01章在线测试《数字电路》第01章在线测试剩余时间:59:54答题须知:1、本卷满分20分。

2、答完题后,请一定要单击下面的“交卷”按钮交卷,否则无法记录本试卷的成绩。

3、在交卷之前,不要刷新本网页,否则你的答题结果将会被清空。

第一题、单项选择题(每题1分,5道题共5分)1、将下面的二进制数转换为等值的十进制数:(01101)2A、10B、13C、15D、172、逻辑函数的基本运算有与、或和A、与或B、非C、同或D、异或3、在一个函数中,将其中的与“·”换成或“+”,所有的或“+”换成与“·”;“0”换成“1”,“1”换成“0”;原变量换成反变量,反变量换成原变量。

这个规则称为A、反演规则B、代入规则C、摩根规则D、取消规则4、逻辑函数式通常指的是把逻辑函数的输入、输出关系写成()等的组合式。

A、异或B、最大项C、与、或、非D、同或5、将最小项各用一个小方格表示,并按一定规则(几何相邻的也逻辑相邻)排列,这样的图形称为A、逻辑图B、最小项C、最大项D、卡诺图第二题、多项选择题(每题2分,5道题共10分)1、数字逻辑中常用的数制有A、二进制B、八进制C、十进制D、十六进制E、五十进制F、一百进制2、逻辑函数的基本规则(定理)包括A、代入规则B、反演规则C、最小规则D、对偶规则E、最大规则3、卡诺图具有下面哪些特点A、每个方格内至少包含两个最小项B、几何相邻的最小项,逻辑上也相邻C、几何相邻的情况包括相接(紧挨着)D、是上下、左右均闭合的图形E、几何相邻的情况包括相对(任一行或任一列的两头)4、画卡诺图时遵循的原则包括A、圈内的1格数必须是2的k次方(2,4,8,16等)B、相邻1格包括:上下底、左右边、四角C、圈越大越好(圈尽可能少)D、同一个1格可被不同圈包围,但新增圈中要包含新的1格E、必须要把1格圈完5、数字电路中,逻辑函数常用的两种化简方法有A、加减消去法B、公式法化简C、乘除消去法D、卡诺图法化简E、微变等效电路法第三题、判断题(每题1分,5道题共5分)1、16进制的基数为16正确错误2、在数字电路中,主要研究的是电路的输入与输出之间的逻辑关系,因此数字电路又称逻辑电路,其研究工具是逻辑代数。

数字电子技术基础 第02章门电路习题解

& & &

2.8

试比较TTL电路和CMOS电路的优、缺点。

解 CMOS门电路具有电路结构简单、功耗低、集成度高、抗 干扰能力强;工作速度较慢 TTL门电路工作速度快;功耗高、集成度较低、抗干扰能 力较弱

2.9 试说明下列各种门电路中哪些的输出端可以并联使用。 (1)具有推拉式输出级的TTL门电路; (2)TTL电路的OC门; (3)TTL电路的三态输出门; (4)普通的CMOS门: (5)漏极开路的CMOS门; (6)CMOS电路的三态输出门。

解:TTL输入标准值 UIH=2V (1)以基本TTL与非门为例,当输入端悬空时,T1和射极电流 iE1=0,集电极正偏,T2,T5饱和导通,相当于输入高电平情况,即 等效逻辑1 (2)uI>2V=UIH,所以为逻辑1 (3)uI>3.6V>2V=UIH,所以为逻辑1

2.4 指出图2.43中各门电路的输出是什么状态(高电平、低电平或高阻 态)。假定它们都是T1000系列的TTL门电路。 U & Y

逻辑门电路习题开关特性ttl门oc门综合mos21在图242所示各电路中当输入电压u分别为0v5v悬空时试计算输出电压u010202051102v假设成立u50751084ma1007200535maibsc10032300162mabsct饱和导通10v假设成立uuiuo2k3020k51k20k51k07v5v10va121010202051102v假设成立u50751084ma1007200535maibsc10032300162mabsct饱和导通10v假设成立uuiuo2k18k47k20k51k07v5v10vb122为什么说ttl与非门输入端在以下三种接法时在逻辑上都属于输入为0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

U CC 0.3

N = = 8.7

(U CC U be ) ⋅ 0.5

(1) R i = 0.5K 时, U i = = 0.6V

R L max = = 300& ,所以 R L δ 300&

. . . .

.

. . . . 数字电路与逻辑设计

第二章习题答案

2-1. 根据图 P2-1 所示二极管门电路, 写出电路输出表达式, 计算负载电阻的最小值.

F = A ⊕ B ⊕ C

U OH = E C ⋅

R L 5 + R L

= 3V

R L = 7.5K &

2-2. TTL 与非门按图 P2-2 所示电路进行测试,是否可以得出下述三点结论.

(1)因为

U i = 18V 时, U OL = 0.28V ,由图 2-15可知,当 U OL = 0.4V 时, U i < 18

V , 所以结论正确;

(2)由图 2-15可知, U i ε 18V 时

, U OL δ 0.28V ,所以输出低电平 U OL δ 0.3V ;

(3)图中灌电流

I L = = 13mA ,且能正常工作 ,若 I is = 15mA ,则

380

13

15 2-3. 如图 P2-3 所示, 在 TTL 与非门输入端接入一个电阻, 计算输入电压.

3 + 0.5

(2) R i = 2 K 时,这时 T 2、 T 5导通, U i = 14V

2-4. 有两个 TTL 与非门组件, 试判断哪一个抗干扰能力大.

TTL A 的抗干扰能力大.

2-5. TTL 门电路如图 P2-4(a), (b)所示, 试确定图中电阻的取值范围.

(a)当

F '为高电平时, F 与 R L 无关.

若 F '为低电平, U iL max = 0.4V , I is = 10mA

0.4V 01V

10mA

(b)当 F '为低电平时,不影响 F .

若 F '为高电平, U iH min = 2.4V , I OH = 500∝A , I iH = 20∝A

R L min = U iH min

I OH I iH

= 5K & ,所以 R L ε 5K &

2-6. 判断对错, 并简述理由.

(1) F 1错,输出端不能并接; (2) F 2错,拉电流 16mA > 5mA ; (3) F 3错,输入端接低电阻 200&,输出恒为 1; (4) F 4对,灌电流

5mA < 20mA 正常工作;

(5) F 5错,输入电阻大于开门电阻,输出恒为 0.

2-7. 试写出图 P2-6 所示电路的逻辑表达式, 并用真值表说明这是一个什么逻辑功能部件.

输出

F = AB + AB = A B ,同或门

2-8. 图 P2-7 所示的为高阈值逻辑电路.

(1) T 3和

D 0组成 T 2的有源负载,提高负载能力.

当输入全部是高电平输出低电平时,这时是灌电流负载, D 0导通, T 3截止, R 4 电阻较大,内部电路流入

T 2集电极电流较少,有利于带负载,提高负载能力.

.1.

= = 20

OC 门输出高电平, R L max = = = 3.2 K &

. .

当输入有低电平输出高电平时, T 2、 D 0截止, T 3导通, T 3构成射随输出,输出

电阻很小,提高负载能力.

(2)输出低电平: U OL = U ces 2 + U D 0 = 0.3 + 0.7 = 1V 输出高电平: U OH = U OL U R 4

U be 3

因流出电流小, U R 4 H 0 ,所以

U H = U OL U be 3 = 14.3V

2-9. TTL 与非门测试电路如图 P2-8 所示. 2-10. 分析图 P2-9 所示的电路, 求出各电路能驱动多少个逻辑门.

(a)输出高电平:

I OH 2 ⋅ I iH

0.5 2 ⋅ 0.02 = 12.5

输出低电平: I OL

I iL 8 0.4

(b)输出高电平:

I OH 2 ⋅ I iH

0.5 2 ⋅ 0.02 = 12.5 输出低电平:

I OL 2 ⋅ I iL

=8 2 ⋅ 0.4 = 10 (c)输出高电平:

I OH ⋅ 2 I iH ⋅ 3

0.5 ⋅ 2 0.02 ⋅ 3 = 16

输出低电平:

I OL ⋅ 2 I iL ⋅ 3

8 ⋅ 2 0.4 ⋅ 3 = 13

2-11. 将四个 OC 与非门输出端并接在一起驱动八个 TTL 与非门, 求负载电阻的值.

U CC U OH min 5 2.4

nI OH + mI iH 4 ⋅ 01 + 8 ⋅ 0.05

C 门输出低电平, R L min = U CC U L I L max mI is =5 0.4 25 8 ⋅ 15 = 354& 可以取

R L = 500&

2-12. 把三个与非门首尾相连, 试画出波形,求振荡频率.

.2.

= = 8.3 ⋅ 106 Hz f =

1 1

T 6tpd

2-13. 输入信号 A,B,C 的波形如图 P2-12, 试画出函数波形.

2-14.

试写出图 P2-13 所示 ECL 或/或非门连成的线逻辑函数. F 1 = A + B

F 2 = C + D + E + F +

G F 3 = A + B + C + D + E + F + G

2-15. ECL 门电路的主要特点是什么?

(1)开关时间短,可在 1∝s 以下; (2)功耗大,约为 60<80mW; (3)负载能力强; (4)抗干扰能力低.

2-16. 试分析图 P2-14 所示 NMOS 电路的逻辑功能, 写出函数表达式. 图(a)

F = ( E ⊕ D + B ⊕ C ) ⊕ A + ( A ⊕ B + C ) ⊕ E = AED + ABC + ABE + CE

图(b)

F = AB + AB

2-17. 试分析图 P2-15 所示 PMOS 电路的逻辑功能, 写出函数表达式.

F = AC + B

2-18. 试分析图 P2-16 所示 NMOS 电路的逻辑功能.

F = A + B

2-19. 试画出实现逻辑函数

F = ( A + C ) D + BC 的 NMOS 电路图.

F = AD + CD + BC

.3.

= = 1mA > 0.51 = I OL ; 输出低电平时: N = =

(b)输出高电平时: N = =

输出低电平时: N = = = 1;

2-20. 图

P2-17 所示的 CMOS 电路, 问个电路是否能正常工作. (1)错,灌电流负载,输出低电平时 I L =

U DD

R L 5V 5K &

(2)错,输入端不能悬空;

(3)对,输入低电平,输出恒为 1;

(4)对,两个门电路输入端相同,输出也相同,输出可以并接.实现函数 F 4 = A + B ;

(5)错,输出不能并接;

(6)对,两个门电路的三态控制端互补,输出可以并接.实现函数 F 6 = ABE + CDE

2-21. 试画出实现逻辑函数

F = AB + C 的 CMOS 电路图

F = AB + C = AB + C

2-22. 分析图

P2-18 所示电路, 计算电路能驱动门的个数. (a)输出高电平时: N =

I OH 2 I iH

0.51mA 2 ⋅ 1∝A = 255 ;

I OL

2 I iL 0.51mA 2 ⋅ 1∝A

= 255 ; I OH

2 I iH 0.51mA 2 ⋅ 20∝A H 12 ; I OL 0.51mA

I iL 0.5mA

2-23. 试分析图 P2-19 所示 CMOS(C007)电路逻辑功能, 并写出表达式.

F = A + B + C + D

.4.。