基于PLL的时钟恢复设计方案

PLL基本原理设计及应用

PLL基本原理设计及应用PLL(Phase-Locked Loop)是一种常用的电子电路,用来将输入信号的频率、相位和幅度与一些参考信号同步。

PLL广泛应用于通信系统、电视接收机、射频标准源、数字时钟等领域。

PLL的核心部分是相位比较器、低通滤波器、VCO(VoltageControlled Oscillator)三个部分。

其基本工作原理如下:1.输入信号与参考信号经过相位比较器进行相位检测,产生一个误差信号。

2.误差信号经过低通滤波器进行滤波,得到一个平均值。

3.平均值经过放大后,作为VCO控制电压。

4.VCO产生的输出信号再反馈到相位比较器作为参考信号,与输入信号进行比较。

通过不断的比较和调节,PLL能够使得VCO的输出信号与输入信号的频率、相位和幅度保持同步。

PLL的设计:1.相位比较器的设计:相位比较器的作用是将输入信号与参考信号进行比较,产生误差信号。

常用的相位比较器有边沿触发相位比较器、脉冲控制相位比较器、基于锁相环的数字相位比较器等。

2.低通滤波器的设计:低通滤波器的作用是对误差信号进行滤波,去除高频噪声,得到一个平均值。

常用的滤波器有RC低通滤波器、积分器等。

3.VCO的设计:VCO的作用是根据控制电压的大小产生相应频率的输出信号。

常用的VCO有环形振荡器、LC振荡器、数字控制振荡器等。

应用领域:1.通信系统:PLL被广泛应用于通信系统中,用于频率合成器、时钟恢复、相位调制等。

2.电视接收机:PLL可以用于电视接收机的频率合成,实现抗干扰和频率稳定。

3.射频标准源:PLL可用于射频标准源的频率合成,提供稳定的射频信号。

4.数字时钟:PLL可以用于数字时钟的频率合成,保证时钟精准度和稳定性。

5.数据传输:PLL可以用于数据传输中的时钟恢复和相位同步,提高传输速率和可靠性。

总结:PLL是一种广泛应用的电子电路,能够将输入信号与参考信号同步,实现频率、相位和幅度的调节。

其基本原理是通过相位比较器、低通滤波器和VCO的配合工作来实现。

PLL锁相环时钟设定

PLL锁相环时钟设定PLL锁相环时钟设定未配置锁相环时(OSCCLK_PLLSEL=0):总线频率=外部晶振频率(OSCCLK)/2配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2时钟频率计算⽅法Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1)Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=FvcoFbus=Fpll/2CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。

锁相环从设定到稳定需要时间,故期间应加⼏条空语句。

例程:void CLK_Init(void) {CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许//频率设定80M时SYNR = 0xc0 | 0x09;REFDV = 0x80 | 0x01;POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop);while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟}PWM模块PWME:PWM允许寄存器,置1时允许输出。

PWMPOL:极性寄存器。

置1时⾸先输出⾼电平。

2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源PWMCAE:居中对齐允许寄存器,只有当通道输出禁⽌时才能设置此寄存器置1时为居中对齐,置0时左对齐PWMSCLA:⽐例因⼦寄存器A;⽤于提供clock SA的⽐例因⼦Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时⽐例因⼦默认为256. CLOCKSB 计算⽅法类似,寄存器为PWMSCLB。

adisimpll锁相环设计过程

adisimpll锁相环设计过程锁相环(Phase-Locked Loop,PLL)是一种常用于时钟和信号恢复的电子电路。

它可以将输入信号的频率、相位和幅度与参考信号进行比较,然后通过调整其内部振荡器的频率和相位来保持与参考信号的同步。

在现代电子系统中,锁相环已成为许多应用的核心部件,例如通信系统、数据转换和数字信号处理等。

锁相环的设计过程通常包括以下几个主要步骤:1.确定锁相环的规格要求:首先需要确定系统的特定需求,包括输入和输出信号的频率范围、带宽、相位噪声要求以及抖动限制等。

这些规格要求将直接影响锁相环的设计参数和性能。

2.选择合适的锁相环架构:根据系统的特定需求,选择适合的锁相环架构。

常见的锁相环架构包括基于电压控制振荡器(Voltage-Controlled Oscillator,VCO)的基本锁相环、带自由运行振荡器(Free-Running Oscillator)的环-环(Ring-Oscillator)锁相环和数字控制振荡器(Digital-Controlled Oscillator,DCO)的混合锁相环等。

3.设计相位频率检测器:锁相环中的相位频率检测器(Phase-Frequency Detector,PFD)用于比较参考信号和反馈信号的相位和频率差异,并将其转化为控制信号。

常见的PFD电路包括EXOR门和带有多频偏的PFD等。

4.设计环路滤波器:设计环路滤波器用于平稳化锁相环的控制信号。

环路滤波器通常采用低通滤波器结构,能够滤除高频噪声和不稳定性。

5.设计振荡器:根据系统的频率范围和性能要求,设计合适的振荡器。

常见的VCO设计包括压控晶体振荡器(Voltage-Controlled Crystal Oscillator,VCXO)和频率可调振荡器(Voltage-Controlled Oscillator,VCO)。

6.设计控制电路:根据锁相环的设计需求,设计合适的控制电路。

LMK双回路PLL低噪音时钟抖动消除方案

LMK:双回路PLL低噪音时钟抖动消除方案LMK04800:双回路PLL低噪音时钟抖动消除方案NS公司的LMK04800系列是双回路PLL的低噪音时钟抖动消除器,具有超低的RMS抖动性能:12kHz~20MHz为111fs RMS,100Hz~20MHz为123fs RMS,工作电压3.15V~3.45V,时钟速率高达1536 MHz,可以满足新一代系统所需的要求,主要用在数据转换器时钟、无线基础设备、网络、SONET/SDH、DSLAM、医疗、视频以及测试测量设备等。

该LMK04800系列是业界最高性能的时钟调节器,具有优越的时钟抖动清除、生成和分配性能,并具有其它先进功能,以满足下一代系统时钟调整的要求。

这种双循环PLLatinum™架构,可以采用低噪声VCXO 模块,提供111fs rms抖动(12kHz至20MHz)或者,采用低成本的外部晶体和变容二极管,提供次200fs rms抖动(12kHz至20MHz)。

这种双循环结构包括两个高性能锁相环(PLL)电路,一个低噪声晶体振荡器电路,以及高性能的电压控制振荡器(VCO),第一个锁相环(PLL1)提供了低噪声抖动清除器的功能,而第二个锁相环(PLL2的)执行时钟产生。

PLL1可配置成与外部VCXO模块工作,或者与具有外部可调晶体和变容二极管的集成晶体振荡器工作。

当被用于很窄的环路带宽时,PLL1使用VCXO模块,或可调晶体的优异相位噪声(偏移低于50千赫),以清理输入时钟。

PLL1的输出作为PLL2的清除输入参考,以锁定集成的VCO。

PLL2的环路带宽可以进行优化,以清除远出相位噪声(偏移50千赫以上),集成的VCO优于VCXO模块,或PLL1使用的可调晶体。

图1 LMK0480x 详细方框图LMK04800主要特性•超低RMS抖动性能- 111 fs RMS抖动(12 kHz 至20 MHz)- 123 fs RMS抖动(100 Hz至20 MHz)•双回路PLLatinum PLL架构- PLL1•集成的低噪声晶体振荡器电路•输入时钟丢失时为保持模式- 自动或手动触发/恢复• 正常[1 Hz]锁相环底噪声-227 dBc/Hz•最高相探测器率155兆赫• OSCin频率倍增•集成低噪声压控振荡器• 2个Los 冗余输入时钟- 自动和手动切换模式• 50%占空比输出分离,1至1045(奇偶)• LVPECL,LVDS或LVCMOS的可编程输出•精密数字延时,固定或动态调整• 25 ps步模拟延时控制。

verilog中时钟校准的原理

verilog中时钟校准的原理

时钟校准是指将设计中的时钟与外部时钟进行同步,以保证电路的正常运行。

在Verilog中,时钟校准的原理是通过使用时钟锁相环(Clock Phase-Locked Loop,PLL)或者时钟数据恢复器(Clock Data Recovery,CDR)来实现的。

时钟锁相环是一种反馈控制系统,它可以自动调整输出时钟的相位和频率,使其与输入时钟保持同步。

PLL的基本原理是通过反馈控制,将输出时钟的相位和频率与输入时钟保持一致。

PLL一般由相位频率检测器(Phase Frequency Detector,PFD)、环形计数器(Loop Filter)、振荡器(VCO)和分频器(Divider)等组成。

具体操作时,输入时钟经过PFD与反馈时钟进行相位频率对比,得到一个差值信号。

然后,这个差值信号经过环形计数器进行滤波处理,并驱动振荡器调整输出时钟的相位和频率。

最后,通过分频器将输出时钟的频率分频得到所需的稳定时钟。

时钟数据恢复器是一种通过采样和重建输入时钟信号的方法来恢复时钟的技术。

在Verilog中,CDR可以通过采样输入时钟信号并得到采样信号的边沿,然后通过边沿对齐和时钟多倍帧间滤波等技术来重建时钟信号。

总而言之,时钟校准的原理在Verilog中主要通过使用PLL或CDR技术来实现,以确保设计中的时钟与外部时钟同步,并保证电路的正常运行。

一种基于 PLL 的 CBR 业务时钟恢复算法与方案

一种基于 PLL 的 CBR 业务时钟恢复算法与方案

杨震;胡家骏

【期刊名称】《上海交通大学学报》

【年(卷),期】1997(31)5

【摘要】提出了一种基于PLL的时钟恢复新方案.该方案可以明显地降低由于信元延时抖动而造成的CBR业务时钟的抖动和漂移。

【总页数】4页(P11-14)

【关键词】异步转移模式;恒定比特率业务;时钟恢复;ATM网

【作者】杨震;胡家骏

【作者单位】"区域光纤通信网与新型光通信系统"国家重点实验室;上海交通大学光纤技术研究所

【正文语种】中文

【中图分类】TN913.24

【相关文献】

1.一种基于差分技术的CBR业务时钟自适应恢复方案 [J], 杨震;胡家骏

2.一种基于差分技术的CBR业务时钟自适应恢复算法与方案 [J], 杨震;胡有骏

3.一种基于PLL的CBR业务时钟恢复方案 [J], 杨震;胡家骏

4.以太网传输中CBR业务时钟恢复的技术研究 [J], 牛增新

5.电路仿真业务中DCR时钟恢复算法的VLSI实现 [J], 冯肖雄; 邱超

因版权原因,仅展示原文概要,查看原文内容请购买。

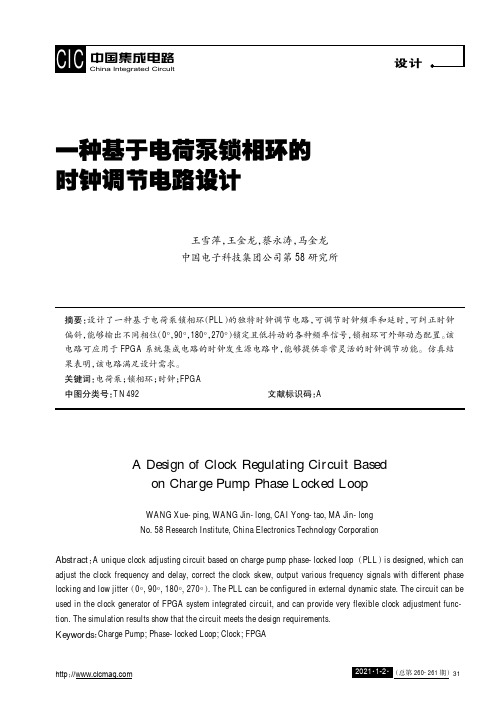

一种基于电荷泵锁相环的时钟调节电路设计

一种基于电荷泵锁相环的时钟调节电路设计王雪萍,王金龙,蔡永涛,马金龙中国电子科技集团公司第58研究所摘要:设计了一种基于电荷泵锁相环(PLL)的独特时钟调节电路,可调节时钟频率和延时,可纠正时钟偏斜,能够输出不同相位(0°,90°,180°,270°)锁定且低抖动的各种频率信号,锁相环可外部动态配置。

该电路可应用于FPGA系统集成电路的时钟发生源电路中,能够提供非常灵活的时钟调节功能。

仿真结果表明,该电路满足设计需求。

关键词:电荷泵;锁相环;时钟;FPGA中图分类号:TN492文献标识码:AA Design of Clock Regulating Circuit Basedon Charge Pump Phase Locked LoopWANG Xue-ping,WANG Jin-long,CAI Yong-tao,MA Jin-longNo.58Research Institute,China Electronics Technology CorporationAbstract:A unique clock adjusting circuit based on charge pump phase-locked loop(PLL)is designed,which can adjust the clock frequency and delay,correct the clock skew,output various frequency signals with different phase locking and low jitter(0°,90°,180°,270°).The PLL can be configured in external dynamic state.The circuit can be used in the clock generator of FPGA system integrated circuit,and can provide very flexible clock adjustment func-tion.The simulation results show that the circuit meets the design requirements.Keywords:Charge Pump;Phase-locked Loop;Clock;FPGA图1时钟调节电路结构1引言锁相环(Phase-locked Loop ,PLL )是FPGA 类系统集成电路中重要的时钟资源,随着FPGA 在通信、自动化控制、航空航天等领域应用越来越广泛[1-2],PLL 电路设计也越来越关键。

一种低抖动快锁定的时钟数据恢复电路设计

一种低抖动快锁定的时钟数据恢复电路设计胡腾飞;方毅;黄鲁【摘要】采用TSMC 0.13μm CMOS工艺,设计了一种基于延迟锁相环(DLL)与锁相环(PLL)混合技术的时钟数据恢复(CDR)电路.它结合延迟锁相环电路追踪速度快和锁相环电路抖动抑制能力强的特点,与通常基于二阶锁相环结构的电路相比,在输出抖动相同的情况下,具有更快的锁定时间.仿真结果表明该电路可以成功恢复出480 MHz伪随机数据,数据峰峰值抖动约为39 ps,即相对抖动约为0.02 UI,锁定时间约为793 ns,较二阶锁相环结构的电路提升了32%.芯片核心电路面积为0.15 mm2,1.2 V电源供电下消耗功耗6.9 mW.【期刊名称】《微型机与应用》【年(卷),期】2018(037)003【总页数】5页(P113-116,121)【关键词】锁相环;延迟锁相换;时钟数据恢复【作者】胡腾飞;方毅;黄鲁【作者单位】中国科学技术大学电子科学与技术系,安徽合肥230027;中国科学技术大学信息科学技术实验中心,安徽合肥230027;中国科学技术大学电子科学与技术系,安徽合肥230027【正文语种】中文【中图分类】TN430 引言时钟数据恢复电路(CDR)广泛应用于各类串行通信中,如微波通信[1]、光纤通信[2]、以太网等。

时钟数据恢复电路主要通过调整时钟与数据的相对相位关系,从带有噪声的信号中恢复出“干净”的时钟与信号,通常要求电路具有恢复数据抖动小、锁定时间短、抖动尖峰低等性能。

基于锁相环与延迟锁相环混合技术[3]的时钟数据恢复电路相对于传统基于二阶锁相环结构的电路,可以有效解决抖动抑制与锁定时间之间的矛盾,实现零抖动尖峰。

它利用延迟锁相环(DLL)调节输入数据相位实现快速锁定;通过锁相环(PLL)实现小的传输带宽,降低恢复时钟与数据的抖动;并且闭环传输函数无零点,实现零抖动尖峰。

1 时钟数据恢复电路的整体结构基于传统二阶锁相环技术的时钟数据恢复电路的结构如图1所示,主要由鉴相器(PD)、电荷泵(CP)、低通滤波器(LPF)、压控振荡器(VCO)四个模块组成。

通信系统中的时钟提取电路 -回复

通信系统中的时钟提取电路-回复通信系统中的时钟提取电路由于其重要性,是现代通信系统中不可或缺的部分。

时钟提取电路能够从复杂的数字信号中提取出恢复时钟信号,在信号的传输和接收过程中起到关键作用。

本文将从时钟提取电路的重要性、原理、设计和应用等方面进行详细介绍。

一、时钟提取电路的重要性在通信系统传输信号的过程中,为了保证数据的正确接收和处理,需要有一个统一的时间参照。

而时钟信号就是为了提供这样一个统一的时间参照,使得发送端和接收端的时钟保持同步。

时钟提取电路的作用就是从传输信号中提取出时钟信号,确保传输的数据能够正确地被接收和处理。

二、时钟提取电路的原理时钟提取电路主要基于相位锁环(PLL)的原理来工作。

相位锁环是一种电路,通过调整自身的频率和相位与输入信号进行比较,最终将输出的时钟信号与输入信号的相位同步。

具体来说,相位锁环包括一个比较器、一个环路滤波器、一个数字控制器和一个振荡器。

1. 比较器:将输入信号和输出时钟信号进行相位比较,产生一个误差信号。

2. 环路滤波器:用于过滤误差信号,使其成为控制器能够处理的信号。

3. 数字控制器:根据环路滤波器输出的信号,控制振荡器的频率和相位,使得输出的时钟信号与输入信号相位同步。

4. 振荡器:产生时钟信号,并根据数字控制器的指令进行频率和相位的调整。

通过这样的反馈调整过程,相位锁环能够不断调整输出的时钟信号,使其与输入信号的相位保持同步。

三、时钟提取电路的设计时钟提取电路的设计需要考虑到多方面的因素,包括传输信号的特点、误码率的要求、带宽和功耗等。

1. 传输信号的特点:不同的传输信号具有不同的特点,例如有时钟信息的时分多路复用(SDH)、同步以太网(SyncE)等,需要根据不同的信号特点设计相应的时钟提取电路。

2. 误码率的要求:通信系统中有严格的误码率要求,时钟提取电路需要在保证误码率性能的同时,尽可能地减小功耗和带宽占用。

3. 带宽和功耗:时钟提取电路需要在一定的带宽和功耗要求下工作,因此设计中需要考虑如何有效利用带宽和降低功耗。

高速数字信号传输设计中的时钟数据恢复技术

高速数字信号传输设计中的时钟数据恢复技术在高速数字信号传输设计中,时钟数据恢复技术起着至关重要的作用。

当信号传输速度达到一定水平时,准确、稳定的时钟信号是保证数据传输质量的关键。

在本文中,我们将深入探讨高速数字信号传输设计中的时钟数据恢复技术。

首先,让我们了解时钟数据恢复技术的基本原理。

在数字通信中,发送端和接收端的时钟频率可能会产生偏差,导致数据传输时钟信号不同步,从而影响到数据的准确性和稳定性。

时钟数据恢复技术的主要目的就是通过在接收端重新生成一个稳定的时钟信号,以确保正确采样数据。

这种技术在高速传输中尤为重要,因为在高速传输中时钟偏差会更加明显。

时钟数据恢复技术主要有两种方法:一种是基于信号的恢复,另一种是基于时钟的恢复。

基于信号的恢复方法通过分析接收到的数据信号来提取时钟信息,然后根据这些信息生成本地时钟信号。

这种方法适用于信号质量较好的情况下,但在高噪声环境下可能会受到影响。

而基于时钟的恢复方法则是通过在数据中嵌入时钟信息,然后在接收端利用这些信息来恢复时钟信号。

这种方法对信号质量要求不高,但可能会增加数据传输的复杂性。

在实际应用中,常用的时钟数据恢复技术包括Costas环、PLL(锁相环)和CDR(时钟数据恢复器)。

Costas环是一种经典的时钟数据恢复技术,通过对接收信号的相位进行解调,提取出时钟信息并进行时钟恢复。

PLL则是一种常用的时钟同步技术,通过对输入信号进行频率和相位的比较,使得输出时钟信号与输入信号同步。

而CDR则是一种更加先进的技术,通过对接收到的数据进行采样和比较,自动调整时钟频率和相位来实现时钟数据恢复。

在设计高速数字信号传输系统时,选择合适的时钟数据恢复技术至关重要。

不同的应用场景可能需要不同的技术方案,例如对于长距离传输和高噪声环境下,CDR技术可能更适合;而对于简单的短距禁止传输,PLL可能就足够了。

在选择时钟数据恢复技术时,还需要考虑到系统的复杂度、成本和功耗等因素,以寻求最佳的平衡点。

抖动分析使用的时钟恢复方法-TECHNICALBRIEF

技术简介抖动分析使用的时钟恢复方法Michael Schnecker抖动测量是串行数据系统分析和认证中的关键要素。

由于当前许多设计中的符号速率通常要超过2.5 Gb/s,因此准确地检定抖动正变得更加重要。

参考时钟是所有抖动测量的核心,必须针对这个参考时钟测量符号定时。

在理想情况下,会有这样一个时钟;但在实践中,通常没有这样的时钟。

因此,必须从被测信号中恢复参考时钟。

恢复这一时钟使用的方法对测得的抖动有着直接影响。

串行数据标准如PCI Express™和串行ATA解决了这个问题,它们不仅定义了抖动,还定义了推导测量结果使用的具体时钟恢复方法。

选择的时钟恢复方法影响着追踪能力及可以测量的抖动总量。

抖动测量系统中灵活的时钟恢复不仅有助于满足特定标准要求,还提供了强大的分析工具,可以预测实际接收机的性能。

时钟恢复图1是串行数据接收机的基本方框图。

接收机检测数据流的跳变,在本文中假设为NRZ。

时钟恢复方框通过使用锁相环(PLL)把时钟信号锁相到数据跳变,从数据边沿中导出采样时钟。

PLL操作生成一个时钟,其抖动与数据的抖动相同,以支持位速率的长期变化,但它允许传送短期变化。

恢复的采样时钟上出现的抖动速率由PLL反馈环路的低通滤波器确定。

这一设计允许接收机不受长时间内平均位速率相对较大变化的影响。

检测器使用恢复的时钟,定位符号边界,在符号的标称中心(单位间隔或UI)对电压采样,确定存在电平1或0。

通过时钟恢复电路传送的抖动包含随机成分和确定性成分。

发射机抖动使用锁相环恢复定时参考,分析发射机定时抖动。

在这方面,抖动测量系统的行为与串行数据接收机类似。

数据流与恢复的时钟之间的相位误差在抖动分析函数中分析。

相位误差代表着用来调节VCO频率,以追踪被测信号符号速率的控制信号。

这种相位误差实际上是参考时钟和数据跳变之间的抖动。

图1. 串行数据接收机方框图。

时钟恢复函数生成一个采样时钟,追踪数据流中的抖动。

[图示内容:]serial data signal (NRZ): 串行数据信号(NRZ)detector: 检测器de-serializer: 解串行器parallel data out: 并行数据输出phase detector: 相位检测器low pass filter: 低通滤波器图2. 抖动测量系统。

PLL时钟解决方案实现精确系统同步

九 款 产 品 ,均 具 有 业 界 一 流 的 长 期 时 域 抖 动 性

能 和 1 0 MHz 率 优 异 的 一6 BcHz 件 域 噪 频 1 3d / 元 声 ,可 弥 补 在 整 合 1 至 2 Hz 率 时 的04 2 Hz 0M 频 . 皮 秒 ( s均 方 根 ( p) RM S 相 位 抖 动 ,使 整 个 系 统 ) 时 钟树具 有更大 的时序 裕量 。这些 元件 创造 了 亚 皮 秒 抖 动 质 量 的 时 钟 ,可 以 实 现 1 0 MHz O 、

能 方面 领 先 业 界 。

安 森 美 半 导 体 的 时 间 抖 动 比 竞 频 率技术产 品 。这 些产 品可 以在 系统 中提 供犹

争 对 手 d 5 % ,令 系统 设 计 更 简 易 , ,0

如 心 脏 有 规 律 的 跳 动 的 准 确 频 率 , 在 实 现 更 高

并 消 除 时 间 误 差 。 此 外 , 安 森 美 半 性 能 的 同 时 ,简 化 系 统 的 复 杂 程 度 ,实 现 精 确 导体在 全球 时钟支持 ( C E L)市场排 的 系统 同步 。”

名 第一 。

安 森 美 半 导 体 的 时 钟 树 解 决 方 案 包 括 时 钟

基础 电子 l 0 8 1 2 0 .2

I 产业聚焦 I d s yWa c ut th I n r

产 生 和 时 钟 支 持 及 分 配 两 大 部 分 。 前 者 包 括 高 性 能 时 钟 、时 钟 模 块 、 灵 活 的 C 0S 编 程 时 M 可 钟 ;后 者 包 括 时 钟 分 配 、 分 立 式P L 件 、时 钟 L器 支 持 逻 辑 。 其 中 ,时 钟 产 生 部 分 中 基 于 P L L 的

以太网物理层芯片时钟同步PLL的设计方案

以太网物理层芯片时钟同步PLL的设计方案在以太网中,物理层芯片(Physical Layer Interface Devices,PHY)是将各网元连接到物理介质上的关键部件。

负责完成互连参考模型(OSI)第I层中的功能,即为链路层实体之间进行位传输提供物理连接所需的机械、电气、光电转换和规程手段。

其功能包括建立、维护和拆除物理电路,实现物理层比特(bit)流的透明传输等。

物理层包括4个功能层和两个上层接口。

两个上层接口为物理介质无关层接口(MII)和物理介质相关层接口(MDI),在MII的上层是逻辑数据链路层(DLL),而MDI的下层则直接与传输介质相连。

而这些子层的正常工作都离不开一个稳定精确的时钟同步信号。

PLL在物理层芯片的时钟同步应用中,要求其输出时钟带宽覆盖范围广,电压控制频率线性度好,频谱纯度高。

在PLL设计过程中,VCO是最为关键的设计环节,其性能将直接决定PLL的设计工作质量。

近年来,VCO相位噪声得到越来越深入的研究,各种低噪声VCO结构不断涌现,文献中提到的交叉耦合电流饥饿型VCO便是其中一种。

电流饥饿是指电路单元的电流受到电流源的钳制而不能达到其应有的最大值。

本文在其基础上采用了一种有效控制电压变换电路,保证原有电路优点的同时扩展了线性度,提高抗噪声能力,有效降低了相位噪声。

1 VCO延迟单元工作原理图1所示为电流饥饿型VCO中的单级结构。

PNP管M1和NPN管M2是延迟单元的组成部分,Ictrl是用于控制电容的放电电流Id1和充电电流Id2,他们是构成环形振荡器的每一级。

Ictrl控制着流过M1管和M2管的电流,所以由M1管和M2管构成的延迟单元处于电流饥饿状态。

每一级迟单元处于电流饥饿状态。

每一级的电流都由同一个电流源所镜像,所以Id1=Id2同时电流大小由输入控制电流Ictrl控制。

反相延迟主要是2个原因:一个是RC的充电时间;另一个是反相器的预置电压。

而这2个延迟时间的产生都是可以通过调整宽长比来实现。

单片机中时钟系统设计与优化方案

单片机中时钟系统设计与优化方案摘要:时钟系统是单片机中的重要组成部分,对单片机的正常工作起着至关重要的作用。

本文将介绍单片机中时钟系统的设计原理、时钟系统的分类、常用的时钟源以及时钟系统的优化方案。

一、设计原理时钟系统是单片机中用于计时和同步各个模块工作的重要部分。

单片机中的时钟系统通常采用晶振和时钟电路来提供精确的时钟信号。

晶振通过产生稳定的振荡信号来驱动时钟电路工作。

时钟电路则通过将晶振振荡信号进行二次处理,以获取最终的时钟信号。

二、时钟系统的分类根据时钟源的不同,单片机中的时钟系统可以分为外部时钟源和内部时钟源。

1. 外部时钟源外部时钟源通常采用晶振作为时钟信号的参考源。

晶振具有稳定性好、频率准确的特点,能够为单片机提供可靠的时钟信号。

根据振荡频率的不同,晶振可以分为常用的4MHz、8MHz、12MHz等。

外部时钟源的优点是精度高,但需要外部接口和占用额外的单片机引脚。

2. 内部时钟源内部时钟源通常由单片机内部的时钟电路产生,不需要外部振荡器。

内部时钟源的优点是结构简单、占用引脚少,适用于资源有限的应用。

然而,由于工艺制程的限制,内部时钟源的精度较低,频率相对不稳定。

三、常用的时钟源根据单片机的类型和应用需求的不同,常用的时钟源主要包括晶振、RC振荡器和内部高频振荡器。

1. 晶振晶振是最常用的外部时钟源,具有稳定性好、精度高的优点。

在设计时,需要根据单片机的工作频率和性能要求选择适合的晶振频率。

晶振的选择应考虑到单片机和外设的时钟要求。

2. RC振荡器RC振荡器是一种使用电阻和电容构成的振荡电路,由于结构简单成本低,被广泛用于一些低成本和低功耗的应用。

然而,由于电阻和电容制造工艺的限制,RC振荡器相对于晶振的稳定性和精度较差。

3. 内部高频振荡器内部高频振荡器是一种由单片机内部电路产生的时钟源,不需要外部元件。

内部高频振荡器具有结构简单、占用少量资源的优点,适用于一些对精确时钟要求不高的应用。

超高速数码信号传输中的时钟恢复技术研究

超高速数码信号传输中的时钟恢复技术研究引言随着数字通信技术的进步和智能设备的不断出现,对于高速数据传输的需求也越来越大。

超高速数码信号传输中的时钟恢复技术是实现高速数据传输的关键技术之一。

本文将从时钟恢复技术的基本概念、原理和分类,时钟恢复技术在超高速数码信号传输中的应用以及研究进展等方面进行阐述和分析。

第一章时钟恢复技术的基本概念、原理和分类1.1 什么是时钟恢复技术时钟恢复技术是将接收机收到的信息进行采样,并根据采样的结果恢复出原信号的时钟信息,以保证正确的解析数据。

由于信号的传输存在着很多的不确定性,如信号失真、抖动、滞后……等,因此,时钟恢复技术在实际通信中显得十分重要,也是一项非常复杂的技术。

1.2 时钟恢复技术的原理对于高速信号,在信号传输过程中,由于存在着噪声、失真、抖动等因素,经过传输的信号时钟可能与原信号时钟有一定偏移,采样时钟与信号时钟之间也有可能存在较大的相位偏移。

因此,正确恢复原信号时钟信息是非常关键的。

时钟恢复技术的实现原理主要有两种方法:基于锁相环(PLL)的时钟恢复和基于延迟锁定环(DLL)的时钟恢复。

基于PLL的时钟恢复主要利用自适应滤波器将误差信号反馈到VCO来调整与发射时钟的相位,从而实现时钟的恢复。

而基于DLL的时钟恢复则是将接收到的信号和本地时钟进行延时,并将两路信号进行比较,通过调节延时量来实现时钟的恢复。

两种方式具有不同的优缺点,具体的应用需根据具体情况选择。

1.3 时钟恢复技术的分类时钟恢复技术根据采样时钟和数据时钟的关系,一般可分为三类:边沿对齐、符号同步和自适应时钟恢复。

边沿对齐主要是将参考时钟与接收到的时钟进行相位对齐,当接收到的时钟存在相位偏移,需要根据已知的速率调整时钟相位。

符号同步是指通过接收机对已传输数据的边界进行识别,并根据此对时钟相位进行调节。

自适应时钟恢复则是通过自适应算法将参考时钟与接收到的时钟进行相位同步。

第二章时钟恢复技术在超高速数码信号传输中的应用时钟恢复技术在高速通信中广泛应用于多种领域,特别是在超高速网络、高速存储系统、视频传输等领域中则有着广泛的应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

不管是放到测试设置中,还是作为被测设备的一部分,时钟恢复都在进行准确的测试测量时发挥着重要作用。

由于大多数千兆位通信系统都是同步系统,因此系统内部的数据都使用公共时钟定时。

不管是沿着几英寸的电路板传送,还是经过光纤横跨大陆,数据与其定时输入的时钟之间的关系都可能会被打乱。

通过直接从数据中提取时钟,可以在接收机正确实现信号再生。

必须指出的是,接收机通常会改善输入的数据信号,然后再继续传送。

接收机中的判定电路对数据再定时,使波形变方。

这一过程依赖于与输入数据同步的时钟信号。

接收机内部的时钟恢复功能实现了这一目标,前提是再定时时钟要以相同的方式、相同的时间移动。

基于PLL的时钟恢复

可以通过不同架构实现时钟恢复,测量设备中最常用的是基于锁相环(PLL)的方法。

根据在数据中看到的跳变,使用恢复电路导出与输入数据同步的时钟,这取决于看到数据中的跳变。

对拥有多串完全相同位的数据段,PLL必须保持锁定。

环路增益对环路带宽的影响最明显,环路滤波器内部的任何滤波一般都会产生次生效应。

应该指出的是,输入数据的跳变密度会影响进入环路的能量,进而影响环路的特性。

因此,一致性测试中的环路带宽会视选择的码型的跳变密度而变化。

系统转函在输入信号的相位调制上执行低通滤波操作,错误响应转函则执行高通滤波功能。

在未能追踪带宽以外的相位调制时,环路会追踪环路带宽以内的输入相位调制。

这样,环路就可以追踪低频抖动,而忽略PLL环路带宽以外的高频抖动。

衡量PLL抖动追踪特性的指标之一是环路带宽(LBW),通常在“抖动输入/抖动输出”转函为-3dB的点上测得。

但这并不是确定环路的唯一方式。

宽LBW改善了抖动容限,窄LWB则会从被恢复的时钟中去掉更多的抖动,这有利于下游的同步器,但会降低抖动容限。

尽管宽LBW似乎是理想选择,但通常还要考虑成本和技术。

宽LBW还会带来更多的噪声或随机抖动。

目前测量中使用的LBW一般在1~10MHz的范围内。

时钟恢复的输入和输出

必须指出测量中是怎样使用时钟恢复的,哪些地方会发生错误。

例如,在发射机测试一侧,要求时钟恢复的主要原因通常有两个:没有提供作为测试设备触发的时钟信号,或者标准要求使用特定的LBW进行抖动测量(参见图1中的a部分)。

后一种情况的目的,是用系统接收机(如BERTScope BSA系列)包含时钟恢复来追踪部分输入抖动,这样发射机测试应该只涉及接收机没有追踪的高频抖动(参见图1)。

由此可见,对抖动成分接近时钟恢复LBW的被测信号,LBW设置不正确可能会导致抖动测量不准确。

有时标准会暗示要在测试中使用时钟恢复,例如提到“黄金PLL”,或指定要“在使用以20dB/decade将抖动衰减到(比特率/1,667)频率以下的单极、高通、频率加权函数后”测量抖动。

扩频时钟(SSC)把时钟能量(和数据)扩散在0.5%的频段上,降低了频谱给定频率上的平均功率。

这可以帮助产品满足放射辐射和传导辐射的法规要求。

为成功地追踪SSC,接收机必须能够追踪调制(包括其谐波),以避免眼图闭合。

如果环路响应未能充分追踪SSC,或在时钟和数据路径之间出现错误的延迟,那么测试眼图就会模糊闭合。

不正确的峰值(即LBW附近区域,这里的时钟恢复设备抖动输出可能会大于抖动输入)可能会放大被测的抖动数量。

此外,测试设备中相对于输入数据信号的触发延迟可能会导致测得的抖动数量不正确。

例如,测量系统中的固定延迟可能会导致测得额外的明显抖动。

增加的抖动幅度取决于相对于延迟量的抖动频率。

在接收机端,时钟恢复可能会出现在被测器件中,也可能作为测试设备校准程序的一部分出现。

在被测器件中,时钟恢复频频出现,在测试中通常使用压力和正弦曲线抖动实现(参见图1中的b部分)。

在正弦曲线抖动中,测试一般使用模板,这会在较低的调制频率上应用较多的抖动,或在较高频率上应用较少的抖动。

其中的问题包括在接收机中使用设计不当的LBW,这会导致抖动容限模板失效。

追踪响应的斜率不正确可能会使追踪SSC的准确性不够,导致测试眼图模糊闭合,并产发生误码。

时钟恢复被频繁用于测试设备设置及接收机抖动容限或受压的眼图信号校准(参见图1中的c部分)。

正弦曲线抖动通常设置成频率高于校准过程中时钟恢复的LBW。

但是,LBW不正确可能会导致压力量设置错误,进而造成被测器件压力不足或过大,前者会提高客户拒收的可能性,后者则会影响良率。

从所有这些情况中,很容易得出这样的结论,即LBW设置非常关键,对测量中观察到的抖动有着明显影响。

改变环路带宽可以显示抖动频谱。

以非常窄的LBW进行测试,可以显示被测发射机产生的所有抖动。

而使用非常宽的LBW进行测试,则只会显示发射机产生的、预定系统接收机用自己的PLL不能滤掉的抖动。

一般来说,一致性测试中会指定后一种时钟恢复方式。

系统设计人员主要关心超出接收机追踪能力的抖动。

分布式时钟方案

并不是所有系统都从数据流中导出时序。

部分系统如PCI Express和全缓冲双直列内存模块(DIMM),它们使用发送到通信链路每一端的分布式时钟来为数据定时。

发送端和接收端使用PLL来生成参考时钟。

一般来说,分布式参考时钟将有一定数量的抖动,如来自原始晶体的相位噪声。

它也可能会有SSC。

时钟

在每个IC内再生,并用来为发送功能和接收功能提供时钟。

每个PLL将有一个环路响应,如果其作用完全相同,那么一个PLL上的抖动完全可以由另一个PLL追踪,也就是说,接收机看不到任何净效应。

但实际情况往往要更加复杂。

即使对采用相同设计、相同制造工艺及相同生产批次制造的器件来说,几乎也不可能获得完全相同的环路响应。

由于确保IC之间及IC内部的路径长度一样也很困难,因此在接收机抖动中还会出现同等的触发延迟,导致出现更多的抖动。

嵌入式时钟方案

把时钟嵌入到数据中是保证在接收机准确恢复发射的数据流的一种常用方式。

但一旦实现,就会产生一个问题,即系统以一种时钟速率运行,而输入的码流会以略微不同的速率运行。

必须以某种方式重新为数据输入时钟,以便与接收端系统相匹配。

在某些结构中,特别是在SONET/SDH中,设计人员做的一项重要工作是使系统中的所有时钟尽可能地匹配,这是通过基于全球定位系统(GPS)来分配高度准确的系统时钟,或者基于铷(Rubidium)或类似标准来分配本地时钟而实现的。

其它结构则承受了时钟速率差异性更大的特点,以此来降低成本和复杂性。

在任何情况下,系统最终都必须处理所有的不匹配,这一般要等到差异超过1个比特或1个帧,然后插入或删除比特或字符。

通常,系统协议会插入多个字符,称为填充字,这些字符在接收机上会被舍弃掉。

还有的时候,如果需要的话,协议会允许接收机插入自己的字符,而不会打乱数据的含义。

增加或删除这些字符可能会极大地影响测试。

基于协议的测试设备通常被设置成处理插入的或删除的字符,同时仍能识别底层信息。

但是,物理层测试设备有时更加受限,它要求码型完全符合没有变化的已知重复序列。

多出或漏掉码会导致设备认为发生了错误。

在系统管理基线漂移时也会发生数据码型变化,即系统会经过AC耦合和一长串完全相同的位,导致平均信号电压漂移,直到发生误码。

在这种情况下,协议方案对于每个有效字符通常有两个版本,并确定发送最能有效抗击任何基线漂移或运行不一致的版本。

接收机上的协议智能完全能够识别哪种版本是正确,但这也违反了某些测试设备对码型不变的要求。

某些测试设备可以进行参数测量,而无需重复码型。

这在检查物理层问题时非常有效,但不能处理协议错误。

此外,还有可能会漏掉清除后作为正确码重传的接收机误码,尽管这些码是有问题的。

通过使用环回测试,发送到接收机的信号被环回,成为发射机的输出。

但数据并不总是完全相同,因为时钟速率匹配错误会导致填充字变化,这可能会使测试设备混乱。

在这些情况下,一种解决方案是创建一个测试环境,其中发射机时钟域和接收机时钟域完全一样,从而无需进行域速率匹配。

许多使用仪器时钟恢复的方案可以用测试设备输出的准确速率创建一个时钟信号,然后再利用这个信号为环回测试生成一个测试信号。

随着时钟恢复在更多的系统和测试设置中日益普遍,必须考虑其对测量的影响。

许多外部影响可能会打乱数据和时钟源之间的关系。

通过了解这两者之间的关系,可以获得更实用、更准确的测量结果。