PADS功能使用技巧V0.3

PADS两个常用使用技巧

PADS两个常⽤使⽤技巧

虽然不是画板⼦得硬件⼯程师,但是很多时候也需要从PCB和原理图上⾯查看引脚。

本篇⽂章描述在使⽤PADS时两个⽐较常⽤的操作:

1、将PCB和原理图连接,同步显⽰

2、学会如何屏蔽多余的线,可以清晰的看到引脚或者⾛线等

⼀、连接PCB和原理图

如图点击⼯具栏PADS图标,弹出的串⼝可关闭,下⽅显⽰已连接,下⾯点击原理图或PCB试⼀下,OK,⼆者可以同步了。

⼆、屏蔽多余部分(Ctrl+Alt+C)

将⿏标点击在PCB图上,使⽤Ctrl+Alt+C,在弹出的对话框中选择需要屏蔽的部分,将 √ 去掉,点击应⽤-----OK!

功能实现⽅式

界⾯左右移动 Shift+⿏标滚轮。

PADS应用技巧

PADS应用技巧PADS是一款非常流行的PCB设计软件,被广泛应用于电子行业。

它具有功能强大、易于学习和使用的特点。

在使用PADS时,掌握一些技巧和窍门可以提高工作效率和设计质量。

下面是一些常用的PADS应用技巧:1.使用快捷键:熟悉并使用快捷键可以大大提高工作效率。

可以通过点击“帮助”菜单下的“快捷键参考表”来查看所有快捷键的列表,并根据自己的工作习惯进行个性化设置。

2.使用工具栏:PADS提供了丰富的工具栏,可以方便地访问各种功能。

可以根据需要自定义工具栏,将常用的工具添加到工具栏上,以便快速访问。

3.使用层设置:在进行布局和布线时,使用层设置可以选择显示或隐藏特定层。

通过点击“视图”菜单下的“层设置”选项可以打开层设置对话框,可以根据需要选择显示或隐藏一些层。

4.使用自动布局和布线工具:PADS提供了强大的自动布局和布线工具,可以帮助设计师快速完成复杂的布局和布线任务。

在进行自动布局和布线之前,可以通过设置一些参数来调整自动布局和布线的结果。

5.使用电气规则检查工具:PADS提供了电气规则检查工具,可以帮助设计师快速检查电路板设计中的错误和潜在问题。

在进行布局和布线之前,应该使用电气规则检查工具对电路进行检查,以确保设计的正确性。

6.使用信号完整性工具:PADS提供了信号完整性工具,可以帮助设计师在设计电路板时解决信号完整性问题,如时钟分配、信号回退等。

在进行布局和布线之前,可以使用信号完整性工具对布局和布线进行优化。

7.使用三维视图:PADS提供了三维视图功能,可以帮助设计师更好地理解电路板的外观和布局。

可以通过点击“视图”菜单下的“三维网架”选项来打开三维视图,可以通过鼠标控制视图的旋转、缩放和移动。

8. 使用导入和导出功能:PADS支持多种文件格式的导入和导出,如Gerber、DXF、PADS ASCII等。

可以通过点击“文件”菜单下的“导入”和“导出”选项来导入和导出文件,以便与其他CAD软件进行交互。

PADS快捷键和技巧大全

PADS快捷键和技巧大全PADS(PowerPCB Advanced Design System)是一款强大的电子设计自动化软件。

它具有丰富的功能和工具,使得电路设计师能够快速而准确地完成电路布局和布线工作。

在使用PADS进行设计时,掌握一些快捷键和技巧可以提高工作效率和准确性。

下面是一些常用的PADS快捷键和技巧,帮助您更好地使用该软件。

1.快捷键:- Ctrl + N:新建设计文件。

- Ctrl + O:打开设计文件。

- Ctrl + S:保存设计文件。

- Ctrl + Z:撤销上一步操作。

- Ctrl + Y:重做。

- Ctrl + C:复制选定的元素。

- Ctrl + V:粘贴元素。

- Ctrl + X:剪切选定的元素。

- Ctrl + A:全选。

- Ctrl + D:删除选定的元素。

- Ctrl + G:对选定元素进行分组。

- Ctrl + U:解除选定元素的分组。

2.利用网格:在设计过程中,利用网格可以使布局和布线更加整齐和对齐。

您可以使用快捷键“G”打开网格设置对话框。

在这里,您可以设置网格的间距和显示选项。

还可以使用快捷键“Ctrl + Shift + G”重新对齐元件。

3.使用箭头和空格键:在布线时,使用箭头键可以调整元件的位置。

使用上箭头键可以向上移动元件,使用右箭头键可以向右移动元件,以此类推。

另外,使用空格键可以旋转元件。

4.使用自动布局工具:PADS提供了一些自动布局工具,可以帮助您布局电路板。

在布线完成后,使用“Tools”菜单中的“AutoRouter”选项可以自动完成布线。

这样可以节省时间和精力,并确保更好的布线质量。

5.使用层功能:PADS支持多层设计。

您可以使用快捷键“L”切换不同的层。

使用“Tab”键可以切换显示层。

使用“+”和“-”键可以放大和缩小显示。

7.使用高级选项:PADS提供了一些高级选项,可以进一步优化设计。

例如,使用快捷键“A”可以添加阵列,使用快捷键“M”可以移动选定元件。

pads操作规范和技巧

本文档一:操良好的板厂、当然,1.1我们需产品,何画了导入网的孔径布局也再根据1.2 标注规不管我请标注请画出版本V1.0本文档主要介绍一:操作规范 良好的操作习惯,板厂、贴片厂的成不同的板子.1了解产品,设计我们需要了解我们产品,我们知道这何画了。

导入网表后,不要的孔径多少,不要布局也没有想象中再根据接口摆放模.2 标注规范,设标注规范:不管我们前期如何请标注出板子的尺请画出拼板图 创建第一介绍pads 操作规范习惯,能够极大的厂的成本。

的板子密度、层数都,设计规则,整体解我们画的产品,是知道这个板子有哪些,不要急于去布局,不要随意去设置想象中的复杂,先摆摆放模块电路,再调,设计规范 期如何去设置原点子的尺寸,标注前pads 操作内容建第一个版本作规范和使用技巧大的方便后期硬件层数都不一样,过,整体布局产品,是机顶盒、路有哪些网络,有哪去布局走线,我们看去设置孔径,最好不杂,先摆放结构件,路,再调整SOC 置原点,板子画完后标注前,设置精度到操作规范和杨启宝用技巧。

期硬件、软件调试样,过孔、BGA 、路由器、还是,有哪些重要的走我们看下是否有最好不要超过构件,再放置OC 位置。

走线时候画完后,务必原点精度到小数点后两规范和技巧 作者杨启宝(Daryl.yang 件调试,测试,也GA 大小都不一样、还是电话机等,要的走线。

积累的否有BGA,最小过3种。

SOC 器件,DDR 线时候优先走重要必原点标在板框左点后两位。

yang)试,也能够方便生不一样,但是设计机等,等我们下次积累的多了,新的,最小的线宽、线距DDR,再将模块电走重要的线,密集板框左下脚板边交时间2018.4.4方便生产,甚至节是设计思想是一样们下次再碰到类似,新的产品就知道、线距多少,最小模块电路相互分开,密集的数据总线板边交叉点。

甚至节省是一样。

到类似的就知道如,最小互分开,据总线。

可以把设计规方便后布局打证美观过孔尽对于接整体来二:使2.1 复制粘但是仍元器件制,可可以把制板要求直设计规范,对于双方便后期走线,也布局打开栅格。

PADS功能使用技巧V0.3

PADS功能使⽤技巧V0.3PADS功能使⽤技巧V0.3由于⽂档更新较为繁琐,故今后不再以PDF格式进⾏更新,此次为最后⼀次,有兴趣⼀起探讨PADS PCB设计的可加群号:34098324。

与之前版本有所区别的是,本次⽂档添加了PADS9.0的新功能,以往版本可能会较复杂的操作在该版本中会更简洁。

⼀、如何⾛蛇形线?蛇形线是布线过程中常⽤的⼀种⾛线⽅式,其主要⽬的是为了调节延时满⾜系统时序设计要求,但是设计者应该有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使⽤,因此⼀块PCB上的蛇形线越多并不意味着越“⾼级”。

实际设计中,为了保证信号有⾜够的保持时间,或减⼩同组信号之间的时间偏移,往往不得不故意进⾏绕线,例如DDR*(DDR1/DDR2/DDR3)中的DQS与DQ信号组要求要严格等长以降低PCB skew,这时就要⽤到蛇形线。

(1)设置蛇形线的参数。

蛇形线的参数主要有线长、同组线线长的差值、平⾏线段距离(Gap)及平⾏线段长度。

Router中打开项⽬浏览器(Project Explorer),展开Net Objects树形列表下的Net项,选择需要等长的⽹络(此处是DDR_DQ[15..0]以及DDR_DQS[1..0]),右击选择Copy,如下图所⽰。

(2)点击Nets组上的Matched Length Nets Groups,右击后选择Paste将上述⽹络粘贴到该项内,如下图所⽰。

(3)此时在Matched Length Net Groups组内出现⼀个默认名为MLNetGroup1的⽹络组,展开就可以看到,拷贝的⽹络在这⾥出现,如下图所⽰。

(4)点击MLNetGroup1⽹络组,右击后选择Properties,弹出如下图所⽰的对话框。

其中Tolerance即⽹络组内最长与最短⾛线的之间的差值,PADS默认不对⾛线长度加以限制,若需要,可勾选Restrict length 进⾏相应的设置,此两者的值可根据经验或仿真结果进⾏设置。

PADS-实用技巧

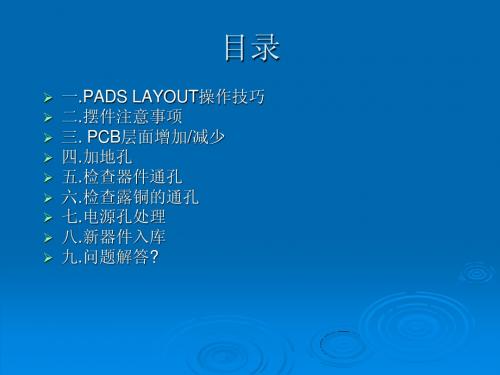

问题解答?(二)

3.如何中所有 netRemoveOK

问题解答?(三)

4.无法选取PCB器件,

铜…,如何处理? 鼠标任意点取空 白处Filter

检查layer层面是否都已 打开,无勾选的层面将 无法选取此层的所有东 西。

Part Decal/ Part Type (一)

在 PowerPCB的元件库来说,很多人都会混淆一个问题, 就是Part type 和 PartDecal这两个概念。 简单地说,放在 PCB 上面大家看得到的就是Part Decal。Part Type 表示元 件类型,是供导入网络表时对应的。 对于PowerPCB 中元件的制作, Part Type主要有以下一 些方面的东西要注意 : 1.器件定义 此图为标准定义,如发现 2.高度 有不一样的,请与库管理 员确认,确保器件正确性 3.供应商 4.HQ料号 5.Part type 的对应

PCB层面增加/减少

增加

按照各层的功能 命名

不要使用Max Layers功能

点此键会出现层 数定义,如需6层 输入6即可。

减层 减层时需将内层的Tracks,Via,Copper,Lines,Text删干净,在modify 中输入所需层数。

加地孔

后期加via可把gnd显示为空心线或则设

勾选所需要选取的内容。 单独勾选,适合在PCB 中运用框选的操作。

问题解答?(四)

5.如何恢复缺少层? SetupLayer DefinitionEnabe/Disable 勾选缺少层面OK

层面由L8直接到L12,缺 少了L9,L10,L11

问题解答?(五)

6.如何快速查net? a. 键盘输入n XXXX+Enter.被选net会高亮显示。 b.EditFindFind by 7.如何查找PCB中相同的封装? 同上

PADS使用技巧

PADS使用技巧PADS是一款功能强大的PCB设计软件,广泛应用于电子产品设计领域。

在使用PADS进行设计时,合理利用一些技巧可以提高工作效率,下面将介绍几个常用且实用的PADS使用技巧。

1.学习快捷键:快捷键可以极大地提高工作效率,因此学习并熟练使用PADS的快捷键是非常重要的。

可以通过查看软件的帮助文档或者在软件界面上查找相应的快捷键。

一旦掌握了常用的快捷键,设计过程中不再需要频繁切换鼠标和键盘操作,大大提高了工作效率。

2.利用功能:PADS提供了非常强大的功能,可以帮助我们快速定位到需要的元素或设置。

例如,可以使用功能找到特定元件、特定信号网或者特定层的元素。

在设计复杂的PCB时,利用功能可以减少寻找元素的时间,提高设计效率。

3. 使用设计覆盖层:PADS提供了设计覆盖层(Overlay)功能,可以将设计中的部分内容以一种半透明的方式覆盖在布线图上。

这样可以在进行布线时,同时参考原理图和布线约束,提高设计准确性。

设计覆盖层还可以用于表示设计规则的半透明图形,以便在设计过程中随时检查设计符合性。

4. 利用本地库:PADS提供了本地库(Library)功能,可以将元器件封装和参数保存为本地库。

在设计过程中,可以直接从本地库中选择相应的元器件,减少重复设计的工作量,提高设计效率。

同时,本地库还可以方便进行参数和封装的更新维护,确保设计的准确性和一致性。

5. 使用布线指导:PADS提供了布线指导(Route Guidance)功能,可以根据设计规则自动对设计进行布线指导。

在进行布线时,布线指导会根据设计规则对线宽、间距、走线方向等进行限制和优化,帮助我们遵循设计规则,提高布线效果。

布线指导还可以进行手动优化,以满足特定的布线要求。

6.利用批量操作:PADS提供了一些批量操作的功能,可以帮助我们同时对多个元素进行相同的操作。

例如,可以通过批量选择和批量修改的功能,一次性对多个元器件或者连线进行相同的修改。

PADS使用技巧和快捷键

PADS使用技巧和快捷键PADS(PowerPCB Advanced Design System)是一款强大的PCB设计软件,它可以帮助工程师快速、高效地设计和布局电路板。

在PADS中,有很多使用技巧和快捷键,可以帮助用户更快更好地完成设计任务。

下面是一些常用的PADS使用技巧和快捷键:1.快速创建器件:在PADS中创建器件非常简单。

只需要在构建菜单中选择"新建封装",然后选择要创建的器件类型,输入器件名称和封装参数,即可快速创建自定义封装。

2. 设计规则检查:在设计过程中,使用设计规则检查功能可以帮助用户查找和解决潜在的设计问题。

使用快捷键Ctrl+D可以快速打开设计规则检查对话框,用户可以在其中选择要检查的规则类型并运行检查。

3. 定位和切换层:在PADS中,使用快捷键F5可以打开层定位对话框,用户可以在其中选择要查看的层和对象类型。

另外,使用快捷键Shift+L可以在不同层之间快速切换。

7. 导入和导出BOM:在PADS中,使用快捷键Ctrl+B可以导出BOM (Bill of Materials)。

用户可以选择要导出的BOM格式,并指定导出文件的路径。

另外,使用快捷键Ctrl+Shift+B可以导入BOM。

8. 快速查找:在PADS中,使用快捷键Ctrl+F可以快速查找分量、线路或其他对象。

用户只需输入要查找的内容,然后PADS会自动定位并突出显示匹配的对象。

11. 更新布局:在PADS中,使用快捷键Ctrl+U可以更新布局。

当用户修改了原理图或器件设置后,可以使用此快捷键将更改应用于布局。

12. 生成3D模型:在PADS中,使用快捷键Ctrl+Shift+M可以生成3D模型。

用户可以选择要生成3D模型的分量,并指定模型的类型和文件路径。

14.自定义快捷键:在PADS中,用户可以根据自己的需求自定义快捷键。

只需要在设置菜单中选择"快捷键设置",然后选择要定义快捷键的命令,并设置相应的快捷键。

pads使用技巧

pads使用技巧1. 鼠线的处理Layout的缺省设置并不是让飞线最短化。

一开始布元件时,飞线实在是密如蛛网,晕头转向。

Tools\length minimization (CRTL+M) 也没有用,硬着头皮在缺省设置下完成了元件布局。

几欲faint。

后来才发现其实没有设置好。

正确或者说方便的设置应该是让飞线最短并且在移动中始终最短。

Setup\design rules\default rules\routing\ topology type\minimize 这样在按CTRL+M,很多飞线就消失了,也就最短。

2. 移动中鼠线处理Setup\preference\length minimize\during moving 这样移动元件是飞线始终最短。

很多飞线其实是地线。

可以把地线的飞线先hide起来。

并把地线的net 设置成比较特殊的颜色。

这样就布局就方便多了。

*3. 字体属性的修改单击鼠标右键,选select components, 再单击右键,选select all (CTRL+A)。

再单击右键,选query/modify (CTRL+Q), part outline width 输入想要的宽度,下面选label,选Ref. Des. Press the big button under it. 弹出新窗口, input the value you want at size and width. Press OK. Then the size, width , even the part outline width are same.4. 加过孔击老鼠右键,check “select net”, select the net you w ant to add via, usually, GND net, the GND is high light. Then right click mouse again, select “ add via”, then you can add vias which are connected to GND net. Freely and put them wherever you want. Remember, if the GND net is hide and set to a special color, no connection for these vias, but they are same color as other pads and trace in GND net.5. 覆铜。

PADS快捷键和技巧大全

别的发一些最根本常用的几个快捷键:设置通孔显示模式:D+O设置铜只显示外框形式:P+O改变当前层:L〔如改当前层为第二层,为L2〕测量:从当前地址开始测量:Q改变线宽:W设置栅格:G对找元件管脚或元件:S搜寻绝对坐标点:S〔 n〕 (n)改变走线角度:AA任意角, AD斜角, AO直角取消当前操作:UN,如 UN(1) 为取消前一个操作重复屡次操作:RE设计规那么检查:翻开 : ? DRP, 关闭: DRO,忽略设计规那么: DRI,以无过孔形式暂停走线: E锁定当前操作层对:PL(n)(n)选择当前过孔使用模式:自动过孔选择:VA埋孔或盲孔:VP通孔模式:VT保存: CTRL+S翻开: CTRL+O新建: CTRL+N选择全部:CTRL+A全屏显示:CTRL+W搬动: CTRL+E翻转: CTRL+F任意角度翻转:CTRL+I高亮: CTRL+H盘问与更正:CTRL+Q45 度翻转: CTRL+R增加走线:F2锁定层对:F4选择网络:F6选择管脚对:F5Ctrl+A选择全部。

Ctrl+B以板框为界整体显示当前设计。

Ctrl+C复制。

Ctrl+D Ctrl+E Ctrl+F Ctrl+G Ctrl+H Ctrl+I Ctrl+J 刷新。

搬动。

水平镜像翻转。

建立组合。

高亮。

以任意角度变换。

在布线模式下使用鼠标“十〞字光标中心呈环形。

Ctrl+K建立簇。

Ctrl+L排列元件。

Ctrl+M长度最短化。

Ctrl+N建立新元件。

Ctrl+O翻开文件。

Ctrl+P不在使用中。

PowerPCB 专业群、 PCB Layout学习群Ctrl+Q调出被选中对象的“盘问与更正〞对话框。

Ctrl+R以 90°角度为单位旋转。

Ctrl+S存盘。

Ctrl+T不在使用中。

Ctrl+U取消高亮。

Ctrl+V粘贴。

Ctrl+W以 Zoom模式查察。

Ctrl+X剪切。

Ctrl+Y扩展。

Ctrl+Z取消操作。

Ctrl+Alt+C调出颜色设置对话框。

PADS快捷键和技巧大全教学提纲

P A D S快捷键和技巧大全另外发一些最基本常用的几个快捷键:设置通孔显示模式:D+O设置铜只显示外框形式:P+O改变当前层:L(如改当前层为第二层,为L2)测量:从当前位置开始测量:Q改变线宽:W设置栅格:G对找元件管脚或元件:S寻找绝对坐标点:S(n)(n)改变走线角度:AA任意角,AD斜角,AO直角取消当前操作:UN,如UN(1)为取消前一个操作重复多次操作:RE设计规则检查:打开: DRP,关闭:DRO,忽略设计规则:DRI,以无过孔形式暂停走线:E锁定当前操作层对:PL(n)(n)选择当前过孔使用模式:自动过孔选择:VA埋孔或盲孔:VP通孔模式:VT保存:CTRL+S打开:CTRL+O新建:CTRL+N选择全部:CTRL+A全屏显示:CTRL+W移动:CTRL+E翻转:CTRL+F任意角度翻转:CTRL+I高亮:CTRL+H查询与修改:CTRL+Q45度翻转:CTRL+R增加走线:F2锁定层对:F4选择网络:F6选择管脚对:F5Ctrl+A 选择全部。

Ctrl+B 以板框为界整体显示当前设计。

Ctrl+C 复制。

Ctrl+D 刷新。

Ctrl+E 移动。

Ctrl+F 水平镜像翻转。

Ctrl+G 建立组合。

Ctrl+H 高亮。

Ctrl+I 以任意角度转换。

Ctrl+J 在布线模式下使用鼠标“十”字光标中心呈环形。

Ctrl+K 建立簇。

Ctrl+L 排列元件。

Ctrl+M 长度最短化。

Ctrl+N 建立新元件。

Ctrl+O 打开文件。

Ctrl+P 不在使用中。

PowerPCB 专业群 42336805、PCB Layout 学习群 48381494Ctrl+Q 调出被选中对象的“查询与修改”对话框。

Ctrl+R 以90°角度为单位旋转。

Ctrl+S 存盘。

Ctrl+T 不在使用中。

Ctrl+U 取消高亮。

Ctrl+V 粘贴。

Ctrl+W 以Zoom模式查看。

Ctrl+X 剪切。

Ctrl+Y 扩展。

PADS常用设置方法说明

布线时自动切换的两 个层 1. 动态走线 2. 添加走线 1. 自动保护走线 2. 使总线走线光滑

1. 允许走线以任何角度 出入焊盘 2. 走线以45度角出入焊 盘

1.高度/幅度(A): 线宽的整数倍 2. 间距 (G): 线宽的整数倍

二. PCB LAYOUT规则设置

Options参数设置-Thermals(花孔)

所以一个好的PCB设计图,应该是在设计人员充分了解 电路工作原理 PCB加工生产工艺及加过程

SMT/DIP组装部门作业方法加工过程

整机测试流程

为前提,按照机构的设计尺寸和以上环节,生产和测试要求去设计

PCB。

PCB LAYOUT

以下是我们将要学习的内容: PADS LAYOUT软件的使用。 PCB加工生产工艺要求。 PCB设计规则设定。 PCB设计初到设计结束的全过程。 接下来将从下面三个地方开始学习:

PCB LAYOUT

一.软件PADS LAYOUT的介绍 二.PCB LAYOUT规则设置

三.举例:PCB设计初到结束的全过程

进 入

进 入

进 入

一.PADS LAYOUT的使用

标题栏 工具栏

菜单栏

工作区域

状态栏

线宽

设计栅格

坐标栏

一.PADS LAYOUT的使用

(1)标题栏(Title bar):显示应用程序的图标,名称和文档名称. (2)菜单栏(Menu bar);将Power PCB所有操作指令归类总结 在一起. (3)工具栏(Tool bar):一些常用的命令以图标的形式排列出来, 方便用户操作. (4)状态栏(Status bat):显示设计过程中的操作信息. (5)工作区域(Work bat):PCB设计的主要工作区域. (6)坐标栏(x,y Coordinates)显示了光标所在工作区域以相 对原点的坐标值. (7)设计栅格(Design Grid)PCB设计中在工作区域中移动的 最小距离. (8)线宽(Line Width)PCB走线默认的走线宽度.

pads操作技巧

a.PADS2007中文教程1111----PADS2007_教程-PADS Logic.pdf 2222----PADS2007_教程-PADS Layout.pdf 3333----PADS2007_教程-PADS Router.pdf 4444----PADS2007_教程-高级封装设计.pdf1、PAGE UP/PAGE DOWN为视图的放大与缩小//1111----按住CTRL键,滑动鼠标的滑轮,就可以起到放大与缩小的功能,这样也可以省去去按右边的小键盘2、原理图的标框可以自己去画,这样可以一张图可以显示更多的内容---SHEET尺寸大小也可以选择,常用A3大小3、可以自己建立自己的PART TYPE库,这样跟系统自带可以分开,自己也好查找4、增加OFF-PAGE连接的时候,可以设置对应的页码是显示还是隐藏5、建立一个PART TYPE的顺序为----先建立CAE DECAL,然后是创建PART TYPE来引用刚才的CAE DECAL6、可以新建自己的PIN DECAL,并在画CAE DECAL引用它7、增加文字与文字变量8、无模命令模式的显示----直接按键盘字母,退出按ESC键9、显示网格的设置-----设置可见网格的大小,方便元器件对齐放置 10、文字字体跟线宽设置11、多个SHEET建立与管理-----方便原理图成模块化/功能块化放置12、增加总线及总线的编辑与连接13、原理图打印成PDF,打印成智能化PDF14、左边的各种类型列表-----封装,网络连接,元器件等等15、Display Color控制各层的显示与颜色设置16、ECO工程更改在LAYOUT跟LOGIC之间17、LAYOUT怎么画板的外形18、LAYOUT怎么导入网表----直接从ASC文件导入,从LOGIC发送过去19、LAYOUT的走线怎么显示出来20、定义层----信号/厚度21、定义设计规则22、inch,mil,mm之间的换算关系 1mil=1/1000inch=0.00254cm=0.0254mm1inch=1000mil=2.54cm=25.4mm 1mm=39.37mil23、OZ----盎司----重量单位1oz=28.35g(克)24、怎么查看当前设计的单位//1111----Tools/Options/Gobal/Design units----mil/metric/inchs25、LAYOUT怎么散开元器件----导入网表后,所有的元器件都在原点,需要散开来//1111----Tools/Disperse components26、原理图上如何找到对应的元器件点左边的Project Explorer中的components将对应元器件选到search and select组合框,再在组合框里面按确认键,对应的元器件就会高亮显示或者在search and select组合框输入要查找的元器件编号再按回车确认就可以找到对应的元件了27、LAYOUT里面选择各种对象----元器件/网络/任一对象/形状/未布的线28、LAYOUT里面怎么验证设计/查错//1111----Tools/Verify Design29、如何更改PADS2007的项目保存路径找到安装目录下的powerlogic.ini和powerpcb.ini文件,用记事本打开,将所有C:\PADS Projects替换E:\PADS Projects,然后就OK了。

PADS使用技巧和快捷键

PADS使用技巧和快捷键PADS是一款专业的PCB设计软件,在实际应用中,掌握一些PADS的使用技巧和快捷键,可以有效提高设计效率。

下面是一些常用的PADS使用技巧和快捷键:1.使用批量命名工具:PADs中有一个很方便的批量命名工具,可以一次性对多个元件的命名进行批量更改。

使用方法是首先选择需要更改的元件,在“属性填充”窗口中选择“命名”选项卡,然后点击“多个元件重命名”,填写新的命名规则即可。

2.使用层管理器:PADs的层管理器可以帮助用户进行层的选择和切换。

通过按下快捷键“L”或者点击菜单栏中的“视图”->“层管理器”,可以打开层管理器窗口。

在该窗口中,可以选择想要显示或隐藏的层。

3.自定义快捷键:PADs允许用户自定义快捷键,以适应个人的习惯。

可以点击菜单栏中的“工具”->“快捷键设置”,在弹出的对话框中选择想要修改的命令,然后设置新的快捷键。

4.使用局部放大功能:长时间的设计工作容易导致眼睛疲劳,PADs的局部放大功能可以帮助用户在细节设计时更清晰地观察。

使用方法是按住“CTRL”键并使用鼠标滚轮向上滚动放大,向下滚动缩小。

5.快速切换图层选择:在布线过程中,经常需要在不同的图层之间切换,PADs提供了一种快速切换图层选择的方式。

在任何时候,按下数字键1-9可以快速切换到对应编号的图层。

6.使用工具栏快捷键:PADS的工具栏中有很多常用的功能按钮,点击按钮可以快速访问对应的功能。

每个按钮都有与其对应的快捷键,用户可以将这些快捷键记下来,以便更快速地访问功能。

7.使用轨迹追踪功能:PADs有一个很实用的轨迹追踪功能,可以帮助用户在布线过程中更精确地移动元件或布线。

使用方法是在进行布线时,按住“ALT”键并拖动元件或布线,可以通过实时显示轨迹来更精确定位。

8.使用撤销和重做功能:PADs提供了撤销和重做功能,可以帮助用户在设计过程中随时进行撤销和恢复操作。

使用方法是按下快捷键“CTRL+Z”可以撤销上一步操作,“CTRL+Y”可以重做。

PADS使用技巧和快捷键

PADS使用技巧和快捷键PADS(PowerPCB Advanced Design System)是一款功能强大且广泛使用的PCB设计软件。

对于PADS的使用者来说,掌握一些技巧和快捷键可以提高设计效率和准确性。

以下是一些常用的PADS使用技巧和快捷键:1.快捷键概述:- Ctrl+N:新建工程- Ctrl+O:打开工程- Ctrl+S:保存工程- Ctrl+F:查找- Ctrl+H:替换- Ctrl+Z:撤销- Ctrl+Y:重做- Ctrl+C:复制- Ctrl+V:粘贴- Ctrl+X:剪切- Ctrl+A:全选2.绘制PCB:-使用鼠标滚轮可以放大和缩小视图。

- 在绘制路径时,按下Shift键可以保持直线或45度角。

- 使用Tab键可以在不同的引脚间切换。

- 按住Ctrl键并拖拽元件可以快速复制。

3.网格设置:- 在Design菜单下的Options中,可以设置网格大小和显示方式。

- 使用Ctrl+Shift+G可以直接打开网格选项对话框。

-在网格选项对话框中,可以设置网格单位、刻度线和显示网格。

4.元件布局和放置:- 使用Ctrl+L可以快速打开元件库列表。

-按下F9键可以自动停靠元件。

-按下F10键可以打开元件层框架。

-按下F11键可以打开元件层设置对话框。

-按下T键可以快速切换信号线的方向。

-按下M键可以在信号线之间切换阻值。

-使用鼠标右键可以选择信号线连接方式(连线/跳线/换层)。

6.视图和层管理:- 使用Alt+1可以切换到“PCB”层。

- 使用Alt+2可以切换到“Top Overlay”层。

- 使用Alt+3可以切换到“Bottom Overlay”层。

- 使用Alt+4可以切换到“Silkscreen”层。

- 使用Alt+5可以切换到“Soldermask”层。

- 使用Alt+6可以切换到“Copper 1”层。

- 使用Alt+7可以切换到“Copper 2”层。

7.标注和文档:-使用M键可以添加标识符。

pads使用技巧

pads使用技巧Pads是一款常用的电子设计自动化(EDA)软件,用于电路设计和仿真。

以下是使用Pads的一些技巧,以帮助提高工作效率。

1. 建立工作环境:Pads可以按照个人喜好进行设置,包括工作区域和工具栏的布局。

可以根据自己的习惯设置快捷键以及常用的工具。

2. 数据库管理:在Pads中,可以创建和管理元件库和原理图库。

对于常用的元件,可以在库中进行分类和组织,方便检索和使用。

此外,还可以导入和导出元件库以与其他用户共享。

3. 原理图设计:Pads提供了丰富的元件库和工具,可以快速绘制电路原理图。

在设计原理图时,可以使用连接线、节点和端子等工具,确保电路连接正确。

4. 原理图仿真:Pads可以进行电路仿真,以验证电路的功能和性能。

可以添加仿真器件和信号源,设置仿真参数,并查看波形和结果。

5. PCB布局设计:在进行PCB布局设计时,可以利用Pads的工具来放置元件和布线。

可以使用自动布线功能或手动优化布线,以确保信号完整性和电磁兼容性。

6. PCB布线规则:在进行PCB布线时,可以设置布线规则,以确保符合设计要求。

可以设置电气规则、信号完整性规则和机械规则等,Pads会在布线过程中进行检查。

7. 三维模型:Pads可以将PCB设计转换为三维模型,并进行三维可视化。

这有助于检查PCB布局和元件之间的冲突,以及检查整体外观和尺寸。

8. 设计规则检查:在设计完成后,可以使用Pads的设计规则检查功能,对布线和元件进行检查。

可以避免布线错误、元件覆盖和空置,确保设计质量。

9. 输出文件:完成PCB设计后,可以使用Pads生成制造文件和文档。

可以导出Gerber文件、钻孔文件和焊盘文件等,以供制造商进行生产。

10. 学习和交流:Pads有很大的用户群体,可以通过参加培训和用户交流等活动,学习更多关于Pads的技巧和经验,也可以分享自己的经验和问题。

总之,Pads作为一款强大的EDA工具,可以帮助工程师进行电路设计和布局。

pads 应用技巧,帮你快速提升你的画图能力

POWERPCB常用技巧:(一)1。

移动元件时可按TAB键翻转。

2。

加任何形状的孔(包括方形元件脚):可在24层用二维线画。

3。

加裸铜(即阻焊,在加大导通电流和增加焊接附着力时经常用到)用铺铜功能在28层加。

4。

把当前PCB板用到的元件封装存入自已的库:圈住所有元件按右键选SA VE TO LIB...,再选所需的库即可.(把别人的库占为已有算是不费吹灰之力)5.在POWERPCB把二维线图形存入库:先用二维线功能画好所需的图形(可加上文字)把它们全部圈住按右键选SA VE TO LIB...,再选所需的库即可.(方便日后调用)在POWERPCB中,将两块板合并成一块板的方法:1.打开要复制的线路板文件,打开ECO模式2.全选(可用单击鼠标右键选择SELECT ALL)3.复制4.打开复制到的线路板文件,打开ECO模式5.粘帖6.移动到合适位置7. ; ; ; ;OK!powerlogic中好像没有copy功能吧!比如说在protel中我想在一个project中将一张图上的内容粘到另一张图上式可以做到的,在powerlogic中好像不能这么做,只能在同一页图中进行粘贴,这样好像不利于资源的重复利用,不知道大家有没有什么方法,我好像没找到!可以是可以,但是比较麻烦!先将选中的原理图部分做“Make Group”,然后再将其“Copy to File”。

然后在需要粘贴的新页中,选择“Add Item-Paste From File”即可。

以上操作均使用右键菜单。

请教:POWERPCB如何能象PROTEL99那样一次性更改所有相同的或所有的REF或TXT文字的大小,还有,怎么更改一个VIA的大小而不影响其他VIA的大小.这功能POWERPCB真不如PROTEL99SE.可以通过鼠标右键选择“document”,然后就可以选中所需要的ref或文字了。

如果要更改一个Via的大小,需要新建一种类型的Via。

PADS使用技巧

PADS使用技巧1.用filter选择要删除的东东,然后框选,delete即可或者:无模下右键Select Net-Select All-Delete2.在Filter中只选Lable,在板图上框选整个电路板,将选中所有的元件标号,选择Property,可以同时修改所有元件标号的大小、字体的粗细等。

3.Solde Mask是用来画不要绿油的吗?这一层是在PCB板生产商生成的吗?//这一层是阻焊层,每个元件脚都有阻焊的。

你要做好特殊的部分,正常的部分不用理。

至于在哪里生成,就随意了。

我一般是生成后给PCB厂家。

4.Paste Mask是用来干吗的?是不这一层只有去贴片厂才生成的?//这一层是锡膏涂布层,只有贴片元件的焊盘才有,一般你出好GERBER给钢网厂。

5.在PADS焊盘对话框中[Offset]编辑栏起什么作用?//主要是用在一些焊盘和过孔的中心不在一点上的焊盘,也可以灵活地应用在其他方面。

gerber 文件的生成,作用,等等。

6.加入公司格式框的步骤:Drafting Toolbar---from library---*******(库名字)库选择即可。

7.Gerber文件输出的张数,一共为N+8张:n张图为板子每层的连线图2张丝印图(silkscreen top/bottom)2张阻焊图(solder mask top/bottom)2张助焊图(paste mask top/bottom)2张钻孔图(drill/Nc drill)8.在PADS输出光绘文件时去掉自动添加的文件名,不选择Plot Job Name即可。

9.脚间距,BSC是指基本值,其它还有TYP(典型值),REF参考值10.在利用PADS2007做新的器件封装时,如果在多个库中有同一个封装,数据库在定义part与decal对应关系时容易出错。

应尽量少出现同名的封装。

删除同名的封装后要同新建立part,以便建立part与decal的数据库联系,不然就会出现灾难性的错误。

PADS使用技巧和快捷键

其它命令

? 可以打开英文帮助文件help。

BMW 创建宏命令。详见"To Use BMW"。

BLT 实行基本的 Log 测试,详见"To Run BLT"。

F 快速打开文件,这里的 为文件路径与文件名。

命令字符命令 含义及用途

C 补充格式,在内层负片设计时用来显示Plane;层的焊盘及Thermal。使用方法是:从键盘上输入C 显示;再次输入C 可去除显示。

Q 快速测量命令。可以快速.测量dx,dy 和d 。注意精确测量时将状态

框中的Snaps to the design grid 取消。

QL 快速测量配线长度。可对线段、网络、配线对进行测量。

测量方式如下:首先选择线段、网络或者配线对,然后输入QL 就会得

到相关长度报告。

R 改变显示线宽到 , 如, R 50。

或者 PL top bottom。

SH 推挤方式on /off 切换。

V 选择 via 类型,如 V 标准via。

VA 自动 via 选择。

VP 选择使用partial via.

VT 选择使用贯通 via.

T 透明显示切换。在复杂板子设计时很有用。

绘图相关命令Drafting Objects

如G25 或者G25 25。

GD {} 屏幕上的显示Grid 设定。第二个参数为可选项。

如GD25 25 或者GD100。

GP 切换极坐标 grid 。极坐标 grid 在设计外形为圆形、或者元件布局按

极坐标方式放置时使用。

GP r a 极坐标下的元件指定移动方式(r 为半径,a 为角度)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PADS功能使用技巧V0.3由于文档更新较为繁琐,故今后不再以PDF格式进行更新,此次为最后一次,有兴趣一起探讨PADS PCB设计的可加群号:34098324。

与之前版本有所区别的是,本次文档添加了PADS9.0的新功能,以往版本可能会较复杂的操作在该版本中会更简洁。

一、如何走蛇形线?蛇形线是布线过程中常用的一种走线方式,其主要目的是为了调节延时满足系统时序设计要求,但是设计者应该有这样的认识:蛇形线会破坏信号质量,改变传输延时,布线时要尽量避免使用,因此一块PCB上的蛇形线越多并不意味着越“高级”。

实际设计中,为了保证信号有足够的保持时间,或减小同组信号之间的时间偏移,往往不得不故意进行绕线,例如DDR*(DDR1/DDR2/DDR3)中的DQS与DQ信号组要求要严格等长以降低PCB skew,这时就要用到蛇形线。

(1)设置蛇形线的参数。

蛇形线的参数主要有线长、同组线线长的差值、平行线段距离(Gap)及平行线段长度。

Router中打开项目浏览器(Project Explorer),展开Net Objects树形列表下的Net项,选择需要等长的网络(此处是DDR_DQ[15..0]以及DDR_DQS[1..0]),右击选择Copy,如下图所示。

(2)点击Nets组上的Matched Length Nets Groups,右击后选择Paste将上述网络粘贴到该项内,如下图所示。

(3)此时在Matched Length Net Groups组内出现一个默认名为MLNetGroup1的网络组,展开就可以看到,拷贝的网络在这里出现,如下图所示。

(4)点击MLNetGroup1网络组,右击后选择Properties,弹出如下图所示的对话框。

其中Tolerance即网络组内最长与最短走线的之间的差值,PADS默认不对走线长度加以限制,若需要,可勾选Restrict length进行相应的设置,此两者的值可根据经验或仿真结果进行设置。

(5)点击工具栏上图标或按热键Ctrl+Enter,选中Options对话框中的Routing页表项,其中红色框中的参数即针对蛇形线,这里我们把平行线段距离(Gap)设置为3,点击OK,即可完成蛇形线的设置。

(6)在PCB中选定一个引脚,按F3开始走线,在需要走蛇形线的地方停顿,右击后选择Add Accordion,即可开始蛇形走线,如下图所示。

控制方面的细节不再赘述。

(7)完成蛇形线后,右击选择Complete Accordion即可进入常规走线模式。

(8)最后完成的结果如下图所示。

细心的读者可能发现自己走出来的有135o角,而上图中却是弧线☺☺,是的!走出来的原本不是弧线,是在Layout中通过Add Miters处理过的。

用Layout打开刚才的PCB,选择菜单栏Tool -> Options后出现如下对话框,在Miters组合框内选择Arc,表示对走线进行圆弧修正,Ratio可按具体情况设置,此处为3,此值不宜过小(没效果)亦不可过大(有些角度修正不到位),Angle为135o,表示允许对135o角进行修正,完成后点击OK即可。

选择需要修正的网络,右击后选择Add Miters如下图所示,这样蛇形线就成圆弧走线了。

上述操作有点繁琐,PADS9.0提供了新的功能,可以直接走圆弧蛇形线,读者可以试试。

二、如何走差分线?差分信号在高速电路设计中应用越来越广泛,如USB、HDMI、PCI、DDR*等,承载差分信号的差分线主要优势有:抗干扰能力强,能有效抑制EMI、时序定位精确等,对于PCB 工程师来说,最关注的是如何确保在实际走线中能完全发挥差分线的这些优势。

(1)定义差分对信号:在Router中,同时选定需要走差分线的网络(Net),右击后选择Make Differential Net,如下图所示。

(2)打开项目浏览器Project Explorer窗口,展开Net Objects树形列表下的Differential Pairs 项,刚刚定义的差分对DM<->DP就在这里,选定该差分对后右击选择Properties,如下图所示。

(3)在弹出的对话框中,可设置相应的线宽及线距,此处分别设置为8与6(8:8:6)。

点击OK,即完成差分对的定义。

线宽及线距影响差分线的阻抗,其值可由Polar SI8000软件粗略估算一下,如下图所示,对于阻抗要求高的可与PCB厂家沟通确定。

(4)选择其中的一个引脚,按F3或单击工具栏上图标,即可开始差分对布线(与常规布线一致),如下图所示。

(5)在终端处需要分开布线,右击后选择弹出菜单中的Route Separately,如下图所示。

(6)按如上操作后,按常规走线完成即可,如下图所示。

至此已经完成了差分线的走线,有些读者可能会见过一些如DDR*的板子,差分线也走了蛇形线,其实将上述两个结合起来是很容易做到的,这里就不赘述了。

三、如何统一修改元件标号字体?LAYOUT完毕后进行元件标号字体调整时,你是否试图用Select Document+Select All 来选定所有标号?可结果却并不令人满意。

(1)在Layout中,选择菜单栏Edit -> Filter…,将对话框按如左下图设置(即仅勾选Labels)。

(2)右击->Select All,即可选定所有的元件标号,再右击-> Properties,即可出现右上图对话框,此时可进行需要的设置。

(需要注意的是,Layer下拉列表不应选择任何层,否则丝印会放在错误的板层上)当然也可以用Select Document+Select All的方式,前提是在Layout中菜单栏Setup -> Display Colors中仅选定Ref.De(纵向栏),如下图所示,这种方法较费时一点。

四、如何做到20H规则?电源层与地层之间变化的电场在板边缘会向外辐射电磁干扰(EMI),称为边沿效应。

20H规则可将70%的电场限制在接地层边沿内,100H可达到98%。

(1)在Layout中,选择菜单栏Setup -> Design Rules… -> Conditional Rules,在出现的Conditional Rule Setup对话框的Source rule object中选择需要约束的Nets(这里是DVDD),Against rule object中选择POWER层(自定义的电源层名称),确定Clearance单选框,点击Create,在左下角的Existing rule sets中即出现定义的约束项,如下图所示。

(2)选择该约束项,点击Matrix…,在下图所示对话框中的Board与Copper处填入200(此处假定电源与地层的间隔为10mil,读者可按需要进行配置)(3)点击OK,即可完成规则设置,以上规则约束表示:当DVDD在POWER层时,Copper 与Board之间间距为200mil。

同样可以设置其它的规则,下图为一PCB进行20H规限后的图片。

读者也可以尝试在菜单栏Setup -> Design Rules… -> Net中进行规则约束,效果大体是一样的。

五、如何自定义快捷键?热键(或快捷键)是每一个EDA工程师会(也应该)关注的问题,因为好用且合理的热键可以使工作效率大幅度地提高。

PADS定义了很多无模命令可以实现这一目的,但菜单执行的热键却不大友好,甚至还不如Protel。

当你因为PCB一点点修改而进行第N次Flood 时,你是否会因为屡次陷入点击Tools –> Pour Manager… Tools -> Pour Manager…这个“圈套”而感到厌烦?当你看到下图所示的由三个键堆积起来的按键组合时,会不会有点望而生畏的感觉?! 没关系,现在我们可以定义自己的热键。

(1)找到PADS的安装目录(这里是D:\Program Files\Mentor Graphics),按Ctrl+F或点击工具栏上的图标,在左边出现的搜索项目中填入“menufile.dat”,此文件即为PADS 的菜单定义文件,点击立即搜索即可搜到如上述名字的文件,如右下图所示。

(2)用记事本打开“menufile.dat”,此时你看到的文件可能是空白的,因为文件内容很长,而前面是空白的,我们用查找的方式定位到快捷键定义的区域。

按Ctrl+F,在出现的对话框中填入“insert”,再选择查找下一个即可定位到如下所示的快捷键定义区域。

读者可以对照下图所示的菜单来熟悉此文件的结构,其中第二列为菜单名,第四列为其对应的快捷键。

比如在menufile中File项中定义了Ctrl+N、Ctrl+O、Ctrl+S,相应地在Layout 的File菜单栏中有此三个热键。

按照这种思路,只要我们在想要设置热键的菜单后面给出心仪的热键组合,即可完成热键的设置。

当然在此操作之前应注意如下几点:①建议在更改menufile.dat前将此文件备份。

在操作失误且没有备份的情况下,可在其它机器上拷贝同软件版本的该文件放到相应的目录下即可;②添加热键时应首先搜索该文件中是否已经存在该热键,即热键不应与已有的组合重复,否则新添加的热键组合将不会有效;③建议保留通用的热键而不做它用,如Ctrl+N、Ctrl+S、Ctrl+C、Ctrl+V等。

(当然这只是建议☺☺)(3)以下以更改Display Colors…的热键为例(默认为Ctrl+Alt+C,我们设置为Ctrl+G)。

按Ctrl+F,在弹出的对话中填入Ctrl+G,点击查找下一个,出现如下图所示的。

此举的目的在于确定是否已经存在Ctrl+G这一热键组合做为它用。

若存在,我们可以评估一下对应功能的使用频度,如果使用次数很少,则可以将其删除以做它用。

(4)由上图可知,我们已经找到了Ctrl+G的热键组合,默认的定义是Create_Union(创建联合体),由经验可得,该操作是很少被用到的,因此我们可以将其做为它用。

在此我们将其删除掉,如下图所示。

(5)查找下一个,直到出现如下对话框,表明所有的Ctrl+G已经不再存在,此时即可将此组合赋给其它功能。

(6)我们查找关键字“display”,如下图所示。

可知Display Color…默认其热键组合为Ctrl+Alt+C(这与前面在菜单栏中看到的是一致的),我们将其更改为Ctrl+G。

(7)点击查找下一个,将其它的Ctrl+Alt+C均改为Ctrl+G即可完成设置(该组合有两处用到,因此需修改两处),做完以上步骤后点击保存即可。

(8)重新启动Layout(若做上述步骤时Layout已打开),点击Setup菜单如下图所示,可知我们的Ctrl+G已经按预定计划更改。