HIGH SPEED AND LOW POWER DYNAMIC LATCH COMPARATOR

UCC2813D-1中文资料

UCC2813-0/-1/-2/-3/-4/-5UCC3813-0/-1/-2/-3/-4/-5FEATURES100µA Typical Starting Supply Current 500µA Typical Operating Supply Current Operation to 1MHz Internal Soft Start Internal Fault Soft StartInternal Leading-Edge Blanking of the Current Sense Signal 1 Amp Totem-Pole Output70ns Typical Response fromCurrent-Sense to Gate Drive Output 1.5% Tolerance Voltage Reference Same Pinout as UCC3802, UC3842, and UC3842ADESCRIPTIONThe UCC3813-0/-1/-2/-3/-4/-5family of high-speed,low-power inte-grated circuits contain all of the control and drive components required for off-line and DC-to-DC fixed frequency current-mode switching power supplies with minimal parts count.These devices have the same pin configuration as the UC3842/3/4/5family,and also offer the added features of internal full-cycle soft start and internal leading-edge blanking of the current-sense input.The UCC3813-0/-1/-2/-3/-4/-5family offers a variety of package options,temperature range options,choice of maximum duty cycle,and choice of critical voltage levels.Lower reference parts such as the UCC3813-3and UCC3813-5fit best into battery operated systems,while the higher reference and the higher UVLO hysteresis of the UCC3813-2and UCC3813-4 make these ideal choices for use in off-line power supplies.The UCC2813-x series is specified for operation from –40°C to +85°C and the UCC3813-x series is specified for operation from 0°C to +70°C.BLOCK DIAGRAMLow Power Economy BiCMOSCurrent Mode PWMUDG-96134Part Number Maximum Duty CycleReference VoltageTurn-On ThresholdTurn-Off ThresholdUCCx813-0100%5V 7.2V 6.9V UCCx813-150%5V 9.4V 7.4V UCCx813-2100%5V 12.5V 8.3V UCCx813-3100%4V 4.1V 3.6V UCCx813-450%5V 12.5V 8.3V UCCx813-550%4V4.1V3.6VORDERING INFORMATIONCONNECTION DIAGRAMSVCC Voltage (Note 2). . . . . . . . . . . . . . . . . . . . . . . . . . .12.0V VCC Current. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30.0mA OUT Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.0A OUT Energy (Capacitive Load). . . . . . . . . . . . . . . . . . .20.0µJ Analog Inputs (FB, CS). . . . . . . . . . . . . . . . . . . .–0.3V to 6.3V Power Dissipation at T A < +25°C (N Package). . . . . . . . . 1.0W Power Dissipation at T A < +25°C (D Package). . . . . . . .0.65W Storage Temperature . . . . . . . . . . . . . . . . . . .–65C to +150°C Junction Temperature. . . . . . . . . . . . . . . . . . .–55C to +150°C Lead Temperature (Soldering, 10 Seconds). . . . . . . . .+300°CABSOLUTE MAXIMUM RATINGS (Note 1)Note 1:All voltages are with respect to GND.All currents are positive into the specified terminal.Consult Unitrode Integrated Circuits databook for information regarding thermal specifica-tions and limitations of packages.Note 2:In normal operation VCC is powered through a current limiting resistor.Absolute maximum of 12V applies when VCC is driven from a low impedance source such that ICC does not exceed 30mA.UCCPACKAGETEMPERATURE RANGEPRODUCT OPTION ORDERING INFORMATIONTEMPERATURE RANGEPACKAGES UCC2813–40°C TO +85°C N, D,PW UCC38130°C TO +70°CN, D,PWELECTRICAL CHARACTERISTICS Unless otherwise stated, these specifications apply for –40°C ≤T A ≤+85°C forUCC2813-x; 0°C ≤T A ≤+70°C for UCC3813-x;VCC = 10V (Note 3); RT = 100k from REF to RC; CT=330pF from RC to GND;0.1µF capacitor from VCC to GND; 0.1µF capacitor from VREF to GND. T A =T J .PARAMETERTEST CONDITIONSUCC2813-x UCC3813-xUNITSMINTYPMAXReference Section Output Voltage T J = +25°C, I = 0.2mA, UCCx813-0/-1/-2/-4 4.925 5.00 5.075V T J = +25°C, I = 0.2mA, UCCx813-5 3.944.00 4.06V Load Regulation 0.2mA <I <5mA1030mV Total Variation UCCx813 -0-1/-2/-4 (Note 7) 4.84 5.00 5.10V UCCx813-5 (Note 7)3.844.00 4.08V Output Noise Voltage 10Hz ≤f ≤10kHz,T J = +25°C (Note 9)70µV Long Term Stability T A = +125C, 1000 Hours (Note 9)5mV Output Short Circuit –5–35mAOscillator Section Oscillator Frequency UCCx813-0/-1/-2/-4 (Note 4)404652kHz UCCx813-5 (Note 4)263136kHz Temperature Stability (Note 9)2.5%Amplitude Peak-to-Peak 2.25 2.40 2.55V Oscillator Peak Voltage2.45VELECTRICAL CHARACTERISTICS Unless otherwise stated, these specifications apply for –40°C≤T A≤+85°C for UCC2813-x; 0°C≤T A≤+70°C for UCC3813-x;VCC= 10V (Note 3); RT = 100k from REF to RC; CT=330pF from RC to GND;0.1µF capacitor from VCC to GND; 0.1µF capacitor from VREF to GND. T A=T J.PARAMETER TEST CONDITIONSUCC2813-xUCC3813-x UNITS MIN TYP MAXError Amplifier SectionInput Voltage COMP= 2.5V; UCCx813-0/-1/-2/-4 2.42 2.50 2.56VCOMP= 2.0V; UCCx813-3/-5 1.92 2.0 2.05V Input Bias Current–22µA Open Loop Voltage Gain6080dB COMP Sink Current FB = 2.7V,COMP= 1.1V0.4 2.5mA COMP Source Current FB = 1.8V,COMP= REF – 1.2V–0.2–0.5–0.8mA Gain Bandwidth Product(Note 9)2MHz PWM SectionMaximum Duty Cycle UCCx813-0/-2/-39799100%UCCx813-1/-4/-5484950 Minimum Duty Cycle COMP= 0V0% Current Sense SectionGain(Note 5) 1.10 1.65 1.80V/V Maximum Input Signal COMP= 5V (Note 6)0.9 1.0 1.1V Input Bias Current–200200nA CS Blank Time50100150ns Over-Current Threshold 1.32 1.55 1.70V COMP to CS Offset CS = 0V0.450.90 1.35V Output SectionOUT Low Level I = 20mA, all parts0.10.4VI = 200mA, all parts0.350.90VI = 50mA,VCC= 5V, UCCx813-3/-50.150.40VI = 20mA,VCC= 0V, all parts0.7 1.2VOUT High V SAT (V CC-OUT)I = –20mA, all parts0.150.40V I = –200mA, all parts 1.0 1.9V I = –50mA,VCC= 5V, UCCx813-3/-50.40.9VRise Time C L= 1nF4170ns Fall Time C L= 1nF4475ns Undervoltage Lockout SectionStart Threshold (Note 8)UCCx813-0 6.67.27.8VUCCx813-18.69.410.2VUCCx813-2/-411.512.513.5VUCCx813-3/-5 3.7 4.1 4.5V Stop Threshold (Note 8)UCC1813-0 6.3 6.97.5VUCC1813-1 6.87.48.0VUCCx813-2/-47.68.39.0VUCCx813-3/-5 3.2 3.6 4.0V Start to Stop Hysteresis UCCx813-00.120.30.48VUCCx813-1 1.62 2.4VUCCx813-2/-4 3.5 4.2 5.1VUCCx813-3/-50.20.50.8VELECTRICAL CHARACTERISTICS Unless otherwise stated, these specifications apply for –40°C≤T A≤+85°C for UCC2813-x; 0°C≤T A≤+70°C for UCC3813-x;VCC= 10V (Note 3); RT = 100k from REF to RC; CT=330pF from RC to GND;0.1µF capacitor from VCC to GND; 0.1µF capacitor from VREF to GND. T A=T J.PARAMETER TEST CONDITIONSUCC2813-xUCC3813-x UNITS MIN TYP MAXSoft Start SectionCOMP Rise Time FB = 1.8V, Rise from 0.5V to REF–1V4ms Overall SectionStart-up Current VCC< Start Threshold0.10.23mA Operating Supply Current FB = 0V, CS = 0V, RC = 0V0.5 1.2mA VCC Internal Zener Voltage ICC = 10mA (Note 8)1213.515V VCC Internal Zener Voltage Minus StartThreshold VoltageUCCx813-2/-40.5 1.0VNote 3: Adjust VCC above the start threshold before setting at 10V.Note 4: Oscillator frequency for the UCCx813-0, UCCx813-2 and UCCx813-3 is the output frequency.Oscillator frequency for the UCCx813-1, UCCx813-4 and UCCx813-5 is twice the output frequency.Note 5: Gain is defined by:A VVV V COMPCSCS≤≤008..Note 6: Parameter measured at trip point of latch with Pin 2 at 0V.Note 7: Total Variation includes temperature stability and load regulation.Note 8: Start Threshold, Stop Threshold and Zener Shunt Thresholds track one another. Note 9: Guaranteed by design. Not 100% tested in production.COMP:COMP is the output of the error amplifier and the input of the PWM comparator.Unlike other devices,the error amplifier in the UCC3813 family is a true,low output-impedance,2MHz operational amplifier.As such,the COMP terminal can both source and sink current.However,the error amplifier is internally current limited,so that you can command zero duty cycle by externally forcing COMP to GND.The UCC3813family features built-in full cycle Soft Start. Soft Start is implemented as a clamp on the maximum COMP voltage.FB:FB is the inverting input of the error amplifier.For best stability,keep FB lead length as short as possible and FB stray capacitance as small as possible.CS:CS is the input to the current sense comparators. The UCC3813family has two different current sense comparators:the PWM comparator and an over-current comparator.The UCC3813family contains digital current sense filter-ing,which disconnects the CS terminal from the current sense comparator during the100ns interval immediately following the rising edge of the OUT pin.This digital filter-ing,also called leading-edge blanking,means that in most applications,no analog filtering(RC filter)is re-quired on pared to an external RC filter tech-nique,the leading-edge blanking provides a smaller effective CS to OUT propagation delay.Note,however, that the minimum non-zero On-Time of the OUT signal is directly affected by the leading-edge-blanking and the CS to OUT propagation delay.The over-current comparator is only intended for fault sensing,and exceeding the over-current threshold will cause a soft start cycle.RC:RC is the oscillator timing pin.For fixed frequency operation,set timing capacitor charging current by con-necting a resistor from REF to RC.Set frequency by con-necting a timing capacitor from RC to GND.For best performance,keep the timing capacitor lead to GND as short and direct as possible.If possible,use separate ground traces for the timing capacitor and all other func-tions.PIN DESCRIPTIONSThe frequency of oscillation can be estimated with the following equations:UCCx813-0/-1/-2/-4:F R C=•15.UCCx813-3, UCCx813-5:F R C=•10.where frequency is in Hz,resistance is in Ω,and capaci-tance is in farads.The recommended range of timing re-sistors is between 10k and 200k and timing capacitor is 100pF to 1000pF .Never use a timing resistor less than 10k.GND:GND is reference ground and power ground for all functions on this part.OUT:OUT is the output of a high-current power driver capable of driving the gate of a power MOSFET with peak currents exceeding ±750mA.OUT is actively held low when VCC is below the UVLO threshold.The high-current power driver consists of FET output de-vices,which can switch all of the way to GND and all of the way to VCC.The output stage also provides a very low impedance to overshoot and undershoot.This means that in many cases,external schottky clamp diodes are not required.VCC:VCC is the power input connection for this device.In normal operation VCC is powered through a current limiting resistor.Although quiescent VCC current is verylow,total supply current will be higher,depending on OUT current.Total VCC current is the sum of quiescent VCC current and the average OUT current.Knowing the operating frequency and the MOSFET gate charge (Qg),average OUT current can be calculated from:I Q F OUT g =•.To prevent noise problems,bypass VCC to GND with a ceramic capacitor as close to the VCC pin as possible.An electrolytic capacitor may also be used in addition to the ceramic capacitor.REF:REF is the voltage reference for the error amplifier and also for many other functions on the IC.REF is also used as the logic power supply for high speed switching logic on the IC.When VCC is greater than 1V and less than the UVLO threshold,REF is pulled to ground through a 5k Ωresis-tor.This means that REF can be used as a logic output indicating power system status.It is important for refer-ence stability that REF is bypassed to GND with a ce-ramic capacitor as close to the pin as possible.An electrolytic capacitor may also be used in addition to the ceramic capacitor.A minimum of 0.1µF ceramic is re-quired.Additional REF bypassing is required for external loads greater than 2.5mA on the reference.To prevent noise problems with high speed switching transients,bypass REF to ground with a ceramic capaci-tor very close to the IC package.PIN DESCRIPTIONS (cont.)APPLICATION INFORMATION4.003.983.963.943.923.903.883.863.843.8244.24.44.64.855.25.45.65.86V (V)CC V (V )R E F Figure 5.UCC3813-3/-5V REF vs.V CC ;I LOAD= 0.5mA.APPLICATION INFORMATION (cont.)T and C T.R T and C T .oscillator frequency.oscillator frequency.CC APPLICATION INFORMATION (cont.)CCCS = 0V.T T UNITRODE CORPORA TION7 CONTINENTAL BLVD.• MERRIMACK, NH 03054TEL.(603) 424-2410 • FAX (603) 424-3460IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

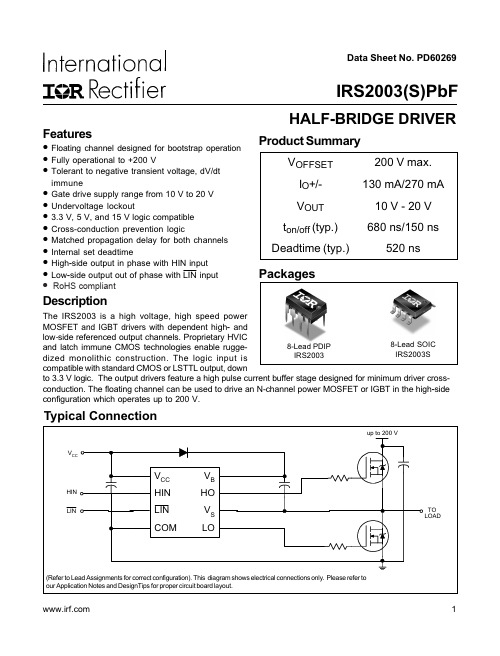

IRS2003STRPbF中文资料

Data Sheet No. PD60269Typical ConnectionProduct SummaryV OFFSET 200 V max.I O +/-130 mA/270 mA V OUT 10 V - 20 V t on/off (typ.)680 ns/150 nsDeadtime (typ.)520 nsHALF-BRIDGE DRIVERFeatures•Floating channel designed for bootstrap operation •Fully operational to +200 V•Tolerant to negative transient voltage, dV/dtimmune•Gate drive supply range from 10 V to 20 V •Undervoltage lockout•3.3 V, 5 V, and 15 V logic compatible •Cross-conduction prevention logic•Matched propagation delay for both channels •Internal set deadtime•High -side output in phase with HIN input •Low -side output out of phase with LIN input DescriptionThe IRS2003 is a high voltage, high speed power MOSFE T and IGBT drivers wi th dependent high - and low -side referenced output channels. Proprietary HVICand latch immune CMOS technologies enable rugge-dized monolithic construction. The logic input iscompatible with standard CMOS or LSTTL output, downto 3.3 V logic. The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. The floating channel can be used to drive an N-channel power MOSFET or IGBT in the high -side configuration which operates up to 200 V. 1IRS2003(S)PbFPackages8-Lead PDIP IRS20038-Lead SOIC IRS2003S • RoHS compliantIRS2003(S)PbFAbsolute Maximum RatingsAbsolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage param-eters are absolute voltages referenced to COM. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.Note 1: Logic operational for V S of -5 V to +200 V. Logic state held for V S of -5 V to -V BS . (Please refer to the Design Tip DT97-3 for more details).IRS2003(S)PbFStatic Electrical CharacteristicsV BIAS (V CC, V BS) = 15 V and T A = 25 °C unless otherwise specified. The V IN, V TH, and I IN parameters are referenced to COM. The V O and I O parameters are referenced to COM and are applicable to the respective output leads: HO or LO. Dynamic Electrical CharacteristicsV BIAS (V CC, V BS) = 15 V, C L = 1000 pF and T A = 25 °C unless otherwise specified.IRS2003(S)PbFLead DefinitionsSymbol DescriptionHIN Logic input for high -side gate driver output (HO), in phase Logic input for low-side gate driver output (LO), out of phase V B High -side floating supply HO High -side gate drive output V S High -side floating supply return V CC Low-side and logic fixed supply LO Low -side gate drive output COMLow -side returnLIN Lead Assignments8 Lead PDIP 8 Lead SOICIRS2003PbF IRS2003SPbF12348765V CC HIN LIN COMV B HO V S LO12348765V CC HIN LIN COMV B HO V S LOIRS2003(S)PbFLINHOLOHINFigure 3. Deadtime Waveform DefinitionsFigure 2. Switching Time Waveform DefinitionsLOIRS2003(S)PbFIRS2003(S)PbF8-50-250255075100125Temperature (oC)Figure 10A. Logic "0"(HIN) & Logic "1" ( )Input Voltage vs. TemperatureLINIRS2003(S)PbFIRS2003(S)PbFIRS2003(S)PbF10vs. Temperaturevs. VoltageFigure 17A. Logic "0" Input Bias Currentvs. TemperatureFigure 17B. Logic "0" Input Bias Currentvs. VoltageL o g i c “0” I n p u t B i a s C u r r e n t (µA )0123456-50-250255075100125Temperature (°C)F ig u r e 17A. L o g ic "0" I n p u t B ia s C u r r e n t 0123456101214161820Supply Voltage (V)Case OutlinesCTape & Reel 8-lead SOICPer SCOP 200-002The SOIC-8 is MSL 2 qualified.This product has been designed and qualified for the industrial level.Qualification standards can be found at Data and specifications subject to change without notice. 11/27/2006。

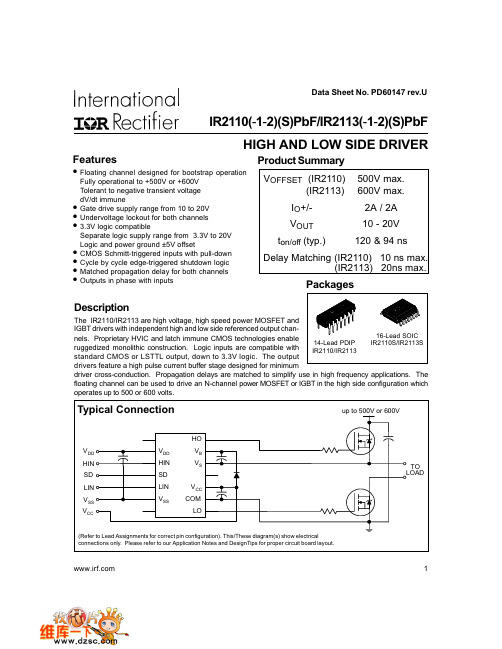

IR2110.PDF

IR2110(-1-2)(S)PbF/IR2113(-1-2)(S)PbF

HIGH AND LOW SIDE DRIVER

Features

• Floating channel designed for bootstrap operation

Fully operational to +500V or +600V

14-Lead PDIP IR2110/IR2113

16-Lead SOIC IR2110S/IR2113S

drivers feature a high pulse current buffer stage designed for minimum

driver cross-conduction. Propagation delays are matched to simplify use in high frequency applications. The

Product Summary

VOFFSET (IR2110) 500V max. (IR2113) 600V max.

IO+/-

2A / 2A

VOUT

10 - 20V

ton/off (typ.)

120 & 94 ns

Delay Matching (IR2110) 10 ns max. (IR2113) 20ns max.

Symbol

ton toff tsd tr tf MT

Definition

Turn-on propagation delay

Turn-off propagation delay

Shutdown propagation delay

74LVC245A_04中文资料

1/12July 2004s 5V TOLERANT INPUTSs HIGH SPEED: t PD = 6.3ns (MAX.) at V CC = 3V sPOWER DOWN PROTECTION ON INPUTS AND OUTPUTSsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 24mA (MIN) at V CC = 3Vs PCI BUS LEVELS GUARANTEED AT 24 mA sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 1.65V to 3.6V (1.2V Data Retention)sPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 245sLATCH-UP PERFORMANCE EXCEEDS 500mA (JESD 17)sESD PERFORMANCE:HBM > 2000V (MIL STD 883 method 3015); MM > 200VDESCRIPTIONThe 74LVC245A is a low voltage CMOS OCTAL BUS TRANSCEIVER (3-STATE) fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology. It is ideal for 1.65 to 3.6V CC operations and low power and low noise applications.This IC is intended for two-way asynchronous communication between data buses and the direction of data transmission is determined by DIR input. The enable input G can be used to disable the device so that the buses are effectively isolated.It has more speed performance at 3.3V than 5V AC/ACT family, combined with a lower power consumption.All inputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.All floating bus terminals during High Z State must be held HIGH or LOW.74LVC245ALOW VOLTAGE CMOS OCTAL BUS TRANSCEIVER(NOT INVERTED) HIGH PERFORMANCE.Table 1: Order CodesPACKAGE T & R SOP 74LVC245AMTR TSSOP74LVC245ATTR74LVC245A2/12Figure 2: Input And Output Equivalent CircuitTable 2: Pin DescriptionTable 3: Truth TableX : Don’t CareZ : High ImpedanceTable 4: Absolute Maximum RatingsAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied1) I O absolute maximum rating must be observed 2) V O< GNDPIN N°SYMBOL NAME AND FUNCTION 1DIR Directional Control 2, 3, 4, 5, 6, 7, 8, 9A1 to A8Data Inputs/Outputs 18, 17, 16, 15, 14, 13, 12, 11B1 to B8Data Inputs/Outputs19GOutput Enable Input 10GND Ground (0V)20V CCPositive Supply VoltageINPUTS FUNCTION OUTPUT G DIR A BUSB BUSYn L L OUTPUT INPUT A = B L H INPUT OUTPUT B = A HXZ ZZSymbol ParameterValue Unit V CC Supply Voltage -0.5 to +7.0V V I DC Input Voltage-0.5 to +7.0V V O DC Output Voltage (High Impedance or V CC = 0V)-0.5 to +7.0V V O DC Output Voltage (High or Low State) (note 1)-0.5 to V CC + 0.5V I IK DC Input Diode Current- 50mA I OK DC Output Diode Current (note 2)- 50mA I O DC Output Current ± 50mA I CC or I GND DC V CC or Ground Current per Supply Pin± 100mA T stg Storage Temperature -65 to +150°C T LLead Temperature (10 sec)300°C74LVC245A3/12Table 5: Recommended Operating Conditions1) Truth Table guaranteed: 1.2V to 3.6V 2) V IN from 0.8V to 2V at V CC = 3.0VTable 6: DC SpecificationsSymbol ParameterValue Unit V CC Supply Voltage (note 1) 1.65 to 3.6V V I Input Voltage0 to 5.5V V O Output Voltage (High Impedance or V CC = 0V)0 to 5.5V V O Output Voltage (High or Low State)0 to V CC V I OH , I OL High or Low Level Output Current (V CC = 3.0 to 3.6V)± 24mA I OH , I OL High or Low Level Output Current (V CC = 2.7 to 3.0V)± 12mA I OH , I OL High or Low Level Output Current (V CC = 2.3 to 2.7V)±8mA I OH , I OL High or Low Level Output Current (V CC = 1.65 to 2.3V)±4mA T op Operating Temperature-55 to 125°C dt/dvInput Rise and Fall Time (note 2)0 to 10ns/VSymbolParameterTest ConditionValueUnitV CC (V)-40 to 85 °C -55 to 125 °C Min.Max.Min.Max.V IHHigh Level Input Voltage 1.65 to 1.950.65V CC0.65V CC V2.3 to 2.7 1.7 1.72.7 to3.622V ILLow Level Input Voltage1.65 to 1.950.35V CC0.35V CC V 2.3 to 2.70.70.72.7 to 3.60.80.8V OHHigh Level Output Voltage1.65 to 3.6I O =-100 µA V CC -0.2V CC -0.2V1.65I O =-4 mA 1.2 1.22.3I O =-8 mA 1.7 1.72.7I O =-12 mA 2.2 2.23.0I O =-18 mA 2.4 2.43.0I O =-24 mA 2.22.2V OLLow Level Output Voltage1.65 to 3.6I O =100 µA 0.20.2V 1.65I O =4 mA 0.450.452.3I O =8 mA 0.70.72.7I O =12 mA 0.40.43.0I O =24 mA 0.550.55I I Input Leakage Current 3.6V I = 0 to 5.5V ± 5± 5µA I off Power Off Leakage Current0V I or V O = 5.5V 1010µA I OZHigh Impedance Output Leakage Current3.6V I = V IH orV IL V O = 0 to 5.5V ± 10± 10µA I CCQuiescent Supply Current3.6V I = V CC or GND1010µA V I or V O = 3.6 to5.5V± 10± 10∆I CCI CC incr. per Input2.7 to3.6V IH = V CC -0.6V500500µA74LVC245A4/12Table 7: Dynamic Switching Characteristics1) Number of output defined as "n". Measured with "n-1" outputs switching from HIGH to LOW or LOW to HIGH. The remaining output is measured in the LOW state.Table 8: AC Electrical Characteristics1) Skew is defined as the absolute value of the difference between the actual propagation delay for any two outputs of the same device switch-ing in the same direction, either HIGH or LOW (t OSLH = | t PLHm - t PLHn |, t OSHL = | t PHLm - t PHLn |2) Parameter guaranteed by designTable 9: Capacitive Characteristics1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption without load. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC /n (per circuit)SymbolParameterTest ConditionValue UnitV CC (V)T A = 25 °C Min.Typ.Max.V OLP Dynamic Low Level Quiet Output (note 1)3.3C L = 50pFV IL = 0V, V IH = 3.3V0.8V V OLV-0.8SymbolParameterTest ConditionValueUnitV CC (V)C L (pF)R L (Ω)t s = t r (ns)-40 to 85 °C -55 to 125 °C Min.Max.Min.Max.t PLH t PHLPropagation Delay Time1.65 to 1.953010002.0 2.09.0 2.012ns2.3 to 2.730500 2.0 2.08.0 2.010.52.750500 2.5 1.57.3 1.58.83.0 to 3.650500 2.5 1.0 6.3 1.07.6t PZL t PZHOutput Enable Time 1.65 to 1.95301000 2.0 2.012 2.016ns2.3 to 2.730500 2.0 2.09.5 2.012.52.750500 2.5 1.09.0 1.0113.0 to 3.650500 2.5 1.08.5 1.010t PLZ t PHZOutput Disable Time 1.65 to 1.95301000 2.0 2.011 2.014ns2.3 to 2.730500 2.0 2.09.0 2.0122.750500 2.5 2.08.5 2.0103.0 to 3.6505002.52.07.5 2.09.0t OSLH t OSHLOutput To Output Skew Time (note1, 2)2.7 to3.611nsSymbolParameterTest ConditionValue UnitV CC (V)T A = 25 °C Min.Typ.Max.C IN Input Capacitance4pF C PDPower Dissipation Capacitance (note 1)1.8f IN = 10MHz28pF 2.5303.33474LVC245A5/12Figure 3: Test CircuitR T = Z OUT of pulse generator (typically 50Ω)Table 10: Test Circuit And Waveform Symbol ValueFigure 4: Waveform - Propagation Delays (f=1MHz; 50% duty cycle)SymbolV CC1.65 to 1.95V2.3 to 2.7V 2.7V3.0 to 3.6V C L 30pF 30pF 50pF 50pF R L = R 11000Ω500Ω500Ω500ΩV S 2 x V CC 2 x V CC 6V 6V V IH V CC V CC 2.7V 2.7V V M VCC /2V CC /2 1.5V 1.5V V OH V CC V CC 3.0V 3.0V V X V OL + 0.15V V OL + 0.15V V OL + 0.3V V OL + 0.3V VY V OH - 0.15V V OH - 0.15V V OH - 0.3V V OH - 0.3V t r = t r<2.0ns<2.0ns<2.5ns<2.5ns74LVC245AFigure 5: Waveform - Output Enable And Disable Time (f=1MHz; 50% duty cycle)6/1274LVC245A7/12DIM.mm.inch MIN.TYPMAX.MIN.TYP.MAX.A 2.35 2.650.0930.104A10.10.300.0040.012B 0.330.510.0130.020C 0.230.320.0090.013D 12.6013.000.4960.512E 7.47.60.2910.299e 1.270.050H 10.0010.650.3940.419h 0.250.750.0100.030L 0.4 1.270.0160.050k 0°8°0°8°ddd0.1000.004SO-20 MECHANICAL DATA0016022D74LVC245A8/12DIM.mm.inchMIN.TYPMAX.MIN.TYP.MAX.A 1.20.047A10.050.150.0020.0040.006A20.81 1.050.0310.0390.041b 0.190.300.0070.012c 0.090.200.0040.0079D 6.4 6.5 6.60.2520.2560.260E 6.2 6.4 6.60.2440.2520.260E1 4.34.4 4.480.1690.1730.176e 0.65 BSC0.0256 BSCK 0˚8˚0˚8˚L0.450.600.750.0180.0240.030TSSOP20 MECHANICAL DATAcEbA2AE1D1PIN 1 IDENTIFICATIONA1LK e0087225C74LVC245A Tape & Reel SO-20 MECHANICAL DATAmm.inchDIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992C12.813.20.5040.519D20.20.795N60 2.362T30.4 1.197Ao10.8110.4250.433Bo13.213.40.5200.528Ko 3.1 3.30.1220.130Po 3.9 4.10.1530.161P11.912.10.4680.4769/1274LVC245ATape & Reel TSSOP20 MECHANICAL DATAmm.inch DIM.MIN.TYP MAX.MIN.TYP.MAX.A33012.992 C12.813.20.5040.519 D20.20.795N60 2.362T22.40.882 Ao 6.870.2680.276 Bo 6.97.10.2720.280 Ko 1.7 1.90.0670.075 Po 3.9 4.10.1530.161 P11.912.10.4680.47610/1274LVC245A Table 11: Revision HistoryDate Revision Description of Changes26-Jul-20044Ordering Codes Revision - pag. 1.11/1274LVC245AInformation furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.The ST logo is a registered trademark of STMicroelectronicsAll other names are the property of their respective owners© 2004 STMicroelectronics - All Rights ReservedSTMicroelectronics group of companiesAustralia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America12/12。

ECN

New Logic Family Achieves Highest Speeds at Lower Voltagesby Stephen Nolan and Ji Park, Texas InstrumentsWorkstations, servers, and other high-performance systems are reaching new heights in innovation daily. As these productsimprove, bus- and memory-interface devices must keep paceand must advance to greater speeds as well. Moreover, thesesystems require that this increased speed be coupled with lower power consumption. This imperative usually means a lowervoltage node. Also to function as viable solutions, these logicdevices must reach these faster and faster speeds withoutsacrificing signal integrity.Texas Instruments’ new logic family, the AVC (AdvancedVery-low-voltage CMOS) family, delivers both high speed and low power without reducing signal quality. AVC logic follows on the heels of TI’s ALVC (Advanced Low Voltage CMOS) logic, which helped engineers make the transition from 5-V to 3.3-Vdesigns beginning in 1994. Many designs are now migratingfrom 3.3-V to 2.5-V, creating new design challenges.Complicating this transition is the industry’s appetite for higher system speeds, which has driven bus speeds above the125-MHz mark (Figure 1). The AVC logic family is the firstlogic family in the industry with propagation delays of less than two nanoseconds (2 ns).High-speed logic usually generates significant undershoot andovershoot noise from the very fast signal transitions. Seriesdamping resistors are sometimes used to reduce electrical noise; but resistors, whether they are internal or external to the logic,also slow the speed of the signals through the circuitry. TheAVC family does not require series damping resistors to reduce electrical noise (Figure 2).TI has developed a unique innovation called Dynamic OutputControl (DOC™) (patent pending), which gives AVC logic "the best of both worlds." Specifically, AVC logic achieves very high signaling speeds because the circuitry behaves as though therewere no resistors in the output when a signal transition is taking place. Then, as the signal transition nears completion, circuitry is automatically activated that behaves as though there were series damping resistors on the output. This capability dramaticallyminimizes the signal undershoot or overshoot and effectivelymuffles electrical noise.In addition to high-speed and low electrical noise, AVCconsumes little power and is easy to design into a mixed-voltage system. Although AVC is very low power with its optimization for 2.5-V systems, it remains compatible with 3.3-V or even1.8-V components as well. In fact, AVC is operational from1.65 V to 3.6 V. Moreover, AVC logic can save battery lifesince it has a feature that supports partial power off--thusallowing the power to be turned off to portions of a systemwhen those sections are not in use.The AVC family is over-voltage tolerant at both the inputs and the outputs--a feature which helps the engineer who is facedwith a mixed voltage mode design. For example, if a design calls for interfacing a 2.5-V memory controller with 3.3-V memories, all the designer needs to do is place an AVC transceiver inbetween the memory controller and the memories. The AVCdevice, powered at 2.5 V, will provide reliable bi-directionaldata communication between the devices at these two voltagenodes. The data from the 3.3-V memories are accepted at theinputs of the AVC transceiver without any problems, since the transceiver’s inputs are over-voltage tolerant. Also, an AVCdriver or register device, powered at 1.8 V, can be used toprovide uni-directional data communication from devices at the 3.3-V or the 2.5-V nodes to devices at 1.8 V.Dynamic Output Control (DOC)The way the AVC family’s DOC circuitry handles high-speedsignals is similar to the way a race car driver negotiates an oval track. On the straight-aways, the driver can accelerate tomaximum speed. But, as he approaches a curve in the track, the driver must slow down or risk losing control of the car. In much the same way, DOC circuitry (Figure 3) allows the signaling to accelerate to its maximum speed during the transition from a low to a high state (or from a high to a low). Then, in much the same way that a race car driver eases off the accelerator as henegotiates a curve, the DOC circuitry reduces the power of the electrical signal when the transition nears completion. Thisreduction minimizes overshoot and undershoot noise that would otherwise be generated by a high-speed signal transition.Specifically, DOC lowers the output impedance of the circuitry at the beginning of a signal transition to drive the load at highspeeds. Then, as the end of transition is near, DOCautomatically raises the impedance to roll-off the signal and toreduce noise.(figure 4)The DOC effectively consists oftwo parallel drivers and animpedance control circuit (ZCC)that monitors the output signal.When the impedance controlcircuit senses that more current isneeded, the outputs of both theparallel drivers are enabled,thereby reducing the outputimpedance. As the signal passes through the threshold during a transition, the impedance control circuit disables the output ofone of the drivers, thereby increasing the output impedance.Obviously, the driver that is disabled does not contribute anyadditional drive current or loading to the output.Bus Hold™(figure 5)The bus hold feature was alsoincluded in the AVC family of logicdevices. Bus hold helps solve theproblem of floating inputs andeliminates the need for pull-up orpull-down resistors. With thetotem-pole structure that characterizesthe inputs of CMOS devices, theinput must be held as close to VCC orGND rails as possible. Precautions should be taken to preventthe input voltage from floating near the threshold voltagebecause this eventuality would bias both input transistors on and would create undesirably high ICC currents at the VCC pin of the device. One possible method would be to use pull-up orpull-down resistors, but these are costly and take up additionalcircuit-board area. An alternative solution is to use devices in the AVC family that utilize the optional bus-hold circuit at the inputs. AVC devices with bus-hold circuitry are designated AVCH.The bus-hold circuit consists of two series inverters with theoutput fed back to the input through a resistor. This arrangement provides a weak positive feedback by sinking or sourcingcurrent to the input node. The bus-hold circuit consists of twoseries inverters with the output fed back to the input through aresistor. This arrangement provides a weak positive feedbackby sinking or sourcing current to the input node. The bus-holdcell holds the input at its last known valid logic state until thisstate is forcibly changed by a driving circuit.A Full Family of LogicA comprehensive selection of AVC devices is planned forintroduction over the next two years. The AVC productportfolio will be comprised of gate, octal, Widebus™, andWidebus+™ logic devices. A complete selection of differentdevice types such as bus drivers and transceivers, buffers,flip-flops, latches, and address drivers will eventually find their way into the AVC family. Samples of the first four members of the AVC logic family should be available from TexasInstruments and its authorized distributors in the fourth quarter of 1998. Part numbers and anticipated resale pricing in quantitiesof 1000 are as follows: AVC16244 16-bit buffer $2.92,AVC16245 16-bit transceiver $2.92, AVC16373 16-bitD-type transparent latch $2.92, and AVC16374 16-bit D-typeflip-flop $2.92. Military versions of selected AVC functions are also planned.Top of PageAbout the AuthorsStephen Nolan is the senior applications engineer for TexasInstruments' CBT and CBTLV bus switches and the AVC(Advanced Very-low-voltage CMOS) logic family. Nolan hadpreviously worked in TI's BiPolar wafer fabrication family as a photo lithography engineer. He has a BS in electronicsengineering technology and a MS in electronics engineeringtechnology from Southeastern Oklahoma State University.Ji Park's Advanced Computing Solutions team at TI isresponsible for the strategic development of advanced logicdevices for PCs, workstations, and servers. Park received aBSEE from the University of Texas.。

比较器小信号延迟小信号仿真结果如...

东南大学模拟实训MPW流片报告课题名称:预放大再生比较器设计姓名:学号:指导老师:摘要比较器是电子系统中应用较为广泛的电路之一。

比较器的设计以开环高增益放大器的设计为基础。

虽然和运算放大器相比,比较器的应用范围相对狭窄,但比较器仍在很多应用中不可或缺,尤其在模数转换器(Analog-to-digital converters,简称ADC)中。

比较器作为流水线型ADC的关键模块,其速度、功耗等性能对整个模数转换器的速度和功耗都有着至关重要的影响。

在各种比较器结构中,预放大再生比较器速度快、功耗低、失调电压小,被广泛应用于高速比较器。

本文基于预放大再生理论,采用TSMC 3.3V 0.35μm CMOS 工艺,设计一种适用于流水线型ADC 的高速低功耗比较器电路。

该比较器由前置放大器,比较器和SR锁存电路构成。

经过Cadence软件下的Virtuoso 平台对电路进行前仿真,比较器工作电压为3.3V,共模输入电压1.6V,在500MHZ 的时钟频率下,能够实现精度为30uV的比较,功耗为5.6mW,传输时延为4ns,翻转电压0.4mV。

关键词:比较器,预放大锁存,高速低功耗AbstractComparator is one of the most important units widely used in electronic systems. The design of a comparator is based on loop gain amplifier. Compared with amplifiers, comparators are not that widely used, but it is really necessary especially in Analog-to-digital converters (ADC). The comparator is a crucial part of ADC. Its speed and power have great impact on the characteristic of the whole ADC.Being one of various architectures, preamplifier-latch is widely used as high-speed comparator due to its high-speed, low-power and small offset voltage. Based on preamplifier-latch comparator, adopted TSMC 0.13μm CMOS process, a high-speed, low-power comparator applied for pipelined-ADC is proposed in this paper. This comparator consists of three blocks:pre-amplifier, comparator and SR latch. The pre-simulations use Virtuoso simulation of Cadence, the comparator’s work voltage is 1.8V, and common input voltage is 1.6V, the simulation results indicate that the resolution of the comparator is 30uV, transmission delay is less than 4ns and power dissipation is about 5.6mW under the 500MHZ clock.Key W ords: Comparator, Preamplifier-latch, High-speed low-power目录摘要 (I)Abstract (II)第一章绪论 (1)1.1 背景 (1)1.2 本文的研究内容和结构安排 (1)第二章比较器电路的基本模型 (2)2.1 比较器电路的系统参数分析 (2)2.1.1 主要性能参数 (3)2.1.2 比较器静态分析 (5)2.1.3 比较器动态特性 (6)2.2 比较器的电路结构与分析模型 (7)2.2.1 开环比较器 (8)2.2.2 离散时间比较器 (9)2.2.3 高速比较器 (13)2.3 几种常见的比较器结构 (15)2.3.1 电阻分配式比较器 (15)2.3.2 差分对比较器 (16)2.3.3电荷分配型比较器 (16)2.4 小结 (17)第三章高速低功耗比较器设计 (18)3.1 前置放大器设计 (18)3.1.1 二极管负载差分放大器 (18)3.1.2 差分放大器的级联 (22)3.2 锁存比较器的结构 (24)3.2.1 两种锁存比较器的结构对比 (24)3.2.2 锁存器优化 (26)3.3 输出缓冲级设计 (28)3.4 比较器整体结构和参数 (30)3.5 小结 (31)第四章比较器电路功能仿真 (32)4.1 比较器的逻辑仿真 (32)4.2 比较器的速度与精度 (33)4.3 比较器的传输延迟 (35)4.4 比较器的翻转电压 (37)4.5 比较器的功耗 (38)4.6 小结 (38)第五章比较器的版图设计和后仿 (40)5.1 比较器的版图设计 (40)5.2 比较器的版图验证 (44)5.3 比较器的后仿真 (45)5.4 小结 (47)第六章总结和心得 (48)致谢 (50)参考文献 (51)第一章绪论1.1 背景从国际和国内发展情况来看,比较器的研究趋势就是高速度、低功耗和高温度等。

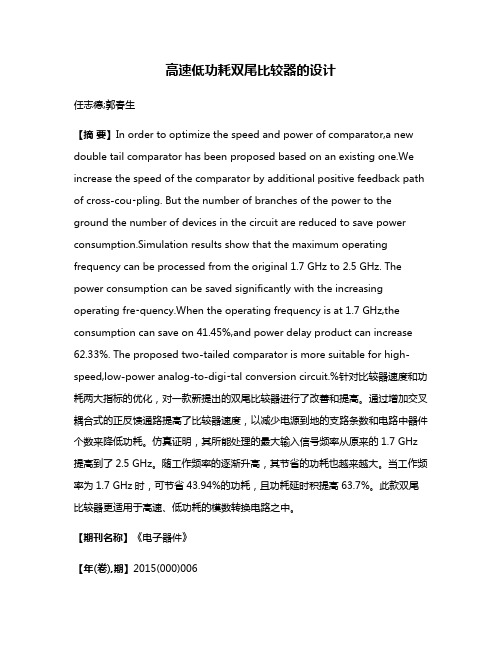

高速低功耗双尾比较器的设计

高速低功耗双尾比较器的设计任志德;郭春生【摘要】In order to optimize the speed and power of comparator,a new double tail comparator has been proposed based on an existing one.We increase the speed of the comparator by additional positive feedback path of cross-cou⁃pling. But the number of branches of the power to the ground the number of devices in the circuit are reduced to save power consumption.Simulation results show that the maximum operating frequency can be processed from the original 1.7 GHz to 2.5 GHz. The power consumption can be saved significantly with the increasing operating fre⁃quency.When the operating frequency is at 1.7 GHz,the consumption can save on 41.45%,and power delay product can increase 62.33%. The proposed two-tailed comparator is more suitable for high-speed,low-power analog-to-digi⁃tal conversion circuit.%针对比较器速度和功耗两大指标的优化,对一款新提出的双尾比较器进行了改善和提高。

高速低功耗CMOS动态锁存比较器的设计

高速低功耗CMOS动态锁存比较器的设计李靖坤;杨骁;陈国晏;娄付军;邱伟彬【摘要】A high-speed low-power dynamic latched comparator including a pre-amplifier,a latched compara-tor and a SR-latch is presented.A novel reset circuit that only has one PMOS transistor is adopted for the latched comparator,which can realize the electric charge reusing.As a result,the delay and power consump-tion are reduced.The parasitic capacitance of input transistors of the SR-latch acts as the load capacitance of the latched comparator.An improved method for the SR-latch is adopted to avoid shifting of the input offset voltage caused by the load capacitance mismatch of the latched comparator.The comparator is implemented with TSMC 0.18 μm complementary metal-oxide-semiconductor(CMOS)technology.Simulation results show that a sensitivity of 0.3 mV and a maximum input offset of 8 mV are achieved with the operating frequency of 1 GHz,and the power consumption is 0.2 mW with 1 .8 V supply.The dynamic latched comparator is concise and simple to implement,and has features of low power.%提出一种高速低功耗动态锁存比较器,电路包含预放大器、锁存比较器和SR 锁存器 3 部分.采用一种新的锁存比较器复位电路,该电路仅由一个P沟道金属氧化物半导体(PMOS)管构成,实现电荷的再利用,减小了延迟,降低了功耗.SR锁存器输入端口的寄生电容为锁存比较器的负载电容,对 SR 锁存器的输入端口进行改进,避免由于锁存比较器的负载电容失配导致的输入失调电压偏移的问题.电路采用TSMC 0.18 μm 互补金属氧化物半导体(CMOS)工艺实现.结果表明:电源电压为1 .8 V,时钟频率为1 GHz时,比较器精度达0.3 mV;最大输入失调电压为8 mV,功耗为0.2 mW;该比较器具有电路简单易实现、功耗低的特点.【期刊名称】《华侨大学学报(自然科学版)》【年(卷),期】2018(039)004【总页数】5页(P618-622)【关键词】动态锁存比较器;互补金属氧化物半导体;高速低功耗;失调电压【作者】李靖坤;杨骁;陈国晏;娄付军;邱伟彬【作者单位】华侨大学信息科学与工程学院,福建厦门 361021;厦门市ASIC与系统重点实验室,福建厦门 361008;华侨大学信息科学与工程学院,福建厦门361021;厦门市ASIC与系统重点实验室,福建厦门 361008;华侨大学信息科学与工程学院,福建厦门 361021;厦门市ASIC与系统重点实验室,福建厦门 361008;华侨大学信息科学与工程学院,福建厦门 361021;厦门市ASIC与系统重点实验室,福建厦门 361008;华侨大学信息科学与工程学院,福建厦门 361021;厦门市ASIC与系统重点实验室,福建厦门 361008【正文语种】中文【中图分类】TN432随着现代通信和信号处理技术的广泛应用,高速低功耗的电子设备成为市场的主流.比较器作为模数转换器、数据接收器等系统不可缺少的模块,对其系统的性能指标有着重要的影响[1].常见的比较器有静态锁存比较器[2-3]和动态锁存比较器[4-8].其中,静态锁存比较器无论是在复位阶段还是再生阶段都存在静态电流,速度较慢、功耗较大[3].动态锁存比较器采用一对背靠背交叉耦合的反相器构成正反馈,使小的差分输入信号迅速放大到满摆幅的数字信号输出,具有速度快、功耗低、高输入阻抗、满输出摆幅等优点,在高速电路中得到了广泛地应用[6].然而,传统动态锁存比较器存在失调电压高、回踢噪声大的缺点.在锁存比较器之前,增加一级预放大器可以减小失调电压、回踢噪声的影响.本文在传统动态锁存比较器的基础上,设计一种高速低功耗互补金属氧化物半导体(CMOS)动态锁存比较器.图1 预放大器和锁存比较器电路Fig.1 Pre-amplifier and latched comparator circuit1 比较器电路分析与设计在文献[5]的基础上提出的预放大器和锁存比较器电路,如图1所示.用P沟道金属氧化物半导体(PMOS)管MP5替代原来的复位管MN8,MN9(虚线所示),实现电荷再利用,减小延迟时间并降低功耗.图1中:MN1~MN3及MP1,MP2构成预放大器;MN4~MN7及MP3~MP7构成锁存比较器;MP5为复位管;时钟(CLK)为低电平时,MP5导通,使M,N两点的电压相等,避免M,N两点残余电荷不相等,从而影响比较器的精度.图2 SR锁存器电路Fig.2 SR latch circuitSR锁存器电路,如图2所示.SR锁存器是由两个首尾交叉连接的或非门构成.若采用图2中NOR1的A输入端和NOR2的B输入端作为SR锁存器的输入引脚,则会造成锁存比较器的两个输出节点out+和out-负载电容不同,这会产生比较器失调电压偏移的问题[9].文中采用两个或非门的同一端引脚B作为锁存比较器的负载,且B输入端连接的是或非门中两个不存在体效应的金属氧化物半导体场效应晶体(MOS)管MN1和MP2,从而避免比较器输入失调电压偏移的问题.文中比较器的工作原理如下所述.其中,N沟道金属氧化物半导体(NMOS)管的阈值电压为VTHN;PMOS管的阈值电压为VTHP.1) 复位阶段.CLK为低电平,MOS管MN1截止,MP1,MP2导通,预放大器将节点Di(Di+和Di-)充电至VDD;MP6,MP7截止,MN4,MN7导通,节点out+,out-被下拉至零电位(GND),SR锁存器处于保持状态,比较器的输出保持上一个状态不变;复位管MP5导通,使节点M,N的电压相等,MP3,MN5和MP4,MN6为交叉耦合的反相器,此时均截止.2) 再生阶段.CLK为高电平,MOS管MN1导通,MP1,MP2截止,节点Di-和Di+根据输入信号VIP和VIN的不同,以不同的速率放电.记节点Di放电到VDD-|VTHP|的时间为T1,这段时间,MN2,MN3工作在饱和区.假设比较器的差模输入信号很小,则流过MN2,MN3的电流近似相等,记为ID1,忽略二级效应,有(1)式(1)中:(W/L)1为MN2,MN3的宽长比;VIP,VIN为输入电压信号;VS为MN1导通时节点S的电压.节点Di的电压随时间变化可表示为(2)因此,时间T1为T1=(|VTHP|CDi)/ID1.(3)式(3)中:CDi为节点Di+和Di-的寄生电容,CDi=CDi+=CDi-.当VDi下降到VDD-|VTHP|,MP6,MP7管开始导通并工作在饱和区,忽略二级效应,流过MP6,MP7的电流为(4)式(4)中:(W/L)2为MP6,MP7的宽长比.MP6,MP7以电流ID2分别对节点M,N进行充电.此时,MP3,MP4仍然截止,Vout(Vout+和Vout-)等于GND,MN4,MN7工作在深线性区,电流几乎为0.当VM,VN充电到|VTHP|时,MP3,MP4导通,记VM,VN达到|VTHP|的时间为T2,同理有(5)式(5)中:CM,N为节点M,N的寄生电容,CM,N=CM=CN.MP3,MP4导通后,MN4,MN7工作在线性区,流过MN4和MN7的电流为(6)式(6)中:(W/L)3为MN4,MN7的宽长比.节点out+和out-以电流ID2-ID3充电,记Vout达到VTHN的时间为T3,即T3=VTHNCout/(ID2-ID3).(7)式(7)中:Cout为节点out+和out-的寄生电容,Cout=Cout+=Cout-.Vout达到VTHN后,MN5,MN6开始导通,由MP3,MN5和MP4,MN6构成的锁存器开始工作.由于节点Di-和Di+以不同的速率放电,同一时间VDi-和VDi+必然会有一个微小的差值,进而造成Vout+和Vout-产生压差,记为ΔVout,这个压差作为锁存器的初始压差,会被迅速放大到VDD-GND,驱动SR锁存器置0或置1,即比较器的输出.锁存器再生过程需要的时间记为T4[10],则有(8)τ为锁存器的时间常数,即(9)式(9)中:gm为锁存器的跨导.由以上的分析可知,比较器总的延迟时间约为Tdelay=T1+T2+T3+T4.(10)3) 比较器再次复位.CLK跳变为低电平,MN1截止,MP1,MP2导通,节点Di被充电至VDD;MP6,MP7截止,MN4,MN7导通,节点out+和out-通过MN4和MN7放电到GND;节点M,N的电压因为复位管MP5的导通而相等,且分别通过MP3,MN4支路及MP4,MN7支路放电;当节点M,N的电压放电至|VTHP|时,MP3,MP4截止,忽略亚阈值导电特性,M,N的电压最终保持在|VTHP|不变.当比较器再次处于再生状态,由于节点M,N的电压已经为|VTHP|,所以比较器在再生阶段节约了时间T2,且避免再次对节点M,N进行充电.因此,相较于文献[5]将M,N两点的电压放电到0的做法,文中实现了电荷的再利用,减小了比较器的延迟时间.比较器总的延迟时间缩减为Td=T1+T3+T4.(11)比较器每个周期节约电荷量,即Q=C×V=2×CM,N×|VTHP|.(12)2 电路仿真结果对文中提出的比较器和文献[5]的架构进行设计与仿真.两个电路都采用TSMC 0.18μm CMOS工艺实现,复位管MP5采用的尺寸和文献[5]中复位管MN8,MN9采用的尺寸均为600 nm/180 nm,其他晶体管一一对应.仿真条件:电源电压VDD为1.8 V;时钟频率CLK为1 GHz;温度为27 ℃;工艺角为TT;比较器输入共模电压VCM为0.9 V,输出电容负载为5 fF.比较器的延迟时间(t)和功耗与输入电压的关系(VDD=1.8 V,VCM=0.9 V),如图3所示.以输入电压ΔVIN=50 mV为例,文献[5]架构比较器的延迟时间为282.85 ps,文中比较器的延时为246.13 ps,改进后的比较器延迟时间减小了36.72 ps,速度提升约13%;文献[5]架构比较器的平均动态功耗为198.8 μW·GHz-1,文中为175.6 μW·GHz-1,平均动态功耗降低了11.7%(此处不包含SR锁存器的功耗).比较器延迟时间和功耗与电源电压的关系(ΔVIN= 50 mV,VCM= VDD -0.4 V),结果如图4所示.(a) 延迟时间与输入电压 (b) 功耗与输入电压图3 比较器延迟时间和功耗与输入电压的关系(VDD=1.8 V,VCM=0.9 V)Fig.3 Comparators′ delay and power consumption versus input voltage (VDD=1.8 V,VCM=0.9 V)(a) 延迟时间与电源电压 (b) 功耗与电源电压图4 比较器延迟时间和功耗与电源电压的关系(ΔVIN= 50 mV,VCM= VDD -0.4 V)Fig.4 Comparators′ delay and power consumption versus supply voltage (ΔVIN= 50 mV,VCM= VDD -0.4 V)图5 文中比较器最坏情况仿真波形Fig.5 Simulation waveform of proposed comparator in worst case在较低的电源电压下,文中比较器的延时相较于文献[5]架构的比较器最多减小了18.7%;随着电源电压的升高,文中比较器的低功耗优势逐渐增大.在不同温度(-40~125 ℃)和工艺角(FF,TT,SS,FS,SF)下对文中的比较器进行仿真.仿真结果表明:温度为125 ℃,工艺角为SS时,出现最坏情况.此时的瞬态仿真波形,如图5所示.由图5可知:比较器可分辨的最小电压为0.3 mV,延迟时间为729.595 ps.对整个比较器进行100次Monte carlo分析仿真,SR锁存器的输入引脚改进前后输入失调电压(Voffset)的仿真结果,如图6所示.图6中:Vmu为平均值;Vsd 为标准偏差;N为仿真次数;η为概率.由图6可知:SR锁存器的输入引脚改进前,比较器的输入失调电压呈现整体偏移的情况,最大达到14 mV;SR锁存器的输入引脚改进后,失调电压平均值为0.65 mV,标准偏差为3.96 mV,失调电压集中分布在-8~8 mV.(a) SR锁存器改进前 (b) SR锁存器改进后图6 比较器失调电压分布Fig.6 Distribution of comparator′s offset voltage文中比较器与部分文献比较器的性能指标对比,如表1所示.由表1可知:文中比较器在功耗、失调电压等方面有一定优势,适合于高速低功耗的应用.表1 比较器性能指标对比Tab.1 Performance index comparisons of comparators指标特征尺寸/μmVDD/V平均动态功耗/μW·GHz-1Voffset/mV文献[3]0.181.224 600.0 12.5文献[4]0.181.8610.012.0文献[7]0.181.8250.010.0文中0.181.8200.08.03 结束语提出一种高速低功耗动态锁存比较器.锁存比较器的复位电路仅由一个PMOS管组成,实现了电荷的再利用,减小了延迟,降低了功耗.对SR锁存器的输入端口改进后,避免了比较器输入失调电压偏移的问题.电路采用TSMC 0.18 μm CMOS工艺实现,在电源电压1.8 V,时钟频率1 GHz的条件下,比较器精度为0.3 mV,最大输入失调电压为8 mV,功耗为0.2 mW,适合于高速低功耗应用中.参考文献:【相关文献】[1] SCHINKEL D,MENSINK E,KLUMPERINK E A M,et al.A 3-Gb/s/ch transceiver for 10-mm uninterrupted RC-limited global on-chip interconnects[J].Journal of Solid-State Circuits,2006,41(1):297-306.[2] SHEIKHAEI S,MIRABBASI S,IVANOV A.A 0.35 μm CMOS comparator circuit for high-speed ADC applications[C]∥International Symposium on Circuits and Systems.Kobe:IEEE Press,2005:6134-6137.[3] FAHMY G A,POKHAREL R K,KANAYA H,et al.A 1.2 V 246 μW CMOS latched comparator with neutralization technique for reducing kickback noise[C]∥IEEE Region 10 Conference.Fukuoka:IEEE Press,2010:1162-1165.DOI:10.1109/TENCON.2010.5686392. [4] 吴笑峰,刘红侠,石立春,等.新型高速低功耗CMOS动态比较器的特性分析[J].中南大学学报(自然科学版),2009,40(5):1354-1359.[5] MIYAHARA M,ASADA Y,PAIK D,et al.A low-noise self-calibrating dynamic comparator for high-speed ADCs[C]∥Asian Solid-State Circuits Conference.Fukuoka:IEEEPress,2008:269-272.[6] JEON H J,KIM Y B.A novel low-power, low-offset, and high-speed CMOS dynamic latched comparator[J].Analog Integrated Circuits and Signal Processing,2012,70(3):337-346.DOI:10.1007/s10470-011-9687-5.[7] WONG K L J,YANG C K K.Offset compensation in comparators with minimum input-referred supply noise[J].Journal of Solid-State Circuits,2004,37(5):837-840.DOI:10.1109/JSSC.2004.826317.[8] SCHINKEL D,MENSINK E,KLUMPERINK E,et al.A double-tail latch-type voltage sense amplifier with 18 ps setup+hold time[C]∥International S olid-State Circuits Conference.California:IEEE Press,2007:314-605.[9] NIKOOZADEH A,MURMANN B.An analysis of latch comparator offset due to load capacitor mismatch[J].Transactions on Circuits and Systems Ⅱ: ExpressBriefs,2006,53(12):1398-1402.[10] RAZAVI B,WOOLEY B A.Design techniques for high-speed, high-resolution comparators[J].Journal of Solid-State Circuits,1993,27(12):1916-1926.DOI:10.1109/4.173122.。

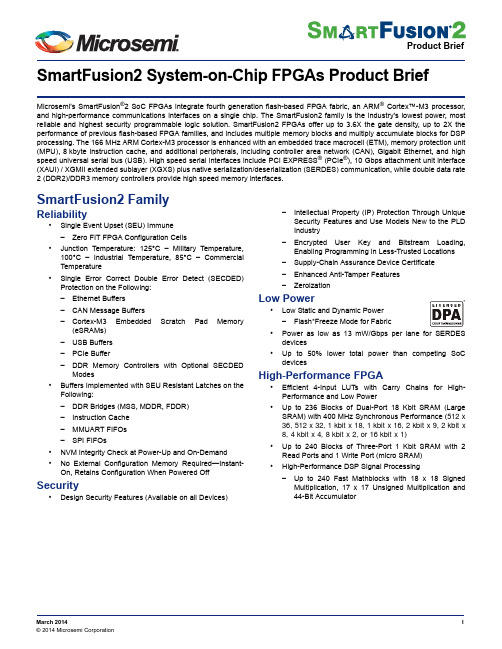

SmartFusion2_Brief_v15

• High-Performance DSP Signal Processing

– Up to 240 Fast Mathblocks with 18 x 18 Signed Multiplication, 17 x 17 Unsigned Multiplication and 44-Bit Accumulator

SmartFusion2 Family

Reliability

• Single Event Upset (SEU) Immune – Zero FIT FPGA Configuration Cells

• Junction Temperature: 125°C – Military Temperature, 100°C – Industrial Temperature, 85°C – Commercial Temperature

Integrated Analog PLLs

– Output Clock with 8 Output Phases and 45° Phase Difference (Multiply/Divide, and Delay Capabilities)

– Frequency: Input 1 MHz to 200 MHz, Output 20 MHz to 400 MHz

On, Retains Configuration When Powered Off

Security

• Design Security Features (Available on all Devices)

XC2C32A-6QFG32I中文资料

© 2004-2007 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at /legal.htm .All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.Features•Optimized for 1.8V systems-As fast as 3.8ns pin-to-pin logic delays -As low as 12 μA quiescent current •Industry’s best 0.18 micron CMOS CPLD-Optimized architecture for effective logic synthesis -Multi-voltage I/O operation: 1.5V through 3.3V •Available in multiple package options -32-land QFN with 21 user I/O -44-pin PLCC with 33 user I/O -44-pin VQFP with 33 user I/O -56-ball CP BGA with 33 user I/O -Pb-free available for all packages •Advanced system features-Fastest in system programming· 1.8V ISP using IEEE 1532 (JTAG) interface -IEEE1149.1 JTAG Boundary Scan Test -Optional Schmitt-trigger input (per pin)-Two separate I/O banks-RealDigital 100% CMOS product term generation -Flexible clocking modes-Optional DualEDGE triggered registers -Global signal options with macrocell control·Multiple global clocks with phase selection permacrocell ·Multiple global output enables ·Global set/reset-Efficient control term clocks, output enables andset/resets for each macrocell and shared across function blocks-Advanced design security-Open-drain output option for Wired-OR and LEDdrive-Optional configurable grounds on unused I/Os -Optional bus-hold, 3-state or weak pullup onselected I/O pins-Mixed I/O voltages compatible with 1.5V, 1.8V,2.5V, and3.3V logic levels -PLA architecture·Superior pinout retention ·100% product term routability across functionblock-Hot pluggableRefer to the CoolRunner™-II family data sheet for architec-ture description.DescriptionThe CoolRunner ™-II 32-macrocell device is designed for both high performance and low power applications. This lends power savings to high-end communication equipment and high speed to battery operated devices. Due to the low power stand-by and dynamic operation, overall system reli-ability is improvedThis device consists of two Function Blocks interconnected by a low power Advanced Interconnect Matrix (AIM). The AIM feeds 40 true and complement inputs to each Function Block. The Function Blocks consist of a 40 by 56 P-term PLA and 16 macrocells which contain numerous configura-tion bits that allow for combinational or registered modes of operation.Additionally, these registers can be globally reset or preset and configured as a D or T flip-flop or as a D latch. There are also multiple clock signals, both global and local product term types, configured on a per macrocell basis. Output pin configurations include slew rate limit, bus hold, pull-up,open drain and programmable grounds. A Schmitt trigger input is available on a per input pin basis. In addition to stor-ing macrocell output states, the macrocell registers may be configured as "direct input" registers to store signals directly from input pins.Clocking is available on a global or Function Block basis.Three global clocks are available for all Function Blocks as a synchronous clock source. Macrocell registers can be individually configured to power up to the zero or one state.A global set/reset control line is also available to asynchro-nously set or reset selected registers during operation.Additional local clock, synchronous clock-enable, asynchro-nous set/reset and output enable signals can be formed using product terms on a per-macrocell or per-Function Block basis.The CoolRunner-II 32-macrocell CPLD is I/O compatible with standard LVTTL and LVCMOS18, LVCMOS25, and LVCMOS33 (see Table 1). This device is also 1.5V I/O com-patible with the use of Schmitt-trigger inputs.Another feature that eases voltage translation is I/O bank-ing. Two I/O banks are available on the CoolRunner-II 32A macrocell device that permit easy interfacing to 3.3V, 2.5V,1.8V, and 1.5V devices.XC2C32A CoolRunner-II CPLDDS310 (v2.0) March 8, 2007Product Specification2DS310 (v2.0) March 8, 2007RealDigital Design TechnologyXilinx CoolRunner-II CPLDs are fabricated on a 0.18 micron process technology which is derived from leading edge FPGA product development. CoolRunner-II CPLDs employ RealDigital, a design technique that makes use of CMOS technology in both the fabrication and design methodology.RealDigital design technology employs a cascade of CMOS gates to implement sum of products instead of traditional sense amplifier methodology. Due to this technology, Xilinx CoolRunner-II CPLDs achieve both high performance and low power operation.Supported I/O StandardsThe CoolRunner-II 32 macrocell features both LVCMOS and LVTTL I/O implementations. See Table 1 for I/O stan-dard voltages. The LVTTL I/O standard is a general purpose EIA/JEDEC standard for 3.3V applications that use an LVTTL input buffer and Push-Pull output buffer. TheLVCMOS standard is used in 3.3V, 2.5V, 1.8V applications.CoolRunner-II CPLDs are also 1.5V I/O compatible with the use of Schmitt-trigger inputs.Table 1: I/O Standards for XC2C32A IOSTANDARD Attribute Output V CCIO Input V CCIO Input V REF BoardTermination Voltage V T LVTTL 3.3 3.3N/A N/A LVCMOS33 3.3 3.3N/A N/A LVCMOS25 2.5 2.5N/A N/A LVCMOS18 1.8 1.8N/A N/A LVCMOS15(1)1.51.5N/AN/A(1) LVCMOS15 requires Schmitt-trigger inputs.Figure 1: I CC vs FrequencyTable 2: I CC vs Frequency (LVCMOS 1.8V T A = 25°C)(1)Frequency (MHz)255075100150175200225250300Typical I CC (mA)0.0160.871.752.613.445.165.996.817.638.369.93Notes:1.16-bit up/down, resettable binary counter (one counter per function block).Recommended Operating ConditionsDC Electrical Characteristics (Over Recommended Operating Conditions)Absolute Maximum RatingsSymbol DescriptionValue Units V CC Supply voltage relative to ground –0.5 to 2.0V V CCIO Supply voltage for output drivers –0.5 to 4.0V V JTAG (2)JTAG input voltage limits –0.5 to 4.0V V CCAUX JTAG input supply voltage –0.5 to 4.0V V IN (1)Input voltage relative to ground –0.5 to 4.0V V TS (1)Voltage applied to 3-state output –0.5 to 4.0V T STG (3)Storage Temperature (ambient)–65 to +150°C T JJunction Temperature+150°CNotes:1.Maximum DC undershoot below GND must be limited to either 0.5V or 10 mA, whichever is easiest to achieve. During transitions,the device pins may undershoot to –2.0v or overshoot to +4.5V, provided this over or undershoot lasts less than 10ns and with the forcing current being limited to 200 mA.2.Valid over commercial temperature range.3.For soldering guidelines and thermal considerations, see the Device Packaging information on the Xilinx website. For Pb freepackages, see XAPP427.Symbol ParameterMin Max Units V CC Supply voltage for internal logic and input buffersCommercial T A = 0°C to +70°C 1.7 1.9V Industrial T A = –40°C to +85°C1.7 1.9V V CCIOSupply voltage for output drivers @ 3.3V operation 3.0 3.6V Supply voltage for output drivers @ 2.5V operation 2.3 2.7V Supply voltage for output drivers @ 1.8V operation 1.7 1.9V Supply voltage for output drivers @ 1.5V operation1.4 1.6V V CCAUXJTAG programming pins1.73.6VSymbol ParameterTest ConditionsTypical Max.Units I CCSB Standby current Commercial V CC = 1.9V, V CCIO = 3.6V 2290μA I CCSB Standby current Industrial V CC = 1.9V, V CCIO = 3.6V38150μA I CC (1)Dynamic current f = 1 MHz -0.25mA f = 50 MHz - 2.5mA C JTAG JTAG input capacitance f = 1 MHz -10pF C CLK Global clock input capacitance f = 1 MHz -12pF C IO I/O capacitance f = 1 MHz-10pF I IL (2)Input leakage current V IN = 0V or V CCIO to 3.9V -+/-1μA I IH (2)I/O High-Z leakageV IN = 0V or V CCIO to 3.9V-+/-1μANotes:1.16-bit up/down resettable binary counter (one per Function Block) tested at V CC = V CCIO = 1.9V.2.See Quality and Reliability section of the CoolRunner-II family data sheet.LVCMOS 3.3V and LVTTL 3.3V DC Voltage SpecificationsSymbol Parameter Test Conditions Min.Max.UnitsV CCIO Input source voltage 3.0 3.6VV IH High level input voltage2 3.9VV IL Low level input voltage–0.30.8VV OH High level output voltage I OH = –8 mA, V CCIO = 3V V CCIO – 0.4V-VI OH = –0.1 mA, V CCIO = 3V V CCIO – 0.2V-VV OL Low level output voltage I OL = 8 mA, V CCIO = 3V-0.4VI OL = 0.1 mA, V CCIO = 3V-0.2VLVCMOS 2.5V DC Voltage SpecificationsSymbol Parameter Test Conditions Min.Max.UnitsV CCIO Input source voltage 2.3 2.7VV IH High level input voltage 1.7V CCIO + 0.3(1)VV IL Low level input voltage–0.30.7VV OH High level output voltage I OH = –8 mA, V CCIO = 2.3V V CCIO – 0.4V-VI OH = –0.1 mA, V CCIO = 2.3V V CCIO – 0.2V-VV OL Low level output voltage I OL = 8 mA, V CCIO = 2.3V-0.4VI OL = 0.1mA, V CCIO = 2.3V-0.2V(1) The V IH Max value represents the JEDEC specification for LVCMOS25. The CoolRunner-II input buffer can tolerate up to 3.9V without physical damage.LVCMOS 1.8V DC Voltage SpecificationsSymbol Parameter Test Conditions Min.Max.Units V CCIO Input source voltage 1.7 1.9VV IH High level input voltage0.65 x V CCIO V CCIO + 0.3(1)VV IL Low level input voltage–0.30.35 x V CCIO VV OH High level output voltage I OH = –8 mA, V CCIO = 1.7V V CCIO – 0.45-VI OH = –0.1 mA, V CCIO = 1.7V V CCIO – 0.2-VV OL Low level output voltage I OL = 8 mA, V CCIO = 1.7V-0.45VI OL = 0.1 mA, V CCIO = 1.7V-0.2V(1) The V IH Max value represents the JEDEC specification for LVCMOS18. The CoolRunner-II input buffer can tolerate up to 3.9V without physical damage.LVCMOS1.5V DC Voltage Specifications(1)Symbol Parameter Test Conditions Min.Max.Units V CCIO Input source voltage 1.4 1.6VV T+Input hysteresis threshold voltage0.5 x V CCIO0.8 x V CCIO VV T-0.2 x V CCIO0.5 x V CCIO VV OH High level output voltage I OH = –8 mA, V CCIO = 1.4V V CCIO – 0.45-VI OH = –0.1 mA, V CCIO = 1.4V V CCIO – 0.2-V4DS310 (v2.0) March 8, 2007Schmitt Trigger Input DC Voltage SpecificationsAC Electrical Characteristics Over Recommended Operating ConditionsV OLLow level output voltageI OL = 8 mA, V CCIO = 1.4V -0.4V I OL = 0.1 mA, V CCIO = 1.4V-0.2VNotes:1.Hysteresis used on 1.5V inputs.Symbol ParameterTest ConditionsMin.Max.Units V CCIO Input source voltage1.4 3.9V V T+Input hysteresis threshold voltage0.5 x V CCIO 0.8 x V CCIO V V T-0.2 x V CCIO0.5 x V CCIOVSymbol Parameter-4-6Units Min.Max.Min.Max.T PD1Propagation delay single p-term - 3.8- 5.5ns T PD2Propagation delay OR array - 4.0- 6.0ns T SUD Direct input register clock setup time 1.7- 2.2-ns T SU1Setup time fast (single p-term) 1.9- 2.6-ns T SU2Setup time (OR array) 2.1- 3.1-ns T HD Direct input register hold time 0.0-0.0-ns T H P-term hold time 0.0-0.0-ns T CO Clock to output - 3.7- 4.7ns F TOGGLE (1)Internal toggle rate-500-300MHz F SYSTEM1(2)Maximum system frequency -323-200MHz F SYSTEM2(2)Maximum system frequency -303-182MHz F EXT1(3)Maximum external frequency -179-137MHz F EXT2(3)Maximum external frequency-172-128MHz T PSUD Direct input register p-term clock setup time 0.4-0.9-ns T PSU1P-term clock setup time (single p-term)0.6- 1.3-ns T PSU2P-term clock setup time (OR array)0.8- 1.8-ns T PHD Direct input register p-term clock hold time 1.5- 1.6-ns T PH P-term clock hold 1.3- 1.2-ns T PCO P-term clock to output- 5.0- 6.0ns T OE /T OD Global OE to output enable/disable - 4.7- 5.5ns T POE /T POD P-term OE to output enable/disable- 6.2- 6.7ns T MOE /T MOD Macrocell driven OE to output enable/disable - 6.2- 6.9ns T PAO P-term set/reset to output valid - 5.5- 6.8ns T AO Global set/reset to output valid - 4.5- 5.5ns T SUEC Register clock enable setup time 2.0- 3.0-ns T HEC Register clock enable hold time 0.0-0.0-ns T CW Global clock pulse width High or Low 1.4- 2.2-ns T PCWP-term pulse width High or Low4.0- 6.0-nsSymbol ParameterTest ConditionsMin.Max.Units6DS310 (v2.0) March 8, 2007T APRPW Asynchronous preset/reset pulse width (High or Low)4.0- 6.0-ns T CONFIG (4)Configuration time-50-50μsNotes:1.F TOGGLE is the maximum clock frequency to which a T-Flip Flop can reliably toggle (see the CoolRunner-II family data sheet).2.F SYSTEM1 (1/T CYCLE ) is the internal operating frequency for a device fully populated with one 16-bit counter through one p-term permacrocell while F SYSTEM2 is through the OR array .3.F EXT1 (1/T SU1+T CO ) is the maximum external frequency using one p-term while F EXT2 is through the OR array .4.Typical configuration current during T CONFIG is 500 μA.Symbol Parameter-4-6Units Min.Max.Min.Max.Internal Timing ParametersSymbol Parameter(1)-4-6Units Min.Max.Min.Max.Buffer DelaysT IN Input buffer delay- 1.3- 1.7ns T DIN Direct register input delay- 1.5- 2.4ns T GCK Global Clock buffer delay- 1.3- 2.0ns T GSR Global set/reset buffer delay- 1.6- 2.0ns T GTS Global 3-state buffer delay- 1.1- 2.1ns T OUT Output buffer delay- 1.8- 2.0ns T EN Output buffer enable/disable delay- 2.9- 3.4ns P-term DelaysT CT Control term delay- 1.3- 1.6ns T LOGI1Single p-term delay adder-0.4- 1.1ns T LOGI2Multiple p-term delay adder-0.2-0.5ns Macrocell DelayT PDI Input to output valid-0.3-0.7ns T LDI Setup before clock (transparent latch)- 1.5- 2.5ns T SUI Setup before clock 1.5- 1.8-ns T HI Hold after clock0.0-0.0-ns T ECSU Enable clock setup time 0.7- 1.7-ns T ECHO Enable clock hold time 0.0-0.0-ns T COI Clock to output valid-0.6-0.7ns T AOI Set/reset to output valid- 1.1- 1.5ns Feedback DelaysT F Feedback delay-0.6- 1.4ns T OEM Macrocell to global OE delay-0.7-0.8ns I/O Standard Time Adder Delays 1.5V CMOST HYS15Hysteresis input adder- 3.0- 4.0ns T OUT15Output adder-0.8- 1.0ns T SLEW15Output slew rate adder- 4.0- 5.0ns I/O Standard Time Adder Delays 1.8V CMOST HYS18Hysteresis input adder- 3.0- 4.0ns T OUT18Output adder-0.0-0.0ns T SLEW Output slew rate adder- 4.0- 5.0ns8DS310 (v2.0) March 8, 2007Switching CharacteristicsAC Test CircuitI/O Standard Time Adder Delays 2.5V CMOS T IN25Standard input adder -0.5-0.6ns T HYS25Hysteresis input adder - 3.0- 4.0ns T OUT25Output adder-0.6-0.7ns T SLEW25Output slew rate adder- 4.0- 5.0ns I/O Standard Time Adder Delays 3.3V CMOS/TTL T IN33Standard input adder -0.5-0.6ns T HYS33Hysteresis input adder - 3.0- 4.0ns T OUT33Output adder- 1.0- 1.2ns T SLEW33Output slew rate adder- 4.0- 5.0nsNotes:1. 1.5 ns input pin signal rise/fall.Internal Timing Parameters (Continued)Symbol Parameter (1)-4-6Units Min.Max.Min.Max.Figure 2: Derating Curve for T PDFigure 3: AC Load CircuitTypical I/O Output CurvesFigure 4: Typical I/V Curve for XC2C32APin DescriptionsFunction Block Macrocell QFG32PC44VQ44CP56I/O Bank 114438F1Bank 2124337E3Bank 2134236E1Bank 2 1(GTS1)434034D1Bank21(GTS0)523933C1Bank21(GTS3)613832A3Bank 21(GTS2)7323731A2Bank 21(GSR)8313630B1Bank 221 9303529A1Bank21 10293428C4Bank111283327C5Bank2112242923C8Bank21132822A10Bank2114232721B10Bank21152620C10Bank21162519E8Bank2215139G1Bank 122240F3Bank123341H1Bank124442G3Bank1 2(GCK0)56543J1Bank 12(GCK1)67644K1Bank 12(GCK2)7871K2Bank 110DS310 (v2.0) March 8, 2007XC2C32A Global, JTAG, Power/Ground and No Connect Pins28982K3Bank1291093H3Bank1210115K5Bank 1211126H5Bank 121213148H8Bank 1213171812K8Bank1214181913H10Bank1215192014G10Bank 12162216F10Bank1Notes:1.GTS = global output enable, GSR = global set reset, GCK = global clock2.GTS, GSR, and GCK pins can also be used for general purpose I/O.Pin TypeQFG32PC44(1)VQ44(1)CP56(1)TCK 161711K10TDI 14159J10TDO 253024A6TMS 151610K9Input Only22 (bank 2)24 (bank 2)18 (bank 2)D10 (bank 2)V CCAUX (JTAG supply voltage)44135D3Power internal (V CC )Power bank 1 I/O (V CCIO1)Power bank 2 I/O (V CCIO2)202115G812137H6273226C6Ground 11, 21, 2610,23,314,17,25H4, F8, C7No connects--K4, K6, K7, H7, E10, A7, A9, D8, A5, A8,A4, C3Total user I/O (includes dual function pins)21333333Notes:1.All packages pin compatible with larger macrocell densitiesPin Descriptions (Continued)Function BlockMacrocellQFG32PC44VQ44CP56I/O BankOrdering InformationPart Number Pin/BallSpacingθJA(C/Watt)θJC(C/Watt)Package TypePackage BodyDimensions I/OComm.(C)Ind. (I)(1)XC2C32A-4QFG32C0.5mm35.524.0Quad Flat No Lead;Pb-free5mm x 5mm21CXC2C32A-6QFG32C0.5mm35.524.0Quad Flat No Lead;Pb-free5mm x 5mm21CXC2C32A-4PC44C 1.27mm55.135.3Plastic Leaded ChipCarrier16.5mm x 16.5mm33CXC2C32A-6PC44C 1.27mm55.135.3Plastic Leaded ChipCarrier16.5mm x 16.5mm33CXC2C32A-4VQ44C0.8mm47.78.2Very Thin Quad FlatPack10mm x 10mm33CXC2C32A-6VQ44C0.8mm47.78.2Very Thin Quad FlatPack10mm x 10mm33C XC2C32A-4CP56C0.5mm66.014.9Chip Scale Package6mm x 6mm33C XC2C32A-6CP56C0.5mm66.014.9Chip Scale Package6mm x 6mm33C XC2C32A-4PCG44C 1.27mm55.135.3Plastic Leaded ChipCarrier; Pb-free16.5mm x 16.5mm33CXC2C32A-6PCG44C 1.27mm55.135.3Plastic Leaded ChipCarrier; Pb-free16.5mm x 16.5mm33CXC2C32A-4VQG44C0.8mm47.78.2Very Thin Quad FlatPack; Pb-free10mm x 10mm33CXC2C32A-6VQG44C0.8mm47.78.2Very Thin Quad FlatPack; Pb-free10mm x 10mm33CXC2C32A-4CPG56C0.5mm66.014.9Chip Scale Package;Pb-free6mm x 6mm33CXC2C32A-6CPG56C0.5mm66.014.9Chip Scale Package;Pb-free6mm x 6mm33CXC2C32A-6QFG32I0.5mm35.524.0Quad Flat No Lead;Pb-free5mm x 5mm21IXC2C32A-6PC44I 1.27mm55.135.3Plastic Leaded ChipCarrier16.5mm x 16.5mm33IXC2C32A-6VQ44I0.8mm47.78.2Very Thin Quad FlatPack10mm x 10mm33I XC2C32A-6CP56I0.5mm66.014.9Chip Scale Package6mm x 6mm33I XC2C32A-6PCG44I 1.27mm55.135.3Plastic Leaded ChipCarrier; Pb-free16.5mm x 16.5mm33I12DS310 (v2.0) March 8, 2007Device Part MarkingFigure 5: Sample Package with Part MarkingNote: Due to the small size of chip scale and quad flat no lead packages, the complete ordering part number cannot be included on the package marking. Part marking on chip scale and quad flat no lead packages by line are:•Line 1 = X (Xilinx logo) then truncated part number •Line 2 = Not related to device part number •Line 3 = Not related to device part number•Line 4 = Package code, speed, operating temperature, three digits not related to device part number. Package codes: C3 = CP56, C4 = CPG56, Q1 = QFG32.XC2C32A-6VQG44I 0.8mm 47.78.2Very Thin Quad Flat Pack; Pb-free 10mm x 10mm 33I XC2C32A-6CPG56I0.5mm66.014.9Chip Scale Package;Pb-free6mm x 6mm33INotes:1. C = Commercial (T= 0°C to +70°C); I = Industrial (T = –40°C to +85°C)Part Number Pin/Ball Spacing θJA (C/Watt)θJC (C/Watt)Package Type Package Body Dimensions I/O Comm. (C)Ind. (I)(1)Figure 6: QFG32 PackageFigure 7: VQ44 PackageFigure 8: PC44 PackageFigure 9: CP56 PackageWarranty DisclaimerTHESE PRODUCTS ARE SUBJECT TO THE TERMS OF THE XILINX LIMITED WARRANTY WHICH CAN BE VIEWED AT /warranty.htm. THIS LIMITED WARRANTY DOES NOT EXTEND TO ANY USE OF THE PRODUCTS IN AN APPLICATION OR ENVIRONMENT THAT IS NOT WITHIN THE SPECIFICATIONS STATED ON THE THEN-CURRENT XILINX DATA SHEET FOR THE PRODUCTS. PRODUCTS ARE NOT DESIGNED TO BE FAIL-SAFE AND ARE NOT WARRANTED FOR USE IN APPLICATIONS THAT POSE A RISK OF PHYSICAL HARM OR LOSS OF LIFE. USE OF PRODUCTS IN SUCH APPLICATIONS IS FULLY AT THE RISK OF CUSTOMER SUBJECT TO APPLICABLE LAWS AND REGULATIONS.14DS310 (v2.0) March 8, 2007Additional InformationAdditional information is available for the following CoolRunner-II topics:•XAPP784: Bulletproof CPLD Design Practices •XAPP375: Timing Model•XAPP376: Logic Engine•XAPP378: Advanced Features•XAPP382: I/O Characteristics•XAPP389: Powering CoolRunner-II•XAPP399: Assigning VREF Pins To access these and all application notes with their associ-ated reference designs, click the following link and scroll down the page until you find the document you want: CoolRunner-II Data Sheets and Application Notes Device PackagesRevision HistoryThe following table shows the revision history for this document.Date Version Revision6/15/04 1.0Initial Xilinx release.8/30/04 1.1Pb-free documentation10/01/04 1.2Add Asynchronous Preset/Reset Pulse Width specification to AC Electrical Characteristics.11/08/04 1.3Product Release. No changes to documentation.11/22/04 1.4Changes to output enable/disable specifications; changes to I CCSB.02/17/05 1.5Changes to f TOGGLE, t SLEW25, and t SLEW3303/07/05 1.6Improvement of pin-to-pin logic delay, page 1. Modifications to Table 1, IOSTANDARDs.06/28/05 1.7Move to Product Specification. Change to T IN25, T OUT25, T IN33, and T OUT33.03/20/06 1.8Add Warranty Disclaimer. Add note to Pin Descriptions that GCK, GSR, and GTS pins can alsobe used for general purpose I/O.02/15/07 1.9Change to V IH specification for 2.5V and 1.8V LVCMOS. Change to T OEM for -4 speedgrade.03/08/07 2.0Fixed typo in note for V IL for LVCMOS18; removed note for V IL for LVCMOS33.16DS310 (v2.0) March 8, 2007。

10bit500MS_sPipeline-SARADC的设计

摘要模数转换器(ADC)作为现代通信系统中的关键电路,其性能直接决定了通信系统的整体性能。

在需要中等精度高速ADC的应用场合,如无线网802.11ac通信协议等,流水线逐次逼近型模数转换器(Pipeline-SAR ADC)以其兼顾高速和低功耗的结构特点、对先进工艺兼容良好等优良特性被广泛使用。

针对现代高速通信系统的应用场合,论文设计了一款10bit 500MS/s的Pipeline-SAR ADC,其系统架构为两级结构,两级SAR ADC都实现6bit的数据量化,级间放大器提供4倍增益,设置2bit 级间冗余。

在第一级SAR ADC中,提出了一种基于自关断比较器的非环路(Loop-unrolled)结构,在每位比较完成后,通过自关断信号将当前位比较器关断,在不影响比较器锁存级保持数据的前提下,极大减小了Loop-unrolled结构的功耗;同时,针对Loop-unrolled结构多个比较器之间的失调失配,采用了一种基于参考比较器的后台失调校准方法,参考比较器的引入使得该校准方法可以在不增加额外校准时间的前提下完成后台校准,保证了系统的高速特性。

级间放大器采用了一种增益稳定的动态放大器,通过将动态放大器的增益构造为同种参数比例乘积的形式,实现增益稳定,并对其工作时序进行了优化,避免了额外时钟相的引入。

第二级SAR ADC采用了两路交替比较器结构,同时对两个比较器采用了前台失调校准,以避免引入额外的校准时间。

由于级间放大器仅提供4倍增益,第二级的量化范围较小,本文在第二级电容阵列的设计上使用了非二进制冗余,以减小DAC建立误差造成的影响。

本文还设计了数字码整合电路、全局时钟产生电路,以保证整个Pipeline-SAR ADC设计的完整性。

本文基于TSMC 40nm CMOS工艺设计了具体的电路与版图。

后仿真结果表明,在1.1V电源电压下,采样率为500MS/s时,输入近奈奎斯特频率的信号,在tt工艺角下,有效位数(ENOB)达到9.2位,无杂散动态范围(SFDR)达到64.5dB,功耗为7.52mW,FoM值为25.76fJ/conv.step,达到设计指标要求。

第7章 CMOS比较器

refV ⎪⎩⎪⎨⎧<>=in in V V ,0 ,1预放大判决驱动One stage buffer Two or more stage buffers The polarity of comparator is changed when one more INV used.wujinCross pair: M5/M8, Positive Feedback induced in DP load;Mainly to boost gain and small signal Speed.Fully symmetric & Differential OTA,N/P complimentary DPwujin-i gIf W/L of CP (M21,M23) large than that of MOS diode (M20,M22), Hysteric comparator is formed.wujinTo shift or switch reference based on comparator statutefor positive scanning, V applied first, when V+, switch to V for negative scanning, V applied first, when V, switch to VReference switch methodsexternal feedback control, analog mode & digital mode;internal feedback control, positive FB to introduce unsymmetrical.14wujin+V refNMOS switchPMOS switchBetterOutput as digital controlin configuring actual V refV DD /V ref ?; *i SPH V V +=+Modified CMOSHysterics comp should be firstly scaled down VDDwujin26302×=26302×==V B when V CC in to make I 2CC , V in and thus V A low, V B , V o , keep in CC , V A high, V , toggle.V A ?23wujinϕFor output upper level limitRecharge: initial staterecharge & evaluation mode.in +1ref −ΔωΔϕUnsymmetrical of each stage, C1/C2 charging-discharging carrier out alternately [separated by (N-1)/2=3 stage for each other], for setting frequency & duty cycle , VN-CS?RS Latch needed to hole the statue33wujinINV3ClkClkBis under constant current, a small35。

ST 74LCX74 数据手册