DSP+FPGA四轴运动控制器方案与对策

基于DSP与FPGA的跟踪伺服运动控制器设计

基于DSP与FPGA的跟踪伺服运动控制器设计摘要:在分析光电跟踪伺服系统特点的基础上,以TI 公司DSP 芯片TMS320F2812 作为主控制芯片,采用FPGA 进行逻辑时序控制,设计了基于DSP 和FPGA 的多轴伺服运动控制器。

给出了该控制器的功能和硬件结构以及软件流程设计。

实验结果表明,该控制器具有高集成度、灵活性、实时性、模块化的特点,完全满足了在复杂环境下对伺服系统控制的要求。

在高速光电跟踪系统中,对伺服系统的高速性、精确度和稳定性都有很高的要求。

为了提高跟踪精度,越来越多的控制算法被应用于伺服系统中,因此要求控制器能在很短的时间内完成大量的运算[1]。

DSP 具有较强的运算能力,而FPGA 具有高度灵活的可配置性和逻辑时序控制能力[2]。

因此在很多伺服控制器中,“DSP+FPGA”结构得到了广泛的应用。

实际应用环境一般比较复杂,有大量的信息传递,并且需要对电机转速实行精确控制,因此对伺服控制器的多路通信能力,快速运算能力和抗干扰能力都有较高的要求。

为了解决这一问题,提供一个较好的实验平台,本文结合光电跟踪伺服系统的特点,提出一种以TI 公司的32 位定点数字信号处理器TMS320F2812 为核心,以Altera 公司CycloneⅡ系列FPGA 为辅助处理器结构的跟踪伺服控制器,并综合阐述了该控制器的功能、硬件设计和软件流程。

该控制器采用单+5 V 供电,具有6 路模拟信号输入、4 路模拟信号输出、多路PWM 输出、1 路CAN 总线、2 路RS422 和1 路RS232 串行通信口,具有较强的运算能力和数据通信能力,是良好的数字控制系统实验平台。

1 总体结构设计TMS320F2812 作为一款专为电机控制所设计的芯片,不仅具有运算速度快的特点,而且集成了丰富的片内外设资源[3]。

设计时综合考虑DSP 片上资。

基于DSP+FPGA的开放式机器人运动控制器的研究共3篇

基于DSP+FPGA的开放式机器人运动控制器的研究共3篇基于DSP+FPGA的开放式机器人运动控制器的研究1开放式机器人运动控制器是一种专为机器人运动控制而设计的控制器,其运行在数字信号处理器(DSP)和现场可编程门阵列(FPGA)之上。

这种控制器的目的是完整控制机器人的运动,并提供精细的数据采集和处理,从而可以在进行复杂的运动控制时快速而准确地响应外界的刺激。

DSP+FPGA控制器的设计与传统机器人控制器类似,但是一些核心的结构和特征有所改变。

在DSP+FPGA控制器中,DSP主要用于实现运动控制算法、信号处理和通信控制,而FPGA则用于实现实时IO接口的数据采集及处理。

由于DSP的高效性能和FPGA的高速IO,因此该控制器可以在实时性和精度方面取得更高效的控制效果。

在DSP+FPGA控制器的设计中,需要深入了解机器人的运动学和动力学。

运动学涉及机器人的轨迹和位置控制,而动力学则涉及机器人的力学和电气特性的精确计算和控制。

因此,开发者需要掌握基本的控制算法、数学模型和信号处理技术,才能更好地设计出适应不同机器人类型和应用场景的开放式机器人控制器。

在实现DSP+FPGA开放式机器人运动控制器的过程中,需要注意以下几点:1. 高速数据采集和处理:FPGA作为实时IO接口向DSP提供高速而可靠的数据(例如机器人的位置、偏差、角度和力量数据)。

2. 快速响应和反应能力:DSP负责处理数据和运动控制算法,并通过FPGA控制机器人的开关、电机和伺服系统。

3. 多通道数据处理:DSP和FPGA需要支持多通道数据采集和处理,以实现同步的运动控制和精密的位置控制。

4. 丰富的输入和输出功能:DSP+FPGA控制器需要支持多种IO接口,例如模拟量输入、数字量输入、PWM控制、编码器反馈等,以实现对机器人的全面控制。

5. 跨平台的可移植性:DSP+FPGA控制器需要支持不同操作系统和平台,以适应各种机器人应用场景的需求。

基于FPGA的四轴飞行控制器的硬件系统设计

基于FPGA的四轴飞行控制器的硬件系统设计李刚;蔡启仲;郑力;陆伟男【期刊名称】《计算机测量与控制》【年(卷),期】2015(23)4【摘要】为提高四轴飞行器的数据采集与数据处理能力,降低四轴飞行器的功耗,研制了一种基于FPGA的四轴飞行控制器;飞行控制器以NIOS Ⅱ处理器为控制核心,结合嵌入的SPI、I2C、UART等IP核实现了数据的实时采集与快速处理,并提出并行处理PPM解码和编码、超声波检测与控制、蜂鸣器控制的设计方案,利用VerilogHDL语言在FPGA上设计了这些并行处理功能模块,这些功能模块通过PIO核与NIOS Ⅱ处理器连接,能够自主完成所规定的处理功能;经过多次飞行测试,四轴飞行器能够稳定地起飞和降落、快速的飞行、转弯、上升和下降,也能够避开障碍物,验证了四轴飞行控制器功能稳定,功耗较低,已达到设计的要求.【总页数】4页(P1192-1194,1197)【作者】李刚;蔡启仲;郑力;陆伟男【作者单位】广西科技大学电气与信息工程学院,广西柳州 545006;广西科技大学电气与信息工程学院,广西柳州 545006;广西科技大学电气与信息工程学院,广西柳州 545006;广西科技大学电气与信息工程学院,广西柳州 545006【正文语种】中文【中图分类】TP273【相关文献】1.基于FPGA的四轴飞行器飞行控制系统设计 [J], 徐亚妮;罗文广;张亮2.基于FPGA的四轴飞行器无刷电机智能供电控制系统设计 [J], 蒋文坚3.基于FPGA的四轴飞行器飞行控制系统设计 [J], 徐亚妮;罗文广;张亮;4.基于MSP430单片机的四轴飞行器飞行控制系统设计 [J], 李想; 亢洁5.基于DSP和FPGA的四轴伺服控制器的硬件设计 [J], 朱德荣;温广宇因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP和FPGA的运动控制技术的研究

基于DSP和FPGA的运动控制技术的研究摘要:开放式数控系统具有可互换性、可移植性、可扩展性、互操作性等特点,更能够满足当前制造企业的加工需求,并为技术和产品之间的集成提供了可能。

本文主要对DSP和FPGA两种芯片进行介绍和分析,在此基础上设计运动控制器,以期更好地应用运动控制技术,达到数控系统对运动控制单元实时、精准控制的要求。

关键词:数控系统;DSP;FPGA;运动控制器运动控制技术是一门涵盖多学科的综合性的交叉技术,在生产加工中应用十分广泛,能够完成各种复杂的加工任务。

随着制造工业生产加工速度的日益提高,其对加工精度以及实时控制也提出了越来越高度的要求。

传统的基于单片机的运动控制卡已经无法满足数控系统的工作要求,基于PC的运动控制卡已经得到普及,考虑到高性能、低成本等特性,基于DSP和FPGA的运动控制器设计成为了研究重点,这也是运动控制技术发展的一大趋势。

1.运动控制技术及基于DSP和FPGA的控制方案按照机械运动轨迹来划分,运动控制系统可分为点位、直线和轮廓控制;按照执行部件类型划分,可分为开环、半闭环及闭环伺服系统。

无论基于哪一种分类,都遵循连续运动轨迹插补原理,所谓插补,就是对数据密化进行实时控制的过程,它与坐标轴位置伺服控制共同构成了运动控制系统的两个重要组成部分,作为轨道控制中最重要的计算任务,插补运算必须要保证精度和实时性,目前比较常用的插补运算法是脉冲冲量插补和数据采样插补[1]。

运动控制器就是运动系统和控制技术相结合的产物,其类型较多,但在功能上并无明显差异,关于运动控制的设计,目前主要采用PC机与运动控制卡相结合的控制方案,在此主要介绍基于DSP和FPGA的运动控制卡的设计,以此类控制卡作为运动系统的主控单元,能够完成以下三种功能:其一,从主机接收运动指令,向主机反馈运行状态;其二,根据接收的指令,对4轴电机的位置、速度、插补和PID调节进行控制;其三,完成运动控制的同时还能够对与运动有关的I/O信号进行处理[2]。

基于DSP和FPGA的运动控制器设计

S n Ya m ig,W a g Yo g n u n n n n mi g,Yu n De h ,Ch n Jn g a g a zi e i g u n ,Z a g Pe g h n n ,W a g Ya n n

( a gc u sa c n tt t o eh n c lS in eCo ,Lt Ch n h nRee r h I siu ef rM c a ia ce c . d.Ch n h n 1 0 1 a gc u 3 0 2,Jii ln,Ch n ia)

V 15 O 3 o. 2N .

工 程 与试 验 E NGI E R NG & T S N E I ET

Sp 0 2 e.2 1

基 于 DS P和 F GA 的 运 动 控 制 器 设 计 P

孙艳 明 , 永 明 , 德 志 , 王 袁 陈景 光 , 张 鹏 , 王 艳

( 长春机 械科 学研 究院有 限公 司 , 吉林 长春 1 0 1 ) 3 0 2

The f c i ft o r l ri x nd d b un ton o he c ntole s e pa e y FPGA ,t n,t l e o p c t o fs v r lAC he he cos d l o on r lo e e a s r o m o o lc r — yd a i e vo v l e i e lz d The c t o l ri e a e he e o rsg e v t rore e t o h r ulcs r a v s r a ie . on r le nt gr t s t nc de i — n la q ston,PLC nt r a e,1 t g s e a c uiii i ef c bishi h— pe d AD o l c i n a d c 6 c le to n ompu e o t rc mmun c to n iain i— t r a e,a h o r le a gh i e a i n a a c l to pe d. efc nd t e c nt o l r h s hi nt gr to nd c l u a i n s e Ke wo d DS y r s: P;FPGA ;Re i t r;Ve io DL gs e rl g H

基于DSP和FPGA的数控系统运动控制的设计

关 键词 DS P P F GA 步 进 电机 伺 服 系统

0 引 言

运 动 控制 是 数 控 系 统 的重 要 组 成 部 分 ,数 控 系 统 的性 能 很 大程 度 上 取 决 于 运 动 控 制 器 的 选 择 。DS P器

上 的 多轴 运动 控 制 卡 大 多 采 用 多 个 DS P控 制 多 轴 联 动

和 DS P负 责 复 杂运 算 ,结 合 扩展 的 ]o或 D/ 通 道去 / A 控制 多 轴 联 动 。 全 部 数 控 系 统 的 功 能 都 集 中在 一 块 运 动控 制 卡 中 , 维 护 困 难 , 也 不 能 满 足 不 同 用 户 的 需

件 的 升 级 维 护 容 易 ,开 放 性 进 一 步 提 高 。

图 1 数控系统的结构模型

ADS 2 0 5 内部 有 2个 完 全 相 同 的定 时 器 块 , P 16 L 以 2倍 于输 入 时 钟 的 频 率 工 作 , 每个 定 时 器 都 有 1个

I0 引脚 P M— VE x ( 一 1 ) / W E NT ,2 ,既 可 以 配 置 为

求 ] 。本 文 利 用 可 编 程 大 规 模 门 阵列 电 路 F G 的 并 PA 行 性 和 可 编 程 性 ,对 光 电 编 码 器 输 出 信 号 倍 频 、 鉴 相 、计 数 ,有 利 于提 高 被 控 对 象 的 测 量 精 度 和 控 制 精 度 。而 高 精度 的 不 同 电 机 的 两 轴 控 制 ,使 单 个 DS P控 制 多 轴 联 动 成 为 可 能 。硬 件 结 构 化 的设 计 思 想 , 使 硬

基于DSP和FPGA的多轴运动控制系统设计

基于DSP和FPGA的多轴运动控制系统设计马汉波;颜钢锋【期刊名称】《电子技术应用》【年(卷),期】2013(39)3【摘要】传统的机器人运动控制器都是采用PC+运动控制卡的方法,成本较高.提出了一种基于DSP和FPGA的通用型运动控制系统,大大降低了系统成本.利用FPGA内部生成的双端口RAM作为DSP与上位机之间的缓冲区,同时采取串行转并行的策略,简化了系统的布线.在DSP上实现了直线与圆弧插补算法以及逆运动学的求解,并进行了仿真.仿真结果表明,系统能够按照预定轨迹运动,同时各轴的速度变化也较平稳.%Traditional motion controllers for robots make use of PC and motion control board, which cost much. This article presents a generic motion control system,which saves cost. DPRAM implemented in FPGA is used to transmit data between DSP and upper computer. FPGA also converts data from serial to parallel and simplify the routing of board. The algorithm of curve interpolation and inverse kinematics is simulated on DSP. The result shows that this system works properly and the speed of each axis changes smoothly.【总页数】3页(P34-36)【作者】马汉波;颜钢锋【作者单位】浙江大学电气工程学院,浙江杭州310027【正文语种】中文【中图分类】TP242.2【相关文献】1.基于ARM+DSP+FPGA的机器人多轴运动控制器的设计与研究 [J], 刘大伟;王苏洲2.基于 DSP 和 FPGA 的多轴伺服运动控制器设计 [J], 黄建3.基于DSP-FPGA的多轴运动控制系统设计 [J], 刘岩;丁大伟4.基于DSP的多轴运动控制系统设计 [J], 齐山成;刘海华;刘毅5.一种基于DSP和FPGA的多轴运动控制卡的设计 [J], 郑晓峰;方凯;黄迎华因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP-FPGA的多轴运动控制系统设计

式 中L 为弹 目距 离初值 ,v 弹 目接近 速 度 ,t n 为

为工 作时 间 。

步 变 速 控 制 , 以及 两 个 干 扰 投 放 电机 间 的 同步 控 制 ,并 且 完成 了对 它们 的精 确 定位 。系统 中对DS P 和F G P A进 行 了功能 划 分 ,在硬 件 上 实现 了对 多路

31 同步变速算法 . 可 变 光 阑 电机 在 有 效 工 作 时 间 内运 行 轨 迹 为 不 规 则 的 ,所 以采 用 多份 匀速 运 动 来拟 合 变 速 运

动 。 当弹 目接近 速 度 为v ,可变 光 阑 电机 从 闭合 时 运 行到 最大 尺 寸 时( 模拟 目标 从 初 始位 置 到 终点 ) 即 的 工 作 时 问为 t 设 每 份 匀 速 运动 时 间为 T 与 系 (

目标 模 拟 器 系统 是 由黑 体 作 为 红 外 光 源 产 生 两 路 红 外 光 , 经 光 学 系 统形 成 一 路平 行 目标 光线 和 两 路 平 行干 扰 光 线 。其 光 学 总体 结构 中包 括 离 轴 抛 物 面 镜 组 、 可 变 光 阑 、干 扰模 拟 组 件 和 目标 模 拟 组 件 。它 是 一 种 对称 的 结 构 , 包括 两 个 对 称 的 干 扰通 道 和一 个 目标通 道 , 主要 受控 部 件 为可 变 光 阑( 目标通 道) 干扰 模 拟组 件 ( 和 干扰 通道 ) ,共

数 字 控 制 器 具 有对 环 境 变 化 不 敏 感 、可 实 现 复 杂

算 法 和 可 增 加 附 属功 能 等 优 点 ,是 今 后 控 制 器 发 展 的方 引 。数 字 信 号 处理 器 ( P 被 广 泛 应 用 于 DS ) 电机 控 制 中 , ̄ T 公 司 的C2 0 系 列DS / I I 00 P,其 可 以高 速 完成 一 些较 为 复杂 的 算法 ,但 是 其 外 设 模

基于DSP和FPGA的运动控制器

基于DSP和FPGA的运动控制器

钱志恒;周亚军

【期刊名称】《机电工程》

【年(卷),期】2009(026)001

【摘要】为了满足开放式运动控制器的设计要求,给出了一种基于数字信号处理器(DSP)和现场可编程门阵列(FPGA)的四轴通用运动控制器设计方案,详细论述了该四轴通用运动控制器的体系结构特点、硬件电路设计、FPGA模块分析和软件模块组成;系统结合PC/104模块化设计思想,基于TMS320F2812 DSP外部总线的设计,采用高性价比FPGA芯片EP2C5实现了运动控制专用外设模块,使系统具有结构简单、低成本、开放性、模块化特点,而且总线上各模块可独立设计,亦降低了系统实现难度.实际应用结果表明,该控制器具有良好的性能.

【总页数】4页(P38-41)

【作者】钱志恒;周亚军

【作者单位】杭州电子科技大学,自动化学院,浙江,杭州,310018;杭州电子科技大学,自动化学院,浙江,杭州,310018

【正文语种】中文

【中图分类】TP274

【相关文献】

1.基于DSP和FPGA的运动控制器设计 [J], 孙艳明;王永明;袁德志;陈景光;张鹏;王艳

2.基于ARM+DSP+FPGA的机器人多轴运动控制器的设计与研究 [J], 刘大伟;王苏洲

3.基于ARM+DSP+FPGA模块的机器人运动控制器设计 [J], 赵岩;李秀荣;臧勇

4.基于 DSP 和 FPGA 的多轴伺服运动控制器设计 [J], 黄建

5.基于DSP与FPGA的运动控制器研究 [J], 周国娟;金红莉;苏福根

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP和FPGA的运动控制器的设计与实现

计与 实现 。在 充分考 虑上 述芯 片特 点和 资源 的基 础 上 , 该控 制 器采 用浮 点型 D P与 F G 能够更好 S P A,

地 满 足 数 控 系统 对 运 动 控 制 单 元 的 实 时 性 和 控 制 精 度 的 苛 刻 要 求 。 同 时 介 绍 了运 动 控 制 器 的 硬 件 整 体 结 构 及 主 要 模 块 的 详 细 设 计 , 给 出 了 DS 并 P软 件 实现 的 程 序 结 构 框 架 。

c n r l r h r w a e s r t r nd t e a l d d sg f t e m an m o uls a e i t od e a l o g v s t e o t o l a d r tuc u e a he d t i e i n o h i d e r r uc d, nd a s i e h e e n pr g a t u t e o S o t a e fa e o k. o r m s r c ur f D P s f w r r m w r Ke y wo ds:CN C ; S r D P; FPG A ;mo i n c n r l r to o t o l e

关 键 词 : 控 系统 ; S F G 运 动 控 制 器 数 D P; P A; 中 图 分 类 号 : H1 T 6 T 6; G 5 文献标 识码 : A

The De i n a e lz i n 0 o i n Con r le s g nd R a i ato f M t o t o l r Bas d o e n DSP a d FPG A n

a d f au e fTM ¥ 0C6 3 n e t r s o 32 71 D S c i o a d A 3 0 P h p f TI n P4 0 FPG A c i o hp f ACTEL,pr s n s e in e e t a d sg

一种基于STM32和FPGA的多轴运动控制器的设计与实现

一种基于STM32和FPGA的多轴运动控制器的设计与实现一种基于STM32和FPGA的多轴运动控制器的设计与实现引言数控系统在工矿领域已得到广泛应用,计算机数控系统通过对数字化信息的处理和运算,并转化成脉冲信号,实现对电机的控制,进而控制数控机床动作和零件加工。

随着嵌入式技术的发展,我们可以设计规模更小,成本更低,功能更特定的嵌入式系统来完成传统计算机数控系统所完成的工作。

1、设计方案本系统以嵌入式处理器STM32和FPGA芯片为核心,运动控制方案中的处理部分都放在FPGA内部实现。

这是1种硬件软化的方案,即具有软件可编程、可重构的特点,又有硬件那样高性能、高可靠、高一致性的优点。

其系统原理框图如图1所示。

STM32从SD 卡中读取数据文件并进行相关算法处理,通过键盘扫描电路设置系统加减速的初始速度、最大速度、加速度的初始值以及一些控制参数。

将相应参数传送到FPGA进行处理,最后由FPGA控制输出脉冲和脉冲间延时,通过高光耦隔离后输出,控制电机的运转。

通过RS232实现和上位机数据通信以及驱动LCD完成人机交互工作。

FPGA主要用来实现指令和数据处理模块、加减速模块、插补功能模块(包括直线插补和圆弧插补)等运动控制算法。

2、运动控制算法在FPGA中的实现2.1、速度控制算法在FPGA 中的实现为避免电机在启动、运行以及换速过程中使各轴产生超程、冲击、失步和振荡的现象,保证运动机构的平稳和准确定位,这就要求电机在各程序段转接时具有一个加减速的过程,使其平滑的过渡。

大多运动控制系统都拥有梯形加减速和S型加减速功能。

由于梯形加减速算法简单,系统响应快,效率高等优点,结合本课题要解决的主要问题以及应用的相关领域,课题在传统梯形加减速的基础进行改进来实现脉冲的输出。

梯形加减速算法采用脉冲叠加的方法在FPGA内部的实现,即:以某一时钟为基准,将其进行n次分频后产生互不重叠的不同频率的n种脉冲,然后提取所需要的几种脉冲以式(1)进行叠加,从而输出连续可调的、不同频率的脉冲来完成加减速运算。

基于DSP与FPGA的运动控制器设计

基于DSP与FPGA的运动控制器设计运动控制技术是数控机床的关键技术,其技术水平的高低将直接影响一个国家装备制造业的发展水平。

目前,多轴伺服控制器越来越多地运用在运动控制系统中,具有较高的集成度和灵活性,可实时完成运动控制过程中复杂的逻辑处理和控制算法,能实现多轴高速高精度的伺服控制。

本文选用DSP 与FPGA 作为运动控制器的核心部件,设计了通用型运动控制器。

其中DSP 用于运动轨迹规划、速度控制及位置控制等功能;FPGA 完成运动控制器的精插补功能,用于精确计算步进电机或伺服驱动元件的控制脉冲,同时接收并处理脉冲型位置反馈信号。

本文对该运动控制器的总体结构、硬件设计和软件设计进行了描述。

1 系统总体设计运动控制器的总体性能指标为:作为一个单独的运动控制器使用,控制信号采用数字量方式输出,能控制四轴的伺服电机;最高脉冲输出频率为4MP/s,能处理的编码器反馈信号最高频率为4MP/s;能接收和处理4 路编码器反馈信号;可以处理原点信号、正负方向信号、到位信号以及急停信号等数字量输入信号;提供16 路数字量输出信号和16 路数字量输入信号接口。

运动控制器采用DSP 与FPGA 芯片作为主控芯片,主要包括DSP 模块、FPGA 模块、FPGA 外围电路模块和数字量输入输出接口模块。

采用基于DSP 与FPGA 的运动控制器,能够实时完成复杂的轨迹运算,而且利用DSP 的高速数字信号处理功能和FPGA 功耗低、主频高的优点,能充分显示该运动控制器的优点。

采用DSP 与FPGA 相结合的运动控制器可以方便地对系统的控制策略进行修改,对控制参数进行修正,并可使设备具有良好的可靠性、可维修性,而且还降低了成本。

系统还可以采用更多的智能控制策略,结构灵活,有较强的通用性,适合于模块化设计,能够提高算法效率,且易于维护和扩展。

总体设计方案原理框复位电路设计采用TI 公司的TPS382x 系列电压监。

基于DSP和FPGA的四轴运动控制卡的研究与开发

部分内容编入有关数据库进行检索 手段保存和汇编本学位论文 保密 本学位论文属于 不保密 请在以上方框内打 学位论文作者签名

在 年解密后适用本授权书

指导教师签名

谢明 陈德荣

上海交通大学 硕士学位论文 基于DSP和FPGA的四轴运动控制卡的研究与开发 姓名:谢明 申请学位级别:硕士 专业:电力电子与电力传动 指导教师:陈德荣 20050101

基于 DSP 和 FPGA 的四轴运动控制卡的研究与开发 摘 要

数控技术是生产设备自动化水平的重要标志之一 是现代制造的核 心技术 运动控制卡是数控技术的核心部件 是 PC 机与驱动执行部件之 间的桥梁 近年来 工业发达国家数控技术发展迅速 我国也在积极研

日期 2005 年 1 月 10 日 日期 2005 年 1 月 10 日

上海交通大学硕士学位论文

第一章 引言

1.1 数字控制技术的基本概念

数字控制 numerical control

简称数控 NC 是近代发展起来的一种自动控制

技术 国家标准 GB 8129-87 对其进行的定义为 用数字化信号对机床运动及其加 工过程进行控制的一种方法 换言之 数控技术就是以数字量编程实现控制机械或其 他设备自动工作的技术 如果一种设备的控制过程是以数字形式来描述的 其工作过 程是可编程序的 并能在程序控制下自动地进行 那么这种设备就从称为数控设备[1] 数字控制的对象是多种多样的 事实上 所有能计算确定运动要求的设备 都可 能实现数控化 如 数控机床 数控火焰切割机 数控绘图机 数控冲剪机等都是属 于这个范围的自动化设备 数控设备的一般工作原理如下

直线和圆弧插补算法以及数字积分插补原理也进行了分析 最终 提出 总体程序流程控制 行了具体程序设计 速度控制算法 四轴运动控制卡在硬件上实现了直线插补 插补算法等的程序设计框架 并进

DSPFPGA四轴运动控制器设计方案

D S P F P G A四轴运动控制器设计方案Standardization of sany group #QS8QHH-HHGX8Q8-GNHHJ8-HHMHGN#D S P+F P G A四轴运动控制器设计方案引言运动控制技术是制造自动化的关键基础,其水平高低是衡量一个国家工业现代化的重要标志,研究和开发具有开放式结构的运动控制器是当前运动控制领域的一个重要发展方向。

设计了一种基于DSP与FPGA的运动控制器。

该控制器以DSP和FPGA为核心器件,针对运动控制中的实时控制、高精度等具体问题,规划了DSP的功能扩展,并在FPGA上扩展了功能相互独立的四轴运动控制电路。

该电路实现了四路控制信号输出,四路编码信号的接收和处理,以及原点信号,正负限位信号等数字量的接收和处理。

具有结构简单、开放性、模块化等特点,能够较好的满足运动控制器的实时性和精确性。

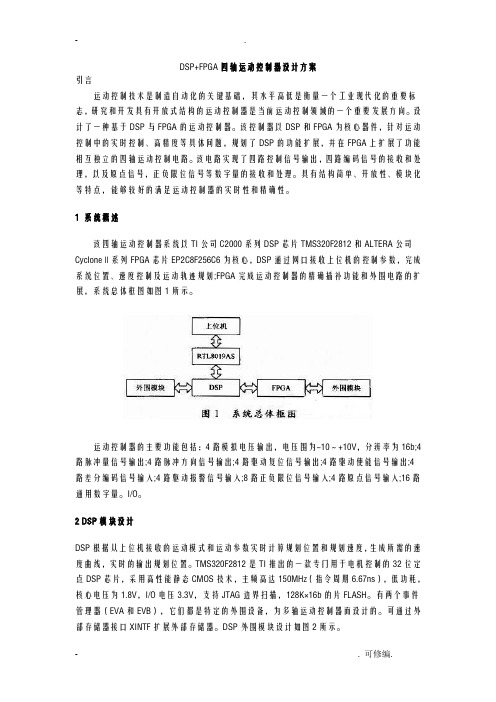

1 系统概述该四轴运动控制器系统以TI公司C2000系列DSP芯片TMS320F2812和ALTERA公司CycloneⅡ系列FPGA芯片EP2C8F256C6为核心,DSP通过网口接收上位机的控制参数,完成系统位置、速度控制及运动轨迹规划;FPGA完成运动控制器的精确插补功能和外围电路的扩展,系统总体框图如图1所示。

运动控制器的主要功能包括:4路模拟电压输出,电压范围为-10~+10V,分辨率为16b;4路脉冲量信号输出;4路脉冲方向信号输出;4路驱动复位信号输出;4路驱动使能信号输出;4路差分编码信号输入;4路驱动报警信号输入;8路正负限位信号输入;4路原点信号输入;16路通用数字量。

I/O。

2 DSP模块设计DSP根据从上位机接收的运动模式和运动参数实时计算规划位置和规划速度,生成所需的速度曲线,实时的输出规划位置。

TMS320F2812是TI推出的一款专门用于电机控制的32位定点DSP芯片,采用高性能静态CMOS技术,主频高达150MHz(指令周期),低功耗,核心电压为,I/O电压,支持JTAG边界扫描,128K×16b的片内FLASH。

基于DSP的四轴台式工业机器人控制器的研究与设计

基于DSP的四轴台式工业机器人控制器的研究与设计

陈曦;余超;彭鑫;欧阳竟成;荣军;李茜铭

【期刊名称】《湖南理工学院学报(自然科学版)》

【年(卷),期】2012(025)003

【摘要】以四轴台式工业机器人为研究对象,设计了一种基于DSP的工业机器人控制器.该控制器以DSP及CPLD为主要核心,通过PCI总线与上位机PC及交流伺服驱动电路进行通信.测试表明其具有较快的运算速度,较高的控制精度,较强的抗干扰能力,及良好的开放性.

【总页数】3页(P67-68,88)

【作者】陈曦;余超;彭鑫;欧阳竟成;荣军;李茜铭

【作者单位】湖南理工学院信息与通信工程学院,湖南岳阳414006;湖南理工学院信息与通信工程学院,湖南岳阳414006;湖南理工学院信息与通信工程学院,湖南岳阳414006;湖南理工学院信息与通信工程学院,湖南岳阳414006;湖南理工学院信息与通信工程学院,湖南岳阳414006;湖南理工学院信息与通信工程学院,湖南岳阳414006

【正文语种】中文

【中图分类】TP273

【相关文献】

1.基于DSP运动控制器的5R工业机器人系统设计 [J], 顾剑锋;张兴国;朱龙彪

2.一种基于DSP的四轴运动控制卡的研究与设计 [J], 郭伟;闫发军;岳艳红

3.基于DSP与FPGA的四轴运动控制器设计与研究 [J], 石江华;魏世民;李金泉;杨向东

4.基于ARM+DSP的三轴工业机器人运动控制器设计 [J], 王成琼;麦麦提明·阿不都克力木;尹福成;刘武周

5.基于DSP和FPGA的四轴伺服控制器的硬件设计 [J], 朱德荣;温广宇

因版权原因,仅展示原文概要,查看原文内容请购买。

基于DSP和FPGA的多轴运动控制系统设计

D S P与 上 位 机 之 间的缓 冲 区 , 同时采 取 串行 转 并行 的 策略 , 简化 了 系统 的 布 线 。在 D S P上 实现 了直 线 与 圆弧 插 补 算 法 以及 逆 运 动 学 的 求 解 , 并 进 行 了仿 真 。仿 真 结 果 表 明 , 系统 能 够 按 照 预 定 轨 迹 运 动 ,

p r e s e n t s a g e n e ic r mo t i o n c o n t r o l s y s t e m, wh i c h s a v e s c o s t . DP R AM i mp l e me n t e d i n F P GA i s u s e d t o t r a n s mi t d a t a b e t w e e n D S P a n d u p p e r c o mp u t e r .F P GA a l s o c o n v e t r s d a t a f r o m s e ia r l t o p a r a l l e l a n d s i mp l i f y t h e r o u t i n g o f b o a r d.T h e a l g o i r t h m o f c u r v e i n — t e r p o l a t i o n a n d i n v e r s e k i n e ma t i c s i s s i mu l a t e d o n DS P.T h e r e s u l t s h o ws t h a t t h i s s y s t e m w o r k s p r o p e r l y a n d t h e s p e e d o f e a c h a x — i s c h a n g e s s mo o t h l y .

基于DSP与FPGA的运动控制器研究

hg er eo d lr aypo rmmig n ihp e iino t nc nrl n a c iv o belo o  ̄ l f ih ihd ge f mo ua ,e s rga n ,a dh s rcso f moi o to d c na he ed u l— pe n o s — o a o oh

还 可 以通 过 P I 线 和 P C总 C机 通 信 。 以获 取 控 制 参 数 。 F G PA 因 为 有 着 丰 富 的 内部 资 源 .高 效 的底 层 数 据 计 算 处 理 能 力 ,

p e i o eo i o n o i o o e e r a- mea d a c r c e u r me t e mo o o t e r cs n v lc t l pa d p st n l p t me t h e l i n c u a yr q i i yo i o o t t e n t t n c n mU  ̄ f o h i

b i n e a e cr u to h t n c n r l r s n o s a d moo r e t P u l i tr c i i ft e mo i o t l 、 e s r n tr d v s wi F GA。 1 l u lp a h P’ o e u t f c o oe i h . 1e f l ly o t e DS s p w r l f f c mp t ga d F GA’ a a ll r c si g a a i t sa eg v . h e in h s a v t g so f r o u i n P n Sp r l o e sn c p b l i Y a e T e d sg a d a a e fi o m ̄in p o e sn bl y. ep ie n n o rc siga it a i

基于DSP技术的多轴运动控制器的应用研究

基于DSP技术的多轴运动控制器的应用研究Ξ高军礼 陈 玮 邓则名 李 芳广东工业大学自动化学院,广东广州 510090摘要:本文介绍了利用基于DSP技术的多轴运动控制器作为下位机,PC机作为上位机所构成的主从式数控立式铣床控制系统。

该系统充分利用了PC机技术和DSP技术资源,具有高精度、高速度、高性价比的特性。

关键词:数字信号处理器;运动控制器;数控系统中图分类号:TP34213 文献标识码:A 文章编号:1001-2265(2002)03-0003-03The research on multi-axis motion controller based on DSPG AO J unli CHEN Wei DEN G Zeming L I FangAbstract:This paper introduces one PC—DSP principal and subordinate frame numerical control s ystem on milling machine. The system takes full advantage of the technology resource of PC&DSP.Higher precision,velocity,performance price ratio can be guaranteed.K ey w ords:DSP;motion controller;numerical control system1 引言WTO———中国人企盼十多年的梦想终于实现了,这无疑对我国原本相对落后的机械制造业带来了难得的机遇和巨大的挑战。

作为机械制造业重中之重的数控机床自然首当其冲,未来几年内我们国家能不能尽快与国际接轨,开发出具有自主知识产权的高精密数控机床,在中高端数控机床方面占有一席之地显得十分重要。

“十五”规划中也指出,整个机床行业要以提高国产数控机床市场占有率为目标。

DSP+FPGA四轴运动控制器方案及对策

DSP+FPGA四轴运动控制器设计方案引言运动控制技术是制造自动化的关键基础,其水平高低是衡量一个工业现代化的重要标志,研究和开发具有开放式结构的运动控制器是当前运动控制领域的一个重要发展方向。

设计了一种基于DSP与FPGA的运动控制器。

该控制器以DSP和FPGA为核心器件,针对运动控制中的实时控制、高精度等具体问题,规划了DSP的功能扩展,并在FPGA上扩展了功能相互独立的四轴运动控制电路。

该电路实现了四路控制信号输出,四路编码信号的接收和处理,以及原点信号,正负限位信号等数字量的接收和处理。

具有结构简单、开放性、模块化等特点,能够较好的满足运动控制器的实时性和精确性。

1 系统概述该四轴运动控制器系统以TI公司C2000系列DSP芯片TMS320F2812和ALTERA公司CycloneⅡ系列FPGA芯片EP2C8F256C6为核心,DSP通过网口接收上位机的控制参数,完成系统位置、速度控制及运动轨迹规划;FPGA完成运动控制器的精确插补功能和外围电路的扩展,系统总体框图如图1所示。

运动控制器的主要功能包括:4路模拟电压输出,电压围为-10~+10V,分辨率为16b;4路脉冲量信号输出;4路脉冲方向信号输出;4路驱动复位信号输出;4路驱动使能信号输出;4路差分编码信号输入;4路驱动报警信号输入;8路正负限位信号输入;4路原点信号输入;16路通用数字量。

I/O。

2 DSP模块设计DSP根据从上位机接收的运动模式和运动参数实时计算规划位置和规划速度,生成所需的速度曲线,实时的输出规划位置。

TMS320F2812是TI推出的一款专门用于电机控制的32位定点DSP芯片,采用高性能静态CMOS技术,主频高达150MHz(指令周期6.67ns),低功耗,核心电压为1.8V,I/O电压3.3V,支持JTAG边界扫描,128K×16b的片FLASH。

有两个事件管理器(EVA和EVB),它们都是特定的外围设备,为多轴运动控制器而设计的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DSP+FPGA四轴运动控制器设计方案

引言

运动控制技术是制造自动化的关键基础,其水平高低是衡量一个工业现代化的重要标志,研究和开发具有开放式结构的运动控制器是当前运动控制领域的一个重要发展方向。

设计了一种基于DSP与FPGA的运动控制器。

该控制器以DSP和FPGA为核心器件,针对运动控制中的实时控制、高精度等具体问题,规划了DSP的功能扩展,并在FPGA上扩展了功能相互独立的四轴运动控制电路。

该电路实现了四路控制信号输出,四路编码信号的接收和处理,以及原点信号,正负限位信号等数字量的接收和处理。

具有结构简单、开放性、模块化等特点,能够较好的满足运动控制器的实时性和精确性。

1 系统概述

该四轴运动控制器系统以TI公司C2000系列DSP芯片TMS320F2812和ALTERA公司CycloneⅡ系列FPGA芯片EP2C8F256C6为核心,DSP通过网口接收上位机的控制参数,完成系统位置、速度控制及运动轨迹规划;FPGA完成运动控制器的精确插补功能和外围电路的扩展,系统总体框图如图1所示。

运动控制器的主要功能包括:4路模拟电压输出,电压围为-10~+10V,分辨率为16b;4路脉冲量信号输出;4路脉冲方向信号输出;4路驱动复位信号输出;4路驱动使能信号输出;4路差分编码信号输入;4路驱动报警信号输入;8路正负限位信号输入;4路原点信号输入;16路通用数字量。

I/O。

2 DSP模块设计

DSP根据从上位机接收的运动模式和运动参数实时计算规划位置和规划速度,生成所需的速度曲线,实时的输出规划位置。

TMS320F2812是TI推出的一款专门用于电机控制的32位定点DSP芯片,采用高性能静态CMOS技术,主频高达150MHz(指令周期6.67ns),低功耗,核心电压为1.8V,I/O电压3.3V,支持JTAG边界扫描,128K×16b的片FLASH。

有两个事件管理器(EVA和EVB),它们都是特定的外围设备,为多轴运动控制器而设计的。

可通过外部存储器接口XINTF扩展外部存储器。

DSP外围模块设计如图2所示。

为增强抗干扰性,DSP通过以太网控制器RTL8019AS与上位机连接,RTL8019AS部含有一个16KB的SDRAM,DSP通过外部存储器接口对其进行读写来接收上位机的命令或向上位机传送反馈信号。

在数据处理过程中要占用大量的存储空间,DSP部仅含有18K×16b的SARAM 和128K×16b的FLASH,存储空间显得过小,所以通过外部接口扩展了256K×16b RAM和512K ×16b FLASH,RAM和FLASH芯片分别选择IS61LV25616 AL、SST39VF800,它们都具有接口简单、读写速度快等优点。

SCI模块用于扩展RS 232串行通信接口,串口芯片使用MAX3232。

运动控制器所需电压为5V,3.3V,1.8V,1.2V。

输入电压5V,分别采用稳压芯片

LM1085IS3.3,LM1117-1.8将其转换成3.3V和1.8V,由于TMS320F2812的I/O电压3.3V

要先于核电源上电,所以1.8V要由3.3V降压得到,以确保上电次序。

1.2V是FPGA核所需电压,由稳压芯片LM317S稳压得到,LM317S的输出电压围为1.2~25V,复位电路采用SP708低功耗微处理器监控器件,此器件有众多的组件,有效的增强了系统的可靠性及工作效率。

3 FPGA模块设计

FPGA用于轴资源的扩展,当接收到DSP中的规划位置后,在轴资源中对其进行变换处理,输出到伺服控制器中,伺服控制器将规划位置与编码反馈的计数位置进行比较,获得跟随误差,并通过伺服控制算法得到实时的控制量,将控制量传递给D/A转换器,由D/A转换器转换成控制电压输出。

EP2C8F256C6是ALTERA公司CycloneⅡ系列芯片,其特点为高性能低功耗,核供电电压为1.2V,8256个逻辑单元(LEs),182个用户I/O口(项目中使用了157个I/O口),165888b 的部RAM,嵌入了18b的乘法器,每个乘法器又可拆成2个9b的乘法器,芯片部含有2个锁相环(PLL),8个全局时钟(Global Clocks)。

该芯片所具有的逻辑单元数、频率和用户I/O口等都能很好的满足设计需求。

FPGA的外围模块扩展如图3所示。

3.1 与DSP接口设计

DSP芯片的事件管理器(EVA,EVB)用于和FPGA连接,当输出脉冲量控制驱动器时,DSP使用两个事件管理器进行PWM波的控制,当输出模拟量时,DSP使用GPIOA/GPIOB向FPGA 输出规划位置。

3.2 模拟信号输出电路设计

采用D/A转换器AD669进行模拟信号的输出,AD669具有两级锁存,在设计中,将其四路D/A芯片的第一级锁存处于透明状态,第二级锁存控制信号LDAC连在一起,当四路D/A 芯片的数据预装好后,打开第二级锁存,四路D/A芯片即可同时转换,实现了四轴驱动的同时控制。

3.3 脉冲信号输出电路设计

脉冲输出电路由FPGA部精插补器完成,精插补器根据DSP发送来的粗插补数据产生均匀的脉冲输出,脉冲的输出有两种格式:“脉冲+方向”和“正负脉冲”。

由于差分信号对外部电磁等信号有很好的抗干扰性,特别是对共模干扰有很好的抑制作用。

所以脉冲经过光耦隔离后,再将信号接入差分线驱动器AM26LS31后输出,差分线驱动器AM26LS31的作用是将输入的单极性方波信号转化为一对极性相反的电机驱动信号。

3.4 编码反馈电路设计

电机编码信号直接传入电机驱动器中,电机驱动器将三对差分编码信号A+,A-,B+,B-,N+,N-作为反馈传给运动控制器。

在电机旋转时,所发出的编码信号会出现非常多的毛刺,并且经过驱动器大电源的干扰,如果直接接到FPGA中,可能会引起误判断,所以先将

三对编码信号经过差分芯片AM26LS32转化成单路信号A,B,N后再接入FPGA中。

芯片

AM26LS32功能是将输入的一对极性相反的编码器差分信号转化成单极性的脉冲信号,与

AM32LS31正好相反。

3.5 开关量接口和通用I/O电路设计

输出信号包括复位信号和使能信号,由FPGA产生,经光耦隔离后直接输出;输入信号包括驱动报警信号,正负限位信号和原点信号,这些信号经光耦隔离、电平转换后再由FPGA 接收,当FPGA检测到这些信号后,确定具体的触发信号,做出相应的反应。

另外运动控制器还提供了八路数字量输入通道和八路数字量输出通道,输入、输出通道都经光电隔离,以提高抗干扰性。

4 网口模块设计

DSP通过以太网控制器RTL8019AS与上位机连接,RTL8019AS在一块芯片上集成了

RTL8019AS核和一个16KB的SDRAM存储器,兼容RTL8019AS控制软件和NE20008b或16b传输,其接口符合Ethernet2和IEEE802.3标准。

RTL8019AS与主机的接口模式有三种模式:跳线模式,PnP模式,RT模式。

此运动控制器使用便于DSP应用的跳线模式。

DSP与RTL8019AS 的连接如图4所示。

(1)数据总线和地址总线。

RTL8019AS的数据总线和DSP的16位数据总线直接相连即可。

RTL8019AS片NE2000寄存器组都是通过其映射I/O端口进行访问,I/O端口共32个,地址偏移量为00H~1FH,把I/O基地址设为300H,则对应的I/O端口寻址围为:300H~31FH。

只需要10根地址线就可以对I/O端口进行寻址,把SA10~SA19接低电平,SA0~SA9按照表1接法即可。

由表1可以看出,只需要5根地址线就可以寻址32位I/O端口,所以可以直接把SA9,SA8接高电平,SA5~SA7接低电平,SA0~SA4与DSP的低5位地址线XA0~XA4相接。

(2)控制总线。

RTL8019AS片选信号AEN使用DSP的扩展片选信号

,IORB、IOWB直接与DSP的读写控制信号

相连,中断输出引脚INT0与DSP的XINT2相连,高电平有效的复位输入引脚与监控电路芯片SP708的RST相连,当DSP复位时,RTL8019AS也复位。

(3)RTL8019AS与网络介质接口。

RTL8019AS可以使用同轴电缆或双绞线作为传输媒介,将其AUI接口接地或悬空,使用BNC接口。

BNC接口方式支持8线双绞线或同轴电缆。

20F001N 是双绞线驱动器,为耦合隔离变压器模块,通过它可以去除因电路数字特性导致的高次谐波。

RTL8019AS与20F001N的连接如图4所示。

其差分输入信号TPIN+、TPIN-与差分输出信号TPOUT+、TPOUT-分别与20F001的对应引脚相连。

5 结语

在PC平台下,充分利用了DSP的数据处理能力和FPGA的硬件特性,使系统既能进行复杂的轨迹规划、高速插补,又能保证运动控制器的稳定性和精确性,这种运动控制器能应用于数控系统,机器人制造等控制领域。