PCB制图

使用AltiumDesigner软件制作PCB原理图电路图

使用AltiumDesigner软件制作PCB原理图电路图Altium Designer是一款功能强大、全面的PCB设计软件,可用于制作原理图和电路图。

以下是使用Altium Designer软件制作PCB原理图电路图的步骤和说明。

首先,打开Altium Designer软件并创建一个新的工程。

选择“File”选项,然后点击“New Project”或使用快捷键"Ctrl+N"来创建新项目。

选择“PCB Project”作为新项目的类型,并设置项目的名称和存储位置。

点击“Next”来继续。

接下来,选择“Blank Project”作为项目模板,并点击“Finish”来完成项目创建。

一旦绘制完电路图,可以添加文档选项卡来编写描述电路的文字。

单击工具栏中的“Add Document”按钮,并选择“Document”选项。

在弹出的对话框中,选择“Schematic Template”模板,然后点击“OK”。

在文档选项卡中,可以输入关于电路的详细信息和说明。

完成电路图设计后,可以进行电路模拟和验证。

点击工具栏中的“Simulate”按钮来打开电路模拟器。

设置所需的模拟参数,并运行模拟以评估电路的性能和功能。

当电路图设计完毕并通过模拟验证后,可以生成PCB布局。

点击工具栏中的“Design”按钮,选择“Create/Update PCB Document”来生成PCB布局。

最后,导出PCB布局文件并进行PCB制造。

选择菜单栏中的“File”选项,点击“Fabrication Outputs”和“Assembly Outputs”来导出相应的文件。

根据制造商提供的要求,准备所需的文件和材料,并提交给制造商进行下一步的制造过程。

综上所述,使用Altium Designer软件制作PCB原理图电路图的步骤包括创建新的工程、添加原理图,通过绘制电器元件和电路连接来设计电路图,添加文档选项卡来描述电路信息,进行电路模拟和验证,生成PCB布局并进行调整和修改,最后导出PCB布局文件进行PCB制造。

PCB制图实训报告

PCB制图实训报告学生姓名专业班级时间指导教师电子与电气工程系PCB制图实训一、实训目的本次实训是针对PCB制图课程结束后的一次综合实训,为检验和巩固学生对PCB制图学习成果以及提高其电子设计制作能力,以达到提高学生综合分析能力、实践技能的目的。

二、实训内容及要求1、实训内容以LM8361为主芯片,设计一个数字钟的PCB图,其原理图电路如图1至图5所示。

LM8361电路与其同类型的LM8363、LM8365曾经是我国专业工厂制作数字钟和定时收音机等应用电路的主芯片,具有性能稳定,走时功能、定时功能和睡眠功能,能够使用50Hz或60Hz频率作为数字钟的基准频率。

本电路是可以交流供电、也可以直流供电的应用电路。

因为数字中需要高精密度的信号源,因此在这里采用32768Hz的晶体振荡源,与CD4060、CD4012共同组成基准频率的电路,为LM8361提供60Hz的信号。

2、设计以TDA2030集成功放块为主芯片的功放电路,该集成电路具有过流、过压、过热的保护,其价格便宜、电路组成简单、且为单电源。

图1 数字钟电源电路图2 数字钟基准频率电路图3 数字钟电铃电路图4 数字钟主电路三、实训设计步骤1、数字钟电路原理图设计打开DXP,建立库文件,通过File/New/Project/PCB Project建立,然后在File/New/Schemotic建立原理图将此原理图移到库里面并通过File/Save As保存到U盘里面(1).数字钟电源电路放置VCC和地线,在工具栏找到电容并修改参数,通过Design/Browse Libraty/Diode找到二极管同时修改参数,搜索Header,点击Search输入Herder 选择Libraries on path点击Search找到该元件,放置两个,采用同样的方法搜索整流桥元件,最后按照给定的标准放置在合适的位置并使用Place Wire功能键将元件连接,大小控制好即可,使用Place Net Label在指定位置放置文字修改为VDD.(2).数字钟基准频率电路找到VCC和地线并放置适当的数量; 通过Design/Browse Libraty/XTAL 找到Y1;在Digital Device一栏放置电阻到适当位置,搜索CD4060BCN找到后修改为U1,搜索CD4012CN放置两个元器件,修改U3B时双击元器件,点击,最后使用Place Wire功能键将元件连接.(3).数字钟电铃电路找到VCC和地线并放置适当的数量,放置电阻,二极管从Design/Browse Libraty/Bell找到电铃. Design/Browse Libraty/PNP找到三极管.修改电阻,三极管,二极管参数并连线,在D6,D7之前放置文字改为SLEEPOUT, 最后使用Place Wire功能键将元件连接.(4).打开File/New/Library/Schematic Library用画图工具Place rectangle建立矩形框画U1 LM3861,通过Place/pin放置所需数量的引脚并调整好位置,修改文字等相关信息,用Design/Browse Libraty搜索Day Yellow-CA 放置四个修改1,6引脚以及名称等信息,参照前面绘图方法找出地线,VCC,电阻,三极管等元器件,使用搜索找出LED放置四个,在矩形框位置添加文字,以及Day Yellow-CA处同样添加文字,继续搜索出SW-PB元器件放置在上方,调整整体布局使之摆放合理。

pcb高级绘图

选择一个物 理连接

第4章 高级绘图

取消选择状态: 取消选择状态: 单击主工具栏上的 图标

4.2.2 对象的拷贝、剪切、粘贴 对象的拷贝、剪切、 SE提供了自己的剪贴板 对象的拷贝、 提供了自己的剪贴板, Protel 99 SE提供了自己的剪贴板,对象的拷贝、剪 粘贴都是在其内部的剪贴板上进行的。 切、粘贴都是在其内部的剪贴板上进行的。

第4章 高级绘图

Name: File Name:插入的图形文件名 Browse: Browse:单击此按钮可重新选择图 形文件 Width: Border Width:图片边框线宽度 Color: Border Color:图片边框线颜色 On:是否显示图片边框, Border On:是否显示图片边框, √表示显示 Ratio:是否保持图片X X:Y Ratio:是否保持图片X方向与 方向原有的比例关系, Y方向原有的比例关系,√表示保 持

a 确定圆心位置

b 确定横向 半径长度

c 确定纵向 半径长度

d 确定弧线起点

e确定弧线终点 确定弧线终点

4.1.7 绘制椭圆图形 图标或执行菜单命令Place|Drawing Tools|Ellipses ①单击 图标或执行菜单命令

第4章 高级Biblioteka 图在合适位置单击鼠标左键, ② 在合适位置单击鼠标左键,确定椭圆圆心 。 在合适位置单击鼠标左键,确定横向半径长度。 ③ 在合适位置单击鼠标左键,确定横向半径长度。 在合适位置单击鼠标左键,确定纵向半径长度。 ④ 在合适位置单击鼠标左键,确定纵向半径长度。 椭圆和圆的编辑方法可参见4.1.4中矩形的编辑方法。 4.1.4中矩形的编辑方法 椭圆和圆的编辑方法可参见4.1.4中矩形的编辑方法。 4.1.8 绘制扇形 ① 单击 图标或执行菜单命令Place|Drawing Tools|Pie 图标或执行菜单命令Place|Drawing charts 在合适位置单击鼠标左键, ② 在合适位置单击鼠标左键,确定扇形圆心 在合适位置单击鼠标左键, ③ 在合适位置单击鼠标左键,确定扇形半径 在合适位置单击鼠标左键, ④ 在合适位置单击鼠标左键,确定扇形的起点 在合适位置单击鼠标左键, ⑤ 在合适位置单击鼠标左键,确定扇形的终点

pcb绘图课件

学习改变命运,知 识创造未来

pcb绘图课件

电路原理图设计----原理图库绘制

3.绘制装饰

用画直线和椭圆的命令绘制“8.8.8.” 。

学习改变命运,知 识创造未来

pcb绘图课件

电路原理图设计----原理图库绘制

4.放置管脚编辑属性

放置10个元件管脚:管脚上的十字叉朝外。

十字叉

2.放置轮廓

3.绘制装饰

4.放置管脚 编辑属性

5.修改名称

学习改变命运,知 识创造未来

pcb绘图课件

电路原理图设计----原理图库绘制

1.新建文件

在工程中新建一个Schematic Library文件,并打开。

学习改变命运,知 识创造未来

pcb绘图课件

电路原理图设计----原理图库绘制

2.放置轮廓

主 01 要 教 02 学 内 03 容

PCB电路板设计

PCB绘图的基础知识 电路板的设计流程 PCB库建立

学习改变命运,知 识创造未来

pcb绘图课件

PCB线路板设计----基础知识

PCB线路板设计中常用各个 层 的含义。

• Toplayer----顶层走线层(默认红色)---顶层导线

顶层(Top layer)

Ctrl+C: 复制

Ctrl+X: 剪切 Ctrl+V: 粘贴

Ctrl+R:复制多个 Ctrl+D:复制一个(先选中元件)

SA(XA):选中(释放)所有的Байду номын сангаас件

鼠标左键点中元件+X:元件水平方向切换;Y垂直

点中元件+TAB键:打开元件属性编辑器

鼠标左键点中某元件+空格:元器件旋转

pcb原理图制作

pcb原理图制作

要制作无标题的PCB原理图,可以按照以下步骤操作:

1. 打开电路设计软件,如Altium Designer、Eagle等。

2. 创建一个新项目,并设置好工作区和单位。

3. 在工作区绘制电路图的基本框架,包括各个元件的位置和连接关系,但不要添加标题。

4. 选取合适的元件并放置到对应的位置,注意元件的方向和引脚连接。

5. 依次连接各个元件的引脚,确保连接正确无误。

6. 添加必要的电路标记,如电源、地线等,确保符号清晰可辨。

7. 通过工具栏或快捷键添加元件的数值、标识等信息,但不要使用相同的标题。

8. 检查电路图的连线和元件连接情况,确保没有错误或遗漏。

9. 根据设计需求,添加辅助元件,如测试点、跳线等。

10. 保存并导出电路图文件,可以选择保存为PDF、PNG等格式。

确保制作的电路图没有相同标题的文字,有助于提高可读性和减少混淆。

请注意,虽然本文提供了一般的PCB原理图制作

步骤,但具体软件操作略有差异,建议根据所使用的电路设计软件的教程进行操作。

pcb画图(入门)

`

焊盘间距设置

图7

⑥单击对话框中的各尺寸,使其处于可编辑状态,输入相应的值, 设置列间距为300mil,焊盘间距为100mil,单击Next按钮,进入 如图8所示的“器件边框线宽”对话框。

`

器件边框线框设置

图8 ⑦设置边框线宽为10mil,单击Next按钮,进入如图9所示的“器件管教个数” 对话框。

`

⑥自动布线后,手动加以修改。

`

⑦设置泪珠滴 所谓泪珠滴,就是在印制导线与焊盘或过孔相连时,为了增强连接的牢固 性,在连接处逐渐加大印制导线宽度。采用泪珠滴后,印制导线在接近焊 盘或过孔时,线宽逐渐放大,形状就象一个泪珠。添加泪珠滴时要求焊盘 要比线宽大,一般在印制导线比较细时可以添加泪珠滴。

`

手动制作元件封装

例子:创建三极管封装

PCB画图实例

利用NE555构成开关电源

`

创建DIP8封装模型

①在Protel 2004中选择File→New→Library→PCB Library命令, 以新建一个PCB封装文件,如下图。

`

②保存PCB封装文件(ctrl+s) `

③选择Toll→New component命令(图3),打开如下图4所示的Component Wizard对话框,单机Next按钮,进入如图5所示的“封装类型”对话框。

`

利用NE555构成开关电源

①画好原理图,如下图。

`

②首先,确定PCB的大小及形状。新建一个PCB文件,设置PCB大小、形状。 ③设置PCB的物理边界和电气边界。 ④在原理图上Design→undate PCB document,将元器件导入PCB中,并进 行合理的布局,如下图。

`

⑤对布线规则进行必要的设置,比如间距,线宽等参数,就可以使用Protel 2004强大的自动布线功能进行布线了。选择Auto Route→All…命令,单击 Route All按钮,则系统进行自动布线。

pcb原理图绘制

pcb原理图绘制

原理图绘制是电子电路设计的重要步骤之一。

在绘制原理图时,需要注意以下几点:

1. 命名规范:确保每个元件、引脚和连线都有唯一的命名,以便于后续编辑和检查。

2. 元件选择:根据电路需求选择合适的元件,并正确放置在原理图中。

可以使用标准元件库或自定义元件库。

3. 连线布局:按照电路的逻辑关系,用直线或曲线将元件的引脚连接起来。

确保连线的走向清晰简洁。

4. 引脚标识:在连线中使用标记符号表示引脚的功能,并进行适当的编号。

这有助于理解电路的功能和连接关系。

5. 文本标注:除了引脚标识,还可以添加文本标注来解释电路的功能、参数或注意事项。

要避免使用相同的标题或文字,以免造成混淆。

6. 细节标注:对于特殊的元件或连线,可以增加细节标注,比如元件的型号、参数或特殊操作要求等。

7. 文件格式:选择合适的文件格式保存原理图文件,常见的格式包括PDF、JPEG等。

同时,建议定期备份原理图文件,以

防数据丢失。

绘制原理图需要一定的专业知识和经验,遵循上述原则可以提高绘制效果和准确性。

同时,也要注意参考相关标准和规范,确保原理图的可读性和准确性。

PCB制图说明

印制电路板(PCB)设计规范前言本标准根据国家标准印制电路板设计和使用等标准编制而成。

本标准于1998年07 月30日首次发布。

本标准起草单位:CAD研究部、硬件工程室本标准主要起草人:吴多明韩朝伦胡庆虎龚良忠张珂梅泽良本标准批准人:周代琪目录1. 1 适用范围2. 2 引用标准3. 3 术语4. 4 目的.1 4.1 提供必须遵循的规则和约定.2 4.2 提高PCB设计质量和设计效率5. 5 设计任务受理.3 5.1 PCB设计申请流程.4 5.2 理解设计要求并制定设计计划6. 6 设计过程.5 6.1 创建网络表.6 6.2 布局.7 6.3 设置布线约束条件.8 6.4 布线前仿真(布局评估,待扩充).9 6.5 布线.10 6.6 后仿真及设计优化(待补充).11 6.7 工艺设计要求7. 7 设计评审.12 7.1 评审流程.13 7.2 自检项目附录1:传输线特性阻抗附录2:PCB设计作业流程Q/DKBA-Y004-1999印制电路板(PCB)设计规范1. 适用范围本《规范》适用于华为公司CAD设计的所有印制电路板(简称PCB)。

2. 引用标准下列标准包含的条文,通过在本标准中引用而构成本标准的条文。

在标准出版时,所示版本均为有效。

所有标准都会被修订,使用本标准的各方应探讨,使用下列标准最新版本的可能性。

[s1](附注注释shuwenyao不确定所引用的标准按国标、部标及国际标准排序;并按标准号由小到大排序。

特别注意:所列标准一定是在正文中被引用过的。

)GB 4588.3—88印制电路板设计和使用Q/DKBA-Y001-1999印制电路板CAD工艺设计规范1. 术语1..1 PCB(Print circuit Board):印刷电路板。

1..2 原理图:电路原理图,用原理图设计工具绘制的、表达硬件电路中各种器件之间的连接关系的图。

1..3 网络表:由原理图设计工具自动生成的、表达元器件电气连接关系的文本文件,一般包含元器件封装、网络列表和属性定义等组成部分。

4pcb绘制

或P+V

填充、线条、文字、圆弧等

该类元素在电路板上最终的效果与在那个层 绘制有关。在电气层绘制,则最终这些产生 的内容以敷铜的形式出现;如在丝印层则以 油墨的形式出现。

弧形

填充(矩形与多边形) 线 文字

•

安全在于心细,事故出在麻痹。20.10. 2020.10.2011: 20:4811:20:48October 20, 2020

•

踏实肯干,努力奋斗。2020年10月20日上午11时20分20.10. 2020.10.20

•

追求至善凭技术开拓市场,凭管理增 创效益 ,凭服 务树立 形象。2020年10月20日星期 二上午11时20分48秒11:20:4820.10.20

Designator Footprint

J1

HDR1X3

J2

HDR1X5

JP1

HDR1X2

U1

DIP-14/D19.7

U2

DIP-14/D19.7

U3

DIP-14/D19.7

•

树立质量法制观念、提高全员质量意 识。20. 10.2020.10.20Tuesda y, October 20, 2020

(绘制单层板)

Description Header, 3-Pin Header, 5-Pin Header, 2-Pin Dual J-K Flip-Flop with Clear Dual J-K Flip-Flop with Clear Dual J-K Flip-Flop with Clear

ignore obstacle:设置进行交互式走线时,如果遇到障碍 物,则视同没有,直接把它压过去; avoid obstacle:设置进行走线时,如果遇到障碍物,则 避开它,不可以压过去; push obstacle:设置进行交互式走线时,如果遇到障碍物, 则将障碍物推开,让我们的走线优先走过

PCB原理图绘制步骤

原理图的绘制A、新建工作空间和原理图项目是每项电子产品设计的基础,在一个项目文件中包括设计中生成的一切文件,比如原理图文件、PCB图文件、以及原理库文件和PCB库文件。

在项目文件中可以执行对文件的各种操作,如新建、打开、关闭、复制与删除等。

但是需要注意的是,项目文件只是起到管理的作用,在保存文件时项目中的各个文件是以单个文件的形式存在的。

所以每完成一个库就保存一次。

新建工作区间1、在菜单栏中选择File-New-Project-PCB Project.2、形成一个PCB-Project1.PriPCB面板然后重命名最后分别添加scematic sheet形成Sheet.SchDoc文件保存后面一次添加形成PCB.PcbDoc、Pcblib.Pcblib、schlib.schlib文件分别进行保存。

3、在schlib.schlib文件里面添加你需要的库文件进行保存这时候要区分引脚与网口标号,特别是引脚一定要放置正确按照所发的书上进行标号,创建一个库就保存一次直到你需要的几个模块的器件你都画好了。

4、然后找到库文件将你画好的东西放置到Sheet.SchDoc原理图上面这时候再来放置网口标号用线将该连接的地方连接起来画好了看看自己的和书上的区别检查是否有错误的地方,最后将文件进行保存。

点击Libraries面板,点左上角Libraries按钮,如果你想在所有工程里都用就在Imstalled里点Install添加,如果只想在当前工程里使用就在Projiect里面点Add Library。

5、画封装图。

根据我们焊电路板的板子来测量距离将需要的器件进行封装,封装的过程中那一页会出现一个十字号将焊盘放置在十字号上确保第一个焊盘的x、y值都为零然后按照自己测量的数据一次拍好焊盘在一个在Top Layer这一层上放置,防止完成后切换到Top Overlay上面进行划线封装。

对于LED灯要表明它的正极同样的道理没画好一个库进行一次保存直到最终完成了。

pcb板的原理图制作流程

pcb板的原理图制作流程PCB板的原理图制作流程包括以下几个步骤。

1. 需求分析:根据项目需求,确定电路的功能和性能指标,明确所需元件和连接方式。

2. 器件选择:根据需求分析,选择合适的电子器件,包括集成电路、电阻、电容、晶体管等,并记录其性能参数。

3. 原理图绘制:使用电子设计自动化(EDA)软件,按照需求分析和器件选择的结果,绘制原理图。

注意将每个元件的封装型号、引脚标号等详细信息包含在原理图中。

4. 线路连接:根据原理图上的电路连接关系,使用EDA软件进行线路的连接。

确保连接的准确性,包括正确连接元件的引脚,不出现短路或开路等问题。

5. 标注与注释:对重要的电路节点和电子器件进行标注,方便后续的调试和维护。

添加注释说明电路的功能和设计意图。

6. 自动布局:使用EDA软件的布局工具对电子器件进行布局。

考虑分隔高频和低频信号的区域,尽量减小线路的长度,提高电路的抗干扰性。

7. 手工调整布局:根据需要,手动调整布局,优化布线方案,并确保不会有短路或干扰。

8. 线路布线:使用EDA软件的布线工具进行线路的布线。

遵循规则,分配线宽、间距和层数,确保布线的可靠性和稳定性。

9. 贴片元件布置:根据线路布线的情况,调整贴片元件的位置,使得布线更加顺畅和合理。

10. DRC检查:进行设计规则检查(DRC),确保电路符合制造工艺的要求,如最小线宽、最小孔径等。

11. 输出生成:根据设计要求,生成PCB板的制造文件,如Gerber文件,以便进行后续的PCB制造和组装。

以上是PCB板的原理图制作流程,根据这个流程可以完成整个原理图设计的过程。

cadence PCB 画图(傻瓜教程快速入门)

cadence画PCB板傻瓜教程(转帖)一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1Page Properties,在Page Size中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

PCB丝印图制作说明

PCB丝印图制作说明

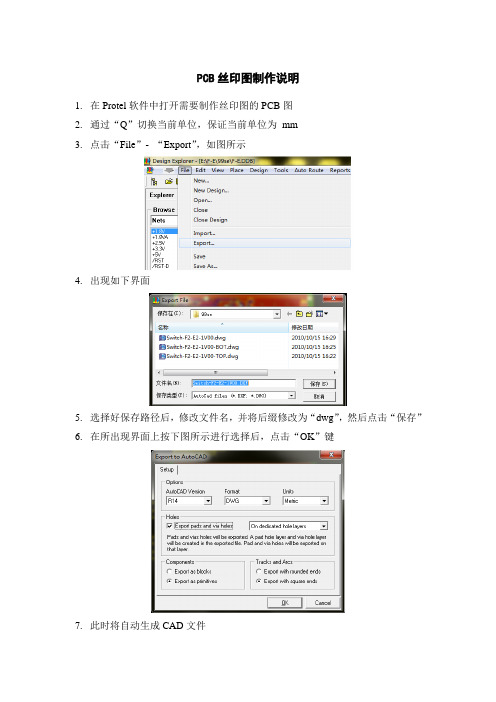

1.在Protel软件中打开需要制作丝印图的PCB图

2.通过“Q”切换当前单位,保证当前单位为mm

3.点击“File”- “Export”,如图所示

4.出现如下界面

5.选择好保存路径后,修改文件名,并将后缀修改为“dwg”,然后点击“保存”

6.在所出现界面上按下图所示进行选择后,点击“OK”键

7.此时将自动生成CAD文件

8.打开CAD文件,可用“Z –空格– E –空格”快捷键使得图形居中显示

9.在CAD文件中需做下列处理:

➢图形颜色全部更改为白色,并删除板外的注释信息;

➢对于顶层丝印图除顶层丝印层、禁止布线层、机械1层外,其它图层内信息全部删除

➢对于底层丝印图除底层丝印层、禁止布线层、机械1层外,其它图层内信息全部删除,并对丝印图做镜像处理

➢增加图幅边框,并修改相应图纸信息;

➢将丝印图移至图幅中心,并适当放大;

2011.01.07(完)。

PCB的设计与制作PPT课件

电磁干扰是由电磁效应而造成的干扰,由于PCB上的元器件及布线越 来越密集,如果设计不当就会产生电磁干扰。为了抑制电磁干扰,可采 取如下措施: (1)合理布设导线

印制线应远离干扰源且不能切割磁力线;避免平行走线,双面板可以 交叉通过,单面板可以通过“飞线”跨过;避免成环,防止产生环形天

第2章 PCB的设计与制作

PCB的电源线和接地线因电流量较大,设计时要适当加宽,一般不要小 于

l mm。对于安装密度不大的PCB,印制导线宽度最好不小于0.5mm,手 工

制板应不小于 0.8 mm。 (2)印制导线间距

由它们之间的安全工作电压决定。相邻导线之间的峰值电压、基板的 质量、表面涂覆层、电容耦合参数等都影响印制导线的安全工作电压。

维修等方面的要求;元器件排列整齐、疏密得当,兼顾美观性。 (2)元器件布局原则:见p78页 (3)元器件布局顺序 (4)常用元器件的布局方法 2 .元器件的排列方式

元器件在PCB上的排列可采用不规则、规则和网格等三种排列方式中 的一种,也可同时采用多种。 3 .元器件的间距与安装尺寸 (1)元器件的引脚间距

第2章 PCB的设计与制作

在PCB设计中,一般采用双面板或多面板,每一层的功能区分都很明确。 在多层结构中零件的封装有两种情况,一种是针式封装,即焊点的导 孔是贯穿整个电路板的;另一种是STM封装,其焊点只限于表面层; 元器件的跨距是指元器件成形后的端子之间的距离。

第2章 PCB的设计与制作

基板是由高分子合成树脂和增强材料组成的绝缘层板;在基板的表面覆 盖着一层导电率较高、焊接性良好的纯铜箔,常用厚度35~50μm; 铜箔覆盖在基板一面的覆铜板称为单面覆铜板,基板的两面均覆盖铜 箔的覆铜板称双面覆铜板;铜箔能否牢固地覆在基板上,则由粘合剂 来完成。常用覆铜板的厚度有1.0mm、1.5mm和2.0mm三种。

绘制PCB图

多层板 多层板就是包含了多个工作层面的电路板。 多层板就是包含了多个工作层面的电路板。除了上面讲 到的顶层、底层以外,还包括中间层、内部电源或接地层等。 到的顶层、底层以外,还包括中间层、内部电源或接地层等。 多层电路一般指三层以上的电路板。 多层电路一般指三层以上的电路板。 从外表看起来多层板和双面板没有什么两样, 从外表看起来多层板和双面板没有什么两样,但多层板 中还有一些导电层存在, 中还有一些导电层存在,如同双面板的上下两层铜泊一样可 以被腐蚀,然后层压在一起。 以被腐蚀,然后层压在一起。上下两层和中间层之间用过孔 VIA进行电气连接,此外还有一个电源层也是如此。 进行电气连接, 进行电气连接 此外还有一个电源层也是如此。

+

+

过孔分为三种:从顶层贯穿至底层的穿透式过孔 过孔分为三种:从顶层贯穿至底层的穿透式过孔; 穿透式过孔; 只实现顶层或底层与中间层连接的盲孔 盲孔; 只实现顶层或底层与中间层连接的盲孔;只实现中 间层连接,而没有穿透顶层或底层的埋孔 埋孔。 间层连接,而没有穿透顶层或底层的埋.2电路板的工作层

打开PCB文件进入PCB编辑器,执行Design— Board Layers&Colors弹出工作层设置对话框如下

电路板的工作层类型大致分为以下几类 1 Signal layer(信号层 信号层) 信号层 主要用于布置电路板上的导线和走线, 主要用于布置电路板上的导线和走线,包括 Top layer(顶层)、Bottom layer(底层) (顶层) (底层) )(Protel 2004最多 和MidLayer(中间层)( (中间层)( 最多 提供16个中间层 个中间层)。 提供 个中间层)。

3.1.1 电路板的结构与分类

PCB的常见结构 的常见结构 PCB是英文 是英文Print Circuit Broad 的英文缩写,中文 的英文缩写, 是英文 含义为印刷电路板。印刷电路板是一块绝缘材料板、 含义为印刷电路板。印刷电路板是一块绝缘材料板、 在表面合理安放有各种电子元件( 在表面合理安放有各种电子元件 ( 此过程称为布 局)、在表面安排有连接电子元件引脚间的金属铜 膜导线(此过程称为布线) 膜导线( 此过程称为布线) 、以及连接不同表面的 铜导孔组成。按复杂程度将印刷电路板分为三类: 铜导孔组成。按复杂程度将印刷电路板分为三类: 单面印刷电路板 双面印刷电路板 多层印刷电路板

画PCB图详细步骤

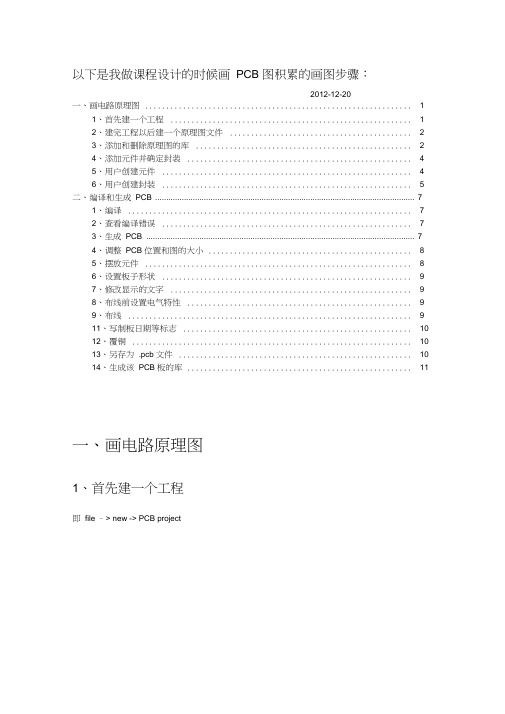

以下是我做课程设计的时候画PCB 图积累的画图步骤:2012-12-20一、画电路原理图 (1)1、首先建一个工程 (1)2、建完工程以后建一个原理图文件 (2)3、添加和删除原理图的库 (2)4、添加元件并确定封装 (4)5、用户创建元件 (4)6、用户创建封装 (5)二、编译和生成PCB (7)1、编译 (7)2、查看编译错误 (7)3、生成PCB (7)4、调整PCB 位置和图的大小 (8)5、摆放元件 (8)6、设置板子形状 (9)7、修改显示的文字 (9)8、布线前设置电气特性 (9)9、布线 (9)11、写制板日期等标志 (10)12、覆铜 (10)13、另存为.pcb 文件 (10)14、生成该PCB 板的库 (11)一、画电路原理图1、首先建一个工程即file –> new -> PCB project2、建完工程以后建一个原理图文件file->new ->schematic 。

这就建立了原理图文件,之后就在这个文件上画原理图。

同时建立一个 PCB 文件, file->new->PCB ,然后可以在这个文件中画 PCB 图。

注意:默认显示的库只有元件库,而没有封装( footprint )库。

如果要在 PCB 文件下放 入封装,则需要点击 library 下一行最右边的三角标志,然后在 footprint 前面打勾。

如下图3、添加和删除原理图的库点右侧 library 对话框,在 installed里面先删除所有的库。

如下图:注意,若是某个元件在这个库中找不到,可以点 library 右侧的 search 查找包含某个元 件名称的库。

注意:默认显示的库只有元件库,而没有封装( footprint )库。

如果要在 PCB 文件下放 入封装,则需要点击 library 下一行最右边的三角标志,然后在 footprint 前面打勾。

如下图然后添加我们需要的库:首先最常用的是 电阻电容等的原理图,同时也包含它们的封装,另外 miscellaneous devices 的 miscellaneous connectors 库也要添加,里面有各种接口,如查排等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Protel 99 SE

protel 各层的解释;

Toplayer 顶层布线

Bottomlayer 底层布线

Topoverlayer 顶层字符丝印

Bottomlayer 底层字符丝印

Multilayer 多层布线(多用在过孔焊盘)

keepoutlayer 机械层(禁止布线)

solder 焊锡(可以让走线不加阻焊)

PCB绘制流程

1.原理图制作

1.原理图绘制前提(原理图库(元器件规格书,日积月累))

建库关键点:

1.新建一个器件Tool->new component

2.修改器件名称Tool-> Rename component

3.pin(引脚)的number(序号)要与实际引脚相对应

4.pin(引脚)的name(名称)加"\"会产生一个上划线(即低电平有效)

5.PIN脚短一点,画原理图是有更多的空间;

6.一个器件分成两部分Tool-> New part(重点)

7.预置封装及位号左侧栏的Description

8.更新原理图:修改一个器件后用左侧栏的Update Schematics

2.开始制作原理图

关键点:

1.图纸尺寸,一般用自定义A4纸,打开安装目录底的

system->Templates,复制A4纸,修改成自己需要的A4纸,在绘制原理图的窗口选择Ddsign->Templates->set Templates,选择刚刚保存的A4纸

2.把所需要的器件放在原理图纸上,整齐放置,再通过多次修整,使布

线也能整齐;器件及布线以水平或垂直放置;

3.在器件属性里面的PART写上器件的参数;

4.在器件属性里面的footprint写上封装库里的封装;

5.把器件属性里面的Designate改成?如电容C?二极管D?,再选择

Tool->annotate自动编号,防止重复编号

6.生成用于PCB布线的网络表Design->create netlist

7.生成简易BOM reports->bill material->protel format, 新建txt文

件后用固定宽度导入excel生成简易BOM

8.更新PCB,Design->update PCB

9.取出原理图的器件作为封装库Design->make project library

10.常用快捷键:page up原理图放大,page down 原理图缩小,X

水平翻转,Y垂直翻转,space 90度旋转,XA取消选中,Table 查看修改属性, VF居中最大显示

★日积月累:建一个自己的库,新建一个mylibrary.ddb,在此DDB里面放置自己所需要的原理图库,PCB封装库,自定义纸张大小等,以后新项目时只需加载此DDB。

3.PCB制作前的准备,制作并加载PCB库;

建PCB库关键点:

1.单位切换到mm,按Q键

2.珊格大小设置L->option(画线时XY设置0.01mm,放焊盘是大小为焊盘间距);

3.新建一个器件封装,Tool->new component或左侧栏Add->取消->renamez(用封装命名)

4. 通过调整珊格,放置焊盘

5.设置原点EF,画边框线JL;

6.按EFC,设置器中心点为原点;

7.保存或用改过的封装更新PCB板,Update PCB

8. 删除器件,Remove

注意事项: 1.画封装时要有实物或对照规格书,孔径比实物大0.2mm,焊盘比孔径大1-1.5mm,封装的大小的体现出,避免叠在一起;

2.不能有空器件,Protel会死掉;

3.一定要设置原点,否则放置器件时可能会打不到在哪里;

.常用快捷键:page up PCB放大,page down PCB缩小,X水平翻转,Y垂直翻转,space 角度旋转,XA取消选中,Table 查看修改属性,Q

单位切换,EFC设置器件中心为0坐标。

EF设置0坐标,OP参数

设置,L,打开层开关管理,VF居中最大显示,JL跳置某坐标;

4.画PCB

1.单位切换到mm,按Q键

2.珊格大小设置L->option(都设置0.01mm)

3.加载PCB封装库,左侧栏browse->library->add/remove

4.在keepoutlayer画边框线或从CAD导入边框图,File->import(需

DXF文件

5.加载网络表;designe->load nets->browse选择从原理图生成的网络表;

6.分开加载的器件Tool->interactive placement ->left

7.隐藏所有器件的comment的属性;

8.取消选中XA,并将位号移动到器件旁;

9.器件布局,根据原理图将器件从左到右从或从上到下按顺序放置,注意贴片器片只能90旋转,插件器件可任意角度旋转;贴片器件放置尽量同一个方向,从波峰焊的良率考虑;有芯片的地方,周围的器件尽量靠近芯片;特别是旁路(去藕)电路;

点中器件按L可切换放置层,

10.设置布线规则:Design->rule->routing->clearance constraint 电气间隔设置(电压50V以上设置0.9mm,50V以下设置0.6mm;

Design->rule->routing->Width Constraint 布线宽度设定,最小0.3mm,最大2mm,根据电流大小设置其属性,在空间足够的情况下,尽量放大线宽至0.5mm,电流密度30A/mm2,铜厚35um(1盎司);即1mm的宽度载1A的电流;

Design->rule->Manufacturing->Polygon connect Style大面积连接设置,可设0.5mm或直接连接;

Design->rule->Placement->component clearance 器件间隙,一般不选,去掉打勾;

11.按OP可设置大小光标,空格键旋转角度,是否自动移除画线;

12.画线,根据网络表及原理图将器件的焊盘连接起来,主环路尽量短,避免EMI问题;

13.测量两点距离:Reports->measure distance

14.放器件的标号放置在该器件旁,同一方向放置,并且放置在贴完或插完器件可以看到的位置;

15.全局变化:选择其中一个属性->Global>>->修改属性-same->OK;

16.选中同一网络的铜箔SP,方面检测及删除;

17.临时更改某个器件的封装,属性->去掉Lock prims勾选;后再打勾;

18.锁定某些器件的位置属性->勾选Locked;

19.生成泪滴焊盘tool->teardrop->add->oK

20.移动图纸,按住右键可移动;

21.添加网络标号:design->netmanage->nets in class->add.

22.修改焊盘网络标号属性->advance->net

23.带网络表重复标号粘贴EA;

24.删除键ED;

25.阵列,点击arrary按键可矩形或圆形阵列;

26.提起PCB封装,design->make library;

27..铝基板外边框与布线的距离设置,建一中间层加网络号28.拼版,。