数字集成电路设计复习课

数字集成电路设计基础

数字集成电路设计基础

1. 数字逻辑

•布尔代数

•组合逻辑电路

•时序逻辑电路

•状态机

2. CMOS 技术

•CMOS 器件的结构和特性•MOS 晶体管的开关特性•CMOS 逻辑门

•CMOS 存储器

3. 数字集成电路设计流程

•系统规范

•架构设计

•逻辑设计

•物理设计

•验证和测试

4. 组合逻辑电路设计

•门级优化

•多级逻辑优化

•可编程逻辑器件 (FPGA)

5. 时序逻辑电路设计

•时钟和复位电路

•触发器和锁存器

•同步和异步时序电路

6. 存储器设计

•静态随机存取存储器 (SRAM) •动态随机存取存储器 (DRAM) •只读存储器 (ROM)

•闪存

7. 芯片设计中的布局和布线

•布局约束和规则•布线算法

•时序和功耗优化8. 验证和测试

•功能验证

•时序验证

•制造测试

9. 数字集成电路应用•微处理器和单片机•数字信号处理•通信系统

•嵌入式系统

其他重要概念:

•数制转换

•可靠性和容错性•EDA 工具

•低功耗设计

•可制造性设计。

集成电路设计复习资料

集成电路设计复习资料集成电路设计是一门涉及电子工程、计算机科学和物理学等多学科交叉的领域,对于现代电子技术的发展起着至关重要的作用。

以下是为大家整理的集成电路设计的复习资料,希望能对大家的学习有所帮助。

一、集成电路的基本概念集成电路(Integrated Circuit,简称 IC)是将大量的电子元件(如晶体管、电阻、电容等)集成在一个微小的芯片上,实现特定功能的电路。

其优点包括体积小、重量轻、性能高、可靠性强等。

集成电路的分类方式众多,按照集成度可分为小规模集成电路(SSI)、中规模集成电路(MSI)、大规模集成电路(LSI)、超大规模集成电路(VLSI)和特大规模集成电路(ULSI);按照功能可分为数字集成电路、模拟集成电路和混合信号集成电路;按照制造工艺可分为双极型集成电路、CMOS 集成电路等。

二、集成电路设计流程集成电路设计是一个复杂而系统的工程,通常包括以下几个主要步骤:1、系统规格定义在这一阶段,需要明确设计的目标和要求,包括功能、性能、功耗、成本等方面的指标。

同时,还需要对市场需求、竞争情况进行分析,以确定设计的可行性和竞争力。

2、算法设计与优化对于数字集成电路,需要设计相应的算法,并对其进行优化,以提高性能和降低资源消耗。

例如,在图像处理领域,需要设计高效的图像压缩算法。

3、逻辑设计将算法转换为逻辑电路,使用硬件描述语言(如Verilog 或VHDL)进行描述。

逻辑设计包括组合逻辑和时序逻辑的设计。

4、电路设计根据逻辑设计,进行晶体管级的电路设计,包括晶体管尺寸的确定、偏置电路的设计等。

5、物理设计将电路设计转换为实际的版图,包括布局(确定各个元件在芯片上的位置)和布线(连接各个元件)。

物理设计需要考虑工艺规则、寄生效应等因素,以保证芯片的性能和可制造性。

6、验证与测试对设计进行各种验证,包括功能验证、时序验证、物理验证等,以确保设计的正确性。

同时,还需要进行芯片的测试,包括晶圆测试和封装测试。

数字集成电路复习要点

数字集成电路复习要点⼀、简答题1.集成电路发展的特点:速度变快,I/O增多,⼯作电压下降……A,特征尺⼨越来越⼩,B,单个芯⽚晶体管数⽬越来越多,速度越来越快,电压越来越⼩,层数越来越多,端⼝越来越多,功耗越来越低2.P181⼤扇⼊的“设计技术”。

A,调整晶体管尺⼨B,逐级加⼤晶体管尺⼨C,重新安排输⼊D,重组逻辑结构(把光键路径上的晶体管靠近门的输出端)3.简述集成电路⼯艺中典型的光刻步骤及其相互关系。

(P28)氧化层,涂光刻胶,光刻机曝光,光刻胶的显影和烘⼲,酸刻蚀,旋转清洗和⼲燥,各种⼯艺加⼯步骤,去除光刻胶4.什么是多晶⾃对准⼯艺,有哪些优点?(P32)在掺杂之前形成图形的多晶硅栅实际确定了沟道区的确切位置,从⽽也确定了源区和漏区的位置。

它使源和漏这两个区域相对于栅具有⾮常精确的位置,有助于减⼩晶体管中的寄⽣电容。

5.CMOS逻辑门特性:(全摆幅,⽆⽐性,低输出阻抗,⾼输⼊阻抗,⽆静态功耗。

)A,电压摆幅等于电源电压,噪声容很⼤,B,逻辑电平与器件的相对尺⼨⽆关,⽆⽐逻辑,C,具有低输出阻抗,⾼输⼊阻抗,D,不消耗任何静态功率6.伪NCMOS门逻辑的特点A,减少晶体管的数⽬,由2N减到N+1,B,速度快缺点:⼩的噪声容限和⼤的静态功耗6.传输管逻辑的优点是什么?有哪些缺点,解决的办法是什么?优点:结构简单,阀值损失⼩,硬件开销⼩缺点:延时⾼,仅含NMOS的传输管将引起静态功耗并减⼩噪声容限解决办法:避免开关长串联以减⼩延时,增加电平恢复晶体管以消除静态功耗7.什么是时钟馈通,有何危害?(P215)原理:电容耦合的特殊情况,由在预充电器件的时钟输⼊和动态输出节点之间电容耦合引起的效应,当下拉⽹络不导通时,这⼀电容耦合会在时钟由低⾄⾼翻转时,引起的动态节点输出上升到VDD以上;⽽快速上升和下降时时钟边沿会耦合到信号节点上。

特点:a)可能使预充电管正常情况下反偏结⼆极管变为正向偏置,使电⼦注⼊到衬底中,被附近处于⾼电平的⾼阻节点收集,导致出错。

数字集成电路复习总结15页PPT

•

29、在一切能够接受法律支配的人类 的状态 中,哪 里没有 法律, 那里就 没有自,也可以废除 法律。 ——塞·约翰逊

21、要知道对好事的称颂过于夸大,也会招来人们的反感轻蔑和嫉妒。——培根 22、业精于勤,荒于嬉;行成于思,毁于随。——韩愈

23、一切节省,归根到底都归结为时间的节省。——马克思 24、意志命运往往背道而驰,决心到最后会全部推倒。——莎士比亚

25、学习是劳动,是充满思想的劳动。——乌申斯基

谢谢!

数字集成电路复习总结

•

26、我们像鹰一样,生来就是自由的 ,但是 为了生 存,我 们不得 不为自 己编织 一个笼 子,然 后把自 己关在 里面。 ——博 莱索

•

27、法律如果不讲道理,即使延续时 间再长 ,也还 是没有 制约力 的。— —爱·科 克

•

28、好法律是由坏风俗创造出来的。 ——马 克罗维 乌斯

数字集成电路复习总结

第二章 制作工艺

不同工艺层的作用 自对准工艺 设计规则:

设计规则

版图设计工程师和工艺工程师之间的接口 指导构造工艺掩模板 单位尺寸:最小线宽(版图中使用的单位) 可按比例变化的规则:lambda (λ)参数 绝对尺寸:微米规则

第三章 器件

MOS晶体管

加法器

十一章 设计运算功能块

超前进位加法器

点运算公式 11.4 加法树(对应点运算的公式) 基2-(基4-)GP点运算的电路实现(4位加法器的 进位逻辑表达式),图11.21 11.23 11.24 定义:阵列乘法器,部分积 波兹编码乘法器 保留进位乘法器 Wallace树乘法器

逻辑努力:F=GBH

第六章 CMOS组合逻辑门:其他门电 路

有比逻辑:

电阻负载: 伪NMOS:VM VIH、VIL、NMH、NML的计算 差分级联电压开关逻辑(逻辑电路设计和识别) 阈值电压损失及解决方法 互补传输管逻辑:电路设计

传输晶体管逻辑(电路设计)

动态CMOS门电路

Lcrit >> tpgate/0.38rc

导线的rc延时只有在输入信号的上升(下降)时间 小于RC时才予以考虑,即trise < RC

如果不满足上式,信号的变化将慢于导线带来的延迟, 因此采用集总电容模型就够了

© MJIrwin, PSU, 2000

第五章 CMOS反相器

电压转移特性(VTC):不同区域pmos、 nmos工作状态

反向门阈值(中点)电压VM的近似计算 VIH、VIL的计算 NMH、NML的计算

数电复习PPTppt课件

F AC BC AD BD AB AC • BC • AD • BD • AB

第 22 页

例:将下列各函数用或非门实现

F m(0,2,8,10,14,15)

解:用圈0的方法

F BC BD AB

F (B C)(B D)( A B)

BCBD AB

第 23 页

例:用卡诺图将下列含有无关项的逻辑函数化简为最简 “与或”式和最简“或与”表达式。

1×20+1×2-1+1×2-2+1×2-3=(109.875)10 例:将十进制数225.246转换为二、八和十六进制数 解:(1)(225.246)10=(11100001.011)2

(2)(225.246)10=(341.175)8 (3)(225.246)10=(E1.3E)16

第 17 页

CMOS 4

输入

输出

位 双 向 移 位 寄

清 零

CR

L H H H

控制信 号

S1 S0

×× LL LH LH

串行输 右入左 移移 DS DS

×R ×L ×× L× H×

时 钟

CP

× × ↑ ↑

并行输入

DI0

DI1

DI2

DI3

Q0n1

Q1n1Q

2n1Q

n1 3

行

× × × × L L L L1

×

×

×

ABC BC AC D

A BC AC D

A BC

例:用公式法证明下列等式 A⊕B⊕C=A⊙B⊙C

解: A B C ( A B)C ( A B)C

( AB)C ( AB)C ABC

第 19 页

例:用公式法化简

《数字集成电路设计》课件

深入研究加法器和减法器的原理,了解如何进行数字的加法和减法运算。

贝叶斯定理在电路设计中的应 用

介绍贝叶斯定理在电路设计中的应用场景,讲解如何利用先验知识和观测结 果进行后验概率的计算。

层级与模块化设计

层级设计

了解层级设计的原理和方法,掌握如何将复杂的电 路分解为多个模块进行设计和测试。

仿真实例

通过案例分析和实际仿真实例,加深对 电路仿真工具和流程的理解和应用。

计算机辅助设计方法与工具介 绍

介绍计算机辅助设计的基本原理和方法,以及常用的电路设计工具,包括EDA 软件和硬件描述语言。

引言

数字集成电路设计是现代信息技术的关键领域,本课程将深入探讨数字电路 设计的理论和实践,为学生打下坚实的基础。

逻辑门与布尔代数

了解常用逻辑门的工作原理,掌握布尔代数的基本概念和运算规则,为后续的电路设计奠定基础。

时序逻辑电路设计基础

1

触发器和计数器

2

深入研究各种触发器和计数器的原理和

应用,掌握时序逻辑电路的设计技巧。

《数字集成电路设计》PPT课件

数字集成电路设计PPT课件大纲: 1. 引言 2. 逻辑门与布尔代数 3. 时序逻辑电路设计基础 4. 组合逻辑电路设计 5. 贝叶斯定理在电路设计中的应用 6. 层级与模块化设计 7. 电路仿真工具与流程 8. 计算机辅助设计方法与工具介绍 9. 电路优化与验证 10. 技术与制造工艺介绍 11. 功耗优化与电源管理 12. 嵌入式系统设计基础 13. CPU架构设计基础 14. SOC(系统片上集成电路)设计基础 15. 集成电路测试方法与介绍

模块化设计

学习模块化设计的思想和技术,掌握如何将多个模 块进行组合,实现复杂功能的集成电路设计。

数字集成电路--电路、系统与设计(第二版)复习资料

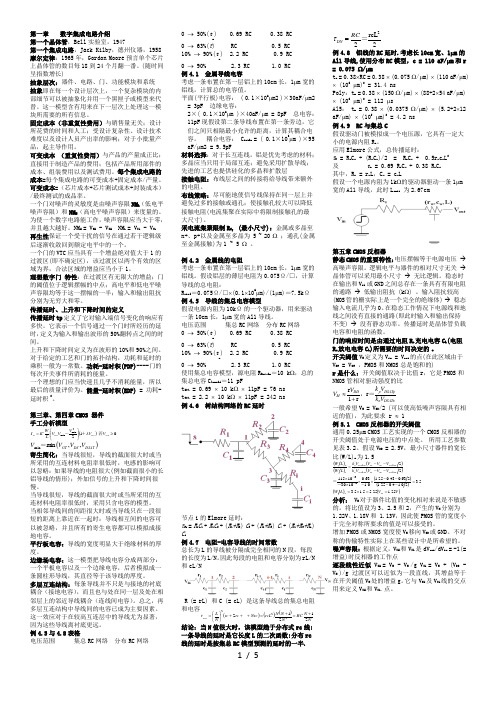

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

数字集成电路复习讲义.53页PPT

31、园日涉以成趣,门虽设而常关。 32、鼓腹无所思。朝起暮归眠。 33、倾壶绝余沥,窥灶不见烟。

34、春秋满四泽,夏云多奇峰,秋月 扬明辉 ,冬岭 秀孤松 。 35、丈夫志四海,我愿不知老。谢谢你的阅读来自❖ 知识就是财富 ❖ 丰富你的人生

71、既然我已经踏上这条道路,那么,任何东西都不应妨碍我沿着这条路走下去。——康德 72、家庭成为快乐的种子在外也不致成为障碍物但在旅行之际却是夜间的伴侣。——西塞罗 73、坚持意志伟大的事业需要始终不渝的精神。——伏尔泰 74、路漫漫其修道远,吾将上下而求索。——屈原 75、内外相应,言行相称。——韩非

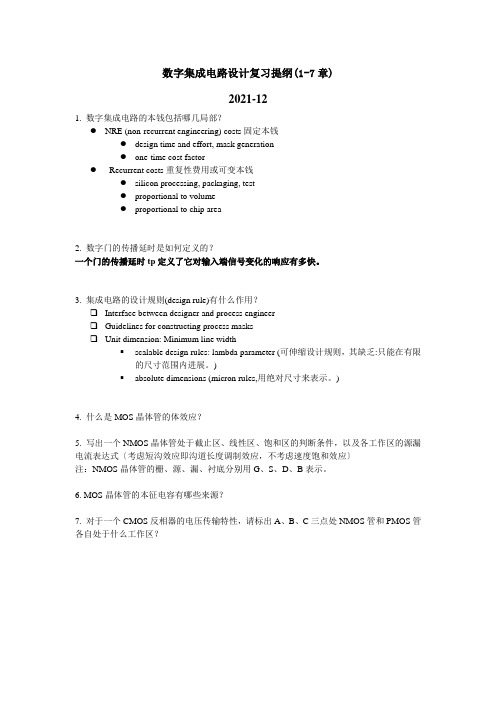

数字集成电路设计复习提纲

数字集成电路设计复习提纲(1-7章)2021-121. 数字集成电路的本钱包括哪几局部?●NRE (non-recurrent engineering) costs固定本钱●design time and effort, mask generation●one-time cost factor●Recurrent costs重复性费用或可变本钱●silicon processing, packaging, test●proportional to volume●proportional to chip area2. 数字门的传播延时是如何定义的?一个门的传播延时tp定义了它对输入端信号变化的响应有多快。

3. 集成电路的设计规则(design rule)有什么作用?❑Interface between designer and process engineer❑Guidelines for constructing process masks❑Unit dimension: Minimum line width▪scalable design rules: lambda parameter (可伸缩设计规则,其缺乏:只能在有限的尺寸范围内进展。

)▪absolute dimensions (micron rules,用绝对尺寸来表示。

)4. 什么是MOS晶体管的体效应?5. 写出一个NMOS晶体管处于截止区、线性区、饱和区的判断条件,以及各工作区的源漏电流表达式〔考虑短沟效应即沟道长度调制效应,不考虑速度饱和效应〕注:NMOS晶体管的栅、源、漏、衬底分别用G、S、D、B表示。

6. MOS晶体管的本征电容有哪些来源?7. 对于一个CMOS反相器的电压传输特性,请标出A、B、C三点处NMOS管和PMOS管各自处于什么工作区?Out InV DDPMOSNMOS8. 在CMOS 反相器中,NMOS 管的平均导通电阻为R eqn ,PMOS 管的平均导通电阻为R eqp ,请写出该反相器的总传播延时定义。

数字集成电路--电路、系统与设计(第二版)复习资料

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

湖北省考研集成电路设计与集成系统复习资料数字电路与模拟电路解析

湖北省考研集成电路设计与集成系统复习资料数字电路与模拟电路解析数字电路与模拟电路是电子信息工程专业中的两个重要学科,也是湖北省考研集成电路设计与集成系统专业的必修科目。

掌握数字电路与模拟电路的相关知识,对于考研的成功至关重要。

本文将对数字电路与模拟电路进行详细解析,为考生提供复习资料和学习指导。

数字电路是以数字信号作信息载体,并处理、传输和存储数字信号的电路系统。

数字电路的基本元件包括逻辑门、触发器、计数器等。

学习数字电路首先要了解数字电路的基本概念和基本原理,如布尔代数、逻辑函数、逻辑门与逻辑电路等。

其次,要学会使用卡诺图进行逻辑函数的最小化,掌握各类逻辑门的真值表和特性。

此外,还要熟练掌握二进制、BCD码和格雷码等数制的表示方法及其互换关系。

另外,数字电路中常用的编码与解码技术、多路选择与复用技术、存储器技术等也是考研数字电路的重点内容。

模拟电路是以模拟信号作信息载体,并处理、传输和存储模拟信号的电路系统。

模拟电路的基本元件包括电阻、电容、电感等被频率相关地进行操作的电路元件。

学习模拟电路首先需要掌握基本的电路元件特性和基本电路理论,如基尔霍夫定律、电压、电流与功率的关系等。

其次,需要了解放大电路的基本知识,包括放大器的分类、放大器的基本参数和放大电路的分析方法。

此外,模拟电路中的滤波器、振荡器、运算放大器等也是考研模拟电路的重要内容。

为了更好地复习数字电路与模拟电路,考生可以参考以下资料:1. 《数字电路与逻辑设计》(作者:眭亚飞):该书详细介绍了数字电路的基本知识与原理,同时提供了大量的习题和实例,帮助考生巩固理论知识和培养解题能力。

2. 《模拟电子技术基础》(作者:刘维民):该书全面介绍了模拟电路的基本概念、元件与电路分析方法,内容通俗易懂,适合考生自学和复习。

3. 《模拟电路分析与设计》(作者:耿国宝、罗勇、刘柏、王红军):该书系统地介绍了模拟电路的基本理论、分析方法和设计技术,并结合实例对各类电路进行了深入讲解,对于考研复习非常有帮助。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

17

数字集成电路

-电路、系统与设计

第3章 器件

18

二极管的结构和手工分析模型

SPICE模型

19

二极管的结电容、扩散电容

20

MOS器件

21

MOSFET 工作区域小结

Strong Inversion VGS > VT

▪ Linear (Resistive) VDS < VDSAT ▪ Saturated (Constant Current) VDS VDSAT

-电路、系统与设计

第1章 引论

3

摩尔定律

电压传输特性

V(y) V OH

VOH = f(VOL) VOL = f(VOH) VM = f(VM)

f V(y)=V(x)

V OL

V OL

VM Switching Threshold

V OH

V(x)

Nominal Voltage Levels

逻辑电平映射至电压范围

数字集成电路

-电路、系统与设计

复习

May. 2012

学习的内容

引论: 数字集成电路中的设计问题 制造工艺(CMOS) 器件(D、MOS) 导线(寄生R、 C 、 L ) CMOS反相器(静态、动态特性) CMOS组合逻辑门的设计 时序逻辑电路设计 设计综合 数字电路中的时序问题

数字集成电路

39

反相器增益

40

影响传输特性的因素

41

直观综述:CMOS电路的特点

噪声容限大 逻辑电平与器件的相对尺寸无关(无比

逻辑) 稳态时,输出具有有限电阻 输入电阻极高 静态功耗小

42

带负载的反相器

延时公式

43

反相器链的应用

44

最优级比(等效扇出)与最优级数

45

CMOS的功耗来源

动态功耗

M odel

Fanout V out CL

32

互连线的电容: 平行板模型 +边缘场电容

33

互连电阻

34

互连模型: RC集总模型

35

Elmore 延时 RC 链

36

导线模型

37

数字集成电路

-电路、系统与设计

第5章 CMOS反相器

38

CMOS 反相器

First-Order DC 分析

瞬态/动态特性

“1 ”

VOH VIH

不确定区

V out V OH

“0 ”

VIL VOL

V OL

斜率 = -1

斜率 = -1

V IL V IH

V in

“再生”特性

扇入与扇出

动态性能(由动态或瞬态响应来决定)

环振

一阶 RC 网络

R

vout

Vdd

E0->1

=

C

LV

2 dd

vin

C

PMOS

isupp ly

A1

NETW OtRpK= ln (2) t = 0.69 RC

▪ absolute dimensions (micron rules)

GND

In

VDD

A

A’

Out (a) L ayout

A

A’

n

p - su b st ra te

F ield

n+

p+

O xide

16

(b) C ross -S ection along A -A ’

封装要求

电气要求: 低参数 机械特性: 可靠性和牢固性 热特性: 散热率越高越好 低成本: 价格低

Classes of parasitics

▪ Capacitive ▪ Resistive ▪ Inductive

31

互连电容

VDD

VDD

M2

V in

C gd12

C db2

C g4

Vout

M4 V out2

Cdb1 Cw

C g3

M1

M3

In te rc o n n e c t

V in S im p lifie d

涂光刻胶

光刻机曝光

一个光刻过程的典型操作步骤(摘自[Fullman99])

工艺步骤

旋转、清洗、干燥

光刻胶显影 酸刻蚀

15

设计规则

设计规则是电路设计者和工艺工程师之间的接口

设计规则是制造各种掩膜的指南

单元尺寸: 最小线宽

▪ scalable design rules: lambda parameter

▪ 电容充放电引起的功耗

短路功耗或交变功耗

▪ 电源和地的直接通路引起的功耗

静态功耗

▪ 主要包括PN结反偏漏电和亚阈值漏电

46

动态功耗

Vin

Vdd

Vout CL

47

短路电流

48

泄漏电流

49

减小功耗的方法

首要选择: 减小电压!

▪ Recent years have seen an acceleration in supply voltage reduction

AN

Vou t NMOS

CL

Important modelN–ETmWOaRtKches delay of inverter

T

T

Vdd

E0 1 = Ptdt = Vdd isup plytdt = Vdd CLdVout = CL • Vdd2

0

0

0

TTBiblioteka VddEca p = Pcaptdt = Voutica ptdt =

CGB B

CGD D

CDB

26

(1) MOS管栅电容(栅沟道电容+栅覆盖电容)

27

(2) MOS管扩散电容

28

寄生电阻

29

数字集成电路

-电路、系统与设计

第4章 导线

30

互连寄生效应的影响

Interconnect parasitics

▪ Increase propagation delay ▪ affect performance and power consumption ▪ reduce reliability

Weak Inversion (Sub-Threshold) VGS VT

▪ Exponential in VGS with linear VDS dependence

22

长沟器件和短沟器件的差别

23

手工分析的标准模型

24

MOS管简单SPICE模型

25

MOS晶体管电容模型

G

CGS S

CSB

能量 and 能量延时

数字集成电路

-电路、系统与设计

第2章 制造工艺

13

现代双阱 CMOS 工艺过程

gate-oxide

TiSi2

Tungsten n+

p-well

p-epi p+

poly

n-well

现代双阱CMOS工艺的截面图

AlCu SiO2

SiO2 p+

14

光刻过程

氧化

光照掩模

去除光刻胶(沙洗)

CLVoutdVout

=

1-- C 2L

•

Vdd2

0

0

0

逻辑门的功耗

瞬时功耗: p(t) = v(t)i(t) = Vsupplyi(t)

峰值功耗: Ppeak = Vsupplyipeak

平均功耗: P av T 1 ett Tp (t)d tV sT uptt p Tisly up td ptl