ChipScope使用说明

chipscope

1、首先按平时一样用chipscope对数据进行采样!不过为了方便以后导入matlab查看,这里我们建议查

看采样信号要使用bus总线方式,这个不多说了,应该都会的。

2、点击file->export 选项,弹出一个export signals窗口,format选择ascii选项,signals to

Export选择bus plot buses,core默认就行。

3、点击export按钮,保存为.prn后缀文件。

如username.prn.

4、打开matlab软件,我们可以直接打开这个.prn文件进行编辑和查看(如果需要),也可以使用matla

b命令

xlLoadChipScopeData(‘username.prn’);

把之前chipscope导出的bus总线数据导入为malab空间变量,并且空间变量的名字和在chipscope 中bus总线对应信号线的名字一样的。

呵呵,信号变量有了,以后就可以方便进行相关信号分析处理了。

ise_chipscope使用实例

ChipScope Pro 使用说明本文档介绍一个在ISE设计中使用ChipScope的例子。

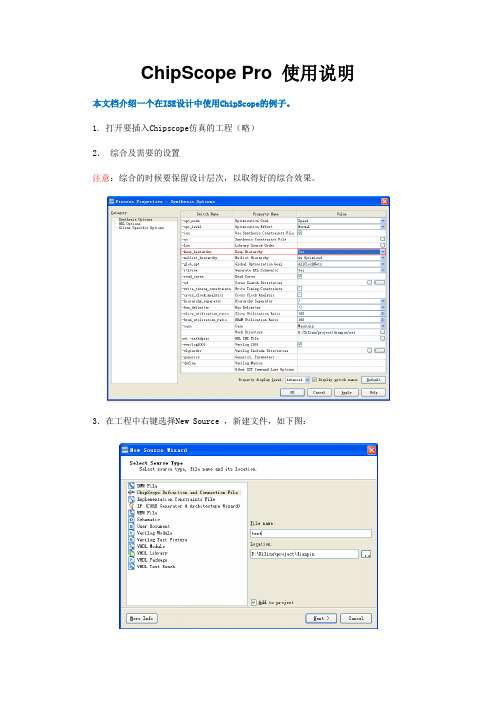

1. 打开要插入Chipscope仿真的工程(略)2.综合及需要的设置注意:综合的时候要保留设计层次,以取得好的综合效果。

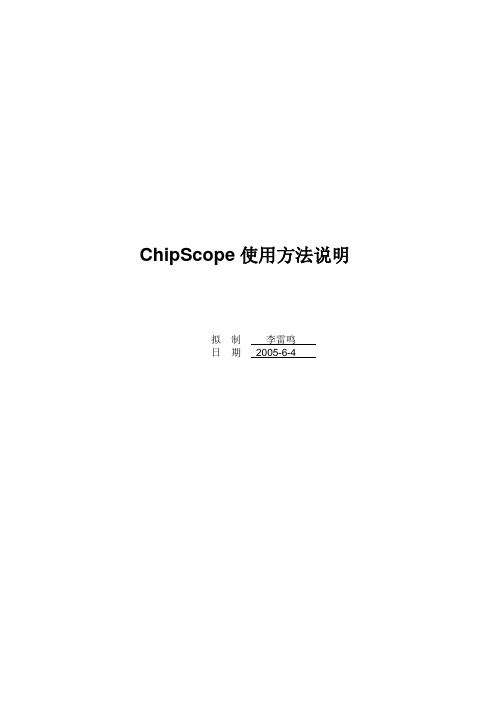

3.在工程中右键选择New Source ,新建文件,如下图:4.双击新建的.cdc文件,启动ChipScope。

1、在DEVICE界面,点击NEXT2、在ICON界面,点击NEXT3、在ILA界面分为3页,如下第一页,在Trigger Width栏填入要触发的数据位宽。

NEXT第二页,Data Depth选择采样深度;Data Same As Trigger为触发条件与采样数据是否相同。

Next第三页,添加时钟触发信号及采样信号。

双击红色CLOCK PORT,选择触发信号关联的时钟信号。

同样双击TRIGGER PORTS关联触发信号(若触发信号TIGGER跟采样信号DATA SIGNALS不同,则分开关联信号)(注,查找信号时,可试用Fitter工具,在Fitter中可以使用通配符*,代表任意个任意字符,帮助快速查找)5.在关联完成所有信号后,点击OK返回。

点击Return to Project Navigator返回ISE。

6.双击Process窗口中的Analyze Design Using Chipscope直到弹出ChipsScpoe工具。

7.选中器件,右键Configure,弹出如下窗口,点击OK。

下载程序后,双击左侧边框打开各窗口。

(注:上方黑色三角表示开始触发采集,黑色方块i代表停止采集,Ti代表无需触发条件满足立即采集。

)系数计算方法:例如,cut_x总线为16位宽,1位符号位、1位整数位、14位小数位,则,试用计算器计算为0.00006103515625。

幅度偏移不需要改,显示精度一般2-4左系数为12右即可。

将所有需要修改格式的总线修改后,双击Bus Plot可打开总线绘图,查看总线波形。

ChipScope使用方法说明

ChipScope使用方法说明拟制李雷鸣日期2005-6-41 ChipScope简介ChipScope的主要功能是能通过JTAG口,在线、实时地读出FPGA内部逻辑的任何信号。

其基本原理是利用FPGA中未使用的Block Ram,将想要观察的信号(寄存器,网线)实时地存到这些BlockRam中,然后根据用户设定的触发条件生成特定的地址译码选择数据读出,送到JTAG口,然后在计算机中根据这些数据动态地画出时序波形来。

使用ChipScope分析FPGA内部信号的优点如下:1. 成本低廉,只要有这套软件加上一根JTAG电缆就可完成信号的分析。

2. 灵活性大,可观测信号的数量和存储深度仅由器件剩余的Block Ram数量决定。

剩余Block Ram越多,可分析的信号的数量和存储深度就越大。

3. 使用方便,该软件可以自动读取原设计生成的网表(*.ngc,*.edf,*.edn)区分时钟信号和普通信号,待观测信号的设定也十分方便,存储深度可变。

可以设计多种触发条件的组合。

然后软件自动将其IP核的网表插入到原设计的网表中。

其IP核只使用少量的查找表资源和寄存器资源,对原设计的影响很小。

4. 使FPGA不再是“黑箱”。

Chip Scope 可以十分方便的观测FPGA内部的所有信号,包括寄存器,网线型,甚至可以观测综合器产生的重命名的连接信号,使FPGA不再是“黑箱”,对FPGA内部逻辑调试非常方便。

2 ChipScope组成ChipScope工具箱包含三个工具:ChipScope Core Generator, ChipScope Core Inserter,和ChipScope Analyzer。

ChipScope Core Generator的作用是根据设定条件生成在线逻辑分析仪的IP核。

使用方法和Xilinx的Core Generator相似。

ChipScope Core Inserter完成读取并分析原设计的网表,设置待分析信号,设定触发条件,和自动生成的该在线逻辑分析仪lP核的网表,并将网表插入到原设计的网表中去。

步骤详细-ISE中使用chipscope

说明:核插入器不仅能产生常用的核,还能将其自动插入设计网表,不需要手工在HDL代码中例化,它在很多场合替代了核生成器的功能。

在ISE中直接调用ChipScope的应用实例。

在XC3S500E芯片上实现一个计数器实例,详细介绍如何在ISE中新建ChipScope应用以及观察、分析数据的操作。

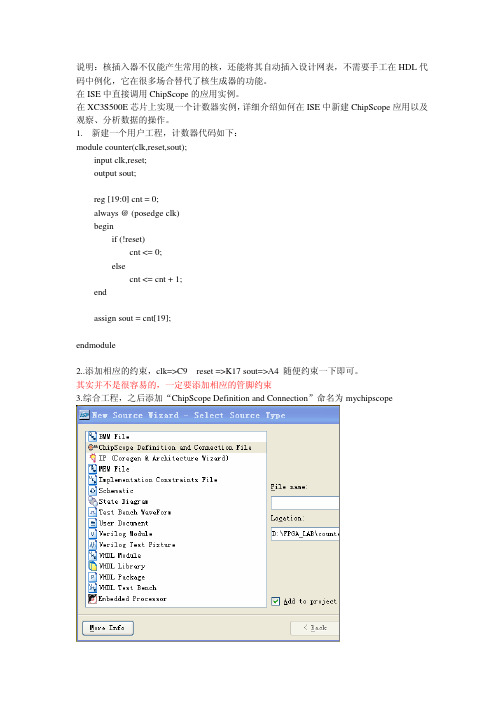

1.新建一个用户工程,计数器代码如下:module counter(clk,reset,sout);input clk,reset;output sout;reg [19:0] cnt = 0;always @ (posedge clk)beginif (!reset)cnt <= 0;elsecnt <= cnt + 1;endassign sout = cnt[19];endmodule2..添加相应的约束,clk=>C9 reset =>K17 sout=>A4 随便约束一下即可。

其实并不是很容易的,一定要添加相应的管脚约束3.综合工程,之后添加“ChipScope Definition and Connection”命名为mychipscope2.在工程区双击mychipscope.cdc文件,即可自动打开ChipScope Pro Inserter软件。

设置参数。

添加触发单元设置触发位宽。

其中触发类型选为Basic,位宽为20bit,设置采样深度为4096。

其中Number of input trigger port---用于设定触发端口数,每个端口ILA核可以支持多路比特数据,最多可有16个端口,具体的比特数取决于用于测试的逻辑资源。

Trigger Width用于设定每个端口的触发比特数。

#Match Units为触发单元的级联数,最多可设置16级,默认选择1级吧。

Sample on Rising Clock Edge--样本在时钟的上升沿进行采样。

选中Data Same As Trigger选项,则数据与触发信号相同,这是一种很常用的模式,可以捕获和采集触发逻辑分析仪的任何数据。

Chipscope实例教程

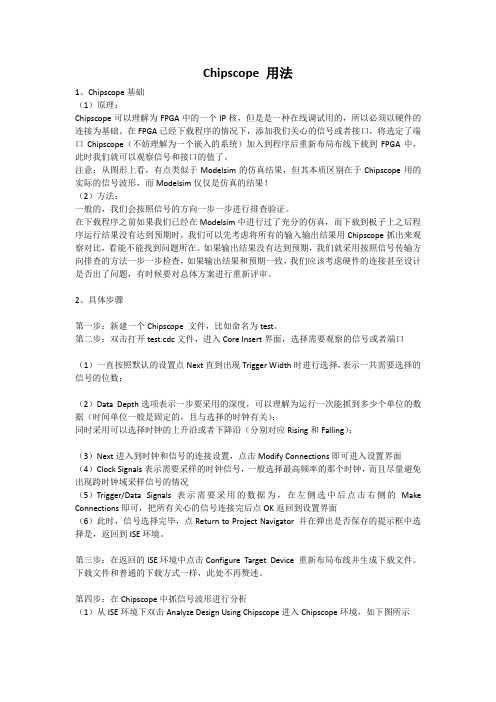

Chipscope 用法1、Chipscope基础(1)原理:Chipscope可以理解为FPGA中的一个IP核,但是是一种在线调试用的,所以必须以硬件的连接为基础。

在FPGA已经下载程序的情况下,添加我们关心的信号或者接口,将选定了端口Chipscope(不妨理解为一个嵌入的系统)加入到程序后重新布局布线下载到FPGA中,此时我们就可以观察信号和接口的值了。

注意:从图形上看,有点类似于Modelsim的仿真结果,但其本质区别在于Chipscope用的实际的信号波形,而Modelsim仅仅是仿真的结果!(2)方法:一般的,我们会按照信号的方向一步一步进行排查验证。

在下载程序之前如果我们已经在Modelsim中进行过了充分的仿真,而下载到板子上之后程序运行结果没有达到预期时,我们可以先考虑将所有的输入输出结果用Chipscope抓出来观察对比,看能不能找到问题所在。

如果输出结果没有达到预期,我们就采用按照信号传输方向排查的方法一步一步检查,如果输出结果和预期一致,我们应该考虑硬件的连接甚至设计是否出了问题,有时候要对总体方案进行重新评审。

2、具体步骤第一步:新建一个Chipscope 文件,比如命名为test。

第二步:双击打开test.cdc文件,进入Core Insert界面,选择需要观察的信号或者端口(1)一直按照默认的设置点Next直到出现Trigger Width时进行选择,表示一共需要选择的信号的位数;(2)Data Depth选项表示一步要采用的深度,可以理解为运行一次能抓到多少个单位的数据(时间单位一般是固定的,且与选择的时钟有关);同时采用可以选择时钟的上升沿或者下降沿(分别对应Rising和Falling);(3)Next进入到时钟和信号的连接设置,点击Modify Connections即可进入设置界面(4)Clock Signals表示需要采样的时钟信号,一般选择最高频率的那个时钟,而且尽量避免出现跨时钟域采样信号的情况(5)Trigger/Data Signals表示需要采用的数据为,在左侧选中后点击右侧的Make Connections即可,把所有关心的信号连接完后点OK返回到设置界面(6)此时,信号选择完毕,点Return to Project Navigator 并在弹出是否保存的提示框中选择是,返回到ISE环境。

ChipScope Pro详细教程(Xilinx在线逻辑分析仪)

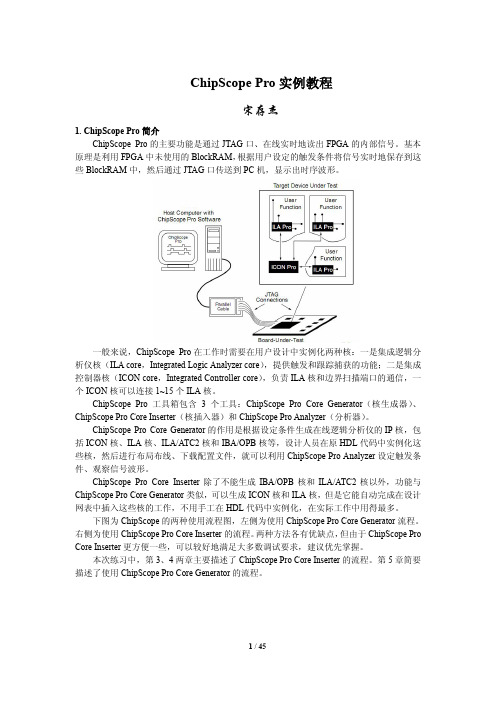

ChipScope Pro实例教程宋存杰1. ChipScope Pro简介ChipScope Pro的主要功能是通过JTAG口、在线实时地读出FPGA的内部信号。

基本原理是利用FPGA中未使用的BlockRAM,根据用户设定的触发条件将信号实时地保存到这些BlockRAM中,然后通过JTAG口传送到PC机,显示出时序波形。

一般来说,ChipScope Pro在工作时需要在用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrated Logic Analyzer core),提供触发和跟踪捕获的功能;二是集成控制器核(ICON core,Integrated Controller core),负责ILA核和边界扫描端口的通信,一个ICON核可以连接1~15个ILA核。

ChipScope Pro工具箱包含3个工具:ChipScope Pro Core Generator(核生成器)、ChipScope Pro Core Inserter(核插入器)和ChipScope Pro Analyzer(分析器)。

ChipScope Pro Core Generator的作用是根据设定条件生成在线逻辑分析仪的IP核,包括ICON核、ILA核、ILA/ATC2核和IBA/OPB核等,设计人员在原HDL代码中实例化这些核,然后进行布局布线、下载配置文件,就可以利用ChipScope Pro Analyzer设定触发条件、观察信号波形。

ChipScope Pro Core Inserter除了不能生成IBA/OPB核和ILA/ATC2核以外,功能与ChipScope Pro Core Generator类似,可以生成ICON核和ILA核,但是它能自动完成在设计网表中插入这些核的工作,不用手工在HDL代码中实例化,在实际工作中用得最多。

下图为ChipScope的两种使用流程图,左侧为使用ChipScope Pro Core Generator流程。

ChipScope的用法

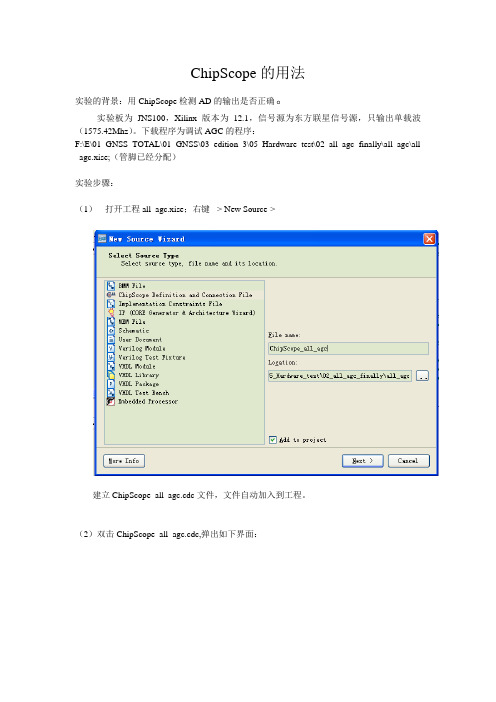

ChipScope的用法实验的背景:用ChipScope检测AD的输出是否正确。

实验板为JNS100,Xilinx版本为12.1,信号源为东方联星信号源,只输出单载波(1575.42Mhz)。

下载程序为调试AGC的程序:F:\E\01_GNSS_TOTAL\01_GNSS\03_edition_3\05_Hardware_test\02_all_agc_finally\all_agc\all _agc.xise;(管脚已经分配)实验步骤:(1)打开工程all_agc.xise;右键-> New Source->建立ChipScope_all_agc.cdc文件,文件自动加入到工程。

(2)双击ChipScope_all_agc.cdc,弹出如下界面:(3)点击Next(4)点击New ILA(Integrated Logic Analyzer Pro cores),进入如下界面:我们在此界面中可以设置;即为所要查看的信号的数目,在此我设置为4,分别用来查看:半秒计数闪灯变量j;红灯闪烁时的电平r_light;GPS的AD输出的8位采样数值:(~(ad_data_gps[7]),ad_data_gps[6:0],注:因为AD输出为偏移二进制码,所以最高位要取反才能转换为二进制补码);GLN的AD输出的8位采样数值。

设置完后界面如下;将产生4个TRIG;再分别设置每个变量的位数(j为25位;r_light为1位,GPS,GLN 的AD输出分别为8位):如下图:(5)点击NEXT:(6)继续点击NEXT,进入信号分配界面:(7)点击,为每个变量建立与实际信号直接的链接关系,如下图:A:首先建立时钟的链接:左键点击NetName中的DSP_AECLKIN_OBUF,然后点击右下角的,即建立起了实际信号与clock之间的连接关系。

B:点击右上角的按钮,进入所需查看的信号的链接。

有图可见:TP0为信号j对应的列表,TP1为信号r_light对应的列表,TP2为信号GPS的AD输出的8位采样数值对应的列表,TP3为信号GLN的AD输出的8位采样数值对应的列表,如下图:(9)分别建立各个信号间的链接关系,最后结果如下所示:(10)分配完之后点击OK返回可以看到,Net Connections中的信号已经有原来的红色变为了黑色,这说明说有的网络都已经建立起了链接关系。

ChipScope使用说明

ChipScope使用说明目录1.建立工程...................................................................................................... 错误!未定义书签。

2.插入及配置核 (3)2.1运行Synthesize (3)2.2新建cdc文件 (3)2.3 ILA核的配置 (4)3. Implement and generate programming file (7)4.利用Analyzer观察信号波形...................................................................... 错误!未定义书签。

4.1连接器件........................................................................................... 错误!未定义书签。

4.2下载配置fpga (9)4.3载入信号端口名 (10)4.4设置触发信号 (10)4.5运行并观察信号波形 (11)补充 (12)1.建立工程ChipScope是配合Xilinx Ise使用的片内逻辑分析工具,使用的第一步是建立ise工程文件,详细步骤可参考ise使用说明。

如果已有建好的ise工程,可跳过此步骤,打开已有工程即可。

建立工程时注意正确添加.v源文件和.ucf管脚配置文件。

2.插入及配置核这里介绍的是ICON核和ILA核的使用方法。

ILA核提供触发和跟踪功能,根据用户设置的触发条件捕获数据;然后在ICON的控制下,通过边界扫描口将数据上传到PC;最后在Analyzer中显示出信号波形。

2.1运行Ise的Synthesize单击选中sources栏中的顶层源文件,右键点击processs栏中的Synthesize,点击Run,进行代码综合。

chipscope10.1使用简要说明

chipscope10.1 使用简要说明一、新建chipscope source。

1、选择工程的Top Module,按右键,选择New Source。

2、在弹出来的对话框里选择Chipscope Definition andConnection File,并填上文件名,按Next。

3、选择要调试的Top Module,按Next.4、确认完成。

二、设置chipscope source。

1、双击添加完成的chipscope source.2、确认Device Option,按Next。

3、确认Integrated Controller Options,按Next。

式Match Type,按Next。

看Core Utilization框,看所需资源是否超出芯片资源,如果是,则要减少采样数或查看信号的数量。

设置完后,按Next。

6、双击Clock Port。

7、设置采样时钟,选中采样时钟的信号名后,按MakeConnections。

小技巧:在Pattern框输入要查找的信号名,可用“*”号代替不确定的字符。

按Filter过滤,在过滤后的信号中选择要查看的信号。

8、选择要查看的信号。

每个通道都必须选上,否则编译的时候会出错。

按OK确定后,按Return to Project Navigator返回工程。

9、编译成功后下载到目标板。

三、查看信号时序1、将USB电缆连接到目标板,打开Analyzer程序。

2、点击初始化链图标,找到JTAG链后会显示以下对话框,按OK确定。

3、点击File —> Import在弹出的对话框理按SelectNew File选择chipscope文件,按OK确定。

4、点击按钮即可查看信号当前的时序。

5、在Trigger Setup框标题栏点击标志最大化,然后点击展开,即可修改信号的触发条件。

“x”为一直触发,“0”为低电平触发,“1”为高电平触发。

设置完成后按返回。

6、设置完触发条件后按,则会等到设置的信号都达到触发条件后才会显示信号的时序图。

Chipscope教程

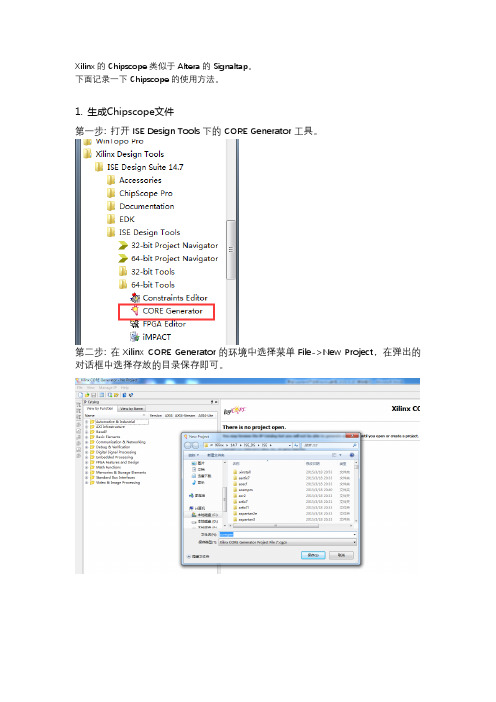

Xilinx的Chipscope类似于Altera的Signaltap。

下面记录一下Chipscope的使用方法。

1. 生成Chipscope文件第一步: 打开ISE Design Tools下的CORE Generator工具。

第二步: 在Xilinx CORE Generator的环境中选择菜单File->New Project,在弹出的对话框中选择存放的目录保存即可。

设置如下。

些,呵呵!选完后Apply一下OK关闭。

第五步: 双击IP Catalog窗口的Debug&Verification下的ICON(chipscope Pro –integrated Controller) 。

第六步: 在弹出的窗口中点击Generate就可以了。

第七步: ICON生成完成后,再双击IP Catalog窗口的Debug&Verification下的ILA(Chipscope Pro –Integrate Logic Analyzer)。

第八步: 在ILA的配置可以根据自己的需要来选择,我们这里不强求,我们这里选择一个触发Group,选择数据的采样深度为2048,就是一次采样2048个点,这个深度当然越大越好,但FPGA资源有限啊!设置完后点击Next。

也会用到Chipscope, 这样程序中基本上的信号都能观察了。

设置完后再Generate。

第十步: 这样我们所需的Chipscope文件都已经生成好了,我们可以在eeprom_test 的目录下看到生成的文件,特别要注意下图中我用红色圈出来的文件,如果在其它的工程中我们需要使用Chipscope的话,只要把这四个文件拷过去就好了,不要费老大力气的再重新生成一边。

接下来是Analyzer:点击Open cable按钮建立JTAG连接。

如果开发板和JTAG连接正常的话,Chipscope能找到开发板使用的FPGA芯片。

点击OK把Data Port里的CH0 ~CH7组合成一个组,方法是按Ctrl键,再选择Data port 里的CH0~CH7, 点击右键,选择Move to Bus->New Bus。

搭建Xilinx开发环境使用ChipScope进行调试

搭建Xilinx开发环境使用ChipScope进行调试Xilinx的ChipScope工具就相当于Altera的SignalTap II,能够捕捉FPGA内部的信号,方便了调试过程。

下面就以一个简单的实例描述一下使用ChipScope的过程(ISE版本为11.1)。

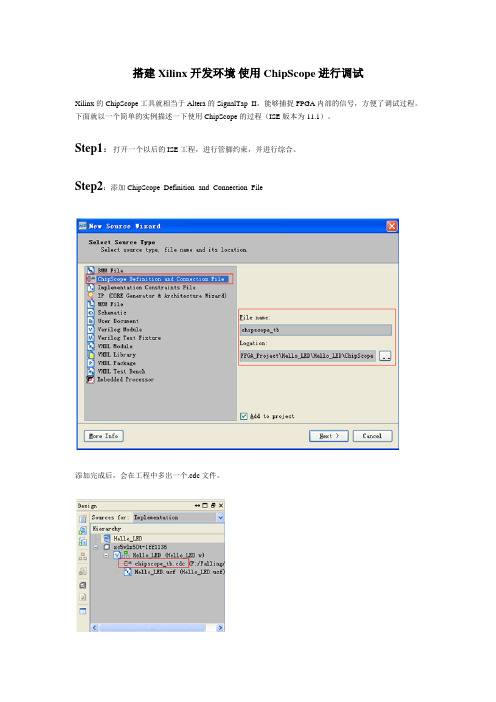

Step1:打开一个以后的ISE工程,进行管脚约束,并进行综合。

Step2:添加ChipScope Definition and Connection File添加完成后,会在工程中多出一个.cdc文件。

Step3:双击*.cdc文件,弹出ChipScope Pro Core Inserter对话框。

首先是指定输入网表和输出网表的路径,以及所选的器件族。

由于ChipScope Pro Core Inserter是从ISE调用的,所以这些选项都已经设置好了,不用修改,直接点NEXT。

不用修改,继续点击NEXTStep4:进行配置ILA核(Integrated Logic Analyzer Pro core)界面。

ILA核用来设置触发条件和捕获数据,并提供将ChipScope核信号和设计中的网表信号连接的功能。

首先是Trigger Parameters界面。

(1)、Number of Input Trigger Ports:用来设置需要观察的信号的数目,例如这里我们需要观察两个信号,所以这里设置为2。

一个ILA最多可以观察16个信号。

(2)、Trigger Width:设置每个要观察信号的位宽。

第一信号是一个计数器30bit计数器,所以第一个设置为30,第二个信号是一个8bit信号,所以这里设置为8(3)、Match Type:设置每一观测信号的触发条件。

ChipScope可以对每一个要观察的信号设置触发条件,最后再采集数据时采用哪个触发条件可以再指定,在这里需要对每一个信号都指定一个触发条件。

主要设置这三个选型,其他保持默认,设置完成后点击NEXT现在进入Capture Parameter界面。

xilinx的Chipscope的使用方法

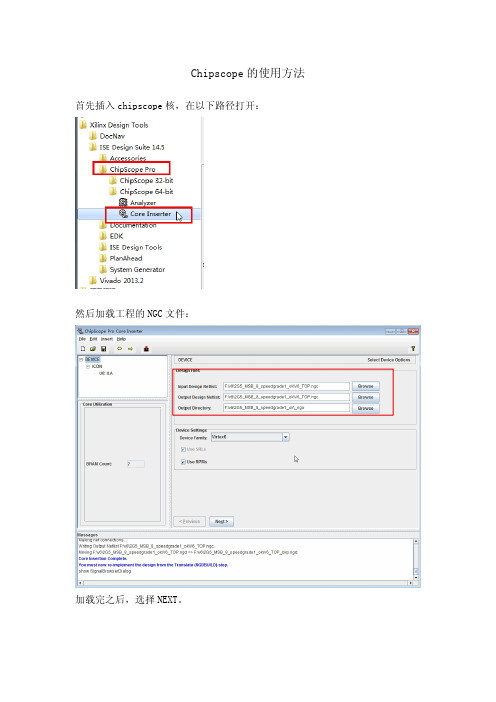

Chipscope的使用方法首先插入chipscope核,在以下路径打开:

然后加载工程的NGC文件:

加载完之后,选择NEXT。

继续next。

这里要选择Trigger的宽度,最大是256,我们一般选择256,以后用多少再返回来修改。

剩下的2项的选择,如下:

然后选择modify connections,

首先选择工程的主时钟,

在选择想要抓取的信号,

选择完后,如果所用的CH少于256,则需要返回之前的地方修改一下,

当所有的信号添加完成后,我们选择insert,加入chipscope核到工程中。

此时,ISE会重新跑一遍synthesize(综合),当执行完后,会产生下面蓝色的信息。

此时,在ISE中执行implement,点击run。

然后,记得保存chipscope,

会保存为.CDC文件,我这里命名保存的是test.cdc。

然后生成bit文件。

这样chipscope核就添加好了。

然后打开ISE中的analyze design using chipscope。

或者这样打开也行,如图:

然后选择连接V6平台,

然后配置V6平台,

选择bit和cdc文件,

这样点击OK,ISE会重新下载一遍工程,然后点击T!,就可以看到需要的信号数据了。

点击这个地方你可以看到想看到的选项,

BUS Plot选项是可以看到数据的波形的,waveform可以看到数据。

Trigger setup是设置触发条件和执行触发的,listing暂时不知道干嘛用的。

ChipScope9使用方法

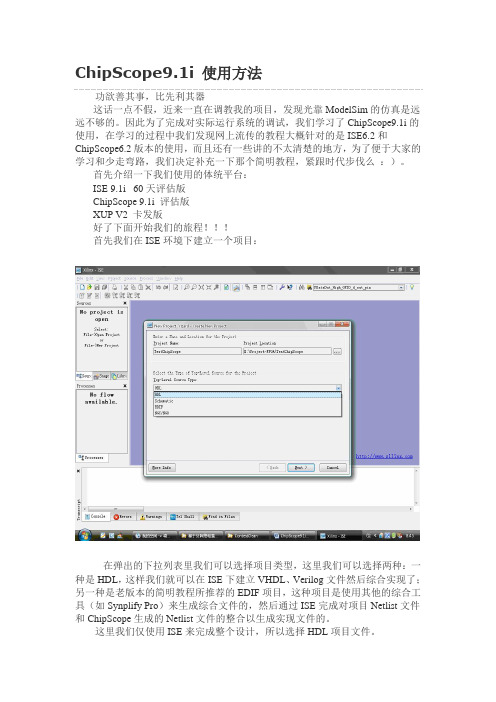

ChipScope9.1i 使用方法功欲善其事,比先利其器这话一点不假,近来一直在调教我的项目,发现光靠ModelSim的仿真是远远不够的。

因此为了完成对实际运行系统的调试,我们学习了ChipScope9.1i的使用,在学习的过程中我们发现网上流传的教程大概针对的是ISE6.2和ChipScope6.2版本的使用,而且还有一些讲的不太清楚的地方,为了便于大家的学习和少走弯路,我们决定补充一下那个简明教程,紧跟时代步伐么:)。

首先介绍一下我们使用的体统平台:ISE 9.1i 60天评估版ChipScope 9.1i评估版XUP V2卡发版好了下面开始我们的旅程!!!首先我们在ISE环境下建立一个项目:在弹出的下拉列表里我们可以选择项目类型,这里我们可以选择两种:一种是HDL,这样我们就可以在ISE下建立VHDL、Verilog文件然后综合实现了;另一种是老版本的简明教程所推荐的EDIF项目,这种项目是使用其他的综合工具(如Synplify Pro)来生成综合文件的,然后通过ISE完成对项目Netlist文件和ChipScope生成的Netlist文件的整合以生成实现文件的。

这里我们仅使用ISE来完成整个设计,所以选择HDL项目文件。

接下来添加一些VHDL源代码, 这个网站不错里面有些很好的VHDL源代码,我们借用其中的gray_counter.vhd来生成项目。

添加一个Top文件来集成这个模块和将要加入的逻辑分析仪模块。

接下来就要用ChipScope来生成逻辑分析仪的核,首先打开Xilinx ChipScope Pro Core Generator。

如下图,选择第一项先生成一个逻辑分析仪控制器。

之后的窗口是指定输出网表文件、目标平台以及icon的一些参数。

其中最主要的是Number of Control Ports它指定了一个icon可以挂载几个ila而ila就是我们链接在信号上的探测点所以这个控制端口的数量一定要考虑清楚。

EDK中chipscope使用说明

EDK中使用Chipscope进行硬件调试一、实验内容及目的1. ChipScope Pro简介ChipScope Pro的主要功能是通过JTAG口、在线实时地读出FPGA的内部信号。

基本原理是利用FPGA中未使用的BlockRAM,根据用户设定的触发条件将信号实时地保存到这些BlockRAM中,然后通过JTAG口传送到PC机,显示出时序波形。

图1为ChipScope Pro工作原理示意图图1 chipscope pro工作原理示意图一般来说,ChipScope Pro在工作时需要在用户设计中实例化两种核:一是集成逻辑分析仪核(ILA core,Integrated Logic Analyzer core),提供触发和跟踪捕获的功能;二是集成控制器核(ICON core,Integrated Controller core),负责ILA核和边界扫描端口的通信,一个ICON核可以连接1~15个ILA核。

2、实验环境简介本实验的开发环境是在Xilinx公司研发的EDK开发环境,版本是14.2.所用到的开发板是diligent公司生产的型号为ATLYS开发板。

3、实验目的及内容本实验的主要目的是学会在EDK开发环境下使用chipscope pro进行硬件调试。

本实验是在H:\atlys_ziliao\microblaze\led目录下原有点灯的工程上进行的。

新建立一个文件夹H:\atlys_ziliao\microblaze\led_chipscope将H:\atlys_ziliao\microblaze\led 目录下的工程文件拷入到该文件夹下。

本实验的内容是使用chipscope获取GPIO的输出引脚的信号。

硬件连接图如图所示图2 硬件连接示意图二、实验步骤步骤一:用XPS打开原来的点灯工程。

图3 XPS打开原来的LED工程步骤二:在原来的硬件系统中添加ICON与ILA IP核如图所示图4 在原有的硬件系统中添加ICON与ILA IP核步骤三:配置chipscope_icon_0 IP核的参数。

Xilinx FPGA的Chipscope工具使用方法

Xilinx FPGA的Chipscope工具使用方法1 ChipScope简介ChipScope是Xilinx FPGA自带的实时调试和验证系统,它将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到设计当中,使我们可以查看任何内部信号或节点,包括嵌入式硬或软处理器。

以操作系统速度或接近操作系统的速度采集信号,并通过设计接口传输出来,避免了使用管脚。

采集到的信号可以通过ChipScope逻辑分析器进行分析。

ChipScope主要有以下关键特性:¾分析任何内部FPGA信号,包括嵌入式处理器总线¾在设计采集时,或综合之后插入小型的、可配置的软件核¾将管脚影响降至最低¾在板上以达到或接近操作系统的速度验证DUT功能¾利用FPGA的可重编程性能,可以在几分钟或几小时内确定设计问题并进行修改,而无需传统ASIC设计中所需的几周或数月时间¾内置的软件逻辑分析器可以用来识别设计问题并进行调试,包括高级触发、滤波器和显示选项¾利用远程调试(从办公室到实验室,或在全球范围内)通过互联网联接进行调试¾逻辑分析器使用的Agilent技术的最优链接,以实现最强大的验证,包括从FPGA 内部到板上任何地方的交叉互联信号。

本文档主要讲解如何使用ChipScope的Core Inserter和Analyzer工具替代逻辑分析仪对DUT逻辑功能进行分析。

2 ChipScope组成ChipScope由三部分构成:The ChipScope Pro Core Generator、The ChipScope Pro Core Inserter和The ChipScope Pro Analyzer。

The ChipScope Pro Core Generator与Xilinx的Core Generator功能相似,用该工具可以产生ICON、ILA、ILA/ATC、IBA/OPB、IBA/PLB、VIO、ATC2等ChipScope Core,通过在DUT中例化这些软核,就把相应的逻辑分析仪功能加入了设计,从而可以观察和调试FPGA内部信号。

Chipscope 简明教程

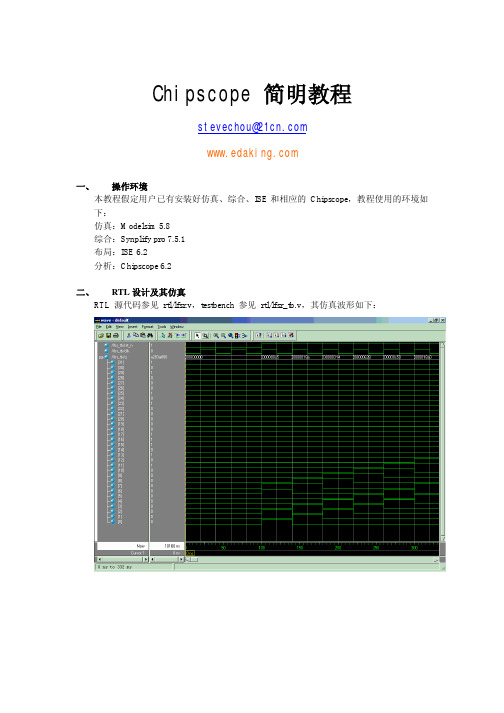

Chipscope 简明教程stevechou@一、操作环境本教程假定用户已有安装好仿真、综合、ISE和相应的Chipscope,教程使用的环境如下:仿真:Modelsim 5.8综合:Synplify pro 7.5.1布局:ISE 6.2分析:Chipscope 6.2二、RTL设计及其仿真RTL 源代码参见rtl/lfsr.v,testbench 参见rtl/lfsr_tb.v,其仿真波形如下:三、逻辑分析仪产生逻辑分析仪的产生有两种方法:Core Generator(核产生器)和Core Inserter(核插入器),Core Inserter 的流程为:1)的RTL 综合成Netlist;2)调用Core Inserter 插入逻辑分析仪;3)布置和布局;4)产生bit 文件下载验证。

而Core Generator 的流程为:1)调用Core Generator 产生逻辑分析仪的Netlist;2)修改用户的RTL,插入逻辑分析代码;3)布置和布局;4)产生bit 文件下载验证。

因为使用Core Inserter 需要在网表中搜索信号,相对修改RTL 来说比较麻烦,并且每次修改RTL 后需要重新插入逻辑分析仪,故本教程以Core Generator 流程为例,这样每次修改RTL 后,只需要重新综合、布置和布局即可。

1)从“开始”-->“程序”-->“ChipScope Pro 6.2”--> “ChipScope Pro Core Generator”2)选择ICON,即集成控制器产生3)选择输出目录和设备家族4)选择语言和综合工具5)点击“Generate Core”产生集成控制器6)点击“Start Over”,回到主菜单,选择“ILA”,即产生集成逻辑分析仪7)选择输出目录、设备家族和采样时钟边缘8)在Trigger Width 框填入触发宽度329)选择“Data Same AsTrigger”,即数据端口和触发端口相同;从Data Depth下拉框选择采样深度,“Number of Block RAMs”处将同时显示需要的Block RAM 块数,对于Sparten II 200 来说,共有14 块Block RAM,注意不要超过限制10)选择语言和综合工具11)点击“Generate Core”产生集成逻辑分析仪Chipscope 将在相应目录产生以下主要文件:icon.edn 集成控制器的网表icon.ncf 集成控制器的网表约束文件icon_synplicity_example.v 集成控制器的嵌入例子代码ila.edn 集成逻辑分析仪的网表ila.ncf 集成逻辑分析仪的网表约束文件ila_synplicity_example.v 集成逻辑分析仪的嵌入例子代码用户需要依照例子代码修改RTL 代码,以下示出最后的结果,请特别注意红色部分://-----------------------------------------------------------------//// ICON core wire declarations////-----------------------------------------------------------------wire [35:0] control0;//-----------------------------------------------------------------//// ICON core instance////-----------------------------------------------------------------icon i_icon(.control0(control0));//-----------------------------------------------------------------//// ILA Core wire declarations////-----------------------------------------------------------------wire [31:0] trig0;//-----------------------------------------------------------------//// ILA core instance////-----------------------------------------------------------------ila i_ila(.control(control0), //控制器接口.clk(clk), //采集的时钟.trig0(trig0));assign trig0 = q; //需要采集的信号列表四、综合代码将文件icon_synplicity_example.v、ila_synplicity_example.v和lfsr.v添加到工程中综合:五、 布置、布局和下载电路将icon.edn 、icon.ncf 、ila.edn 和ila.ncf 拷贝到综合器生成 edf 的目录。

chipscope使用方法

chipscope的学习与使用(1) chipscope有三个主要的功能:1、ChipScope Core Inserter配置ICON核配置ILA核触发参数、捕获参数、网线连接2、ChipScope Pro Analyzer初始化边界扫描链,选择芯片型号配置芯片(JTAG CLOCK)设置触发条件观察信号波形3、ChipScope Pro Generator生成ICON核生成ILA核通过功能1生成了一个CDC文件,在这个CDC文件中需要配置一下触发参数的个数、深度以及连接。

最后工程需要重新run一下。

功能1通过后,可以双击Analyze Design Using ChipScope来启动分析仪,通过分析仪可以查看CDC 文件中配置的连线的波形。

功能3是一个集成功能,它把功能1和功能2集成为一个功能。

功能3需要打开ChipScope Pro Generator软件,在这个软件中新建一个工程,配置芯片型号以及合适的语言(V erilog HDL),配置ICON核和ILA核。

之后在工程中加入这两个文件:xxx_icon.xco和xxx_ila.xco文件在工程.v文件中加入ICON核和ILA核的调用,这时不需要把cdc文件,而且CDC文件需要从工程中移除。

下面是一个小的例子(调用ICON核和ILA核):wire [w_icon-1 : 0] con;wire [w_trig-1 : 0] p_data;xxx_icon u_icon(.CONTROL0(con));xxx_ila u_ila(.CLK(clk),.CONTROL(con),.TRIG0(p_data));最后再打开分析仪就可以来查看波形了,如果需要有时候可以再次加载CDC 文件。

以下是具体的操作说明:ChipScope Pro Generator打开方式:(见图《软件打开》)开始->程序->Xilinx ISE Suite 12.4->ISE Design Tools->CORE Generator打开这个软件后,新建一个工程。

学习使用chipscope逻辑分析仪v1.1

学习使用chipscope逻辑分析仪v1.1学习使用chipscope逻辑分析仪帮助FPGA调试*******************文档说明:本文档叙述在ISE10.1工程环境中使用代码例化Chipscope相关核调试核来帮助FPGA 板上调试。

1. 认识ChipscopeChipScope的基本原理是利用FPGA内部的逻辑和BlockRAM,根据用户设定的触发条件将信号实时地保存到BlockRAM中,然后根据用户设定的触发条件将信号实时地保存到BlockRAM中,通过JTAG 口传回到计算机显示波形。

Chipscope安装好之后,有下面几个工具:在ISE中使用Chipscope有两种方法,如下图所示:方法1:使用Core Generator生成自己需要的Chipscope调试核,并在自己的工程中手工代码中例化和连接,然后综合实现。

方法2:使用Core Inserter工具,向自己已经综合的工程的网表中添加Chipscope核并由图形界面帮助连接,然后综合实现。

两种方法比较:方法2简单,但功能有限,不够灵活,有很多内部信号不能从网表中找到;方法1手工连线虽然复杂一点,但是功能强大!可以选择自己工程中的任何信号点连接调试,有了这个法宝,在调试FPGA时候便有了纵横驰骋的感觉。

2. 建立一个简单的工程建立一个ISE工程。

并添加文件,编写如下代码。

绑定引脚约束。

library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity main isPort (clk : in STD_LOGIC;cnt : out STD_LOGIC_vector(3 downto 0));end main;architecture Behavioral of main issignal counter:std_logic_vector(31 downto 0):=(others =>'0');beginprocess(clk)beginif(clk'event and clk='1')thencounter<=counter+1;end if;end process;cnt<=counter(25 downto 22);end Behavioral;这部分代码非常简单,对时钟做32位计数,并将中间的4位作为输出。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ChipScope使用说明

目录

1.建立工程...................................................................................................... 错误!未定义书签。

2.插入及配置核 (3)

2.1运行Synthesize (3)

2.2新建cdc文件 (3)

2.3 ILA核的配置 (4)

3. Implement and generate programming file (7)

4.利用Analyzer观察信号波形...................................................................... 错误!未定义书签。

4.1连接器件........................................................................................... 错误!未定义书签。

4.2下载配置fpga (9)

4.3载入信号端口名 (10)

4.4设置触发信号 (10)

4.5运行并观察信号波形 (11)

补充 (12)

1.建立工程

ChipScope是配合Xilinx Ise使用的片内逻辑分析工具,使用的第一步是建立ise工程文件,详细步骤可参考ise使用说明。

如果已有建好的ise工程,可跳过此步骤,打开已有工程即可。

建立工程时注意正确添加.v源文件和.ucf管脚配置文件。

2.插入及配置核

这里介绍的是ICON核和ILA核的使用方法。

ILA核提供触发和跟踪功能,根据用户设置的触发条件捕获数据;然后在ICON的控制下,通过边界扫描口将数据上传到PC;

最后在Analyzer中显示出信号波形。

2.1运行Ise的Synthesize

单击选中sources栏中的顶层源文件,右键点击processs栏中的Synthesize,点击Run,进行代码综合。

2.2新建cdc文件

右键单击sources栏中顶层源文件,点击new source,选择chipscope definition and connection file,设好文件名及文件路径,勾选add to project,然后一直点next

完成建立。

2.3核的配置

双击sources栏中的刚刚建立的cdc文件,启动core inserter。

点击两次next,进入ILA的设置界面,首先是trigger parameters界面。

弹出netlist changed的提示框,点选ok刷新网表。

通过number of input trigger ports可设置要观察波形的组数,通过trigger width可设置每组观察的信号的数

目。

时钟周期数,采集数目越多,观察信号的时间越长。

点击next进入net connections界面。

可以看到net connections端口列表显示红色字体,表示端口没有完全连接;当全部端口都与具体信号连接时,字体变为黑色。

双击clock ports打开select net对话框。

首先连接时钟信号,在右边net selections框中点clock signals,选择时钟的信道CH0,在左下方的信号列表中找到时钟信号,单击选中,然后单击右下方make connections按钮,完成clk信号的连接。

在右边net selections框中点trigger/data signals,用同样的方法连接所有想要观察的信号。

如果之前设置观察多组信号,可点击右下方TP0/TP1切换信号组。

连接完成后点击下方OK退出select net对话框,然后点击return to project navigator退出core inserter,并保存设置。

3.Implement和Generate Programming File

单击选中sources框中顶层源文件,运行processes框中的Implement。

注意,如果Implement过程中报错端口连接不完全,应返回ILA配置检查端口是否全部连接。

右键单击Generate Programming File,点击properties,在startup options中将start-up clock设为JTAG clock,点击ok。

运行Generate Programming File,生成.bit文件。

4.利用Analyzer观察信号波形

运行process框中的analyze design using chipscope,进入chipscope pro analyzer。

4.1连接器件

单击左上角file下面的图标,连接到器件,弹出对话框选ok。

4.2下载配置fpga

右键点击my device1(即fpga芯片),单击configure,弹出对话框,点select new

file,选择之前生成的.bit文件,点击ok,之后程序将把design下载到fpga。

4.3载入信号端口名

单击file->import,点击select new file选中cdc文件,然后点击ok。

此时可以看到端口列表中的端口名称都变成了对应的信号名称。

4.4设置触发信号

双击trigger setup打开触发信号设置框,在value栏中可设置开始信号采集的触发信号值,其中每一位对应一个端口,按照端口顺序排列。

例如图中设置为端口0(cle)为1,并且端口7(clk)为0时开始采集信号。

X表示任意值。

4.5运行并观察波形

单击左上角三角形按钮启动fpga电路,当各端口信号满足设置的触发信号时,程序开始采集信号,并在waveform中显示采集到的信号。

可通过左上角的一系列

控制按钮调节波形显示。

补充:

1、当对源文件进行过修改后需重新运行Synthesize、Implement、Generate programming file,

生成.bit文件,并在chipscope analyzer中通过configure重新加载.bit文件。