用VHDL语言设计一个周期性的11位巴克码11100010010序列发生器

波形发生器(VHDL)

华南理工大学广州学院数字系统设计(VHDL)课程报告题目:波形发生器姓名:学号:序号:学院:班级:指导老师:完成时间: 2014-1-1 __题目:波形发生器一、 功能及原理介绍1、功能介绍此波形发生器,通过选择“00”、“01”、“10”、“11”,这四种模式来选择相应的波形输出,除此之外,它还可以产生一些其它的波形,利用MIF 文件生成器产生波形的MIF 文件,由此产生各种波形。

这个波形发生器可以用作信号发生器,产生一些自己所需要的信号。

2、原理介绍正弦信号发生器的结构由 3 部分组成:数据计数器或地址发生器、数据 ROM 和 D/A 。

性能良好的正弦信 号发生器的设计要求此 3 部分具有高速性能,且数据 ROM 在高速条件下,占用最少的逻辑资源,设计流程最便捷,波 形数据获最方便。

顶层文件any_bo.VHD 在FPGA 中实现,包含2 个部分:ROM 的地址 信号发生器由7 位计数器担任,和正弦数据ROM ,拒此,ROM 由LPM_ROM 模块构成能达到最优设计,LPM_ROM 底层是FPGA 中的EAB 或ESB 等。

地址发生器的时钟CLK 的输入频率 f0 与每周期的波形数据点数(在此选择 128 点)。

2.1.MIF 文件生成器的使用方法mif 文件就是存储器初始化文件,即memory initialization file ,用来配置RAM 或ROM 中的数据。

而产生MIF 文件的在这里有三种方法:(1)利用Quartus 自带的mif 编辑器、(2)利用mif 软件来生成、(3)用C 语言或者matlab 语言等来生成,而我就利用MIF 文件生成器MIF_Maker 2010来产生MIF 文件。

① 双击打开MIF_Maker 2010,如图选择模式00 0110 117位计数器(地址发生器)7位计数器(地址发生器)7位计数器(地址发生器)7位计数器(地址发生器)正弦波数据 存储ROM三角波数据 存储ROM方波数据 存储ROM锯齿波数据 存储ROM正弦波输出 三角波输出 方波输出 锯齿波输出首先我们对所需要的MIF文件对应的波形参数进行设置,如上图,在“查看”,并于此下拉菜单中选择“全局参数设置”,如选择波形参数:数据长度128,输出数据位宽8,数据格式十六进制(有的情况下需要选择符号类型),初始相位0度,按“确定”后,将会出现一波形编辑窗。

(完整word版)数字电路课程设计-1011序列发生器和检测器实现

数字电路课程设计姓名学号选题1011序列发生器和检测器的设计实现题目:1011序列发生器和检测器的设计实现。

要求:1)设计一个1011序列发生器;2)设计一个1011序列检测器, 改变序列检测器的输入可以通过人工拨动开关来选择。

思路:设计1011的序列发生器, 由课件lec27 FSM design & serial bits generator上知识可知实现这一序列可选用计数器和数据选择器构成序列信号发生器, 计数器选用74x163, 它是一个带有低电平负载和清零输入端的同步4位二进制计数器, 逻辑符号如图;数据选择器选用74x151在八个一位输入中选择, 其逻辑图如图所示:选用这两个器件再加上一些组合逻辑器件就可连成如图所示的电路图构成序列信号发生器: /(2)设计一个1011序列检测器, 同理由lec27 FSM design & serial bits generator选用JK触发器设计在选用一些组合逻辑器件即可完成如图所示的电路图(3)整体步骤:状态简化状态编码求驱动方程检查电路自启动仿真(1)具体步骤:(2)确定状态数:S0状态, 初始状态, 当前还没有1输入;S1状态:最后一个输入为1(1…);S2状态:最后二个输入为10(10…) ;S3状态:最后三个输入为101(101…);S4状态:最后四个输入为1011。

原始状态转换图:1/0由原始状态转换图可得其状态转换表为:由上图可知 : 状态S1=S 4由上表可得Q1*, Q2和Z的卡洛图为Q1*故可得: Q1*=XQ2* X 故可得Q2*=Q1X’+XQ2Q1’输出 Z(4)故可得: Z=XQ2Q1求驱动方程:J1=XK1=X’J2=Q1X’K2=XQ1’+Q1X’Z=XQ2Q1可得出思路中电路图:(5)检查电路的自启动: 由上表可知状态00, 01,10,11全部为有效状态, 即其没有无效状态, 故电路肯定能自启动。

基于VHDL的m序列伪随机信号发生器设计 精品

成都电子机械高等专科学校毕业设计论文作者姚世刚学号2009111733系部电子与电气工程系专业电子测量技术与仪器题目基于VHDL的m序列伪随机信号发生器的设计指导教师赵茂林评阅教师完成时间:2012年4 月30日毕业设计(论文)中文摘要题目:基于VHDL的m序列发生器的设计摘要:VHDL/CPLD即复杂可编程逻辑器件作为一种大规模集成电路,可根据用户的需要自行构造逻辑功能,可实现较大规模的电路设计,因此被广泛应用于产品的原型设计和产品生产之中。

几乎所有应用中小规模通用数字集成电路的场合均可应用CPLD器件。

本文介绍了基于CPLD的m序列发生器的设计方法。

关键词:CPLD;MAX+PLUS II;伪随机码;m序列发生器毕业设计(论文)外文摘要Title : M—sequence Generator Based CPLDAbstract: VHDL/CPLD Complex Programmable Logic Device that is, as a large scale integrated circuits can be constructed according to the needs of users on their own logic, enabling large-scale circuit design, it is widely used in product design and prototype production into. Almost all applications of small and medium general-purpose digital integrated circuits may be applied CPLD devices occasions. This article describes the m-sequence generator based on CPLD design method.Key words: CPLD;MAX+PLUS II;Pseudorandom Code;m sequence code Generator目录前言 (6)1课题介绍 (7)1.1为什么研究此课题 (7)1.2伪随机序列的应用与意义 (7)1.3伪随机序列的研究现状 (8)1.4研究内容 (8)2设计中使用芯片及VHDL语言介绍 (9)2.1 CPLD芯片介绍 (9)2.1.1概述 (9)2.1.2 MAX7000特点 (9)2.1.3 EPM7128LC84-7 (11)3 伪随机序列介绍 (12)3.1 伪随机序列理论的发展史 (13)3.2 伪随机序列的构造方法 (13)4 序列信号发生器原理 (14)4.1序列信号发生器的设计 (15)4.1.1反馈移位型序列信号发生器 (15)4.1.2计数型序列码发生器 (18)5 移位寄存器 (20)5.1移位寄存器 (20)5.1.1 寄存器 (20)5.1.2移位寄存器 (21)5.2 线性反馈移位寄存器结构 (22)5.2.1 D触发器 (22)5.2.1.1 D触发器工作原理 (22)5.2.1.2 D触发器真值表 (23)5.2.1.3 特征方程 (23)5.2.1.4 状态转移图 (23)5.2.1.5时序图 (24)5.2.1.6 脉冲特性 (24)5.2.2异或门 (25)5.2.2.1 基本原理 (25)5.2.2.2 异或门逻辑符号 (25)5.2.2.3 逻辑表达式 (25)5.2.2.4 真值表 (25)5.3 线性反馈移位寄存器 (26)5.3.1 什么是反馈移位寄存器 (26)5.3.2 线性反馈移位寄存器 (26)5.3.3 性质 (26)6 伪随机信号 (27)6.1 伪随机信号 (27)6.2 m序列码发生器 (30)7 m序列性质 (33)7.1 均衡性 (33)7.2游程特性 (33)7.3 移位相加性 (33)7.4 相关特性 (33)7.5 伪随机特性 (34)8 序列信号发生器的设计和仿真实现 (35)8.1 m序列生成单元的电路设计 (35)8.1.1 系统组成 (35)8.1.2 程序方框图 (36)8.2 m序列发生器 (36)8.3 VHDL语言实现 (37)8.4 仿真数据及结论 (39)结论 (42)致谢 (43)参考文献 (43)前言CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。

VHDL实例(latest)

3 微分电路

提取脉冲前沿

Q1

Q2

仿真结果

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY weifen2 IS PORT( A,clk:IN STD_LOGIC; Qout:OUT STD_LOGIC ); END weifen2;

练习

设计一个可逆BCD码计数器BICOUNTER, 输入为CLK,BIR,输出为Q[3..0]。当BIR=‘1’时, 计数器进行加计数;当BIR=‘0’时,计数器进行减 计数。

VHDL程序如下:

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY BICOUNTER IS PORT( clk,BIR:IN STD_LOGIC; Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END BICOUNTER;

ARCHITECTURE a OF weifen2 IS SIGNAL Q1,Q2:STD_LOGIC; BEGIN PROCESS(clk) BEGIN IF clk'event AND clk='1' THEN Q1<=A; Q2<=Q1; END IF; END PROCESS; Qout<=Q1 and NOT Q2; END a;

VHDL应用实例

1. 序列信号发生器

在数字信号的传输和数字系统的测试中,有时需要用到一组特定的串 行数字信号,产生序列信号的电路称为序列信号发生器。 “01111110”序列发生器 该电路可由计数器与数据选择器构成,其VHDL描述如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

巴克码发生器-EDA

课程设计任务书学生姓名: 王伟专业班级:电子科学与技术1001班指导教师:葛华 _工作单位: 信息工程学院题目: 巴克码发生器初始条件:quartusII软件, EP1C3T144C8芯片要求完成的主要任务:深入研究EDA技术和VHDL硬件描述语言的理论知识,并设计一序列信号发生器程序,利用quartusII强大的图形处理,语言编译功能及仿真功能,实现序列信号发生器的实现。

1.用VHDL语言设计一个有限状态机,用以实现序列信号发生器。

2.用quartusII软件实现VHDL程序的仿真。

3.用EP1C3T144C8芯片实现序列信号发生器设计的硬件测试。

4.撰写《EDA应用实践》课程设计说明书。

时间安排:1、 2012年 12月 17日,课设任务布置。

2、 2012 年 12月18日至2012年12月21日,设计,软件编程,仿真和调试。

3、 2012年 12月22日,机房检查仿真结果,验证设计的可行性和正确性。

4、 2012年12月23日,熟悉实验平台和实验箱。

5、 2012年12月24日至2012年12月26日,设计的硬件调试。

6、 2012年12月27日至2012年12月28日,实验室检查设计成果,现场演示硬件实物,提交设计说明书及答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (I)ABSTRACT (II)1绪论 (1)2 设计思路 (2)2.1状态机简介 (2)2.2 Moore型状态机 (2)2.3 Mealy型状态机 (2)2.4设计方案 (2)3 各个设计模块 (4)3.1分频模块 (4)3.2状态机实现序列发生器 (5)3.2.1序列发生器的实现 (6)3.2.2序列发生器的波形仿真 (8)3.3总体的电路 (10)3.4引脚锁定及硬件实现结果 (10)4 心得体会 (12)参考文献: (13)附录 (14)摘要EDA 技术是近几年迅速发展起来的计算机软件、硬件和微电子交叉的现代电子设计学科,EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言HDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

用VHDL设计多功能信号发生器

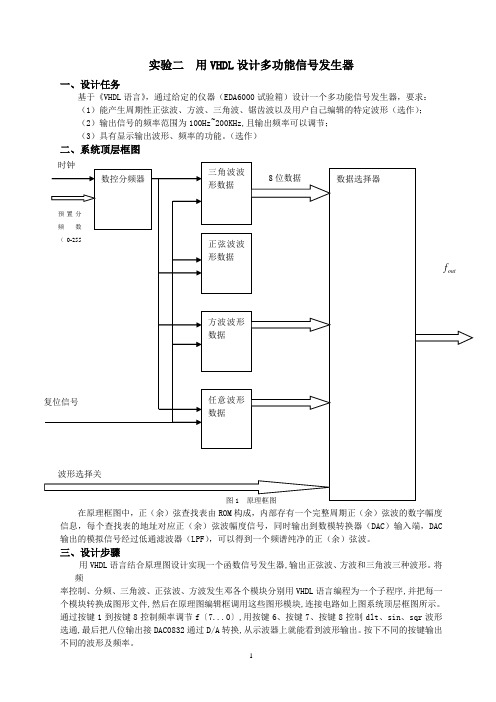

实验二用VHDL设计多功能信号发生器一、设计任务基于《VHDL语言》,通过给定的仪器(EDA6000试验箱)设计一个多功能信号发生器,要求:(1)能产生周期性正弦波、方波、三角波、锯齿波以及用户自己编辑的特定波形(选作);(2)输出信号的频率范围为100Hz~200KHz,且输出频率可以调节;(3)具有显示输出波形、频率的功能。

(选作)在原理框图中,正(余)弦查找表由ROM构成,内部存有一个完整周期正(余)弦波的数字幅度信息,每个查找表的地址对应正(余)弦波幅度信号,同时输出到数模转换器(DAC)输入端,DAC 输出的模拟信号经过低通滤波器(LPF),可以得到一个频谱纯净的正(余)弦波。

三、设计步骤用VHDL语言结合原理图设计实现一个函数信号发生器,输出正弦波、方波和三角波三种波形。

将频率控制、分频、三角波、正弦波、方波发生邓各个模块分别用VHDL语言编程为一个子程序,并把每一个模块转换成图形文件,然后在原理图编辑框调用这些图形模块,连接电路如上图系统顶层框图所示。

通过按键1到按键8控制频率调节f〔7...0〕,用按键6、按键7、按键8控制dlt、sin、sqr波形选通,最后把八位输出接DAC0832通过D/A转换,从示波器上就能看到波形输出。

按下不同的按键输出不同的波形及频率。

四、系统设计(1)数控分频器模块在时钟的作用下,通过预置分频数DIN ,来改变输出频率。

假如分频系数为N ,波形存储模块存储一个周期的波形,实验里按照一个周期波形采样64个点存储在波形存储模块里。

则输出频率N f f clk out .64=(2)数据存储模块 (存储波形数据)数据存储模块主要存的是正弦波、三角波、锯齿波等一个周期的采样点。

三角波模块可设计一个可逆计数器实现,设计时设置一变量作为工作状态标志,在此变量为0时,当检测到时钟的上升沿进行加同一个数操作;为1时,进行减同一个数操作。

DA 转换采用的DA0832,输入有8个数据端,范围是0到255;而且设置64个时钟周期为一个三角波周期,所有每次加、减为8。

VHDL序列检测器设计1110010

VHDL数字系统设计与测试作业序列检测器设计学院:通信工程学院学号:***************设计要求:用状态机设计序列检测器(1110010)。

设计功能:考虑一个序列检测器,检测的序列流为“1110010”,当输入信号依次为“1110010”时输入一个脉冲,否则输入为低电平。

设计思路:序列检测器是一种同步时序电路,它用于搜索,检测输入的二进制代码串中是否出现指定的代码序列,1110010序列检测器的原理图如下:CPX Y 0111010010010首先,本实验要从一串二进制编码中检测出一个已预置的七位二进制码1110010,每增加一位相当于增加一个状态,再加上一个初始态,用八个状态可以实现,其Moore型原始状态转移图如下:根据状态转移图可以得出Moore型原始状态转移表为:源代码:library ieee;use ieee.std_logic_1164.all;entity check isport(din:in std_logic;clk,clr:in std_logic;z:buffer std_logic);end check;architecture arch_check of check istype StateType is(s1,s2,s3,s4,s5,s6,s7,s8);signal present_state,next_state:StateType; beginstate_comb:process(present_state,din)begincase present_state iswhen s1=>z<='0';if din='1'thenelsenext_state<=s1;end if;when s2=>z<='0';if din='1'thennext_state<=s3;elsenext_state<=s2;end if;when s3=>z<='0';if din='1'thennext_state<=s4;elsenext_state<=s1;end if;when s4=>z<='0';if din='1'thennext_state<=s4;elsenext_state<=s5;end if;when s5=>z<='0';if din='1'thennext_state<=s2;elsenext_state<=s6;end if;when s6=>z<='0';if din='1'thenelsenext_state<=s1;end if;when s7=>z<='0';if din='1'thennext_state<=s3;elsenext_state<=s8;end if;when s8=>z<='1';if din='1'thennext_state<=s2;elsenext_state<=s1;end if;end case;end process state_comb;state_clocked:process(clk,clr)beginif(clr='1')thenpresent_state<=s1;elsif(clk'event and clk='1')thenpresent_state<=next_state;end if;end process state_clocked;end arch_check;仿真结果:仿真结果分析:如图所示,当输入1110010序列时,输出Z输出一个高电平,否则输出低电平。

VHDL状态机111000

图像识别算法与系统设计题目:VHDL第一次作业给定任一二值图像,从中串行检测序列111000姓名:刘振宇学号:1502121227学院:电子通信工程学院一、设计功能与要求给定任一图像(不小于256*256),利用MATLAB将其转化成二值图像,并以.tex格式存储。

利用VHDL将文本读取并自主选择状态机进行序列检测,串行检测要求序列(111000)。

二、设计思路首先选取任一图像并利用MATLAB代码将其转换成.BMP格式,再将其转换成二值图像BW,转换之后用fprintf存储为.txt格式的文本形式。

第二部进行状态机的设计,根据要求设计七个状态来完成六位序列的状态循环,根据状态机原理图我选择上课时所讲的mealy_controller状态机,因为当前状态与前一时刻状态还有输入有关。

完成状态机模块的编写后进行子模块的调用和textio的读取,将子模块进行元件例化后用readline和read语句进行读去文本完成循环,最后进行仿真。

三、原理图说明六位状态机要求序列111000用七个状态st1到st7来表示,状态转换过程如下图3-1:图3-1 状态转移图由于当前状态与前一状态还有输入datain有关,所以选用mealy状态机最优。

一旦输入信号发生变化,输出信号即刻发生变化。

输入对输出的影响在当前时钟周期内体现出来,属于同步输出状态机。

满足串行输入时即刻显示状态的要求,能很好的完成题目要求。

状态从st1到st7进行循环,各个状态之间根据输入的不同也有转换关系,只有从st1依次到st7时才能检查到序列111000,其他情况下会重新检索或者自循环。

四、源代码首先要完成任一图片转换成二值图片的要求,MATLAB代码如下:RGB=imread('air.jpg');imwrite(RGB, 'air.bmp', 'bmp');Bw=im2bw(RGB,0.5);imwrite(Bw, 'air_two.bmp', 'bmp');ID=fopen('my_text.txt','w+');fprintf(ID,'%d',Bw);第二步要完成状态机的构造和各个状态在输入后的输出值变化,具体源代码如下:library IEEE;usestd.textio.all;use IEEE.std_logic_1164.ALL;useIEEE.std_logic_textio.all;entitymealy_controller isport (clk,datain,reset:instd_logic;q:out std_logic_vector(5 downto 0));endmealy_controller;architecturebeh of mealy_controller istype states is (st1,st2,st3,st4,st5,st6,st7);signalstx : states;signal q1:std_logic_vector(5 downto 0);begincomreg:process(clk,reset)beginif reset='1' then stx<=st1;elsifclk'event and clk='1'thencasestx iswhen st1=> if datain='1'then stx<=st2;end if;when st2=> if datain='1'then stx<=st3;else stx<=st1;end if;when st3=> if datain='1'then stx<=st4;else stx<=st1;end if;when st4=> if datain='0'then stx<=st5;else stx<=st4;end if;when st5=> if datain='0'then stx<=st6;else stx<=st2;end if;when st6=> if datain='0'then stx<=st7;else stx<=st2;end if;when st7=> if datain='0'then stx<=st1;else stx<=st2;end if;when others=>stx<=st1;end case;end if;end process comreg;com1:process(stx,datain,clk)variable q2:std_logic_vector(5 downto 0);begincasestx iswhen st1=>if datain='1'then q2:="000001";else q2:="000000";end if;when st2=>if datain='1'then q2:="000011";else q2:="000000";end if;when st3=>if datain='1'then q2:="000111";else q2:="000000";end if;when st4=>if datain='0'then q2:="001110";else q2:="000111";end if;when st5=>if datain='0'then q2:="011100";else q2:="000001";end if;when st6=>if datain='0'then q2:="111000";else q2:="000001";end if;when st7=>if datain='1'then q2:="000001";else q2:="000000";end if;when others=>q2:="000000";end case;ifclk'event and clk='1'then q1<=q2;end if;end process com1;q<=q1;--if q1="111000"then q<=q1;else q<="000000";end if;endbeh;为了随着状态变化完成111000的变化,根据状态机的原理图,新的输入被认为是从右向左输入,并在特定位置(如st4)保持不变。

vhdl eda 序列信号发生器与检测器设计

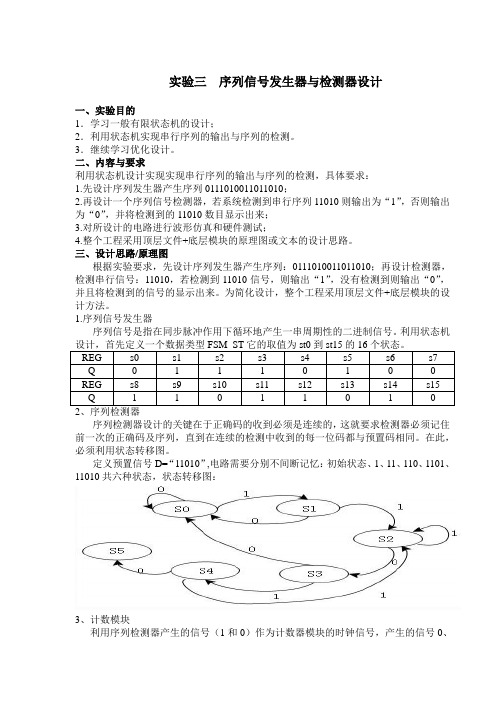

实验三序列信号发生器与检测器设计一、实验目的1.学习一般有限状态机的设计;2.利用状态机实现串行序列的输出与序列的检测。

3.继续学习优化设计。

二、内容与要求利用状态机设计实现实现串行序列的输出与序列的检测,具体要求:1.先设计序列发生器产生序列0111010011011010;2.再设计一个序列信号检测器,若系统检测到串行序列11010则输出为“1”,否则输出为“0”,并将检测到的11010数目显示出来;3.对所设计的电路进行波形仿真和硬件测试;4.整个工程采用顶层文件+底层模块的原理图或文本的设计思路。

三、设计思路/原理图根据实验要求,先设计序列发生器产生序列:0111010011011010;再设计检测器,检测串行信号:11010,若检测到11010信号,则输出“1”,没有检测到则输出“0”,并且将检测到的信号的显示出来。

为简化设计,整个工程采用顶层文件+底层模块的设计方法。

1.序列信号发生器序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号。

利用状态机设计,首先定义一个数据类型FSM_ST它的取值为st0到st15的16个状态。

REG s0 s1 s2 s3 s4 s5 s6 s7 Q 0 1 1 1 0 1 0 0 REG s8 s9 s10 s11 s12 s13 s14 s15 Q 1 1 0 1 1 0 1 0 2、序列检测器序列检测器设计的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及序列,直到在连续的检测中收到的每一位码都与预置码相同。

在此,必须利用状态转移图。

定义预置信号D=“11010”,电路需要分别不间断记忆:初始状态、1、11、110、1101、11010共六种状态,状态转移图:3、计数模块利用序列检测器产生的信号(1和0)作为计数器模块的时钟信号,产生的信号0、1变化,形成类似的CLK信号,实现计数模块计数。

计数模块设计可采用前面的实验二设计。

设计一个产生110001001110序列码的计数器型序列码发生器。

第一章系统概述1.1实验目的及要求1.11 实验目的1.了解并学习EWB软件的使用。

2.了解序列信号发生器的组成及工作原理。

3.熟悉中规模集成电路的运用。

4.掌握序列信号发生器的设计和实验。

5.了解简单数字系统实验调试及故障排除的方法。

1.12 实验要求1.根据设计任务要求,综合运用数字电子技术课程中所学到的理论知识和实践技能独立完成设计课题。

2.根据课题参考书籍,通过独立思考,深入研究课程设计中遇到的问题,培养自己分析,解决问题的能力。

3.进一步熟悉常用电子器件的类型和特性,掌握合理选用的原则。

4.学会电子电路的连线安装和调试技能。

1.2实验设计任务1.21设计任务内容设计一个产生110001001110序列码的计数器型序列码发生器。

第二章 EWB软件的简介2.1 EWB软件的概述随着电子技术和计算机技术的发展,电子产品已与计算机紧密相连,电子产品的智能化日益完善,电路的集成度越来越高,而产品的更新周期却越来越短。

电子工作平台Electronics Workbench (EWB)(现称为MultiSim) 软件是加拿大Interactive Image Technologies公司于八十年代末、九十年代初推出的电子电路仿真的虚拟电子工作台软件,它具有这样一些特点:(1)软件仪器的控制面板外形和操作方式都与实物相似,可以实时显示测量结果。

(2)EWB软件带有丰富的电路元件库,提供多种电路分析方法。

(3)作为设计工具,它可以同其它流行的电路分析、设计和制板软件交换数据。

(4)EWB还是一个优秀的电子技术训练工具,利用它提供的虚拟仪器可以用比实验室中更灵活的方式进行电路实验,仿真电路的实际运行情况,熟悉常用电子仪器测量方法。

2.2 EWB软件的操作界面1.EWB的主窗口2.元件库栏3.信号源库4.基本器件库5.指示器件库第三章 序列信号发生器的原理及设计3.1序列信号发生器原理序列信号是指在同步脉冲作用下循环地产生一串周期性的二进制信号. 序列信号发生器是能够循环产生一组或多组序列信号的时序电路,它可以用以为寄存器或计数器构成。

用VHDL语言设计一个周期性的11位巴克码11100010010序列发生器

班级:09通信(2)班姓名:闫建康学号:090110045 题目:用VHDL语言设计一个周期性的11位巴克码11100010010序列发生器,并用时序仿真验证其功能。

1.设计思路移位寄存器具有并行数据串行输出的功能,所以可以利用移位寄存器将此11位巴克码右移输出,因为巴克码是非周期性的,所以要利用时钟将其周期性的输出。

当时钟有效并且并行数据预置使能型号有效时将巴克码预置到并行数据预置端口,然后使并行数据预置使能型号无效,在时钟有效时依次右移输出巴克码11100010010。

然后再当时钟有效并且并行数据预置使能型号有效时将巴克码预置到并行数据预置端口,在时钟有效时依次右移输出巴克码。

这样就实现了巴克码的周期性输出。

2. VHDL程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY BAKEMA ISPORT ( CLK,LOAD: IN STD_LOGIC;DIN: IN STD_LOGIC_VECTOR(10 DOWNTO 0);QB: OUT STD_LOGIC );END BAKEMA;ARCHITECTURE behav OF BAKEMA ISBEGINPROCESS (CLK,LOAD)V ARIABLE REG11 : STD_LOGIC_VECTOR(10 DOWNTO 0);BEGINIF CLK'EVENT AND CLK='1' THENIF LOAD='1' THEN REG11:=DIN;ELSE REG11 (9 DOWNTO 0) := REG11(10 DOWNTO 1);END IF;END IF;QB<=REG11(0);END PROCESS;END behav;3.仿真波形4. 程序分析该程序描述的是一个带有同步并行预置功能的11位右移移位寄存器。

CLK是移位时钟信号,DIN是8位并行预置数据端口,LOAD 是并行数据预置使能信号,QB是串行输出端口。

简易函数发生器的vhdl设计

简易函数发生器的vhdl设计一、介绍本文将详细介绍如何设计一个简易函数发生器的 VHDL 代码。

函数发生器可以产生各种形式的波形,包括正弦波、方波、三角波等等。

这个设计将使用 VHDL 语言编写,并且基于 FPGA 开发板进行测试。

二、需求分析在设计一个函数发生器之前,我们需要确定它的具体需求。

以下是我们需要实现的功能:1. 可以选择不同类型的波形。

2. 可以设置波形的频率和幅度。

3. 可以输出产生的波形信号。

三、设计思路为了实现上述功能,我们需要使用 VHDL 语言编写一个模块。

该模块将包括以下部分:1. 波形生成器 - 负责产生不同类型的波形。

2. 频率和幅度控制器 - 负责控制波形的频率和幅度。

3. 输出缓冲区 - 负责将产生的信号输出到外部设备。

四、模块设计下面是每个模块的详细设计。

1. 波形生成器该模块负责产生不同类型的波形。

我们可以使用 Look-Up Table (LUT) 来实现这个功能。

LUT 是一种内存单元,可以存储预先计算好的值,并在需要时输出这些值。

在本例中,我们将使用 LUT 存储预先计算好的波形值。

2. 频率和幅度控制器该模块负责控制波形的频率和幅度。

我们可以使用一个计数器来实现这个功能。

这个计数器会根据输入的频率值进行计数,并且当计数到达一定值时,它会输出一个脉冲信号。

该模块还需要一个输入端口用于设置幅度。

3. 输出缓冲区该模块负责将产生的信号输出到外部设备。

我们可以使用一个输出寄存器来实现这个功能。

该寄存器会在每个时钟周期中更新,并且输出当前波形的值。

五、完整代码下面是完整的 VHDL 代码:```library IEEE;use IEEE.STD_LOGIC_1164.all;use IEEE.NUMERIC_STD.all;entity FunctionGenerator isport (clk : in std_logic;reset : in std_logic;sel : in std_logic_vector(1 downto 0); freq : in std_logic_vector(15 downto 0); amp : in std_logic_vector(7 downto 0); out_sig : out std_logic);end FunctionGenerator;architecture Behavioral of FunctionGenerator is -- Waveform LUTstype waveform_lut_t is array (0 to 1023) of integer range -128 to 127;constant sin_lut : waveform_lut_t := (0, 3, 6, 9, 12, 15, 18, 21,...-21, -18, -15, -12, -9, -6, -3);constant square_lut : waveform_lut_t := (127, 127, 127, 127,...-128,-128,-128,-128);constant triangle_lut : waveform_lut_t := (...);-- Waveform generatorsignal wave_pos : integer range 0 to (1024*100)-1;signal wave_val : integer range -128 to 127;procedure update_waveform isbegincase sel iswhen "00" => wave_val <= sin_lut(wave_pos(9 downto 0));when "01" => wave_val <= square_lut(wave_pos(9 downto 0));when "10" => wave_val <= triangle_lut(wave_pos(9 downto 0));when others => null;end case;end procedure;-- Frequency and amplitude controlsignal count : unsigned(15 downto 0) := (others => '0'); signal pulse : std_logic;signal amplitude : integer range -128 to +127;begin-- Waveform generation processgen_waveform: process(clk)beginif rising_edge(clk) thenif reset = '1' thenwave_pos <= (others => '0');out_sig <= '0';else-- Update waveform position and valuewave_pos <= wave_pos + freq;update_waveform;out_sig <= std_logic(amplitude * wave_val / 128);-- Update frequency counterif count = freq thenpulse <= '1';count <= (others => '0');elsepulse <= '0';count <= count + 1;end if;end if;end if;end process gen_waveform;-- Amplitude control processgen_amplitude: process(clk)beginif rising_edge(clk) thenif reset = '1' thenamplitude <= 0;elseamplitude <= signed(amp);end if;end if;end process gen_amplitude;end Behavioral;```六、测试方法为了测试这个设计,我们可以使用 FPGA 开发板。

vhdl时序电路设计

1、设计一个序列脉冲产生电路(产生“10110”序列)(pulse_signal_generator);

2、设计一个模可变的计数器(10进制以下模可变)(change_counter_10);

3、设计一个分频器(N分频);(frequency_divider)

4、设计一个提醒器(每天早上6点,晚上23点提醒)(以分钟作为电路的脉冲信号,一个有24小时共有24*60=1440分钟,6点为计数到第360分钟,23点为计数到第1380分钟)(calling_2)

5、循环8路彩灯控制电路(显示两种以上花色)(color_light_8)

6、硬币存钱罐(能存储5毛和一块的硬币,并能显示存储总额)

7、电子骰子设计(按键,随机产生产生一个点数);

8、自行车速度测量器;

9、完成一个控制AD574-AD转换器电路工作的电路设计。

1 0 1 0 1 低4位加上尾随4个0有效。

序列信号发生器VHDL设计实验报告

实验三序列信号发生器VHDL设计一、实验目的1、设计一个序列信号发生器,可以在时钟的作用下周期性的产生1110010序列信号2、学习时序电路的设计方法;3、掌握产生周期性信号电路的设计方法;4、掌握同步和异步概念;5、掌握仿真的目的和作用;二、实验环境QuartusII 、PC机、GW-PK2 EDA实验箱三、实验原理给出原理图,说明行为描述方式设计序列信号发生器的原理。

可以产生周期信号的序列信号发生器由计数器和译码器构成。

若想产生1110010序列信号,则需要三位二进制计数器,从000记到110,当时钟是上升沿时,若当前记到110,则将计数清为000,再从头开始,否则计数加1,译码器将每个三位二进制数转换为一位序列信号,计数器和译码器分别由两个进程实现。

四、实验内容及要求利用QuartusII完成序列信号发生器的VHDL设计及仿真测试,给出仿真波形,进行引脚锁定,并在实验箱上进行硬件验证。

五、实验步骤(1)用文本方式输入设计文件并存盘①创建工程,利用“New Preject Wizard”创建此设计工程。

选择菜单“File” “New Preject Wizard”,点击Next,即可弹出工程设置对话框点击此框最上一栏右侧的按钮“…”,设置工程路径,找到文件夹D:\Quartus8\vhdl_code\three,填写工程名和顶层文件名称后,点击Next按钮进行下一步。

②添加设计源程序。

如果已有源程序,可以在此加入到工程中,如果没有点击Next进行下一步。

③选择目标芯片。

首先在“Family”栏选芯片系列,在此选“ACEX1K”系列,选择此系列的具体芯片:EP1K30TC144-3。

④选择仿真器和综合器类型。

点击上图的Next按钮,这时弹出的窗口是选择仿真器和综合器类型的,如果都是选默认的“NONE”,表示都选QuartusII中自带的仿真器和综合器,因此,在此都选默认项“NONE”。

⑤结束设置。

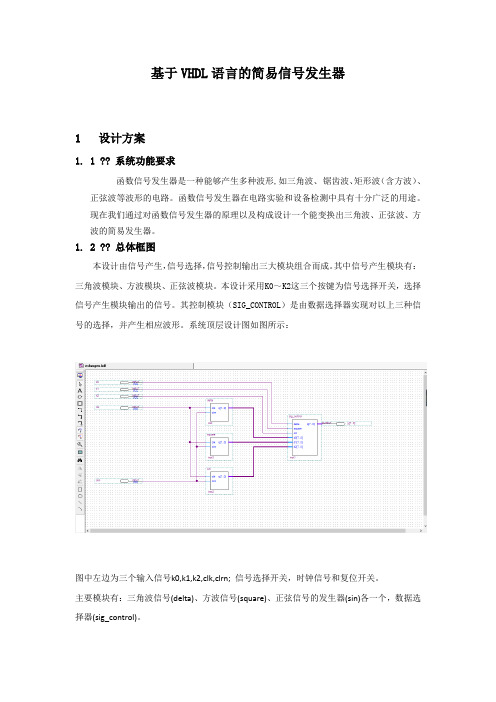

基于VHDL语言的简易信发生器

基于VHDL语言的简易信号发生器1 设计方案1.1 ?? 系统功能要求函数信号发生器是一种能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波等波形的电路。

函数信号发生器在电路实验和设备检测中具有十分广泛的用途。

现在我们通过对函数信号发生器的原理以及构成设计一个能变换出三角波、正弦波、方波的简易发生器。

1. 2 ?? 总体框图本设计由信号产生,信号选择,信号控制输出三大模块组合而成。

其中信号产生模块有:三角波模块、方波模块、正弦波模块。

本设计采用K0~K2这三个按键为信号选择开关,选择信号产生模块输出的信号。

其控制模块(SIG_CONTROL)是由数据选择器实现对以上三种信号的选择,并产生相应波形。

系统顶层设计图如图所示:图中左边为三个输入信号k0,k1,k2,clk,clrn; 信号选择开关,时钟信号和复位开关。

主要模块有:三角波信号(delta)、方波信号(square)、正弦信号的发生器(sin)各一个,数据选择器(sig_control)。

2 ?? 模块功能设计2. 1 三角波模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE delta ISport(clk,clrn:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END delta;ARCHITECTURE a OF delta ISBEGINPROCESS(clk,clrn)VARIABLE tmp:STD_LOGIC_VECTOR(7 DOWNTO 0); VARIABLE f:STD_LOGIC;BEGINIF clrn='0' THEN tmp:="00000000";ELSIF clk'EVENT AND clk='1' THENIF f='0' THENIF tmp="" THEN tmp:=""; f:='1';ELSE tmp:=tmp+1;END IF;ELSEIF tmp ="00000001" THEN tmp:="00000000"; f:='0';ELSE tmp:=tmp-1;END IF;END IF;END IF;q<=tmp;END PROCESS;END a;2. 2 方波模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE square IS PORT(clk,clrn: IN STD_LOGIC;q: OUT STD_LOGIC_VECTOR(7 downto 0)); END square; ARCHITECTURE a OF square ISSIGNAL f: STD_LOGIC;BEGIN PROCESS(clk, clrn)VARIABLE tmp:STD_LOGIC_VECTOR(7 downto 0); BEGIN IF clrn='0' THEN tmp:="00000000";ELSE IF clk'event and clk='1' THENIF tmp="" THEN tmp:="00000000";ELSE tmp:=tmp+1;END IF;IF tmp<"" THEN f<='1';ELSE f<='0';END IF; END IF;END IF;END PROCESS;PROCESS(clk,f)BEGINIF clk'event and clk='1' THENIF f='1' THEN q<="";ELSE q<="00000000";END IF;END IF;END PROCESS;END a;2. 3 正弦波模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USEUSEENTITY sin ISPORT (clk,clrn:IN STD_LOGIC;q:OUT INTEGER RANGE 255 DOWNTO 0);END sin;ARCHITECTURE A OF sin ISBEGINPROCESS(clk,clrn)VARIABLE tmp:INTEGER RANGE 63 DOWNTO 0;BEGINIF clrn='0' THEN q<=0; tmp:=0;ELSEIF clk'EVENT AND clk='1' THENIF tmp=63 THEN tmp:=0;ELSE tmp:=tmp+1;END IF;CASE TMP ISWHEN 00=>q<=255; WHEN 01=>q<=254; WHEN 02=>q<=252;WHEN 03=>q<=249;WHEN 04=>q<=245;WHEN 05=>q<=239;WHEN 06=>q<=233; WHEN 07=>q<=225;WHEN 08=>q<=217; WHEN 09=>q<=207; WHEN 10=>q<=197; WHEN 11=>q<=186;WHEN 12=>q<=174; WHEN 13=>q<=162; WHEN 14=>q<=150; WHEN 15=>q<=137;WHEN 16=>q<=124; WHEN 17=>q<=112; WHEN 18=>q<=99; WHEN 19=>q<=87;WHEN 20=>q<=75; WHEN 21=>q<=64; WHEN 22=>q<=53; WHEN 23=>q<=43;WHEN 24=>q<=34; WHEN 25=>q<=26; WHEN 26=>q<=19; WHEN 27=>q<=13;WHEN 28=>q<=8; WHEN 29=>q<=4;WHEN 30=>q<=1;WHEN 31=>q<=0;WHEN 32=>q<=0; WHEN 33=>q<=1;WHEN 34=>q<=4;WHEN 35=>q<=8;WHEN 36=>q<=13;WHEN 37=>q<=19;WHEN 38=>q<=26;WHEN 39=>q<=34;WHEN 40=>q<=43;WHEN 41=>q<=53; WHEN 42=>q<=64; WHEN 43=>q<=75;WHEN 44=>q<=87;WHEN 45=>q<=99; WHEN 46=>q<=112; WHEN 47=>q<=124; WHEN 48=>q<=137; WHEN 49=>q<=150; WHEN 50=>q<=162;WHEN 51=>q<=174; WHEN 52=>q<=186;WHEN 53=>q<=197;WHEN 54=>q<=207; WHEN 55=>q<=217; WHEN 56=>q<=225;WHEN 57=>q<=233;WHEN 58=>q<=239; WHEN 59=>q<=245;WHEN 60=>q<=249;WHEN 61=>q<=252; WHEN 62=>q<=254;WHEN 63=>q<=255;WHEN OTHERS=>NULL;END CASE;END IF;END IF;END PROCESS;END a;2. 4 数据选择器模块该模块部分VHDL 源程序如下:LIBRARY IEEE;USE sig_control ISPORT(delta,square,sin:IN STD_LOGIC;d0,d1,d2:IN STD_LOGIC_VECTOR(7 DOWNTO 0);q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END sig_control;ARCHITECTURE behave OF sig_control ISSIGNAL sel:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINsel<=delta&square&sin;PROCESS(sel)BEGINCASE sel ISWHEN"100"=>q<=d0;WHEN"010"=>q<=d1;WHEN"001"=>q<=d2;WHEN OTHERS=>NULL;END CASE;END PROCESS;END behave;3仿真波形及分析各部分模块完成后, 用Quartus 对程序编译、仿真、得到的仿真波形,各模块仿真波形及顶层仿真波形如下:3.1三角波模块仿真clk:时钟信号clrn:复位信号低电平清零k0k1k2=100,控制输出三角波。

巴克码发生器完整版

巴克码发生器一、实验目的1.实现一个在通信领域中经常使用的巴克码发生器。

2.掌握用大规模可编程逻辑器件实现时序电路的方法。

二、实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台5.其他器材与材料若干三、实验说明巴克码发生器在数据通信、雷达和遥控领域有相当广泛的应用。

它能自动产生周期性的序列。

本实验要求产生的序列码信号为{1110010},可以用寄存器或同步时序电路实现。

为了能够通过实验开发系统验证试验效果,可以使用两个输出端,其中一个输出端同时输出巴克码,另一个输出端输出节拍。

四、实验步骤1.巴克码的VHDL程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity bakema isport(clk:in std_logic;dout,zhishi:out std_logic); end entity ;architecture behave of bakema issignal count7:integer range 0 to 6; beginprocess(clk)beginzhishi<=not clk;if clk'event and clk='1' thenif count7<6 thencount7<=count7+1;else count7<=0;end if;end if;end process;process(count7)begincase count7 iswhen 0=>dout<='1';when 1=>dout<='1';when 2=>dout<='1';when 3=>dout<='0';when 4=>dout<='0';when 5=>dout<='1';when 6=>dout<='0';when others=>dout<='0';end case;end process;end behave;3.在这里用数码管和一个发光二极管作为指示节拍,另一个发光二极管显示产生的巴克码,随着数码管显示1到7,二极管显示1110010序列。

实验五-10110101序列产生器

●实验名称:利用VerilogHDL设计一个10110101序列发生器

●实验目的:

1.熟悉用可编程器件实现基本时序逻辑电路的方法。

2.了解计数器的Verilog描述方法,以及序列发生器的设计思路与原理。

●预习要求:

1.回顾数字电路中序列发生器的相关知识。

●实验说明:

1.用MAX+plus II软件开发PLD器件有两种设计输入方式:原理图输入和HDL语言

输入方式,或者将两者结合起来,一部分电路采用原理图,另一部分采用HDL语

言。

2.序列信号发生器是指在系统时钟的作用下能够循环产生一组指定序列信号的时序

电路,本实验要求设计一个能够循环产生“10110101”信号的时序电路。

3.请大家回忆前期课程讲过的johnson计数器的实现原理(教材P114),循环产生序

列的设计思路跟johnson计数器是类似的。

●实验内容与步骤:

1.新建一个属于自己的工程目录。

2.用VerilogHDL语言方式编写一个10110101序列发生器。

3.对此序列发生器模块进行编译和仿真。

●实验报告要求:

1.将自己绘制的电路图或者编写的VerilogHDL代码,截图或者复制到实验报告中。

2.将代码关键位置写上相应注释(可用中文)。

3.对仿真波形截图,贴到实验报告中。

●实验图表与数据:

1. 10110101序列发生器的Verilog代码:

2. 10110101序列发生器的仿真波形:。

VHDL程序练习题

V H D L程序练习题(含答案)(总34页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--VHDL程序填空题(一) 在下面横线上填上合适的VHDL关键词,完成2选1多路选择器的设计。

LIBRARY IEEE;USE 1 MUX21 ISPORT(SEL:IN STD_LOGIC;A,B:IN STD_LOGIC;Q: OUT STD_LOGIC );END MUX21;2 BHV OF MUX21 ISBEGINQ<=A WHEN SEL=’1’ ELSE B;END BHV;(二) 在下面横线上填上合适的语句,完成BCD-7段LED显示译码器的设计。

LIBRARY IEEE ;USEENTITY BCD_7SEG ISPORT( BCD_LED : IN STD_LOGIC_VECTOR(3 DOWNTO 0);LEDSEG : OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END BCD_7SEG;ARCHITECTURE BEHAVIOR OF BCD_7SEG ISBEGINPROCESS(BCD_LED)3IF BCD_LED="0000" THEN LEDSEG<="0111111";ELSIF BCD_LED="0001" THEN LEDSEG<="0000110";ELSIF BCD_LED="0010" THEN LEDSEG<= 4 ;ELSIF BCD_LED="0011" THEN LEDSEG<="1001111";ELSIF BCD_LED="0100" THEN LEDSEG<="1100110";ELSIF BCD_LED="0101" THEN LEDSEG<="1101101";ELSIF BCD_LED="0110" THEN LEDSEG<="1111101";ELSIF BCD_LED="0111" THEN LEDSEG<="0000111";ELSIF BCD_LED="1000" THEN LEDSEG<="1111111";ELSIF BCD_LED="1001" THEN LEDSEG<="1101111";ELSE LEDSEG<= 5 ;END IF;END PROCESS;END BEHAVIOR;(三) 在下面横线上填上合适的语句,完成数据选择器的设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

班级:09通信(2)班姓名:闫建康学号:090110045 题目:用VHDL语言设计一个周期性的11位巴克码11100010010序列发生器,并用时序仿真验证其功能。

1.设计思路

移位寄存器具有并行数据串行输出的功能,所以可以利用移位寄存器将此11位巴克码右移输出,因为巴克码是非周期性的,所以要利用时钟将其周期性的输出。

当时钟有效并且并行数据预置使能型号有效时将巴克码预置到并行数据预置端口,然后使并行数据预置使能型号无效,在时钟有效时依次右移输出巴克码11100010010。

然后再当时钟有效并且并行数据预置使能型号有效时将巴克码预置到并行数据预置端口,在时钟有效时依次右移输出巴克码。

这样就实现了巴克码的周期性输出。

2. VHDL程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY BAKEMA IS

PORT ( CLK,LOAD: IN STD_LOGIC;

DIN: IN STD_LOGIC_VECTOR(10 DOWNTO 0);

QB: OUT STD_LOGIC );

END BAKEMA;

ARCHITECTURE behav OF BAKEMA IS

BEGIN

PROCESS (CLK,LOAD)

V ARIABLE REG11 : STD_LOGIC_VECTOR(10 DOWNTO 0);

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF LOAD='1' THEN REG11:=DIN;

ELSE REG11 (9 DOWNTO 0) := REG11(10 DOWNTO 1);

END IF;

END IF;

QB<=REG11(0);

END PROCESS;

END behav;

3.仿真波形

4. 程序分析

该程序描述的是一个带有同步并行预置功能的11位右移移位寄存器。

CLK是移位时钟信号,DIN是8位并行预置数据端口,LOAD 是并行数据预置使能信号,QB是串行输出端口。

此移位寄存器的工作原理如下:

当CLK的上升沿到来时进程被启动,如果这时预置使能LOAD 为高电平,则将输入端口的11位二进制数并行置入移位寄存器中,作为串行右移输出的初始值;如果预置使能LOAD为低电平,则执行语句“REG11 (9 DOWNTO 0) := REG11(10 DOWNTO 1)”,此语句表明:①一个时钟周期后将上一时钟周期移位寄存器中的高10位二进制数REG11赋给此寄存器的低10位REG11;②将上一时钟周期移位寄存器中的最低位,即当前值REG(0)向QB输出。

随着CLK 脉冲的到来,就完成了将并行预置输入的数据逐位向右串行输出的功能,即寄存器中的最低位首先输出。