《集成电路CAD》课程设计报告.doc

南邮集成电路与CAD实验报告4_张长春

《集成电路与CAD》课程实验第 4 次实验报告实验名称:数字集成电路设计实验目的:1,掌握模拟集成电路的基本设计流程2,掌握CADEDNCE基本使用3,学习物理层版图的设计基础实验原理:1,布图规划:在物理实施过程中,从数据输入到时钟树综合之前,大体可以分为:布图规划、电源规划和布局。

布局又称为标准单元放置,包括对I/O单元的排序放置、模块(block)放置和标准单元的规划。

标准单元通常占50%以上芯片面积。

布图规划开始时,要准备好各种基本设计数据和相应的物理库、时序库文件,并输入到布图规划的工具环境中来,为其后的布局和布线做好准备。

2,电源规划电源规划是给整个芯片的供电设计出一个均匀的网络。

电源网络设置、数字与模拟混合供电、单电源与多电源供电电源网络设置。

其中电源环线(power ring)和电源条线(power stripe)的设置为主要工作。

3,布局I/O单元和模块的布放都属于布局的范畴,由于它们已经在布图规划时完成,因此布局的剩余任务主要是对标准单元的布局。

实验内容与结果分析:1,前端设计16位计数器module count(out,clk,rst); //源程序input clk,rst; //指定输入output[3:0] out; //指定输出reg[3:0] out; //out为4位reg型initial out=4'd0; //初始,输出为0always @(posedge clk or negedge rst) //always块beginif(!rst) out=4'd0; //如果rst信号为0输出为0 else //否则开始下面beginout=out+4'd1; //out=out+1if(out==4'd16) out=4'd0; 如果输出为16,归0endendendmodule2,后端设计(1)设计输入:导入前端设计文件(2)布线窗口设定:整体规划版图,如IO口位置,关键路径(3)电源环设定,如下图,设定电源环位置,宽度,长度(3)放置标准单元:将器件放置在版图上(4)多次布线优化(5)时钟树综合,上色最后结果如下:三,实验分析。

集成电路CAD实验报告

集成电路CAD实验报告集成电路CAD实验报告姓名:席悦学号:2120503018 班级:微电子31班一、实验目的:通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence 的Composer,Analog Design Environment,Virtuoso,Assura等各大功能模块逐一了解,使学生掌握模拟集成电路设计的总体流程,为日后的学习、工作打下坚实的基础。

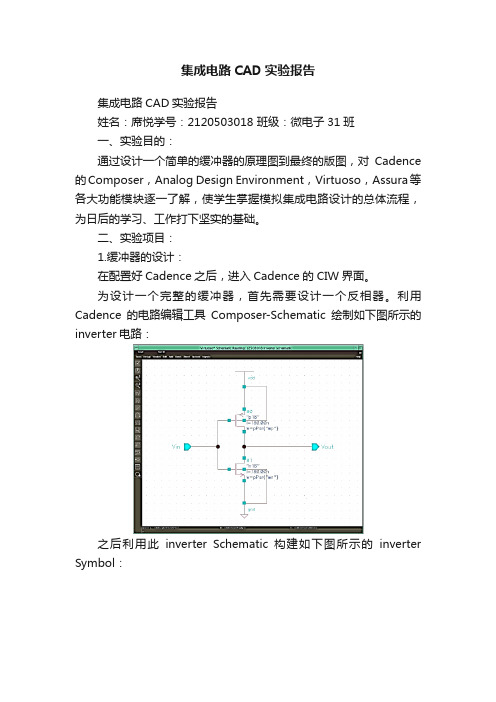

二、实验项目:1.缓冲器的设计:在配置好Cadence之后,进入Cadence的CIW界面。

为设计一个完整的缓冲器,首先需要设计一个反相器。

利用Cadence的电路编辑工具Composer-Schematic绘制如下图所示的inverter电路:之后利用此inverter Schematic 构建如下图所示的inverter Symbol:我们知道,一个Buffer是由两个Inverter组成,利用前边构建Inverter Schematic的方法,画出缓冲器Buffer的电路原理图:其中的反相器直接调用之前做好的Inverter的Symbol。

同样的,利用此缓冲器的原理图生成相应的缓冲器Symbol图:之后构建仿真电路,对所设计的Buffer电路进行电路仿真(ADE)。

仿真电路图如下:在仿真过程中,我们分别采用tt,ss,ff工艺角进行仿真,得到了如下的波形图和仿真数据:①tt工艺角:其相应数据参数为:Marker,/I5/V1,/OUT,/INM0:Y,900mV,900mV,900mV x[0],111.36ps,778.31ps,50ps x[1],5.1063ns,5.9952ns,5.05ns ②ss工艺角:其相应数据参数为:Marker,/I5/V1,/OUT,/INM0:Y,900mV,900mV,900mV x[0],121.55ps,927.99ps,50ps x[1],5.1155ns,6.1676ns,5.05ns ③ff工艺角:其相应数据参数为:Marker,/I5/V1,/OUT,/INM0:Y,900mV,900mV,900mVx[0],103.43ps,653.72ps,50psx[1],5.0984ns,5.8613ns,5.05ns④分析总结:通过对不同工艺角的仿真,可以清晰的看到ss的上升延迟和下降延迟时间最长,而ff的上升延迟和下降延迟最短,而tt工艺角是上升延迟和下降延迟的典型值。

集成电路CAD设计

黑龙江大学电子工程学院实验报告课程名称:集成电路cad设计专业:集成电路设计与集成系统班级:集成一班学号:20083509学生姓名:王迪2010年11月18日实验名称:电阻负载的共源级放大器设计一、实验目的:1.会对Orcad Capture 、Hspice 和Cosmos Scope 三个软件进行基本操作。

2.会用三个软件进行电路图的绘制与仿真。

3.根据仿真结果联系理论分析实验现象。

二、实验所涉及的软件: 1.Orcad Capture [Cadence 公司] 2.Hspice [Synopsys 公司] 3.Cosmos Scope [Synopsys 公司] 三、实验内容和原理:实验内容:绘制电阻负载的共源级放大器电路,分别对电路进行以下操作: ①直流分析.DC ②静态工作点分析.op ③交流分析.ac ④瞬态分析.tran 实验原理:MOS 管处于饱和区:①条件:Vds>Vgs-Vth ②输出电压:V OUT =V DD -R D 212)(Vth Vin LWCox u n - MOS 管处于线性区:①条件:Vds<Vgs-Vth ②输出电压:V OUT =V DD -R D 21])(2[OUT V Vth Vin L WCox u n --V OUT 2 四、操作方法与实验步骤1.建立工程:打开orcad capture 点击file ——new ——project---最后一栏修改存储位置2.添加souse Hspice csms3.画出电路图4.修改环境变量5.要把.NET 文件改成.SP 文件6.用hspice 对电路进行模拟仿真。

仿真前进行Hspice 时注意把D 盘中的h05hvcddtt09v01文件复制到你的保存路径,把网表的存储路径h 前加\7.在Edill 中查找错误,没有错误表示仿真成功。

8.用cosmos 查看生成的图形。

注意事项:1 工程名要用英文2每修改一次电路或是做了改动一定要保存。

南邮集成电路与CAD实验报告1_张长春

1,晶体管级电路图设计

如图为一查分对,驱动一电流镜。

2,Symbol创建以及前仿真

创建一个只有输入输出端口的symbol模块,设定负载和激励,进行直流,交流,瞬态仿真

仿真结果:

选取输入输出节点,vin和vout

增益相位:

至此,完成前端设计。

3,版图

选择晶体管电路图生成的器件版图,进行人工布局布线并进行纠错,使得其与原电路对应。

DRC和LVS相辅相成,有更改要从DRC再次开始验证

DRC和LVS结果

结果匹配

4,后仿真

将寄生电容,电阻等提取成文件,然后反标到电路版图上,再次进行仿真。操作与前仿真一致。

结果:

仿真结果

实验分析:

模拟集成电路比之数字,更加的敏感和难以控制,在设计的过程中,要考虑很多细节问题。例如,线间距,器件间距,各金属层之间的相互影响,所以在设计时候要尤其注意不同金属层的协调使用。而这样又会带来设计复杂度的提升,因此,有逻辑性和系统性的完成版图的布局规划很重要。也要注意美感,不仅是视觉上,同时也是模块化的基本要求,能够使得器件布局紧密而利于外部利用,是极好的。

微电子工艺实验报告

(2016/2017学年第2学期)

课程名称

集成电路与CAD

学院

电子科学与工程学院

指导教师

张长春

专业

微电子科学与工程

姓名

班级学号

《集成电路与CAD》课程实验第1次实验报告

实验名称:差动放大器模拟

实验目的:

1,掌握模拟集成电路的基本设计流程

2,掌握CADEDNCE基本使用

3,学习物பைடு நூலகம்层版图的设计基础

DRC基本过程:(验证版图是否满足工艺要求)

集成电路CAD实训报告

集成电路CAD实训报告系部:尚德光伏学院班级:液晶1001姓名:吴海洋学号:100100266指导老师:陆亚青2012年5月课题一缓冲器1.电路原理图(Schematic Mode 和Symbol Mode)Schematic modeSymbol mode2.瞬时分析语句及波形结果3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md"vin IN GND 1.0vvdd Vdd GND 5.0.dc lin source vin 0 5.0 0.02.print dc v(OUT)4.版图5.LVS对比结果课题二与非门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param 1=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 100n 200n)vb B GND BIT ({0011} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(OUT) v(B) v3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md"va A Gnd 5.0vb B Gnd 5.0vvdd Vdd Gnd 5.0.dc lin source va 0 5.0 0.1 sweep lin source vb 0 5.0 1.print dc v(OUT)4.版图5.LVS对比结果课题三或非门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param 1=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 50n 100n)vb B GND BIT ({0011} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(OUT) v(B) v(A)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md"vvdd Vdd GND 5.0va A GND 5.0vb b GND 5.0.dc lin source va 0 5.0 0.1 sweep lin source vb 0 5.0 1.print dc v(OUT)4.版图5.LVS对比结果课题四CMOS传输门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vin IN GND PULSE (0 5 50n 5n 5n 50n 100n)vc C GND BIT ({1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(OUT) v(C) v(IN)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vin IN GND 5.0vc C GND 5.0.dc lin source vin 0 5.0 0.1 sweep lin source vc 0 5.0 1 .print dc v(OUT)4.版图5.LVS对比结果课题五与或非门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 50n 100n)vb B GND BIT ({0011 0110 1010 1100 0111} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vc C GND PWL (0ns 0V 200ns 0V 205ns 5V 400ns 5V)vd D GND PULSE (5 0 100n 5n 5n 100n 200n).tran/op 1n 400n method=bdf.print tran v(F) v(D) v(C) v(B) v(A)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND 5.0vb B GND 5.0vc C GND 5.0vd D GND 5.0.dc lin source va 0 5.0 1 sweep lin source vb 0 5.0 1 sweep lin source vc 0 5.0 1 .print dc v(F)4.版图5.LVS对比结果课题六异或门1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND PULSE (0 5 50n 5n 5n 50n 100n)vb B GND BIT ({0011 1010 0101} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(F) v(B) v(A)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0va A GND 5.0vb b GND 5.0.dc lin source va 0 5.0 0.1 sweep lin source vb 0 5.0 1 .print dc v(F)4.版图5.LVS对比结果课题七四位加法器1.全加器电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.四位加法器电路原理图(Schematic Mode)3.四位加法器瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0.vector A {A3 A2 A1 A0}.vector B {B3 B2 B1 B0}va A GND BUS ({0011 1110 1100 1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vb B GND BUS ({1101 0111 1010 0101} lt=50n ht=50n on=5 off=0 rt=5n ft=5n).tran/op 1n 400n method=bdf.print tran v(Cout) v(S3) v(S2) v(S1) v(S0)4.四位加法器SPR电路图5.四位加法器SPR版图6.LVS对比结果课题八四位减法器1.全减器电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.四位减法器电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode3.四位减法器瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0.vector A {A3 A2 A1 A0}.vector B {B3 B2 B1 B0}va A GND BUS ({0011 1110 1100 1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vb B GND BUS ({1101 0111 1010 0101} lt=50n ht=50n on=5 off=0 rt=5n ft=5n).tran/op 1n 400n method=bdf.print tran v(Cout) v(S3) v(S2) v(S1) v(S0)4.四位减法器SPR电路图5.四位减法器SPR版图6.LVS对比结果课题九二选一数据选择器1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd0 D0 GND PULSE (0 5 50n 5n 5n 50n 100n)vd1 D1 GND BIT ({1010} lt=50n ht=50n on=5 off=0 rt=5n ft=5n) vs S GND PWL (0ns 0V 200ns 0V 205ns 5V 400ns 5V).tran/op 1n 400n method=bdf.print tran v(Y) v(S) v(D1) v(D0)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd0 D0 GND 5.0vd1 D1 GND 5.0vs S GND 5.0.dc lin source vd0 0 5.0 1 sweep lin source vd1 0 5.0 1 sweep lin source vs 0 5.0 1 .print dc v(Y)4.版图5.LVS对比结果课题十D触发器1.电路原理图(Schematic Mode 和Symbol Mode)Schematic ModeSymbol Mode2.瞬时分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd D GND PULSE (0 5 50n 5n 5n 50n 100n)vclk CLK GND BIT ({0101} lt=100n ht=100n on=5 off=0 rt=5n ft=5n) .tran/op 1n 400n method=bdf.print tran v(Q) v(CLK) v(D)3.直流分析语句及波形结果.include "D:\tanner\TSpice70\models\ml2_125.md".param l=0.5uvvdd Vdd GND 5.0vd D GND 5.0vclk CLK GND 5.0.dc lin source vd 0 5.0 0.1 sweep lin source vclk 0 5.0 1 .print dc v(Q)4.版图5.LVS对比结果。

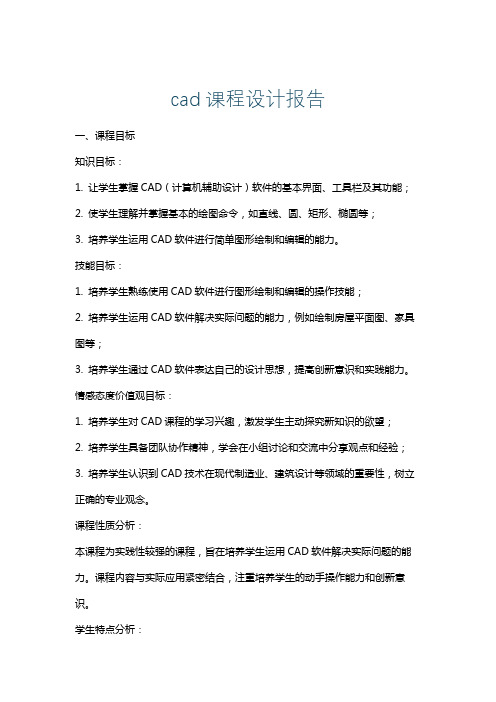

cad课程设计报告

cad课程设计报告一、课程目标知识目标:1. 让学生掌握CAD(计算机辅助设计)软件的基本界面、工具栏及其功能;2. 使学生理解并掌握基本的绘图命令,如直线、圆、矩形、椭圆等;3. 培养学生运用CAD软件进行简单图形绘制和编辑的能力。

技能目标:1. 培养学生熟练使用CAD软件进行图形绘制和编辑的操作技能;2. 培养学生运用CAD软件解决实际问题的能力,例如绘制房屋平面图、家具图等;3. 培养学生通过CAD软件表达自己的设计思想,提高创新意识和实践能力。

情感态度价值观目标:1. 培养学生对CAD课程的学习兴趣,激发学生主动探究新知识的欲望;2. 培养学生具备团队协作精神,学会在小组讨论和交流中分享观点和经验;3. 培养学生认识到CAD技术在现代制造业、建筑设计等领域的重要性,树立正确的专业观念。

课程性质分析:本课程为实践性较强的课程,旨在培养学生运用CAD软件解决实际问题的能力。

课程内容与实际应用紧密结合,注重培养学生的动手操作能力和创新意识。

学生特点分析:学生年级为初中或高中,具备一定的计算机操作基础,对新鲜事物充满好奇,喜欢动手实践。

但可能对CAD软件较为陌生,需要教师耐心引导。

教学要求:1. 教师应注重理论与实践相结合,让学生在实际操作中掌握知识点;2. 教师应关注学生的个体差异,因材施教,提高学生的自信心和成就感;3. 教师应充分利用课堂时间,组织小组讨论和交流,培养学生团队协作能力。

二、教学内容根据课程目标,教学内容分为以下三个部分:1. CAD软件基础操作(2课时)- 熟悉CAD软件界面、工具栏和菜单栏;- 学会使用基本绘图命令,如直线、圆、矩形、椭圆等;- 掌握图形的选择、删除、移动、复制、旋转等基本编辑操作。

2. 基本图形绘制与编辑(4课时)- 绘制简单的平面图形,如房屋平面图、家具图等;- 学会使用尺寸标注、文字注释等功能;- 掌握图层管理、线型、颜色设置等高级编辑功能。

3. CAD综合应用(2课时)- 结合实际案例,运用CAD软件进行设计表达;- 指导学生完成小组项目,如绘制学校平面图、创意家具设计等;- 组织学生进行作品展示和评价,提高学生的创新意识和实践能力。

集成电路CAD实验报告

集成电路CAD实验报告姓名:席悦学号:2120503018 班级:微电子31班一、实验目的:通过设计一个简单的缓冲器的原理图到最终的版图,对Cadence的Composer,Analog Design Environment,Virtuoso,Assura等各大功能模块逐一了解,使学生掌握模拟集成电路设计的总体流程,为日后的学习、工作打下坚实的基础。

二、实验项目:1.缓冲器的设计:在配置好Cadence之后,进入Cadence的CIW界面。

为设计一个完整的缓冲器,首先需要设计一个反相器。

利用Cadence的电路编辑工具Composer-Schematic绘制如下图所示的inverter电路:之后利用此inverter Schematic 构建如下图所示的inverter Symbol:我们知道,一个Buffer是由两个Inverter组成,利用前边构建Inverter Schematic的方法,画出缓冲器Buffer的电路原理图:其中的反相器直接调用之前做好的Inverter的Symbol。

同样的,利用此缓冲器的原理图生成相应的缓冲器Symbol图:之后构建仿真电路,对所设计的Buffer电路进行电路仿真(ADE)。

仿真电路图如下:在仿真过程中,我们分别采用tt,ss,ff工艺角进行仿真,得到了如下的波形图和仿真数据:①tt工艺角:其相应数据参数为:Marker, /I5/V1, /OUT, /INM0: Y, 900mV, 900mV, 900mVx[0], 111.36ps, 778.31ps, 50psx[1], 5.1063ns ,5.9952ns, 5.05ns②ss工艺角:其相应数据参数为:Marker, /I5/V1, /OUT, /INM0: Y, 900mV, 900mV, 900mVx[0], 121.55ps, 927.99ps, 50psx[1], 5.1155ns, 6.1676ns, 5.05ns③ff工艺角:其相应数据参数为:Marker, /I5/V1, /OUT, /INM0: Y, 900mV, 900mV, 900mVx[0], 103.43ps, 653.72ps, 50psx[1], 5.0984ns, 5.8613ns, 5.05ns④分析总结:通过对不同工艺角的仿真,可以清晰的看到ss的上升延迟和下降延迟时间最长,而ff的上升延迟和下降延迟最短,而tt工艺角是上升延迟和下降延迟的典型值。

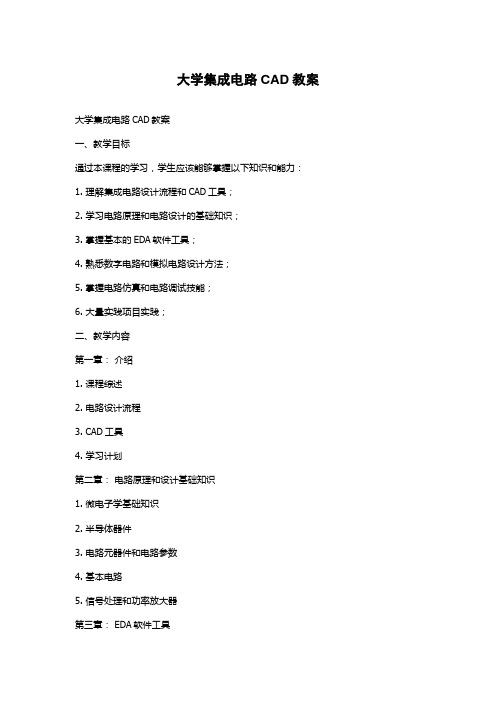

大学集成电路CAD教案

大学集成电路CAD教案大学集成电路CAD教案一、教学目标通过本课程的学习,学生应该能够掌握以下知识和能力:1. 理解集成电路设计流程和CAD工具;2. 学习电路原理和电路设计的基础知识;3. 掌握基本的EDA软件工具;4. 熟悉数字电路和模拟电路设计方法;5. 掌握电路仿真和电路调试技能;6. 大量实践项目实践;二、教学内容第一章:介绍1. 课程综述2. 电路设计流程3. CAD工具4. 学习计划第二章:电路原理和设计基础知识1. 微电子学基础知识2. 半导体器件3. 电路元器件和电路参数4. 基本电路5. 信号处理和功率放大器第三章: EDA软件工具1. 常用EDA软件工具2. 详细介绍特定软件的界面和使用方法3. 电路的概念和基础4. 在EDA工具中创建和完成设计第四章:数字电路设计1. 数字逻辑设计理论和技术2. 组合逻辑电路3. 时序逻辑电路4. 静态存储器第五章:模拟电路设计1. 模拟电路的基础2. 放大器电路3. 滤波电路4. 模拟混合电路设计第六章:电路的仿真与调试1. 仿真软件工具 ~模拟仿真和数字仿真~2. 仿真电路的搭建和参数调整3. 仿真结果分析和优化4. 调试和验证设计第七章:项目实践1. 项目流程安排2. 项目的选题和具体设计3. 必要的EDA软件4. 仿真和调试5. 结果分析和报告撰写三、教学方法1. 理论讲授与实践教学相结合;2. 重视实际项目实践;3. 激发学生的研究兴趣;4. 鼓励自学;5. 培养学生的创新意识和团队合作精神。

四、教学评估方法1. 日常考核:课堂问题解答、小作业;2. 实验报告;3. 课堂设计和项目演示;4. 其他。

五、参考教材1. 微电子电路设计和分析, D.A. Neamen2. 集成电路设计, T. A. Fjeldly和O. H. Saevdal3. 数字电路设计, M. Wakerly4. 电子电路仿真与分析, R. Jacob Baker5. CMOS数字IC设计, J. Rabaey、A. Chandrakasan和B. Nikolic总结大学集成电路CAD教案主要是通过教学目标确定课程的重点和难点,由于IEEE标准的到来,EDA的软件目前已经成为了半导体产业前沿技术的代表。

电路CAD设计报告

电路CAD课程设计报告专业班级:学号:姓名:一、设计的目的与要求:1、设计目的《电路CAD》课程上机操作是建立在已学的单片机,模拟电子技术,数字电子技术等课程以后,综合运用这些课程所学的理论知识,实际的进行一次电路原理图图的设计、PCB印制电路板的设计,其目的有以下几个方面:(1)通过对所学课程的综合运用,熟练掌握运用计算机进行印制电路板的设计,使学到的理论知识相互融汇贯通,在认识上产生一个飞跃。

《电路CAD》课程是一门学习和使用电子设计软件的过程。

上机操作考试和平时理论考试是有区别的,理论考试是为了加深对课堂所讲知识的理解,它内容较窄、训练第一,且是经过抽象加工后给出的理想化的条件,因而有唯一答案,而上机操作考试可全面的考察学生软件使用的熟练程度。

更重要的是,它不仅是停留在理论设计和书面答案上,而要做出符合设计要求的实际电路或者仿真电路。

(2)初步掌握一般电子电路设计的方法,使学生得到一些工程设计的初步训练,并为以后的毕业设计奠定良好基础。

2、设计要求(1)要独立完成设计任务,通过印制电路板的设计,锻炼自己综合运用所学知识的能力。

(2)熟练掌握电子设计软件的使用方法。

(3)学会选用各种电子元器件。

(4)能够写出完整的设计报告。

二、设计方法与步骤:1、设计方法:运用电子设计软件,对一个电路图进行PCB板的制作,包括原理图的绘制,PCB板的设计,最后可以做成成品,最终实现其特定的功能。

2、设计步骤:(1)、原理图的绘制:a、打开电子设计软件进入工作界面,然后执行工作界面的菜单命令File/New,将光标移到菜单File/New处单击,选择project/pcb project,建立一个工程,将默认名改为自己的名字,然后单击OK按钮。

b、继续单击File/New,选择Schematic 进入画原理图的界面。

在按保存按钮保存到自己的工程文件夹中保存名:FSJDL.SchDoc。

c、对原理图进行界面设置,然后添加Miscellaneous Devices .lib 文件库,根据电路图中的元器件,在Miscellaneous Devices .lib库中找到这些元器件,放置在原理图编辑器里。

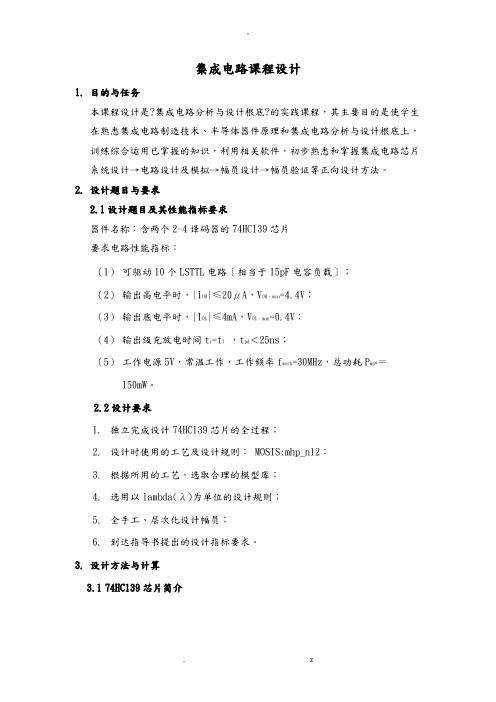

集成电路课程设计报告范例

集成电路课程设计1.目的与任务本课程设计是?集成电路分析与设计根底?的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计根底上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→幅员设计→幅员验证等正向设计方法。

2.设计题目与要求2.1设计题目及其性能指标要求器件名称:含两个2-4译码器的74HC139芯片要求电路性能指标:(1)可驱动10个LSTTL电路〔相当于15pF电容负载〕;(2)输出高电平时,|I OH|≤20μA,V OH,min=4.4V;(3)输出底电平时,|I OL|≤4mA,V OL,man=0.4V;(4)输出级充放电时间t r=t f ,t pd<25ns;(5)工作电源5V,常温工作,工作频率f work=30MHz,总功耗P ma*=150mW。

2.2设计要求1.独立完成设计74HC139芯片的全过程;2.设计时使用的工艺及设计规则: MOSIS:mhp_n12;3.根据所用的工艺,选取合理的模型库;4.选用以lambda(λ)为单位的设计规则;5.全手工、层次化设计幅员;6.到达指导书提出的设计指标要求。

3.设计方法与计算3.174HC139芯片简介74HC139是包含两个2线-4线译码器的高速CMOS数字电路集成芯片,能与TTL集成电路芯片兼容,它的管脚图如图1所示,其逻辑真值表如表1所示:图1 74HC139芯片管脚图表1 74HC139真值表片选输入数据输出C s A1 A0 Y0 Y1Y2Y30 0 0 0 1 1 10 0 1 1 0 10 1 0 1 1 0 10 1 1 1 1 1 01 ×× 1 1 1 1从图1可以看出74HC139芯片是由两片独立的2—4译码器组成的,因此设计时只需分析其中一个2—4译码器即可,从真值表我们可以得出Cs为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。

集成电路CAD综合实践报告

专业综合实践总结报告姓名:林道悦学号:04081400姓名:李操__ 学号:04081366姓名:史正韵学号:专业及班级:电子科学与技术08—1设计题目:D触发器电路图和版图设计起始时间:2010~2011第(2)学期第18周~第19周指导老师:刘海成绩:________日期:________一、课题任务:<1>、利用所学的半导体集成电路设计、微电子学、集成电路CAD和相关的EDA 技术,完成D触发器电路图和版图设计;<2>、利用cadence软件进行集成电路(D触发器)的逻辑分析、仿真分析、交直流分析和瞬态分析及版图设计;<3>、通过实践培养学生的科学性、系统性及全面性的设计素质,开拓学生的设计思路,提高理论知识的应用能力和团队合作精神。

二、方案比较与选择:维持阻塞式边沿D触发器是最常用的触发器之一。

对于上升沿触发的D触发器来说,其输出Q只在CLK由L到H的转换时刻才会跟随输入D的状态而变化,其他时候Q则维持不变。

维持阻塞式边沿D触发器的逻辑图和逻辑符号如图2-1所示。

该触发器由六个与非门组成,其中G1、G2构成基本RS触发器,G3、G4组成时钟控制电路,G5、G6组成数据输入电路。

(a)逻辑图(b)逻辑符号图2-1 持阻塞式边沿D触发器SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当SD=1且RD=0时,不论输入端D为何种状态,都会使Q=1,Q非=0,即触发器置1;当SD=0且RD=1时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D非,Q6=Q5非=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

cad课程设计报告书

cad课程设计报告书一、教学目标本课程的教学目标是使学生掌握CAD(计算机辅助设计)的基本知识和技能,能够熟练使用相关软件进行简单的二维和三维设计。

具体目标如下:1.知识目标:了解CAD的基本概念、原理和常用的操作命令,熟悉CAD软件的界面和功能,掌握二维绘图和三维建模的基本方法。

2.技能目标:能够独立完成简单的二维和三维设计任务,如绘制平面图、立面图、剖面图等,建立基本的三维模型并进行简单的编辑和渲染。

3.情感态度价值观目标:培养学生对CAD技术的兴趣和热情,认识到CAD技术在工程设计、艺术创作等领域的广泛应用和重要性,培养学生的创新精神和团队合作意识。

二、教学内容根据课程目标,教学内容主要包括以下几个部分:1.CAD基本概念和原理:介绍CAD的定义、发展历程和应用领域,理解CAD技术的基本原理和操作方法。

2.CAD软件操作:学习CAD软件的界面和功能,掌握常用绘图命令、编辑命令和三维建模命令,熟悉图层、线型、颜色等基本设置。

3.二维绘图:学习绘制基本二维图形,如直线、圆、多边形等,掌握尺寸标注、文字输入和图块使用等技巧。

4.三维建模:学习建立基本三维模型,如立方体、球体、圆柱体等,掌握三维编辑和渲染的基本方法。

5.实际案例操作:通过实际案例的分析和操作,让学生掌握CAD技术在工程设计、艺术创作等领域的应用,提高学生的综合运用能力。

三、教学方法为了达到课程目标,我们将采用以下几种教学方法:1.讲授法:通过讲解CAD的基本概念、原理和操作方法,让学生掌握相关知识。

2.案例分析法:通过分析实际案例,让学生了解CAD技术在工程设计、艺术创作等领域的应用,提高学生的综合运用能力。

3.实验法:通过上机操作实验,让学生亲手实践,加深对CAD软件操作的理解和掌握。

4.小组讨论法:通过小组合作完成项目任务,培养学生的团队合作意识和沟通能力。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用权威、实用的CAD教材,为学生提供系统、全面的知识学习。

电路CAD课程设计报告

电路CAD课程设计报告—protel 99se实现姓名:学号:指导教师:学院:目录第一章1.1摘要…………………………………………………1.2 概述…………………………………………………第二章以门把防盗自动报警器为例简述用Protel 99se进行电路设计的基本步骤2.1课程设计的目的……………………………………2.2电路原理图设计步骤………………………………2.3印刷电路板设计步骤………………………………第三章设计过程中遇到的问题以及解决方法…………………第四章参考文献…………………………………………………第五章课程设计小结……………………………………………电路CAD课程设计之门把防盗自动报警器—protel 99se实现1.1摘要随着电子技术的发展,大规模的集成电路的应用已经越来越普遍,EDA (Electronic Design Automation,电子设计自动化)已经成为不可逆转的潮流,所以掌握这门技术是成为一个通信电子类人才的基本条件。

电路及PCB设计是EDA技术中一个重要的内容,Protel是其中很杰出的一个软件,流行最早,应用面最宽。

在本文中,将以门把防盗自动报警器为例简述Protel 99se在电路设计中的应用。

其设计步骤主要有:原理图设计,封装,网络表生成,PCB生成,布线。

关键词:protel 99se、原理图、网络表、封装、PCB、布线1.2概述一)、EDA(Electronic Design Automation,电子设计自动化)技术是现代电子工程领域的一门新技术它提供了基于计算机和信息技术的电路系统设计方法。

电路及PCB设计是EDA技术中的一个重要内容,Protel是其中一个很杰出的软件,它是桌面环境下以PDM(设计管理和协作技术)为核心的一个优秀的印刷电路板设计系统。

Protel 99se主要有两大部分组成:电路设计部分,主要有:原理设计系统,包括用于设计原理图的原理图编辑器Sch;用于修改和生成原理图元件的元件编辑器;各种报表的生成器Schlib,印刷电路板设计系统,包括用于设计电路板的电路板编辑器PCB以及用于修改、生成元件封装的元件封装编辑器PCBLib。

课程设计报告---电子线路CAD

课程设计报告---电子线路CAD一、本课程设计的目的和任务电子线路CAD目的是使学生能够掌握电子线路的计算机辅助设计基础知识,培养学生对电子系统设计的基本能力,综合所学电子技术系统知识将各功能环节组合以实现所要求的一个功能,培养学生综合运用所学知识能力和分析解决问题能力,并具有独立设计电子线路图和制版的工作能力。

本项目设计的主要任务是:通过学生独立使用EDA软件设计电子系统的过程,逐渐培养学生的整体系统设计意识,为复杂电路系统的分析和设计打下坚实的基础。

二、具体实施其具体的步骤为:先打开ad软件,点及设置,将文字从英文改为中文,再新建一个工程,新建文件档,新建pcb工程,创建好pcb 好后设计图纸,画原理图,找到元件后安放,之后再连线,修改参数值,绘制好后没有错误的情况之后,将开始的原理图按到pcb板中,调整好位置即可连线,自动连线。

创建工程:首先先点击Libraries显示出面板,在这里面寻找原理图所需要的元件,常用分立元件在 Miscellaneous Devices.IntLib元件库中,一般连接器在Miscellaneous Connectors.IntLib元件库中,而其他的封装元件可以用Search在Libraries里搜索,找到后将其库文件添加到Libraries 中,即可。

三、课程设计总结通过这次4天的专周实践教学电子线路cad的学习,首先学习了ad软件的基本信息,在ad中对于实物布线跟单片机keli软件布置近似,但是在ad软件中可能会找不到对应的实物,这个时候就需要自己去绘制并设计元器件,将原理图绘制好之后,将原理图检查无误没问题之后,就可以将他建立到pcb中,这个时候就可以直接拖动元器件到绘制框图里即可,点击自动连线也是需要之前的操作无误后就行。

这次课对于我的电子线路的学习有了一个更深刻的了解,希望在之后的课程中能有更深刻的感悟,在平时焊接线路板上也能有更深刻的知识基础。

不管是平时的焊接中还是比赛时用电路板都能够有一个更好的基础,使电路板能够正常发挥其作用。

《集成电路课程设计报告

集成电路课程设计报告单级CMOS放大电路的设计与仿真系:专业:—学号:. 姓名:—指导教师:-报告提交日期:目录摘要.............................. 词............ (2)1引言............ .. (2)2 CMOS放大电述22.1 MOS管介绍 (3)2.2 MOS管特性分析 (5)3 设计与仿真......................................................... •. (9)3.1设计............................................................ (9)3.1.1电路设3.1.2结果分析 (10)3.2仿真............................................................•••• 123.2.1技术支持 (12)3.2.2仿真与结果分析 (12)4结论......................................................... .. (17)5体会与展望......................................................... (17)参考文献......................................................... . (18)致谢.........................................................17单级CMOS放大电路的设计与仿真摘要:本文给出单级CMOS放大电路的结构组成和工作原理,电路结构,参数的分析过程。

并对其主要组成部分MOS管进行了各种分析和放大电路的分析和仿真。

关键词:单级CMOS放大电路,设计与仿真,PspicelO.5.Design and Simulation of The single-stage CMOS Amplifier CircuitAbstract : This article has produced single-stage CMOS amplifier circuit composed of the stmctiire and working principle, the electric circuit stmctiire and the parameter analysis process・ And its major component of the CMOS transistors to analysis and amplification circuit analysis and simulatio n. Key words: single-stage CMOS amplifier circuit Design and simulation Pspice 10.51-引言在大多数模拟电路和数字电路中,放大是一个基本的功能。

电路cad课程设计报告

电路cad课程设计报告一、教学目标本课程旨在通过学习电路CAD的基本知识和技能,使学生能够熟练使用电路CAD软件进行电路设计和分析。

具体目标如下:1.理解电路CAD的基本概念和原理。

2.熟悉电路CAD软件的基本操作和功能。

3.掌握电路CAD软件中的常用电路符号和元件。

4.能够使用电路CAD软件进行基本的电路图设计。

5.能够进行电路仿真和分析,并得出合理的结果。

6.能够根据电路需求,设计出符合要求的电路图。

情感态度价值观目标:1.培养学生的创新意识和解决问题的能力。

2.培养学生的团队合作意识和沟通能力。

3.培养学生的自主学习和持续学习的习惯。

二、教学内容根据课程目标,教学内容主要包括以下几个方面:1.电路CAD基本概念和原理的介绍。

2.电路CAD软件的基本操作和功能的讲解。

3.电路CAD软件中常用电路符号和元件的使用。

4.电路图设计的方法和技巧。

5.电路仿真和分析的方法和技巧。

6.实际案例分析和实践操作。

7.电路CAD基本概念和原理:介绍电路CAD的定义、作用和发展趋势。

8.电路CAD软件的基本操作:讲解软件的安装、界面熟悉、基本操作等。

9.电路CAD软件中常用电路符号和元件:介绍常用电路符号和元件的用途和用法。

10.电路图设计:讲解电路图的设计方法、步骤和技巧。

11.电路仿真和分析:讲解电路仿真和分析的方法、步骤和技巧。

12.实际案例分析和实践操作:分析实际电路案例,进行实践操作。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法相结合的方式:1.讲授法:通过讲解和演示,使学生掌握电路CAD的基本概念和原理。

2.讨论法:通过小组讨论,培养学生的团队合作意识和沟通能力。

3.案例分析法:通过分析实际电路案例,使学生能够将理论知识应用于实际问题。

4.实验法:通过实践操作,使学生熟练使用电路CAD软件进行电路设计和分析。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将准备以下教学资源:1.教材:选用权威、实用的电路CAD教材,为学生提供系统的理论知识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《集成电路CAD》课程设计报告

四位全加全减器设计

专业:集成电路

班级:电子0 6 0 4

学号:200681131

姓名:高丕龙

一.实验目的

1熟悉在max+plus II 的环境下设计数字电路的步骤和方法

2学习使用vhdl语言,进行设计数字电路的RTL级电路

3通过max+plus II 软件中对自行设计的电路的仿真,加深对数字电路设计的理解。

二.实验原理

1.功能描述

输入:select,Ci, A, B 输出:S,Co

Select=0时,S为全加器的求和位(A+B),Co为全加器的高位进位。

Ci为全加器低位进位。

Select=1时,S为全减器的求差位(A-B),Co为全减器的高位借位。

Ci为全减器低位借位。

2.一位全加全减器真值表:

输入输出

Select Ci A B S Co

0 0 0 0 0 0

0 0 0 1 1 0

0 0 1 0 1 0

0 0 1 1 0 1

0 1 0 0 1 0

0 1 0 1 0 1

0 1 1 0 0 1

0 1 1 1 1 1

1 0 0 0 0 0

1 0 0 1 1 1

1 0 1 0 1 0

1 0 1 1 0 0

1 1 0 0 1 1

1 1 0 1 0 1

1 1 1 0 0 0

1 1 1 1 1 1

3.逻辑化简

由真值表得

S=A○十B○十Ci=((A○十Select)○十B○十Ci)○十Select

Co=(A○十Select)B+Ci((A○十Select)+B)=((A○十Select)○十B)Ci+(A○十Select)B

对于半加器的逻辑表达式为:S=A○十B Co=AB

综上,一位全加全减器可由两个半加器,两个异或门和一个或门组成。

4.毛刺的产生与消除

组合逻辑电路由于输入到输出各端的延时不同,在输出端稳定之前会产生错误的输出。

在本电路中,由于低位的进位或借位传输到输出的时间比其他信号传输的延时要长,因此当低位产生进位或借位时会出现错误的输出。

一种常见的方法是利用D触发器的D输入端对毛刺信号不敏感的特点,在输出信号的

保持时间内,用触发器读取组合逻辑的输入输出信号。

由组合逻辑电路的最大延时Td为16.7ns,D触发器的时钟周期T应略大于Td,取20ns。

三.电路原理图设计及vhdl代码

1.D触发器vhdl文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY dff IS

PORT ( CLK: IN STD_LOGIC;

D:in std_logic;

Q: OUT STD_LOGIC );

END dff;

ARCHITECTURE behav OF dff IS

begin

process(clk)

begin

if clk'event and clk='1'then q<=d;

end if;

end process;

end architecture behav;

2.半加器vhdl文件

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity half_adder is

port ( a,b :in bit;

c,sum:out bit);

end half_adder;

architecture adder of half_adder is

begin

c<=a and b;

sum<=a xor b;

end adder;

3.一位全加全减器gdf文件(由半加器和异或门,或门组成) 4四位全加全减器gdf文件(由四个一位全加全减器组成)

5.四位全加全减器生成的符号文件

6.D触发器去毛刺gdf文件(由一个四位全加全减器和十五个D触发器组成)

四.仿真波形及分析1.不加D触发器时的仿真波形1)减法波形(select=1)

2)加法波形(select=0)

2.四位全加全减器延时分析

3.加D触发器后的仿真波形1)减法波形(select=1)

2)加法波形(select=0)

四.心得体会

通过这次4位全加全减器的设计,我进一步熟悉了数字系统vhdl设计和仿真的流程,进一步了解了max plusII软件的使用方法。

并且加深了对数字系统中组合逻辑电路和时序逻辑电路的理解,尤其加深了对D触发器输入输出缓冲功能的理解。